JP4748877B2 - Storage device - Google Patents

Storage device Download PDFInfo

- Publication number

- JP4748877B2 JP4748877B2 JP2001148893A JP2001148893A JP4748877B2 JP 4748877 B2 JP4748877 B2 JP 4748877B2 JP 2001148893 A JP2001148893 A JP 2001148893A JP 2001148893 A JP2001148893 A JP 2001148893A JP 4748877 B2 JP4748877 B2 JP 4748877B2

- Authority

- JP

- Japan

- Prior art keywords

- write

- bit line

- transistors

- word line

- line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/16—Multiple access memory array, e.g. addressing one storage element via at least two independent addressing line groups

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/413—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Static Random-Access Memory (AREA)

Description

【0001】

【発明の属する技術分野】

この発明は、MISFET(Metal Insulator Semiconductor Field Effect Transistor)により構成されるマルチポートSRAM(Static Random Access Memory)に関し、特に当該SRAMのメモリセルへのデータの読み書きを行う技術に関する。

【0002】

【従来の技術】

SRAMは集積回路において、データや命令をキャッシュ(cache)、即ちCPU(Central Processing Unit)のタイミングに合わせてデータをCPUへ伝達するために一時的に保持する機能を担ったり、順序回路の状態を記憶するために用いられている。近年では、メモリからデータを読んだり、メモリへデータを書き込む速度(rate)が重要視されている。メモリのバンド幅(bandwidth)を上げるために、SRAMのメモリセルに複数の入出力端子を設ける技術が提案されている。この技術として、一つの読み出し端子(read port)と一つの書き込み端子(write port)とを備えたデュアルポート(dual port)スタティックメモリセルや、多数の読み出し端子と書き込み端子とを備えたマルチポート(multi port)スタティックメモリセルを例挙できる。

【0003】

図51は従来のSRAMのメモリセルアレイ周辺の構成を示す概念図である。メモリセルはm行n列のマトリックス状に配置されており、そのi行j列目のメモリセルをMCijとして示すことにする。図51においては第1行第3列に配置されたメモリセルMC13の符号が表記されている。

【0004】

図51に示されたSRAMでは、行方向にワード線が、列方向にビット線が、それぞれ延在する構成を採っている。ワード線デコーダ3はワード線群30i(i=1,2,3,…,m−1,m)に接続され、入力される行アドレスRAに対応するワード線群30iを選択的に活性化させる。またビット線デコーダ4はビット線群40j(j=1,2,3,…,n−1,n)に接続され、入力される列アドレスCAに対応するビット線群40jを選択的に活性化させる。

【0005】

メモリセルMCijにおいてワード線群30iとビット線群40jが交差する。つまり行方向に配列された複数のメモリセルには共通のワード線群が敷設され、列方向に配列された複数のメモリセルには共通のビット線群が敷設される。

【0006】

ワード線群30iは書き込みワード線31i、読み出しワード線33i、読み出し補ワード線32iから構成されており、後二者は読み出しワード線対を構成している。またビット線群40jは書き込みビット線41j、書き込み補ビット線42j、読み出しビット線43jから構成されており、前二者は書き込みビット線対を構成している。

【0007】

図52はいずれのメモリセルMCにも共通する構造を例示する回路図である。メモリセルMCの構造は基本的には行や列の位置(i,j)には依存しないので、ここでは行や列の位置を示す添字は省略している。

【0008】

メモリセルMCは、一対のインバータL1,L2が逆並列に接続された構成の記憶部(本明細書において「ストレージセル」と称する)SCと、読み出し回路RKと、アクセストランジスタQN3,QN4とを備えている。

【0009】

ストレージセルSCにおいて、インバータL1はトランジスタQP1,QN1の直列接続で、インバータL2はトランジスタQP2,QN2の直列接続で構成されている。また読み出し回路RKはトランジスタQP3,QP4,QN5,QN6の直列接続で構成されるトライステートインバータを備えている。

【0010】

トランジスタQN1〜QN6にはN型のMOSFET(Metal Oxide Semiconductor Field Effect Transistor)が、トランジスタQP1〜QP4にはP型のMOSFETが、それぞれ採用される。例えばN型MOSFETは表面チャネル型であり、P型MOSFETは表面チャネル型か、あるいは、埋め込みチャネル型である。

【0011】

ストレージセルSCは一対のノードN1,N2を有しており、ノードN1,N2がそれぞれ“H”,“L”の場合と、その逆の場合の一対の記憶状態が存在する。なお、“H”とは(VDD+VSS)/2より高い電位に対応する論理を意味し、“L”とは(VDD+VSS)/2より低い電位に対応する論理を意味する。但し電位VSSには、グラウンドが選ばれる場合が多い。以下、“H”、“L”はそれぞれ論理のみならず、その論理対応する電位を意味する場合もある。なお、“H”,“L”のどちらの状態をSRAMのビットの”1”,”0”に対応させるかは、設計する上での選択事項である。

【0012】

N型MOSFETは、そのゲートに“H”が印加されたときにオンし、“L”が印加されたときにオフする。P型MOSFETは、そのゲートに“L”が印加されたときにオンし、“H”が印加されたときにオフする。オンの状態では、電流がソース/ドレイン間を流れ、両者間が電気的に導通する。また、オフの状態では、ソース/ドレイン間は電気的に遮断され電流は殆ど流れない。

【0013】

ノードN1はインバータL2の入力端であり、ノードN1の電位に対応する論理と相補的な論理に対応する電位がノードN2に出力される。ノードN2はインバータL1の入力端であり、ノードN2の電位に対応する論理と相補的な論理の反転ビットがノードN1に出力される。よって互いに相補的な論理に対応する記憶状態が一対存在する。

【0014】

アクセストランジスタQN3はノードN1,N4においてそれぞれストレージセルSC及び書き込みビット線41と接続される。アクセストランジスタQN4はノードN2,N5においてそれぞれストレージセルSC及び書き込み補ビット線42と接続される。そしてアクセストランジスタQN3,QN4のゲートは共通して書き込みワード線31に接続される。

【0015】

読み出し回路RKにおいて、トランジスタQP4,QN5のそれぞれのドレインがノードN3に共通して接続されている。そしてトランジスタQP3,QN6のゲートは共通してノードN1に接続されている。またトランジスタQP4,QN5のゲートは、それぞれ読み出し補ワード線32及び読み出しワード線33に接続されている。上記のようにメモリセルMCにはデュアルポートスタティックメモリセルが採用されている。

【0016】

メモリセルMCからのデータの読み出しを行う場合、読み出しワード線33と読み出し補ワード線32には相補的な論理が設定される。そして読み出しの対象となるメモリセルMCの行に対応した読み出しワード線33と読み出し補ワード線32がそれぞれ“H”,“L”に設定され、それ以外の行に対応した読み出しワード線33と読み出し補ワード線32がそれぞれ“L”,“H”に設定される。

【0017】

よって読み出しの対象となるメモリセルMCの読み出し回路RKのトランジスタQP4,QN5はいずれもオンする。これによりトランジスタQP3,QN6が構成するインバータによって、ノードN1と相補的な値がノードN3を介して読み出しビット線43へと与えられる。その一方で、読み出しの対象ではないメモリセルMCの読み出し回路RKのトランジスタQP4,QN5はいずれもオフする。これにより読み出しビット線43は、読み出しの対象ではないメモリセルMCのストレージセルSCとは遮断される。

【0018】

メモリセルMCへのデータの書き込みを行う場合、書き込みの対象となるメモリセルMCの行に対応した書き込みワード線31が“H”に設定され、それ以外の行に対応した書き込みワード線31が“L”に設定される。

【0019】

よって書き込みの対象となるメモリセルMCのアクセストランジスタQN3,QN4はいずれもオンし、ストレージセルSCのノードN1,N2はそれぞれノードN4,N5を介して書き込みビット線41、書き込み補ビット線42に接続される。一方、書き込みの対象ではないメモリセルMCのアクセストランジスタQN3,QN4はいずれもオフし、ストレージセルSCのノードN1,N2は書き込みビット線41、書き込み補ビット線42とは遮断される。

【0020】

上述のようにストレージセルSCのノードN1,N2の論理は相補的な関係を有するので、書き込みの対象となるメモリセルMCの列に対応した書き込みビット線41と書き込み補ビット線42には相補的な論理が設定される。そしてノードN1,N2には書き込みビット線41と書き込み補ビット線42に設定された論理が書き込まれることになる。

【0021】

書き込み動作が終了すると、書き込みワード線31が“L”に設定され、アクセストランジスタQN3,QN4はオフする。それゆえ、ストレージセルSCは書き込みビット線対から遮断され、ストレージセルSCに保持されたデータは書き換えられず、スタンバイ状態となる。

【0022】

【発明が解決しようとする課題】

上記の構成において、書き込み動作時に書き込みワード線31が“H”に設定されると、書き込み対象であるメモリセルMCと同じ行に属するメモリセルMCの全てにおいて、そのアクセストランジスタQN3,QN4がオンする。よって、書き込み対象であるメモリセルMCと同じ行に属し、かつ書き込み対象ではないメモリセルMCでは、書き込み動作の間、アクセストランジスタQN3,QN4を介してノードN1,N2がそれぞれ書き込みビット線41、書き込み補ビット線42に接続されることになる。

【0023】

その一方、書き込みの対象とならないメモリセルMCの列に対応した書き込みビット線41と書き込み補ビット線42には、通常はいずれも等しい電位をプリチャージする。プリチャージの電位は例えばVDD,(VDD+VSS)/2,VSSである。従って当該メモリセルMCのノードN1,N2の電位に依拠して、書き込みビット線41、書き込み補ビット線42の一方の電位がVSSへと、また他方の電位が(VDD−Vthn)へと、それぞれ引っ張られることになる(但し書き込みワード線31には電位VDDが印加され、トランジスタQN3,QN4のしきい値電圧をVthn>0とする)。このようにプリチャージされた書き込みビット線対へのノードN1,N2を介した電位の印加は、不要な電力消費を招来する。

【0024】

また、上記のようにしてストレージセルSCによって電位が印加されたビット線対に対し、次の書き込み動作に備えて改めてプリチャージが行われる。この際にも新たに不要な電力が消費される。

【0025】

図53は上記の電力消費を防止するために提案されたメモリセルMCの構成を示す回路図であり、例えば米国特許公報6,005,794に紹介されている。

【0026】

NMOSトランジスタQN9,QN10はノードN1と電位VSSを与える電位点(以下「電位点VSS」とも称す)、例えば接地との間に直列に接続されている。NMOSトランジスタQN9のゲートはノードN4において書き込みビット線41と、NMOSトランジスタQN10のゲートは書き込みワード線31と、それぞれ接続されている。同様にして、NMOSトランジスタQN11,QN12はノードN2と電位点VSSとの間に直列に接続されている。NMOSトランジスタQN11のゲートはノードN5において書き込み補ビット線42と、NMOSトランジスタQN12のゲートは書き込みワード線31と、それぞれ接続されている。

【0027】

書き込みの対象となるメモリセルMCに対応する(即ち選択された行の)書き込みワード線31は、書き込み動作時に“H”となり、トランジスタQN10,QN12がオンする。そして当該メモリセルMCに対応する(即ち選択された列の)書き込みビット線41、読み出しビット線43には相補的な論理が与えられるので、トランジスタQN9,QN11のいずれか一方のみがオンする。書き込みビット線41、書き込み補ビット線42がそれぞれ“H”,“L”であれば、ノードN1は論理“L”に設定される。これによりノードN2は“H”となる。逆に書き込みビット線41、書き込み補ビット線42がそれぞれ“L”,“H”であれば、ノードN2は論理“L”に設定される。これによりノードN1は“H”となる。

【0028】

このような書き込み動作時に、選択されない書き込みビット対線はいずれも電位VSSに設定される。よって書き込み対象ではないメモリセルMCにおいてはトランジスタQN9,QN11がオフしているので、選択された書き込みワード線31に対応する行に配置され、書き込みワード線31が“H”となっているメモリセルMCであっても、ノードN1,N2はストレージSCの外部から強制的に電位を設定されることがない。つまり上記の不要な電力消費が生じないという利点がある。

【0029】

しかし、この回路ではストレージセルSCの記憶内容を変更する書き込み動作に必要な時間が長いという問題点がある。つまりストレージセルSCの外部からノードN1,N2のいずれか一方を“L”へと設定するが、他方をストレージセルSCの外部から“H”に設定する機能はない。例えばノードN1,N2がそれぞれ“H”,“L”である状態を、これと相補的な状態へと反転させる場合、トランジスタQN9,QN10がオンして、ノードN1を放電しようとするが、ノードN2が“L”であったし、これをストレージセルSCの外部から“H”にすることもないので、インバータL1はノードN1を“H”に保持しようとする。ストレージセルSCはデータを安定に保持するために、高いスタティックノイズマージンを持つように設計されているため、ノードN1を放電することのみによってストレージセルSCの記憶内容を迅速に反転することはできない。

【0030】

本発明は、上記の背景に基づいて為されたもので、記憶内容を反転する書き込みを迅速に行いつつ、不要な電力の消費を低減する技術を提供することを目的としている。

【0031】

【課題を解決するための手段】

この発明のうち請求項1にかかるものは、(a)ワード線群の複数と、(b)ビット線群の複数と、(c)メモリセルの複数とを備える記憶装置であって、前記ワード線群の各々が(a−1)書き込みワード線を有し、前記ビット線群の各々が(b−1)書き込みビット線と、(b−2)前記書き込みビット線に対応して設けられる書き込み制御線とを有し、(c)前記メモリセルの各々が一の前記ワード線群と一の前記ビット線群とに対応して設けられ、(c−1)第1の記憶ノードを含むストレージセルと、(c−2)対応する前記一のビット線群の前記書き込みビット線と、前記第1の記憶ノードとの間に接続され、対応する前記一のワード線群の前記書き込みワード線と、前記書き込み制御線のいずれもが活性化した場合にのみ導通する第1のスイッチとを有する。そして選択された前記ビット線群における前記書き込み制御線が活性化し、選択されない前記ビット線群における前記書き込み制御線は活性化しない。

【0032】

そして、前記ビット線群の各々は、(b−3)前記書き込みビット線に対応して設けられる書き込み補ビット線を更に有し、前記ストレージセルの各々は、(c−1−1)前記第1の記憶ノードにおける論理と相補的な論理が与えられる第2の記憶ノードを含み、前記メモリセルの各々は、(c−3)対応する前記一のビット線群の前記書き込み補ビット線と、前記第2の記憶ノードとの間に接続され、対応する前記一のワード線群の前記書き込みワード線と、前記書き込み制御線のいずれもが活性化した場合にのみ導通する第2のスイッチを更に有し、前記書き込みビット線及び書き込み補ビット線は、その属する前記ビット線群が選択された場合には相互に相補的な論理を採り、選択されない場合には相互に等しい論理を採り、一の前記ビット線群において、前記書き込み制御線は前記書き込みビット線及び書き込み補ビット線の排他的論理和を採る。

【0033】

この発明のうち請求項2にかかるものは、請求項1記載の記憶装置であって、前記書き込みビット線及び書き込み補ビット線の電位を非反転増幅してから前記排他的論理和が採られる。

【0037】

この発明のうち請求項3にかかるものは、(a)ワード線群の複数と、(b)ビット線群の複数と、(c)メモリセルの複数とを備える記憶装置であって、前記ワード線群の各々が(a−1)書き込みワード線を有し、前記ビット線群の各々が(b−1)書き込みビット線と、(b−2)前記書き込みビット線に対応して設けられる書き込み制御線とを有し、(c)前記メモリセルの各々が一の前記ワード線群と一の前記ビット線群とに対応して設けられ、(c−1)第1の記憶ノードを含むストレージセルと、(c−2)対応する前記一のビット線群の前記書き込みビット線と、前記第1の記憶ノードとの間に接続され、対応する前記一のワード線群の前記書き込みワード線と、前記書き込み制御線のいずれもが活性化した場合にのみ導通する第1のスイッチとを有する。そして選択された前記ビット線群における前記書き込み制御線が活性化し、選択されない前記ビット線群における前記書き込み制御線は活性化しない。

そして、前記第1のスイッチは(c−2−1)制御電極と、前記書き込みビット線に接続された第1の電流電極と、前記第1の記憶ノードに接続された第2の電流電極とを備える第1トランジスタと(c−2−2)前記書き込み制御線が接続された制御電極と、前記第1トランジスタの前記制御電極に接続された第1の電流電極と、前記書き込みワード線に接続された第2の電流電極とを備える第2トランジスタとを含む。

【0038】

この発明のうち請求項4にかかるものは、(a)ワード線群の複数と、(b)ビット線群の複数と、(c)メモリセルの複数とを備える記憶装置であって、前記ワード線群の各々が(a−1)書き込みワード線を有し、前記ビット線群の各々が(b−1)書き込みビット線と、(b−2)前記書き込みビット線に対応して設けられる書き込み制御線とを有し、(c)前記メモリセルの各々が一の前記ワード線群と一の前記ビット線群とに対応して設けられ、(c−1)第1の記憶ノードを含むストレージセルと、(c−2)対応する前記一のビット線群の前記書き込みビット線と、前記第1の記憶ノードとの間に接続され、対応する前記一のワード線群の前記書き込みワード線と、前記書き込み制御線のいずれもが活性化した場合にのみ導通する第1のスイッチとを有する。そして選択された前記ビット線群における前記書き込み制御線が活性化し、選択されない前記ビット線群における前記書き込み制御線は活性化しない。

そして、前記第1のスイッチは(c−2−1)前記書き込みワード線が接続された制御電極と、第1の電流電極と、前記書き込み制御線に接続された第2の電流電極とを備える第1トランジスタと(c−2−2)前記第1トランジスタの前記第1の電流電極が接続された制御電極と、前記書き込みビット線に接続された第1の電流電極と、前記第1の記憶ノードに接続された第2の電流電極とを備える第2トランジスタとを含む。

【0044】

この発明のうち請求項5にかかるものは、請求項3記載の記憶装置であって、前記第1トランジスタはSOI基板上に形成されたNMOSトランジスタであって、非活性の前記書き込みワード線には、前記第1トランジスタの前記第1電流電極とボディとに対する順バイアスを軽減する電位が与えられる。

【0051】

【発明の実施の形態】

本実施の形態において、特に断らない限り、ワード線が活性化、即ち選択されている状態には論理“H”が対応し、活性化していない、即ち選択されていない状態には“L”が対応するものとして説明する。これらの関係を逆にしても、使用されるトランジスタの導電型を適宜に入れ替えれば、下記の説明は妥当する。

【0052】

実施の形態1.

図1はこの発明の実施の形態1にかかるSRAMのメモリセルアレイ周辺の構成を示す概念図である。従来のSRAMの構成に対して、ビット線群40jに書き込み制御線44jが追加されたことが特徴的な構造となっている。書き込み制御線44jもビット線デコーダ4によってその電位(あるいは論理)が設定される。具体的には、書き込み制御線44jには書き込みビット線41jに与えられる論理と書き込み補ビット線42jに与えられる論理との排他的論理和(以下「XOR(exclusive OR)」とも表記する)に相当する論理が設定される。まずは簡単のために、書き込みビット線41jと書き込み補ビット線42jにはプリチャージの期間において電位VDD,VSSのいずれかが与えられるものとして説明する。

【0053】

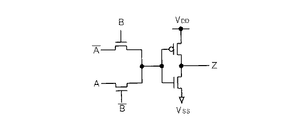

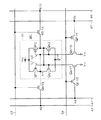

図2は、図1に示されたメモリセルMCの一つの構成を例示する回路図である。従来の技術と同様に、行の位置及び列の位置を示す添字は省略している。メモリセルMCはストレージセルSC、読み出し回路RK及びいずれもNMOSトランジスタであるパストランジスタMN9,MN10,MN11,MN12を備えており、また書き込みビット線41、書き込み補ビット線42、読み出しビット線43、書き込みワード線31、読み出し補ワード線32、読み出しワード線33が敷設されている。

【0054】

ストレージセルSCは、逆並列に接続されたインバータL1,L2を有しており、それぞれの出力端としてノードN1,N2が存在する。インバータL1は、電位VDDが印加されるソース、ノードN1に接続されたドレイン、ノードN2に接続されたゲートを含むPMOSトランジスタQP1と、電位VSSが印加されるソース、ノードN1に接続されたドレイン、ノードN2に接続されたゲートを含むNMOSトランジスタQN1とで構成されている。同様にして、インバータL2は、電位VDDが印加されるソース、ノードN2に接続されたドレイン、ノードN1に接続されたゲートを含むPMOSトランジスタQP2と、電位VSSが印加されるソース、ノードN2に接続されたドレイン、ノードN1に接続されたゲートを含むNMOSトランジスタQN2とで構成されている。

【0055】

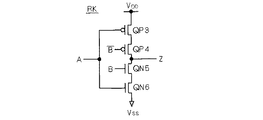

読み出し回路RKは電位VDDが印加されるソース、ノードN1に接続されたゲートを含むPMOSトランジスタQP3と、ノードN3において読み出しビット線43に接続されたドレイン、読み出し補ワード線32に接続されたゲートを含むPMOSトランジスタQP4と、電位VSSが印加されるソース、ノードN1に接続されたゲートを含むNMOSトランジスタQN6と、ノードN3において読み出しビット線43に接続されたドレイン、読み出しワード線33に接続されたゲートを含むNMOSトランジスタQN5とで構成されたトライステートインバータである。トランジスタQP3のドレインとトランジスタQP4のソース、トランジスタQN6のドレインとトランジスタQN5のソースは、それぞれ接続されている。

【0056】

図3はトライステートインバータの構成を例示する回路図であり、実質的に読み出し回路RKの構成を示している。一対のNMOSトランジスタの一方のゲートと、一対のPMOSトランジスタの一方のゲートに共通して論理Aを、一対のNMOSトランジスタの他方のゲートに論理Bを、一対のPMOSトランジスタの他方のゲートに論理Bバー(Bと相補的な論理であって、図中Bに上線を付加して示す:他の論理についても以下同様)を、それぞれ与える。論理Bが“L”であれば出力される論理Zはトライステートインバータによって決定はされない(tristate condition)。しかし、論理Bが“H”であれば、論理Aを反転した論理Zが出力される。

【0057】

図2に戻り、パストランジスタMN9,MN10は書き込みビット線41上のノードN4と、ストレージセルSCのノードN1との間に直列に接続され、書き込み制御線44及び書き込みワード線31の双方が“H”の場合に、書き込みビット線41の論理をノードN1へと伝達するスイッチとして機能する。より詳細には、パストランジスタMN9の電流電極対(ソースドレインの対)の一方はノードN1に接続され、パストランジスタMN10の電流電極対の一方はノードN4に接続され、パストランジスタMN9,MN10の電流電極対の他方同士は共通に接続される。そしてパストランジスタMN9のゲートはノードN6において書き込み制御線44に、パストランジスタMN10のゲートはノードN4において書き込みビット線41に、それぞれ接続される。

【0058】

同様にして、パストランジスタMN11,MN12は書き込み補ビット線42上のノードN5と、ストレージセルSCのノードN2との間に直列に接続され、書き込み制御線44及び書き込みワード線31の双方が“H”の場合に、書き込み補ビット線42の論理をノードN2へと伝達するスイッチとして機能する。より詳細には、パストランジスタMN11の電流電極対の一方はノードN2に接続され、パストランジスタMN12の電流電極対の一方はノードN5に接続され、パストランジスタMN11,MN12の電流電極対の他方同士は共通に接続される。そしてパストランジスタMN11のゲートはノードN6において書き込み制御線44に、パストランジスタMN12のゲートはノードN4において書き込みビット線41に、それぞれ接続される。

【0059】

パストランジスタMN10,MN12は、図53に示されたトランジスタQN10,QN12と類似してその動作が書き込みワード線31における論理に依存するが、それらのソースが電位点VSSに接続されるのではなく、それぞれ書き込みビット線41、書き込み補ビット線42に接続される点で異なっている。またパストランジスタMN9,MN11は、図53に示されたトランジスタQN9,QN11と類似して、パストランジスタMN10とノードN1の間、トランジスタMN12とノードN2との間に、それぞれ介在するが、いずれも導通が書き込み制御線44における論理に依存する点で異なっている。

【0060】

このような構成のメモリセルに対する書き込み動作は以下のようになる。選択された書き込みワード線31は“H”となってパストランジスタMN10,MN12がオンする。そして書き込みビット対線を構成する書き込みビット線41、書き込み補ビット線42はいずれか一方が“H”となり、他方が“L”となる。これに対応して書き込み制御線44は“H”となるので、パストランジスタMN9,MN11はオンになる。

【0061】

従って、ストレージセルSCのノードN1はパストランジスタMN9,MN10を介してノードN4において書き込みビット線41と、ノードN2はパストランジスタMN11,MN12を介してノードN5において書き込み補ビット線42と、それぞれ接続される。書き込みビット線41、書き込み補ビット線42に設定された論理が、それぞれN1,N2へと書き込まれるので、図53に示された回路と比較すると、ストレージセルSCに記憶されたデータを反転するのに必要な時間は短い。

【0062】

電位の大きさについて考察するため、パストランジスタMN9,MN10のしきい値電圧を電位Vthnとし、書き込み制御線44、書き込みワード線31及び書き込みビット線41には“H”として電位VDDが与えられたとする。ノードN4とノードN1の間にはパストランジスタMN9,MN10が介在するので、これら2つのトランジスタのの基板効果により、ノードN1には電位(VDD−2Vthn)が印加されることになる。

【0063】

電位差(VDD−VSS)が1V以下になると、ストレージセルSCのインバータL1,L2が電位(VDD−2Vthn)を“H”ではなく“L”と認識してしまう可能性もある。これを防止すべく、書き込みワード線31に対して“H”として印加される電位を、電位VDDよりも高い、例えば電位(VDD+2Vthn)に設定してもよい。また、書き込みワード線31及び書き込み制御線44に対して“H”として印加される電位を、いずれも電位(VDD+Vthn)に設定しても同様の効果が得られる。

【0064】

さて、選択された書き込みワード線31に対応する行に配置され、選択されていない書き込みビット線対に対応する列に配置されたメモリセルMCの動作について説明する。かかるメモリセルMCにおいて、書き込みビット線41、書き込み補ビット線42はプリチャージによって共に“H”あるいは“L”に設定されている。これに対応して書き込み制御線44は“L”に設定される。換言すれば、書き込み制御線44は選択されていない列において“L”となる。従って書き込みワード線31が“H”であってトランジスタMN10,MN12がオンしていても、トランジスタMN9,MN11はオフしており、ストレージセルSCが書き込みビット線41、書き込み補ビット線42の電位に影響を与えることはない。よって記憶内容を反転する書き込みを迅速に行いつつ、不要な電力の消費を低減することができる。

【0065】

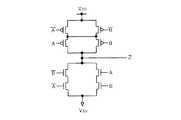

図4乃至図9は論理A,Bから、両者の排他的論理和を論理Zとして得るXOR回路を例示する回路図である。書き込み制御線44に対して、書き込みビット線41に与えられた論理と書き込み補ビット線42に与えられた論理の排他的論理和を得るため、これらのXOR回路を採用することができる。図1ではXOR回路がビット線デコーダ4に内蔵された態様を示しているが、XOR回路をビット線デコーダ4とは別個に設ける態様をとってもよい。

【0066】

例えば、図7に示されたXOR回路の動作について説明する。論理Aが“H”のとき、PMOSトランジスタTP1とNMOSトランジスタTN1とで構成されたインバータはノードJ1に論理“L”を与える。一方、ノードJ2には論理A、即ち“H”が与えられる。PMOSトランジスタTP2とNMOSトランジスタTN2はノードJ2,J1の間に直列に接続されており、両者はインバータとして機能する。このインバータは論理Bを入力し、ノードJ3に論理Zとして論理Bバーを出力する。この際、PMOSトランジスタTP3とNMOSトランジスタTN3が構成するトランスミッションゲートはオフしているので、ノードJ3において論理Bと論理Bバーとの衝突は生じない。

【0067】

論理Aが“L”のとき、ノードJ1,J2はそれぞれ“H”,“L”となる。よってトランジスタTP3,TN3の両方がオンして、論理Bが論理ZとしてノードJ3に与えられる。一方、論理Bが“H”の場合にはNMOSトランジスタTN2によってノードJ1における論理“H”がノードJ3へと伝達され、論理Bが“L”の場合にはPMOSトランジスタTP2によってノードJ2における論理“L”がノードJ3へと伝達される。よっていずれにしてもノードJ3において論理Bが論理Zとして与えられる。

【0068】

以上の動作から、図7の回路は論理A,BのXORを与える。排他的論理和と相補的な値(XNOR:exclusive NOR)を得るためには、出力を更に反転してもよいし、論理A,論理Bのいずれか一方のみを反転して、XORを得るための回路に入力してもよい。

【0069】

図10は本実施の形態の変形を示す回路図である。図2に示された構成と比較すると、書き込み制御線44の論理によってスイッチングが制御されるトランジスタMN9と、書き込みワード線31の論理によってスイッチングが制御されるトランジスタMN10とが、ノードN1,N4の間で直列に接続されている点で共通し、その位置が入れ替わっている点が異なっている。同様にして、トランジスタMN11,MN12も図2に示された構成と比較すると、ノードN2,N5の間での位置が入れ替わっている。このような構成でも図2に示された構成と同様の効果を得ることができるのは当然である。

【0070】

図11はパストランジスタMN9,MN10,MN11,MN12の構成を例示する模式図である。ストレージセルSCは簡単のため、インバータL1,L2をそれぞれ記号で示している一方、パストランジスタMN9,MN10,MN11,MN12は書き込みビット線41、書き込み補ビット線42、書き込み制御線44、書き込みワード線31と共にその構成が平面図で示されている。図中、丸括弧内に記載された符号は図10で示された構成に対応し、その左側に記載された符号は図2で示された構成に対応している。

【0071】

図11を図2で示された構成に則して説明する。パストランジスタMN9,MN10は活性領域R1において形成される。パストランジスタMN9の電流電極対の一方はノードN1に接続され、パストランジスタMN10の電流電極対の一方は書き込みビット線41に接続される。パストランジスタMN9,MN10はその電流電極対の他方同士がソースドレイン領域SD1を共有する。同様にしてパストランジスタMN11,MN12は活性領域R2において形成される。パストランジスタMN11の電流電極対の一方はノードN2に接続され、パストランジスタMN12の電流電極対の一方は書き込み補ビット線42に接続される。パストランジスタMN11,MN12はその電流電極対の他方同士がソースドレイン領域SD2を共有する。

【0072】

そしてパストランジスタMN9,MN11のゲートとして機能するゲート配線G1と、パストランジスタMN10,MN12のゲートとして機能するゲート配線G2とが、いずれも図示されないゲート絶縁膜を介して、活性領域R1,R2の上方(紙面手前側)に敷設される。書き込み制御線44と書き込みワード線31は、ゲート配線G1,G2よりも上方に敷設される。書き込み制御線44と書き込みワード線31は、それぞれゲート配線G1,G2とビアコンタクトV1,V2を介して接続される。

【0073】

以上のようにしてパストランジスタMN9,MN10はソースドレイン領域SD1を共有し、パストランジスタMN11,MN12はソースドレイン領域SD2を共有するので、小さな面積でこれらを配置することができる。

【0074】

なお、書き込みビット線41jと書き込み補ビット線42jにはプリチャージの期間において電位(VDD+VSS)/2が印加されてもよい。この場合、XOR回路の前段に、書き込みビット線41jと書き込み補ビット線42jのそれぞれの電位を非反転増幅する回路を設けておけばよい。例えばVSS=0Vとし、XOR回路の入力マージンが大きくて電位2VDDの入力を許せば、当該増幅回路の増幅率を2倍に設定しておけばよい。これにより、プリチャージの電位がVDD/2であってもVDDであっても、XOR回路の一対の入力はいずれも“H”となる。またプリチャージの電位がVSSであればXOR回路の一対の入力はいずれも“L”となる。従って本実施の形態の効果を享受することができる。

【0075】

実施の形態2.

図12はこの発明の実施の形態2にかかるSRAMのメモリセルアレイ周辺の構成を示す概念図である。実施の形態1で示されたSRAMの構成に対して、ビット線群40jに書き込み補制御線45jが追加され、ワード線群30iに書き込み補ワード線34iが追加されたことが特徴的な構造となっている。

【0076】

書き込み補制御線45j、書き込み補ワード線34iは、それぞれビット線デコーダ4及びワード線デコーダ3によってその電位(あるいは論理)が設定される。具体的には書き込み補制御線45j、書き込み補ワード線34iは、それぞれ書き込み制御線44j、書き込みワード線31iと相補的な論理が与えられる。

【0077】

図13は、図12に示されたメモリセルMCの一つの構成を例示する回路図である。従来の技術と同様に、行の位置及び列の位置を示す添字は省略している。メモリセルMCは、図2で示された構成と比較して、いずれもPMOSトランジスタであるパストランジスタMP9,MP10,MP11,MP12が追加して設けられ、また書き込み補制御線45、書き込み補ワード線34が追加して敷設されている。

【0078】

パストランジスタMP9,MP10,MP11,MP12はそれぞれパストランジスタMN9,MN10,MN11,MN12と並列に接続されている。そしてパストランジスタMP9,MP10,MP11,MP12のゲートに与えられる論理は、パストランジスタMN9,MN10,MN11,MN12のゲートに与えられる論理と、それぞれ相補的である。つまりパストランジスタMP9,MP11のゲートはノードN7において書き込み補制御線45に接続され、パストランジスタMP10,MP12のゲートは書き込み補ワード線34に接続されている。

【0079】

従って、パストランジスタMP9,MP10,MP11,MP12はそれぞれパストランジスタMN9,MN10,MN11,MN12と共にトランスミッションゲートを構成している。従って、図2で示された構成と比較して、ノードN1に書き込みビット線41から論理“H”を伝達する際(あるいはノードN2に書き込み補ビット線42から論理“H”を伝達する際)、基板効果によるしきい値Vthn分の低下は生じない。よって書き込みワード線31に与える電位を昇圧させる昇圧回路は不用となる利点がある。

【0080】

図14は本実施の形態の変形を示す回路図であり、実施の形態1に即していえば図10に相当する。即ち図14に示された構成は、図13に示された構成と比較して、パストランジスタMN9,MP9が構成するトランスミッションゲートとパストランジスタMN10,MP10が構成するトランスミッションゲートとの位置が、ノードN1,N4の間で入れ替わっており、パストランジスタMN11,MP11が構成するトランスミッションゲートとパストランジスタMN12,MP12が構成するトランスミッションゲートとの位置が、ノードN2,N5の間で入れ替わっている。このような構成でも本実施の形態の効果を得ることができるのは当然である。

【0081】

もちろん、パストランジスタMN9,MN10と同様にして、パストランジスタMP9,MP10もソースドレイン領域を共有して必要な面積を節約することができる。パストランジスタMP11,MP12についても同様である。

【0082】

なお、トランスミッションゲートでアクセストランジスタを代替しても、基板効果によるしきい値Vthn分の低下を回避できる。図15は図52に示された回路に対して書き込み補ワード線34を追加し、アクセストランジスタQN3をPMOSトランジスタMP10とNMOSトランジスタMN10が構成するトランスミッションゲートに置換し、アクセストランジスタQN4をPMOSトランジスタMP12とNMOSトランジスタMN12が構成するトランスミッションゲートに置換した構成を示している。

【0083】

図14に示された構成と同様に、トランジスタMN10,MN12は書き込みワード線31の論理によって、トランジスタMP10,MP12は書き込み補ワード線34の論理によって、それぞれ導通が制御されるので、基板効果によるしきい値Vthnの低下を回避できる。従って書き込みワード線31に与える電位を昇圧する必要はない。また、図13や図14に示された構成と比較して、トランスミッションゲートが一つずつ減った分、ストレージセルSCにアクセスする時間が短くなり、かつ、エリアペナルティも小さく、しかも書き込み制御線44を、ひいてはXOR回路を設ける必要もないことが利点である。しかしながら、本実施の形態とは異なり、選択されていない列のメモリセルMCにおいて、ストレージセルSCと書き込みビット線対との間での電位の衝突を回避する機能は劣っている。

【0084】

実施の形態3.

図16は本実施の形態にかかるメモリセルMCの一つの構成を例示する回路図である。従来の技術と同様に、行の位置及び列の位置を示す添字は省略しているが、図1で示されたMCijの各々として採用することができる。

【0085】

メモリセルMCは、図52で示された構成と比較して、アクセストランジスタQN3,QN4の代わりに、いずれもNMOSトランジスタであるアクセストランジスタMN2,MN4及び制御トランジスタMN1,MN3が設けられている。

【0086】

アクセストランジスタMN2はアクセストランジスタQN3と同様に、ノードN1とノードN4の間の導通を制御する。そしてそのゲートには書き込みワード線31が接続される点でアクセストランジスタQN3と共通するが、制御トランジスタMN1が介在する点で相違する。アクセストランジスタMN4もノードN2とノードN5の間の導通を制御し、そのゲートには書き込みワード線31が接続される点でアクセストランジスタQN4と共通するが、制御トランジスタMN3が介在する点で相違する。

【0087】

制御トランジスタMN1,MN3のゲートはノードN6を介して書き込み制御線44に接続されているので、実施の形態1と同様に、ノードN1とノードN4の間及びノードN2とノードN5の間の導通は、いずれも書き込みワード線31及び書き込み制御線44の両方が“H”である場合に限られる。従って、実施の形態1と同様にして記憶内容を反転する書き込みを迅速に行いつつ、不要な電力の消費を低減することができる。

【0088】

上述の構成では、制御トランジスタMN1とアクセストランジスタMN2とが、あるいは制御トランジスタMN3とアクセストランジスタMN4とが、ソースドレインを共有できない点で実施の形態1に示された構成と比較して不利である。

【0089】

しかし制御トランジスタMN1,MN3はいずれも書き込み制御線44における論理に依存して導通し、かつそれらの導通によってアクセストランジスタMN2,MN4のゲートへと書き込みワード線31における論理を伝達する。そこで図17に示すように、制御トランジスタMN3をMN1にマージした変形も可能であり、必要な面積の縮小が可能である。

【0090】

実施の形態4.

図18は本実施の形態にかかるメモリセルMCの一つの構成を例示する回路図である。従来の技術と同様に、行の位置及び列の位置を示す添字は省略しているが、図1で示されたMCijの各々として採用することができる。メモリセルMCは、図16で示された構成と比較して、制御トランジスタMN1,MN3が制御トランジスタMN5,MN6に置換されている。

【0091】

制御トランジスタMN5,MN6のゲートは共通して書き込みワード線31に接続されている。また制御トランジスタMN5は書き込みビット線41とアクセストランジスタMN2のゲートとの間に介在し、制御トランジスタMN6は書き込み補ビット線42とアクセストランジスタMN4のゲートとの間に介在している。従って実施の形態1と同様に、ノードN1とノードN4の間及びノードN2とノードN5の間の導通は、いずれも書き込みワード線31及び書き込み制御線44の両方が“H”である場合に限られる。従って、実施の形態1と同様にして記憶内容を反転する書き込みを迅速に行いつつ、不要な電力の消費を低減することができる。

【0092】

上述の構成では、制御トランジスタMN5とアクセストランジスタMN2とが、あるいは制御トランジスタMN6とアクセストランジスタMN4とが、ソースドレインを共有できない点で実施の形態1に示された構成と比較して不利である。

【0093】

しかし制御トランジスタMN5,MN6はいずれも書き込みワード線31における論理に依存して導通し、かつそれらの導通によってアクセストランジスタMN2,MN4のゲートへと書き込み制御線44における論理を伝達する。そこで図19に示すように、制御トランジスタMN6をMN5にマージした変形も可能であり、必要な面積の縮小が可能である。

【0094】

実施の形態5.

図20は本実施の形態にかかるメモリセルMCの一つの構成を例示する回路図である。従来の技術と同様に、行の位置及び列の位置を示す添字は省略しているが、図12で示されたMCijの各々として採用することができる。但し書き込み補制御線45は不要である。メモリセルMCは、図53に示された構成と比較して、主として2点異なっている。

【0095】

第1の相違点として、トランジスタQN9は直接にはノードN1には接続されず、両者の間にパストランジスタMN9が介在している。同様にしてトランジスタQN11は直接にはノードN2には接続されず、両者の間にパストランジスタMN11が介在している。そして実施の形態1と同様にパストランジスタMN9,MN11のゲートはノードN6において書き込み制御線44に接続されている。トランジスタQN9,MN9の接続点をノードN8として、トランジスタQN11,MN11の接続点をノードN9として、それぞれ表している。

【0096】

第2の相違点として、電位VDDを与える電位点(以下「電位点VDD」とも称す)とノードN8との間にいずれもPMOSトランジスタであるトランジスタMP3,MP4が直列に接続されている。同様にして電位点VDDとノードN9との間にいずれもPMOSトランジスタであるトランジスタMP5,MP6が直列に接続されている。トランジスタMP4、MP6のいずれにおいても、電流電極対の一方には電位VDDが印加され、そのゲートには書き込み補ワード線34が接続されている。そしてトランジスタMP3,MP5の電流電極対の一方にはそれぞれノードN8,N9が接続される。トランジスタMP3,MP4の電流電極対の他方同士、トランジスタMP5,MP6の電流電極対の他方同士は、それぞれ共通に接続される。トランジスタMP3,MP5のゲートはそれぞれ書き込みビット線41、書き込み補ビット線42に接続されている。

【0097】

以上のような構成では、ストレージセルSCの外部からノードN1を“H”へと設定し得るトランジスタMP3,MP4が、ノードN2を“H”へと設定し得るトランジスタMP5,MP6が設けられたので、記憶内容を反転する書き込みを迅速に行うことができる。しかもノードN1,N8の間の導通及びノードN2,N9の間の導通が、それぞれパストランジスタMN9,MN10によって、いずれも書き込み制御線44の論理に依存する。よってノードN1と書き込みビット線41、ノードN2と書き込み補ビット線42との間における電位の衝突に起因した、不要な電力の消費を低減することができる。

【0098】

トランジスタMP3,MP4,QN9,QN10及びトランジスタMP5,MP6,QN11,QN12は、それぞれノードN8,N9を出力端とするトライステートインバータを構成している。本実施の形態にかかるメモリセルMCの動作を、これらのトライステートインバータの動作という観点で以下に説明する。

【0099】

これらのトライステートインバータは、書き込みワード線31が“H”、従って書き込み補ワード線34が“L”の場合にのみインバータとして機能する。つまり書き込みビット線41の論理と相補的な論理がノードN8に与えられ、書き込み補ビット線42の論理と相補的な論理がノードN9に与えられる。そして書き込みワード線31が“L”、従って書き込み補ワード線34が“H”の場合には、たとえトランジスタMP3,QN9がオンしても、ノードN8の電位はトライステートインバータによっては設定されない(tristate condition)。またたとえトランジスタMP5,QN11がオンしても、ノードN9の電位はトライステートインバータによっては設定されない。

【0100】

書き込み対象となったメモリセルMCの属する行のワード線群30、つまり選択されたワード線群30では、書き込みワード線31、書き込み補ワード線34にそれぞれ“H”,“L”の電位が与えられ、ノードN8,N9にはそれぞれ書き込みビット線41、書き込み補ビット線42と相補的な論理が与えられる。また、書き込み対象となったメモリセルMCの属する列のビット線群40、つまり選択されたビット線群40では、書き込みビット線41、書き込み補ビット線42には互いに相補的な論理が与えられるので、書き込み制御線44における論理は“H”となってパストランジスタMN9,MN11が導通する。従って、ノードN1,N2にはそれぞれ書き込みビット線41、書き込み補ビット線42と相補的な論理が、たとえストレージセルSCの記憶内容を反転する場合であっても、迅速に記憶される。

【0101】

選択されたワード線群30に対応する行に配置されたメモリセルMCでは、トライステートインバータがインバータとして機能している。しかし、選択されないビット線群40に対応する列に配置されたメモリセルMCでは、書き込みビット線41、書き込み補ビット線42が互いにほぼ等しい電位にプリチャージされるので、書き込み制御線44における論理は“L”であって、パストランジスタMN9,MN11は導通しない。よってノードN1と書き込みビット線41、ノードN2と書き込み補ビット線42との間は遮断され、電位の衝突に起因した、不要な電力の消費を低減することができる。

【0102】

基板効果によるパストランジスタMN9,MN10のしきい値分の電圧低下を避けるため、これらをトランスミッションゲートに置換してもよい。あるいはパストランジスタMN9,MN10の基板効果を補償すべく、書き込みワード線31の電位をしきい値分だけ昇圧してもよい。

【0103】

図21は本実施の形態の第1の変形にかかるメモリセルMCの構成を示す回路図である。図20に示された構成に対し、トランジスタQN9,QN10の直列接続の順序を入れ替え、トランジスタQN11,QN12の直列接続の順序を入れ替えた構成を有している。かかる変形においても本実施の形態の効果を得ることができるのは当然である。

【0104】

図22は本実施の形態の第2の変形にかかるメモリセルMCの構成を示す回路図である。図21に示された構成に対し、ストレージセルSCへ論理“H”を供給するトランジスタMP3,MP4,MP5,MP6が削除されている。更に、パストランジスタMN9とトランジスタQN10との直列接続の順序と、パストランジスタMN11とトランジスタQN12との直列接続の順序が、それぞれ入れ替えられている。

【0105】

あるいは図53に示された回路と比較すれば、トランジスタQN9,QN10の、ノードN1と電位点VSSとの間での直列接続の順序を入れ替え、かつトランジスタQN9,QN10の間に、書き込み制御線44における論理によって導通が制御されるパストランジスタMN9が介在している。同様にしてトランジスタQN11,QN12の、ノードN2と電位点VSSとの間での直列接続の順序を入れ替え、かつトランジスタQN11,QN12の間に、書き込み制御線44における論理によって導通が制御されるパストランジスタMN11が介在している。

【0106】

このような構成では、ストレージセルSCに対して外部から“H”を設定することはできない。従ってストレージセルSCの記憶する内容を反転する書き込みを迅速に行えない点で不利である。しかし、図20や図21に示された構成と比較して、書き込み補ワード線34を必要とせず、図1に示されたSRAMのメモリセルMCとして採用できるという利点がある。また図53に示された構成と比較して、選択されないビット線群40の書き込みビット線41、書き込み補ビット線42の電位を“L”、“H”のいずれにプリチャージしてもよい点で有利でもある。

【0107】

もちろん、トランジスタQN10,MN9,QN9の直列接続の順序は6通りあって、そのいずれの順序を採用しても上述の効果が得られることは当然である。トランジスタQN12,MN11,QN11の直列接続の順序についても同様である。

【0108】

図23は本実施の形態の第3の変形にかかるデュアル書き込みポート型のスタティックメモリセルの回路図である。ここではワード線群(読み出し補ワード線32、読み出しワード線33を除く)及びビット線群(読み出しビット線43を除く)並びにビット線群に対応するトライステートインバータは、2組設けられている。第1の組及び第2の組には、それぞれ図21に採用された符号に対して、末尾に記号a,bを付加して得られる符号が採用されている。

【0109】

このようなデュアル書き込みポート型のスタティックメモリセルにおいても、ストレージセルSCの記憶内容を反転する場合に迅速に記憶し、電位の衝突に起因した不要な電力の消費を低減できることは当然である。

【0110】

図24は本実施の形態の第4の変形にかかるメモリセルMCの構成を示す回路図である。図21に示された構成に対し、トライステートインバータの出力端となるノードN8とトランジスタMP3,QN9及びノードN1との間に介在する素子の構成、他のトライステートインバータの出力端となるノードN9とトランジスタMP5,QN11及びノードN2との間に介在する素子の構成が変更されている。

【0111】

ノードN8はPMOSトランジスタMP9を介してトランジスタMP3に、NMOSトランジスタMN9を介してトランジスタQN9に、NMOSトランジスタQN10を介してノードN1に、それぞれ接続されている。ノードN9はPMOSトランジスタMP11を介してトランジスタMP5に、NMOSトランジスタMN11を介してトランジスタQN11に、NMOSトランジスタQN12を介してノードN2に、それぞれ接続されている。

【0112】

この変形では書き込み補ワード線34は採用されず、代わりに書き込み補制御線45が採用されている。そしてトランジスタMP9,MP11のゲートはノードN7において書き込み補制御線45に、トランジスタMN9,MN11のゲートはノードN6において書き込み制御線44に、それぞれ接続されている。また、トランジスタQN10,QN12のゲートは書き込みワード線31に接続されている。

【0113】

選択された行において書き込みワード線31は活性化し、トランジスタQN10,QN12がオンする。よってノードN1,N2はそれぞれノードN8,N9と導通する。そして選択された列において書き込み制御線44、書き込み補制御線45はそれぞれ“H”、“L”となるので、トランジスタMP9,MP11,MN9,MN11はいずれもオンする。よって書き込み対象となったメモリセルMCのノードN1,N2には、それぞれノードN8,N9を介して、書き込みビット線41に与えられた論理、書き込み補ビット線42に与えられた論理のそれぞれを反転して、書き込まれるべきデータが与えられる。これはストレージセルSCの記憶するデータを反転する場合であっても迅速に行われる。

【0114】

選択された行には配置されるものの、書き込み対象となっていないメモリセルMC(即ち選択されない列に配置されたメモリセルMC)では書き込み制御線44、書き込み補制御線45はそれぞれ“L”、“H”となるので、トランジスタMP9,MP11,MN9,MN11はいずれもオフする。ノードN8,N9はtristate conditionとなる。従ってノードN1,N2にはストレージセルSCの外部から論理が強制的に設定されることがなく、電位の衝突に起因する不要な電力の消費が防止できる。

【0115】

図25は本実施の形態の第5の変形にかかるメモリセルMCの構成を示す回路図である。この構成は、図24の構成に対して、ノードN8と電位点VDDとの間でのトランジスタMP3,MP9の直列接続の順序を交換し、ノードN8と電位点VSSとの間でのトランジスタMN9,QN9の直列接続の順序を交換し、ノードN9と電位点VDDとの間でのトランジスタMP5,MP11の直列接続の順序を交換し、ノードN9と電位点VSSとの間でのトランジスタMN11,QN11の直列接続の順序を交換した構成を有している。従って、図25に示された構成でも、迅速にデータを書き込み、かつ不要な電力消費を低減する効果がある。

【0116】

図26は本実施の形態の第6の変形にかかるメモリセルMCの構成を示す回路図である。図21に示された構成に対して、ノードN8と電位点VDDとの間でのトランジスタMP3,MP4の直列接続の順序を交換し、ノードN9と電位点VDDとの間でのトランジスタMP5,MP6の直列接続の順序を交換し、更にトランジスタMP4,MP6をマージして一つのトランジスタとして設けている。同様に、ノードN8と電位点VSSとの間でのトランジスタQN9,QN10の直列接続の順序を交換し、ノードN9と電位点VSSとの間でのトランジスタQN11,QN12の直列接続の順序を交換し、更にトランジスタQN10,QN2をマージして一つのトランジスタとして設けている。よって図21に示された回路と比較して、トランジスタの数を低減し、本実施の形態の効果を得るために必要な面積を小さくすることができる。

【0117】

ノードN8,N9は、図53に示されたノードN1,N2と同様の接続関係で電位点VSSに接続されている。しかし、ノードN8とノードN1との間、及びノードN9とノードN2との間は、それぞれトランジスタMN9,MN11によって、いずれも書き込み制御線44が“H”のときのみ導通する。これは選択されないビット線群40の書き込みビット線41、書き込み補ビット線42の電位を“L”、“H”のいずれにプリチャージした場合でも当てはまる。よって図21と同じ効果を得ることができる。

【0118】

図27は第I行のメモリセルMC i1 〜MC in において図26に示された構成を応用した構成を示す回路図である。同じ行に属する複数のメモリセルMC ij は、書き込みワード線31、書き込み補ワード線34を共通に使用する。従ってn個のメモリセルMC i1 〜MC in について、トランジスタMP4(あるいはトランジスタMP6)及びトランジスタQN10(あるいはQN12)は、それぞれ一つのPMOSトランジスタMP400及びNMOSトランジスタQN100へとマージすることができる。このようなマージにより、トランジスタ数を一層低減することができる。

【0119】

実施の形態6.

本実施の形態は、回路図に現れる構成は実施の形態1乃至実施の形態5と同様である。本実施の形態において特徴的な点は、メモリセルMCを構成するMOSFETがSOI(Semiconductor On Insulator or Silicon On Insulator)基板上に形成される点である。

【0120】

まず従来のメモリセルMCを構成するMOSFETが、SOI基板上に形成された場合の問題点を説明する。図28は、図52に示されたアクセストランジスタQN4をSOI基板上にMOSトランジスタとして形成した場合の構成を例示する断面図である。

【0121】

半導体基板91、埋め込み酸化膜92、SOI基板93がこの順に積層されている。SOI基板93には選択的に絶縁分離体94が埋め込まれている。SOI基板93はノードN2,N5にそれぞれ接続され、いずれもn型であるドレイン93a、ソース93bと、ドレイン93a及びソース93bに挟まれ、P型のチャネル領域93cとに区分されている。ソース93bとチャネル領域93cとの間にはpn接合J11が、ドレイン93aとチャネル領域93cとの間にはpn接合J12が、それぞれ形成される。ゲート電極98はゲート絶縁膜95を介してチャネル領域93cと対峙して設けられ、その頂面及び側面は絶縁膜96で覆われている。サイドウォール97は絶縁膜96を介してゲート電極98の側面に対峙して設けられている。ゲート電極98はゲート絶縁膜95に近い方から順に、ドープされたポリシリコン98a、タングステン窒化膜98b、タングステン98cが積層して構成されている。かかる構成では、絶縁分離体94がSOI基板93を周囲から絶縁するので、チャネル領域93cの電位を固定する機構が別途に設けられない限り、通常はいわゆるfloating bodyの状態にある。

【0122】

図52に示された構造のメモリセルMCであって、いずれも第j番目の列に属する2つのメモリセルMCxj,MCyjを想定する。メモリセルMCxjのノードN1,N2にそれぞれ“L”、“H”が書き込まれた後に、メモリセルMCyjのノードN1,N2にそれぞれ“H”、“L”を書き込む動作を行う場合の、いわゆるhalf-select write disturbを考察する。

【0123】

メモリセルMCxjの書き込み動作終了後では書き込みワード線31xは“L”であり、メモリセルMCyjへの書き込み動作においても書き込みワード線31xは“L”のままであるので、当該アクセストランジスタQN4ではソース93bとチャネル領域93cとドレイン93aとが横型の寄生バイポーラトランジスタを構成し、それぞれエミッタ/ベース/コレクタとして機能する。

【0124】

メモリセルMCxjの書き込み動作終了後、書き込みビット線41j、書き込み補ビット線42jはいずれも“H”にプリチャージされるので、メモリセルMCxjのアクセストランジスタQN4はオンしないままで、そのソース93bとドレイン93aとが“H”である状態が保たれる。そしてチャネル領域93cはP型でフローティングの状態であるので、ここには正孔(図中+印で模式的に表示)が熱的に蓄積される。

【0125】

このような状態において、メモリセルMCyjへの書き込み動作のために書き込みビット線41jに“H”が、書き込み補ビット線42jに“L”が、それぞれプリチャージされると、メモリセルMCxjのアクセストランジスタQN4のpn接合J11は順バイアスになる。よってソース93bからチャネル領域93cへと電子が注入され、チャネル領域93cに蓄積された正孔は放電される。この際にpn接合J11を流れる電流I1は、上述の寄生バイポーラトランジスタの実効ベース電流として機能する。そのため、ドレイン93aからチャネル領域93cへと流れるスパイク状の電流I2を誘起する。特にメモリセルMCyjへの書き込みまでの時間が長いと、熱的に蓄積される正孔の量も多くなって電流I2も大きい。その場合には、ノードN2に蓄積されている電荷を放電してその電位を“H”から“L”へと下げ、メモリセルMCxjの記憶内容を反転させる場合がある。

【0126】

しかし、本発明の回路構成を採用する場合には、上記問題を回避することができる。例えば図2に示された構成では、トランジスタMN11,MN12を介して書き込み補ビット線42の論理がノードN2に書き込まれる。一般的にはトランジスタMN11,MN12を相互に接続する配線は、書き込み補ビット線42と比較して非常に短い。よって図52に示された構造のメモリセルMCのアクセストランジスタQN4と比較すると、トランジスタMN11では、電流電極対のうち書き込み補ビット線42に近い方(例えばソース)に接続される寄生容量が小さい。図11で示された様に不純物領域を共有する場合はなおさらである。従ってトランジスタMN11が図28に示されたSOIFETであっても、寄生バイポーラトランジスタは十分に動作しない。よって本実施の形態の回路構成を採用することにより、half-select write disturbの発生確率を小さくすることができる。

【0127】

なお、非選択の書き込みワード線31における論理“L”に相当する電位を、書き込み補ビット線42における論理“L”に相当する電位よりも低く、例えばVSS−0.3Vb〜VSS−Vb程度にすることも望ましい。ここでVbはドレイン93a及びチャネル領域93cが形成するビルトイン電圧である。このような電位を非選択の書き込みワード線31に与えることにより、チャネル領域93cでアキュムレーションを回避しつつ、pn接合J11での順バイアスを軽減できる。このような書き込みワード線31の電位の設定は、特に図16に示された回路構成において有効である。トランジスタMN4の電流電極対はノードN2,N5に接続されており、寄生容量の観点からも図52に示されたトランジスタQN4と同様だからである。

【0128】

もちろん、チャネル領域93cの電位を固定した構成を採って、上記half-select write disturbを回避してもよい。

【0129】

上述した実施の形態ではデュアルポートスタティックメモリセルを例にとって説明したが、マルチポートスタティックメモリセルへに応用できることはいうまでもない。

【0130】

実施の形態7.

実施の形態1乃至実施の形態6では書き込みワード線31のみならず書き込み制御線44の活性化によって書き込み動作を許可することにより、所定の効果を得ていた。しかし、書き込み制御線44の論理を決定するには、電位VSS,VDD、あるいは電位(VDD+VSS)/2であっても、プリチャージによって書き込みビット線41、書き込み補ビット線42の電位を決定しておく必要がある。換言すれば、書き込みビット線41、書き込み補ビット線42がフローティングの状態にあることを許せば、書き込み制御線44の電位は決定されない懸念もある。また書き込みビット線41、書き込み補ビット線42がフローティングの状態にある場合にも、書き込み動作の対象となるメモリセルと同じ行に属し、かつ異なる列に属するメモリセルにおいて、書き込みビット線41、書き込み補ビット線42をストレージセルSCが充放電することによる電力消費が生じる可能性もある。

【0131】

特にマルチポートSRAM、例えばデュアルポートSRAMのように、各セルに複数の読み書きのパスを有し、バイナリ情報の読み書きが独立に、かつ、非同期に行うことができる場合には、ストレージセルSCが書き込みビット線41及び書き込み補ビット線42のみならず、読み出しビット線43をも併行してドライブする場合も生じる。

【0132】

図54は、いずれか一方が書き込みポートとなり、他方が読み出しポートとなる第1及び第2のポートを有しているデュアルポートSRAM80と、その動作を制御する装置との接続を示すブロック図である。第1のマイクロプロセッサ81は第1のリード/ライト制御回路82を介して、デュアルポートSRAM80の第1ポートを使用した読み書き動作を行う。一方、第2のマイクロプロセッサ84は第2のリード/ライト制御回路83を介して、デュアルポートSRAM80の第2ポートを使用した読み書き動作を行う。

【0133】

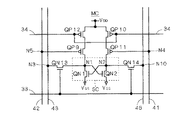

図29はデュアルポートSRAM80に採用され得るメモリセルMCの構成を例示する回路図である。図52に示された構成と比較して、読み出し回路RKの代わりにいずれもNMOSトランジスタであるアクセストランジスタQN13,QN14が設けられている。アクセストランジスタQN13はノードN1と読み出しビット線43との間に介在し、そのゲートは読み出しワード線33に接続されている。アクセストランジスタQN14はノードN2と読み出し補ビット線46との間に介在し、そのゲートは読み出しワード線33に接続されている。

【0134】

図29に示された構成は、図52に示された構成と比較して、メモリセルMC一つあたりのトランジスタ数が2つ低減できる利点を有する。しかしストレージセルSCは、トランジスタQN13,QN14がオンした際に、読み出し回路RKのトランジスタQP3,QN6のゲートよりも大きな静電容量を有する読み出しビット線43、読み出し補ビット線46をそれぞれノードN3,N10において充放電することになる。そのため、いずれも第i行に配置されたメモリセルMCix,MCiy(x≠y)に対し、それぞれ第1のリード/ライト制御回路82による書き込み動作と、第2のリード/ライト制御回路83による読み出し動作とが併行して行われた場合、書き込みワード線31i、読み出しワード線33iが同時に“H”となる期間がある。この期間では、メモリセルMCiyのストレージセルSCは読み出しビット線43、読み出し補ビット線46のみならず書き込みビット線41、書き込み補ビット線42をもドライブすることになり、読み出し動作が遅くなるという可能性がある。

【0135】

図30はこの発明の実施の形態7にかかるSRAMのメモリセルアレイ周辺の構成を示す概念図である。図1に示された構成と比較して、書き込み制御線44を読み出し補ビット線46と置換し、読み出し補ワード線32を省いた構成となっている。

【0136】

図31は図30に示されたメモリセルMCの一つの構成を例示する回路図である。従来の技術と同様に、行の位置及び列の位置を示す添字は省略している。メモリセルMCは図29に示された構成に対して、トランジスタQN3,QN4の代わりにいずれもNMOSトランジスタのトランジスタQN15,QN16,QN17,QN18を備えた構造を有している。もちろん、読み出し補ワード線32をも使用して、メモリセルMCにおいてトランジスタQN13,QN14の代わりに読み出し回路RKを採用してもよい。しかし、本実施の形態は上述のように、ノードN1,N2がトランジスタのゲートではなく、読み出しビット線43、読み出し補ビット線46を充放電する可能性のある読み出し機構を有する場合に特に効果的である。

【0137】

トランジスタQN17の電流電極対の一方、例えばソースには電位VSSが供給され、電流電極対の他方、例えばドレインにはノードN2が接続される。またトランジスタQN18の電流電極対の一方、例えばソースには電位VSSが供給され、電流電極対の他方、例えばドレインにはノードN1が接続される。

【0138】

トランジスタQN15の電流電極対の一方、例えばソースにはノードN4において書き込みビット線41が接続され、電流電極対の他方、例えばドレインにはトランジスタQN17のゲートが接続される。またトランジスタQN16の電流電極対の一方、例えばソースには書き込み補ビット線42が接続され、電流電極対の他方、例えばドレインにはトランジスタQN18のゲートが接続される。そしてトランジスタQN15,QN16のゲートはいずれも書き込みワード線31に接続される。

【0139】

このような構成における書き込み動作では、まずノードN1,N2に与えるべき論理に対応する電位が、それぞれ書き込みビット線41、書き込み補ビット線42にプリチャージされる。例えば“H”、“L”に対応してそれぞれ電位VDD,VSSが書き込みビット線41、書き込み補ビット線42に与えられる。その後に書き込みワード線31が活性化し、トランジスタQN15,QN16がオンし、トランジスタQN17,QN18のゲートにそれぞれ電位(VDD−Vthn),VSSが印加される(但しトランジスタQN15のしきい値電圧をVthn>0とした)。これにより、トランジスタQN17,QN18はそれぞれオン、オフの状態となる。そしてトランジスタQN17がオンとなっているので、ノードN2には電位VSSが伝達される。よってインバータL1の機能によってノードN1には論理“H”が記憶される。

【0140】

その後、書き込みビット線41、書き込み補ビット線42はいずれも電位VSSに設定されてトランジスタQN17,QN18のゲートが“L”となり、これらはオフの状態となる。その後に書き込みワード線31が非活性化して“L”となり、トランジスタQN15,QN16がオフして、トランジスタQN17,QN18のゲートをフローティング状態にする。

【0141】

また読み出し動作は、読み出しワード線33が活性化することにより、トランジスタQN13,QN14がオンし、ノードN1,N2において記憶された論理がそれぞれノードN3,N10において読み出しビット線43、読み出し補ビット線46へと伝達される。読み出し速度を早めるために読み出しワード線33の活性化に先立ってプリチャージが行われることが望ましい。

【0142】

以上のような構成では、書き込み動作において書き込みビット線41、書き込み補ビット線42からストレージセルSCへと電荷が供給されるのではなく、電位VSSをノードN1,N2のいずれか一方にのみ与えている。即ち書き込みビット線41、書き込み補ビット線42とノードN1,N2との間には、電荷が直接に移動する経路が存在しない。従って書き込みワード線31が活性化しており、かつ書き込みビット線41、書き込み補ビット線42がフローティングの状態にあっても、これらがストレージセルSCによって充放電されることがなく、不要な電力が消費されない。よって書き込みワード線31、読み出しワード線33が同時に“H”となる期間があっても読み出し動作が遅くなることもない。

【0143】

上記の書き込み動作の終了時においては、トランジスタQN17,QN18がオフしてからトランジスタQN15,QN16をオフする手順を説明した。しかし逆に、トランジスタQN15,QN16がオフしてからトランジスタQN17,QN18をオフすることも可能である。この場合、トランジスタQN17,QN18のいずれか一方がオンとなる状態でそれぞれのゲートがフローティング状態に移行するので、ストレージセルSCの情報をバックアップする効果がある。例えば中性子線等の宇宙線が照射されることに起因して、ストレージセルSCに記憶された内容が反転するソフトエラーが考えられる。よってストレージセルSCの情報をバックアップすることで、ソフトエラーが生じるのに必要な臨界電荷量が増加し、つまりソフトエラーが起こりにくくすることができる。

【0144】

図32は本実施の形態の変形を示す回路図である。書き込みワード線31を書き込み補ワード線34に置換し、トランジスタQN15,QN16をいずれもPMOSトランジスタQP15,QP16に置換した構成を有している。

【0145】

この構成においても論理の伝搬という点で図31に示された構成と同様の効果がある。但し、トランジスタQN17,QN18のゲートに“H”を与える際、しきい値電圧Vthn(>0)だけ電位が低下することを回避できる。

【0146】

その一方、PMOSトランジスタQP15,QP16のしきい値電圧をVthp(<0)とすると、トランジスタQN17,QN18のゲートに“L”を与える際、その電位がVSS−Vthpと上昇する。よってトランジスタQN17,QN18を確実にオフさせ、ノードN1,N2から電位点VSSへのリーク電流を抑制するという点では、図31に示された構成の方が有利である。

【0147】

図33は本実施の形態の更なる変形を示す回路図である。書き込みワード線31及び書き込み補ワード線34の両方を採用し、ノードN4とトランジスタQN17のゲートとの間には、トランジスタQP15,QN15の並列接続によるトランスミッションゲートが接続され、ノードN5とトランジスタQN18のゲートとの間には、トランジスタQP16,QN16の並列接続によるトランスミッションゲートが接続される。そしてPMOSトランジスタQP15,QP16のゲートは書き込み補ワード線34に、NMOSトランジスタQN15,QN16のゲートは書き込みワード線31に、それぞれ接続される。

【0148】

このような構成により、トランジスタQN17,QN18のオン/オフを正確に制御することができる。

【0149】

実施の形態8.

図34は本実施の形態にかかるメモリセルMCの一つの構成を例示する回路図である。従来の技術と同様に、行の位置及び列の位置を示す添字は省略しているが、図30で示されたMCijの各々として採用することができる。

【0150】

メモリセルMCは、図53で示された構成と比較して、ストレージセルSCの構成が特徴的に異なっている。簡単にいうと、ストレージセルSCはトランジスタQN1,QN2を有さず、トランジスタQP1,QP2のクロスカップルで構成されている。

【0151】

より具体的にいえば、記憶ノードN2は、トランジスタQN9,QN10の直列接続を介してのみ電位点VSSに接続されている。トランジスタQN9,QN10のゲートはそれぞれ書き込みビット線41、書き込みワード線31に接続されており、これらの論理によって導通が制御される。同様にして記憶ノードN1は、トランジスタQN11,QN12の直列接続を介してのみ電位点VSSに接続されている。トランジスタQN11,QN12のゲートはそれぞれ書き込み補ビット線42、書き込みワード線31に接続されており、これらの論理によって導通が制御される。

【0152】

なお、図53で示された構成と比較して、ストレージセルSCの記憶ノードN1,N2から読み出しを行うための構成は異なっている。即ち、読み出し回路RKではなく、実施の形態7で示されたトランジスタQN13,QN14が用いられている。読み出しワード線33が活性化することにより、トランジスタQN13,QN14がオンし、ノードN1,N2において記憶された論理がそれぞれノードN3,N10において読み出しビット線43、読み出し補ビット線46へと伝達される。読み出し速度を早めるために読み出しワード線33の活性化に先立って読み出しビット線43、読み出し補ビット線46のプリチャージが行われることが望ましい。

【0153】

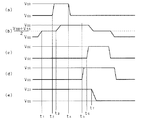

図35は図34に示されたメモリセルMCの動作を示すタイミングチャートの一例である。同図(a),(b),(c),(d),(e)はそれぞれ読み出しワード線33、読み出し補ビット線46、書き込みワード線31、書き込みビット線41、記憶ノードN2の電位を示している。ここでは“H”が記憶されていた記憶ノードN2に“L”を書き込む場合が例示されている。

【0154】

時刻t1以前はスタンバイ時であり、読み出し補ビット線46は読み出しビット線43と共に、実線のように電位VSSに、あるいは破線のように電位(VDD+VSS)/2に、プリチャージされている。そして時刻t1に至って読み出し補ビット線46は読み出しビット線43と共に、電位(VDD+VSS)/2にプリチャージされる。その後、時刻t2において読み出しワード線33が電位VDDへの遷移を開始し、当該遷移を契機としてトランジスタQN14はトランジスタQN13と共にONする。これにより、時刻t3において読み出し補ビット線46は記憶ノードN2が保存していた論理“H”に起因して、その電位が電位VDDへと遷移し始める。その後、時刻t4において読み出しワード線33が電位VSSへの遷移を開始し、更にその後の時刻t5において書き込みビット線41が電位VDDへの遷移を開始する。当該遷移を契機としてトランジスタQN9はONする。更にその後、時刻t6において書き込みワード線31も電位VDDへの遷移を開始し、当該遷移を契機としてトランジスタQN10もONする。これにより、記憶ノードN2はトランジスタQN9,QN10を介して電位点VSSに接続されることになり,時刻t7において記憶ノードN2の電位は電位VDDから電位VSSへと遷移し始める。この後、書き込みワード線31が電位VSSへと遷移してスタンバイ動作となり、書き込みビット線41も電位VSSへと遷移する。

【0155】

もちろん、記憶ノードN2に“L”が記憶されていた状態に対して“L”を書き込む場合も同様にして、トランジスタQN9,QN10を介して電位点VSSに接続されることによって実現される。そして記憶ノードN2に“L”が書き込まれれれば、トランジスタQP1はONし、これを介して記憶ノードN1は電位点VDDに接続されることで“H”が書き込まれる。

【0156】

本実施の形態においても実施の形態7と同様にして、書き込みビット線41、書き込み補ビット線42とノードN1,N2との間には、電荷が直接に移動する経路が存在しない。従って書き込みワード線31が活性化しており、かつ書き込みビット線41、書き込み補ビット線42がフローティングの状態にあっても、これらがストレージセルSCによって充放電されることがなく、不要な電力が消費されない。よって書き込みワード線31、読み出しワード線33が同時に“H”となる期間があっても読み出し動作が遅くなることもない。

【0157】

しかも、図53で示された構成と比較して、トランジスタ数が少ないため、ストレージセル一つ当たりトランジスタ2個分、面積を縮小することができる。またインバータL1,L2は情報を安定に保持するために高いスタティックノイズマージンを持つように設計されており、記憶内容を反転するのに時間がかかる。しかし本実施の形態の構成ではトランジスタのクロスカップルによって記憶を保持しているので、書き込み動作を高速に行うことができる。

【0158】

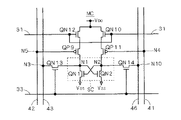

また本実施の形態の構成を有するメモリセルでは、half-select write disturbを回避することができる。図36は図34に示された構造のメモリセルMCがマトリクス状に配置された構成の一部を示す回路図である。そして第x番目の行であって第j番目の列に属するメモリセルMCxjと、第x番目の行であって第z番目の列に属するメモリセルMCxzと、第y番目の行であって第j番目の列に属するメモリセルMCyjとを抽出して描いている。

【0159】

まずメモリセルMCxjの記憶ノードN1に情報を書き込む場合を想定する。書き込みビット線41j、書き込み補ビット線42jがそれぞれ“H”,“L”である場合に書き込みワード線31xが“H”となると、メモリセルMCxjのトランジスタQN9,QN10を介して記憶ノードN2に電位VSSが与えられる。このとき、メモリセルMCxjのトランジスタQN11はオフしている。また記憶ノードN2に電位VSSが与えられているのでメモリセルMCxjのトランジスタQP1はONし、記憶ノードN1には電位VDDが与えられる。

【0160】

この際、メモリセルMCxzのトランジスタQN10,QN12も、書き込みワード線31xが“H”となることによってONする。しかし書き込みビット線41z、書き込み補ビット線42zをいずれも電位VSSにプリチャージしてスタンバイ状態としておくことにより、メモリセルMCxzのトランジスタQN9,QN11をオフさせておくことができる。よってメモリセルMCxzの記憶内容が書き換えられることはない。

【0161】

また、メモリセルMCyjのトランジスタQN9も、書き込みビット線41jが“H”となることによってONする。しかし書き込みワード線31yが選択されていないので“L”であり、よってメモリセルMCyjのトランジスタQN10,QN12をオフさせておくことができる。よってメモリセルMCyjの記憶内容が書き換えられることはない。以上のことから、half-select write disturbを回避することができる。

【0162】

図37は本実施の形態の第1の変形にかかるメモリセルの構成を示す回路図である。当該メモリセルでは図34に示された構成に対し、書き込みワード線31ではなく、書き込み補ワード線34を採用している。そしてNMOSトランジスタQN10,QN12をそれぞれPMOSトランジスタQP10,QP12に置換している。書き込み動作において書き込み補ワード線34には書き込みワード線31と相補的な論理が与えられるので、書き込みワード線31と書き込み補ワード線34とに与えられた論理に関し、PMOSトランジスタQP10,QP12はNMOSトランジスタQN10,QN12と同様の動作をする。従って、図37に示された構成も図34に示された構成と同様の効果を得ることができる。

【0163】

図38は本実施の形態の第2の変形にかかるメモリセルの構成を示す回路図である。当該メモリセルでは図34に示された構成に対し、NMOSトランジスタQN9,QN11をそれぞれPMOSトランジスタQP11,QP9に置換している。そしてPMOSトランジスタQP9,QP11のゲートにはそれぞれ書き込みビット線41、書き込み補ビット線42が接続されている。書き込みビット線41、書き込み補ビット線42には書き込み動作の際に相互に相補的な論理が与えられるので、PMOSトランジスタQP9,QP11は、書き込みビット線41、書き込み補ビット線42に与えられた論理に対してNMOSトランジスタQN11,QN9と同様の動作をする。従って、図38に示された構成も図34に示された構成と同様の効果を得ることができる。

【0164】

図39は本実施の形態の第3の変形にかかるメモリセルの構成を示す回路図である。当該メモリセルでは図34に示された構成と、高電位側と低電位側を入れ替えた構成を有している。即ち、記憶ノードN2は、トランジスタQP11,QP10の直列接続を介してのみ電位点VDDに接続されている。トランジスタQP11,QP10のゲートはそれぞれ書き込みビット線41、書き込み補ワード線34に接続されており、これらの論理によって導通が制御される。同様にして記憶ノードN1は、トランジスタQP9,QN12の直列接続を介してのみ電位点VDDに接続されている。トランジスタQP9,QP12のゲートはそれぞれ書き込み補ビット線42、書き込み補ワード線34に接続されており、これらの論理によって導通が制御される。このような構成でも図34に示された構成と同様の効果が得られるのは明白である。

【0165】

図40は本実施の形態の第4の変形にかかるメモリセルの構成を示す回路図である。当該メモリセルでは図39に示された構成に対し、書き込み補ワード線34ではなく、書き込みワード線31を採用している。そしてPMOSトランジスタQP10,QP12をそれぞれNMOSトランジスタQN10,QN12に置換している。書き込み動作において書き込み補ワード線34には書き込みワード線31と相補的な論理が与えられるので、書き込みワード線31と書き込み補ワード線34とに与えられた論理に関し、NMOSトランジスタQN10,QN12はPMOSトランジスタQP10,QP12と同様の動作をする。従って、図40に示された構成も図39に示された構成と同様の効果を得ることができる。

【0166】

図41は本実施の形態の第5の変形にかかるメモリセルの構成を示す回路図である。当該メモリセルでは図39に示された構成に対し、PMOSトランジスタQP9,QP11をそれぞれNMOSトランジスタQN11,QN9に置換している。そしてNMOSトランジスタQN11,QN9のゲートにはそれぞれ書き込みビット線41、書き込み補ビット線42が接続されている。書き込みビット線41、書き込み補ビット線42には書き込み動作の際に相互に相補的な論理が与えられるので、NMOSトランジスタQN9,QN11は、書き込みビット線41、書き込み補ビット線42に与えられた論理に対してPMOSトランジスタQP11,QP9と同様の動作をする。従って、図41に示された構成も図39に示された構成と同様の効果を得ることができる。

【0167】

図42は本実施の形態の第6の変形にかかるメモリセルの構成を示す回路図である。当該セルは図34に示された構成において、トランジスタQN12をトランジスタQN10で兼用した構成を有している。また図43は本実施の形態の第7の変形にかかるメモリセルの構成を示す回路図である。当該セルは図39に示された構成において、トランジスタQP12をトランジスタQP10で兼用した構成を有している。第6の変形も第7の変形も、1つのメモリセル当たり、2つのトランジスタをマージしてトランジスタの数を1つ減らしている。これにより、メモリセルの占有面積を低減しつつも、本実施の形態の効果を得ることができる。

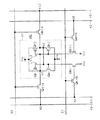

【0168】

図44は第i行のメモリセルMCi1〜MCinにおいて図42に示された構成を応用した構成を示す回路図である。同じ行に属する複数のメモリセルMCijは、書き込みワード線31を共通に使用する。従ってn個のメモリセルMCi1〜MCinについて、トランジスタQN10(あるいはQN12)は、一つのNMOSトランジスタQN100へとマージすることができる。図45は第i行のメモリセルMCi1〜MCinにおいて図43に示された構成を応用した構成を示す回路図である。同じ行に属する複数のメモリセルMCijは、書き込み補ワード線34を共通に使用する。従ってn個のメモリセルMCi1〜MCinについて、トランジスタQP10(あるいはQP12)は、一つのPMOSトランジスタQP100へとマージすることができる。このようなマージにより、トランジスタ数を一層低減することができる。

【0169】

本実施の形態で示されたトランジスタはシリコン基板を用いて形成しても良いし、公知のSOI基板、SON(Silicon On Nothing)基板を用いて形成しても良い。

【0170】

実施の形態9.

図46は本実施の形態にかかるメモリセルMCの一つの構成を例示する回路図である。従来の技術と同様に、行の位置及び列の位置を示す添字は省略しているが、図1で示されたMCijの各々として採用することができる。但し、読み出し回路は省略している。

【0171】

図46に示されたメモリセルMCは、図10に示された構成に対し、ストレージセルSCをクロスカップルされた一対のトランジスタで構成した点で特徴的に異なっている。即ち、記憶ノードN1にはトランジスタQN1のドレインとトランジスタQN2のゲートとが共通に接続され、記憶ノードN2にはトランジスタQN1のゲートとトランジスタQN2のドレインとが共通に接続されていおり、更にトランジスタQN1,QN2のソースには共通に電位点VSSが接続されている。

【0172】

クロスカップルされた一対のインバータではなく、クロスカップルされた一対のトランジスタでストレージセルSCを構成することにより、ストレージセル一つ当たりトランジスタ2個分、面積を縮小することができる。またインバータL1,L2のように高いスタティックノイズマージンを持たせる設計が行われることもなく、書き込み動作を高速に行うことができる。

【0173】

トランジスタMN9,MN10は記憶ノードN1と書き込みビット線41との間に直列に接続され、トランジスタMN11,MN12は記憶ノードN2と書き込み補ビット線42との間に直列に接続されている。そしてトランジスタMN9,MN11はいずれもNMOSトランジスタであってそのゲートに共通して書き込み制御線44が接続されている。またトランジスタMN10,MN12はいずれもNMOSトランジスタであってそのゲートに共通して書き込みワード線31が接続されている。

【0174】

従って、選択された行の書き込みワード線31を共通にするメモリセルの各々のトランジスタMN10,MN12は導通する。しかし選択されていない列のメモリセルの各々のトランジスタMN9,MN11は導通しない。逆に、選択された列の書き込み制御線44を共通にするメモリセルの各々のトランジスタMN9,MN11は導通する。しかし選択されていない行のメモリセルの各々のトランジスタMN10,MN12は導通しない。従ってhalf-select write disturbを回避することができる。

【0175】

図47〜図49は本実施の形態の変形を示す回路図である。図47に示された構成は、図46に示された構成に対し、書き込み制御線44を書き込み補制御線45に置換し、NMOSトランジスタMN9,MN11をそれぞれPMOSトランジスタMP9,MP11に置換した構成を有している。書き込み補制御線45には書き込み制御線44と相補的な論理が与えられるので、図47に示された構成も図46に示された構成と同様に動作することは明白である。

【0176】

図48に示された構成は、図46に示された構成に対し、書き込みワード線31を書き込み補ワード線34に置換し、NMOSトランジスタMN10,MN12をそれぞれPMOSトランジスタMP10,MP12に置換した構成を有している。書き込み動作において書き込み補ワード線34には書き込みワード線31と相補的な論理が与えられるので、書き込みワード線31と書き込み補ワード線34とに与えられた論理に関し、PMOSトランジスタMP10,MP12はNMOSトランジスタMN10,MN12と同様の動作をする。従って、図48に示された構成も図46に示された構成と同様の効果を得ることができる。

【0177】

図49に示された構成は、図48に示された構成に対し、書き込み制御線44を書き込み補制御線45に置換し、NMOSトランジスタMN9,MN11をそれぞれPMOSトランジスタMP9,MP11に置換した構成を有している。図49に示された構成も図46に示された構成と同様に動作することは明白である。

【0178】

図50は本実施の形態の他の変形を示す回路図である。図49に示された構成において、ストレージセルSCの構成のみが異なっている。図50ではクロスカップルされた一対のトランジスタはPMOSトランジスタQP1,QP2である。即ち、記憶ノードN1にはトランジスタQP1のドレインとトランジスタQP2のゲートとが共通に接続され、記憶ノードN2にはトランジスタQP1のゲートとトランジスタQP2のドレインとが共通に接続されていおり、更にトランジスタQP1,QP2のソースには共通に電位点VDDが接続されている。図50に示された構成も図46に示された構成と同様に動作することは明白である。

【0179】

図46に示された構成では、メモリセルMCが全てNMOSトランジスタで構成されているので、PMOSトランジスタとNMOSトランジスタとの間の分離領域を設ける必要が無く、メモリセルMCの占有面積を小さくすることができる。図50に示された構成ではメモリセルMCが全てPMOSトランジスタで構成されているので、同様にしてメモリセルMCの占有面積を小さくすることができる。

【0180】

図46に示された構成では、書き込みビット線41に与えられた論理が“L”で電位VSSが与えられる場合は、NMOSトランジスタMN9,MN10のしきい値は問題とならず、記憶ノードN1には電位VSSが与えられる。しかし書き込みビット線41に与えられた論理が“H”で電位VDDが与えられる場合は、NMOSトランジスタMN9,MN10のしきい値電圧をVthn(>0)として、記憶ノードN1には電位(VDD−2Vthn)が与えられる。そのため記憶ノードN1に“H”を書き込む場合は、“L”を書き込む場合と比較してストレージセルSCの安定は遅くなる。

【0181】

図49や図50に示された構成では、書き込みビット線41に電位VDDが与えられる場合は、PMOSトランジスタMP9,MP10のしきい値は問題とならず、記憶ノードN1には電位VDDが与えられる。しかし書き込みビット線41に電位VSSが与えられる場合は、PMOSトランジスタMP9,MP10のしきい値電圧をVthp(<0)として、記憶ノードN1には電位(VSS−2Vthp)が与えられる。そのため記憶ノードN1に“L”を書き込む場合は、“H”を書き込む場合と比較してストレージセルSCの安定は遅くなる。

【0182】

これに対して図47に示された構成では書き込みビット線41に電位VDDが与えられた場合、PMOSトランジスタMP9でのしきい値分の減少はなく、記憶ノードN1には電位(VDD−Vthn)が与えられる。逆に書き込みビット線41に電位VSSが与えられた場合、NMOSトランジスタMN10でのしきい値分の減少はなく、記憶ノードN1には電位(VSS−Vthp)が与えられる。従ってストレージセルSCの安定に必要な時間の最悪値(最大値)を図49や図50に示された構成よりも小さくすることができる。これは図48に示された構成についても同様である。

【0183】

本実施の形態の説明は全て書き込み回路について説明したが、これらは読み出し回路について採用できることは明白である。即ち書き込みワード線31,書き込み補ワード線34、書き込みビット線41、書き込み補ビット線42をそれぞれ読み出しワード線33,読み出し補ワード線32、読み出しビット線43、読み出し補ビット線46と読み替えればよい。更に書き込み制御線44,書き込み補制御線45はそれぞれ読み出し制御線、読み出し補制御線と読み替えればよい。

【0184】

ここで読み出し制御線には読み出し時に活性化(例えば“H”)、スタンバイ時に非活性化(例えば“L”)する信号が与えられ、読み出し補制御線には読み出し時において読み出し制御線と相補的な論理を採る信号が与えられる。読み出し制御線に与える信号としては、読み出しワード線33に与えられる論理と読み出し補ワード線32に与えられる論理との論理的排他和を採用することができる。

【0185】

もちろん、ワード線対、ビット線対を読み出し/書き込みの両方に採用することもできる。本実施の形態はマルチポート、シングルポートのいずれのタイプにも適用することができる。

【0186】

本実施の形態で示されたトランジスタはシリコン基板を用いて形成しても良いし、公知のSOI基板、SON(Silicon On Nothing)基板を用いて形成しても良い。

【0187】

【発明の効果】

この発明のうち請求項1にかかる記憶装置によれば、書き込み動作時においては、書き込み対象となるメモリセルにおいて、書き込みワード線と、書き込み制御線のいずれもが活性化するので、第1の記憶ノードが第1のスイッチを介して書き込みビット線と接続される。よって書き込みビット線に与えられた論理の如何によらず、第1の記憶ノードに於いて記憶される論理を反転するのに必要な時間は短い。その一方で、書き込み対象とならないメモリセルにおいては書き込み制御線が活性化しないので、第1のスイッチは第1の記憶ノードを書き込みビット線に接続しない。従って、かかるメモリセルにおける不要な電力の消費を低減できる。

【0188】

そして、選択されないビット線群において書き込みビット線及び書き込み補ビット線はプリチャージされる。このプリチャージは通常、書き込みビット線及び書き込み補ビット線を等しい電位に設定するので、両者の排他的論理和を採ることにより、書き込み制御線を非活性化することができる。

【0189】

この発明のうち請求項2にかかる記憶装置によれば、プリチャージの際に書き込みビット線及び書き込み補ビット線に与えられる電位が、相補的な論理に相当する2つの電位の中間の電位であっても、排他的論理和を正確に得ることができる。

【0190】

この発明のうち請求項3又は請求項4にかかる記憶装置によれば、第1のスイッチを第1及び第2のトランジスタで実現することができる。

【0194】

この発明のうち請求項5にかかる記憶装置によれば、第2トランジスタをSOI基板上に形成しても、書き込みワード線が非活性の際に第1電流電極とボディとの間に実効ベース電流が流れることを抑制できるので、いわゆるhalf-select write disturbを解消することができる。

【図面の簡単な説明】

【図1】 この発明の実施の形態1にかかるSRAMを示す概念図である。

【図2】 この発明の実施の形態1にかかるメモリセルの一つを例示する回路図である。

【図3】 トライステートインバータを例示する回路図である。

【図4】 XOR回路を例示する回路図である。

【図5】 XOR回路を例示する回路図である。

【図6】 XOR回路を例示する回路図である。

【図7】 XOR回路を例示する回路図である。

【図8】 XOR回路を例示する回路図である。

【図9】 XOR回路を例示する回路図である。

【図10】 この発明の実施の形態1の変形を示す回路図である。

【図11】 この発明の実施の形態1を例示する模式図である。

【図12】 この発明の実施の形態2にかかるSRAMを示す概念図である。

【図13】 この発明の実施の形態2にかかるメモリセルの一つを例示する回路図である。

【図14】 この発明の実施の形態2の変形を示す回路図である。

【図15】 この発明の実施の形態2の他の変形を示す回路図である。

【図16】 この発明の実施の形態3にかかるメモリセルの一つを例示する回路図である。

【図17】 この発明の実施の形態3の変形を示す回路図である。

【図18】 この発明の実施の形態4にかかるメモリセルの一つを例示する回路図である。

【図19】 この発明の実施の形態4の変形を示す回路図である。

【図20】 この発明の実施の形態5にかかるメモリセルの一つを例示する回路図である。

【図21】 この発明の実施の形態5の第1の変形にかかるメモリセルを示す回路図である。

【図22】 この発明の実施の形態5の第2の変形にかかるメモリセルを示す回路図である。

【図23】 この発明の実施の形態5の第3の変形にかかるメモリセルを示すの回路図である。

【図24】 この発明の実施の形態5の第4の変形にかかるメモリセルを示す回路図である。

【図25】 この発明の実施の形態5の第5の変形にかかるメモリセルを示す回路図である。

【図26】 この発明の実施の形態5の第6の変形にかかるメモリセルを示す回路図である。

【図27】 この発明の実施の形態5の第6の変形にかかるメモリセルの複数を示す回路図である。

【図28】 従来のアクセストランジスタを例示する断面図である。

【図29】 デュアルポートSRAMに採用され得るメモリセルを例示する回路図である。

【図30】 この発明の実施の形態7にかかるSRAMを示す概念図である。

【図31】 この発明の実施の形態7にかかるメモリセルの一つを例示する回路図である。

【図32】 この発明の実施の形態7の変形にかかるメモリセルを示す回路図である。

【図33】 この発明の実施の形態7の更なる変形にかかるメモリセルを示す回路図である。

【図34】 この発明の実施の形態8にかかるメモリセルの一つを例示する回路図である。

【図35】 この発明の実施の形態8にかかるメモリセルの動作を例示するタイミングチャートである。

【図36】 この発明の実施の形態8にかかるメモリセルがマトリクス状に配置された構成の一部を示す回路図である。

【図37】 この発明の実施の形態8の第1の変形にかかるメモリセルの構成を示す回路図である。

【図38】 この発明の実施の形態8の第2の変形にかかるメモリセルの構成を示す回路図である。

【図39】 この発明の実施の形態8の第3の変形にかかるメモリセルの構成を示す回路図である。

【図40】 この発明の実施の形態8の第4の変形にかかるメモリセルの構成を示す回路図である。

【図41】 この発明の実施の形態8の第5の変形にかかるメモリセルの構成を示す回路図である。

【図42】 この発明の実施の形態8の第6の変形にかかるメモリセルの構成を示す回路図である。

【図43】 この発明の実施の形態8の第7の変形にかかるメモリセルの構成を示す回路図である。

【図44】 この発明の実施の形態8の第6の変形にかかるメモリセルの複数を示す回路図である。

【図45】 この発明の実施の形態8の第7の変形にかかるメモリセルの複数を示す回路図である。

【図46】 この発明の実施の形態9にかかるメモリセルMCの一つの構成を例示する回路図である。

【図47】 この発明の実施の形態9の変形を示す回路図である。

【図48】 この発明の実施の形態9の変形を示す回路図である。

【図49】 この発明の実施の形態9の変形を示す回路図である。

【図50】 この発明の実施の形態9の他の変形を示す回路図である。

【図51】 従来のSRAMを示す概念図である。

【図52】 従来のメモリセルを例示する回路図である。

【図53】 従来のメモリセルを例示する回路図である。

【図54】 デュアルポートSRAMと、その動作を制御する装置との接続を示すブロック図である。

【符号の説明】

30 ワード線群、31 書き込みワード線、32 読み出し補ワード線、33 読み出しワード線、34 書き込み補ワード線、40 ビット線群、41 書き込みビット線、42 書き込み補ビット線、43 読み出しビット線、44書き込み制御線、45 書き込み補制御線、46 読み出し補ビット線、MC

メモリセル。[0001]

BACKGROUND OF THE INVENTION

The present invention relates to a multi-port SRAM (Static Random Access Memory) composed of a MISFET (Metal Insulator Semiconductor Field Effect Transistor), and more particularly to a technique for reading and writing data from / to a memory cell of the SRAM.

[0002]

[Prior art]

In an integrated circuit, an SRAM has a function of temporarily storing data and instructions in order to transmit data and data to a CPU in accordance with the timing of a cache, that is, a CPU (Central Processing Unit). Used to memorize. In recent years, the rate at which data is read from or written to the memory has been emphasized. In order to increase the bandwidth of the memory, a technique has been proposed in which a plurality of input / output terminals are provided in an SRAM memory cell. As this technology, a dual port static memory cell having one read port and one write port, and a multi-port having many read terminals and write terminals ( multi port) Static memory cell can be cited as an example.

[0003]

FIG. 51 is a conceptual diagram showing a configuration around a memory cell array of a conventional SRAM. The memory cells are arranged in a matrix of m rows and n columns, and the memory cells in the i rows and j columns are MC.ijLet's show it as In FIG. 51, memory cells MC arranged in the first row and the third column.13The symbol of is described.

[0004]

The SRAM shown in FIG. 51 employs a configuration in which word lines extend in the row direction and bit lines extend in the column direction. The

[0005]

Memory cell MCijWord

[0006]

[0007]

FIG. 52 is a circuit diagram illustrating a structure common to all the memory cells MC. Since the structure of the memory cell MC basically does not depend on the position (i, j) of the row or column, the subscript indicating the position of the row or column is omitted here.

[0008]

Memory cell MC includes a storage unit SC (referred to herein as a “storage cell”) SC having a pair of inverters L1 and L2 connected in antiparallel, a read circuit RK, and access transistors QN3 and QN4. ing.

[0009]

In the storage cell SC, the inverter L1 is constituted by series connection of transistors QP1 and QN1, and the inverter L2 is constituted by series connection of transistors QP2 and QN2. Further, the readout circuit RK includes a tristate inverter constituted by series connection of transistors QP3, QP4, QN5, and QN6.

[0010]

N-type MOSFETs (Metal Oxide Semiconductor Field Effect Transistors) are used for the transistors QN1 to QN6, and P-type MOSFETs are used for the transistors QP1 to QP4. For example, the N-type MOSFET is a surface channel type, and the P-type MOSFET is a surface channel type or a buried channel type.

[0011]

The storage cell SC has a pair of nodes N1 and N2, and there is a pair of storage states when the nodes N1 and N2 are “H” and “L”, respectively, and vice versa. “H” means (VDD+ VSS) / 2 means logic corresponding to a potential higher than “/ 2”, and “L” means (VDD+ VSS) / 2 means a logic corresponding to a potential lower than 2. However, the potential VSSIn many cases, the ground is selected. Hereinafter, “H” and “L” may mean not only logic but also potentials corresponding to the logic. It should be noted that which one of “H” and “L” corresponds to the SRAM bits “1” and “0” is a matter of design choice.

[0012]

The N-type MOSFET is turned on when “H” is applied to its gate and turned off when “L” is applied. The P-type MOSFET is turned on when “L” is applied to its gate and turned off when “H” is applied. In the ON state, a current flows between the source / drain, and the two are electrically connected. In the off state, the source / drain is electrically disconnected and the current isAlmostNot flowing.

[0013]

The node N1 is an input terminal of the inverter L2, and a potential corresponding to a logic complementary to the logic corresponding to the potential of the node N1 is output to the node N2. The node N2 is an input terminal of the inverter L1, and an inverted bit of logic complementary to the logic corresponding to the potential of the node N2 is output to the node N1. Therefore, a pair of storage states corresponding to complementary logics exist.

[0014]

Access transistor QN3 is connected to storage cell SC and write

[0015]

In the read circuit RK, the drains of the transistors QP4 and QN5 are commonly connected to the node N3. The gates of the transistors QP3 and QN6 are commonly connected to the node N1. The gates of the transistors QP4 and QN5 are connected to the read

[0016]

When reading data from the memory cell MC, complementary logic is set in the

[0017]

Accordingly, the transistors QP4 and QN5 of the read circuit RK of the memory cell MC to be read are all turned on. Thus, a value complementary to node N1 is applied to read

[0018]

When writing data to the memory cell MC, the

[0019]

Accordingly, the access transistors QN3 and QN4 of the memory cell MC to be written are both turned on, and the nodes N1 and N2 of the storage cell SC are connected to the

[0020]

As described above, since the logic of the nodes N1 and N2 of the storage cell SC has a complementary relationship, the

[0021]

When the write operation is completed, the

[0022]

[Problems to be solved by the invention]

In the above configuration, when the

[0023]

On the other hand, both the

[0024]

Further, the bit line pair to which the potential is applied by the storage cell SC as described above is precharged again in preparation for the next write operation. At this time, unnecessary power is newly consumed.

[0025]

FIG. 53 is a circuit diagram showing a configuration of a memory cell MC proposed to prevent the above power consumption, and is introduced in, for example, US Pat. No. 6,005,794.

[0026]

NMOS transistors QN9 and QN10 are connected to node N1 and potential VSSPotential point (hereinafter “potential point VSSFor example, connected in series with the ground. The gate of the NMOS transistor QN9 is connected to the

[0027]

The

[0028]

During such a write operation, any unselected write bit pair lines are at potential VSSSet to Therefore, since the transistors QN9 and QN11 are turned off in the memory cell MC that is not a write target, the memory cell MC is arranged in a row corresponding to the selected

[0029]

However, this circuit has a problem that the time required for the write operation for changing the stored contents of the storage cell SC is long. That is, one of the nodes N1 and N2 is set to “L” from the outside of the storage cell SC, but there is no function of setting the other to “H” from the outside of the storage cell SC. For example, when the state where the nodes N1 and N2 are “H” and “L”, respectively, is inverted to the complementary state, the transistors QN9 and QN10 are turned on to try to discharge the node N1. Since N2 is “L” and is not set to “H” from the outside of the storage cell SC, the inverter L1 tries to hold the node N1 at “H”. Since the storage cell SC is designed to have a high static noise margin in order to stably hold data, the storage contents of the storage cell SC cannot be reversed quickly only by discharging the node N1.

[0030]

The present invention has been made based on the above background, and an object of the present invention is to provide a technique for reducing unnecessary power consumption while rapidly performing writing to invert stored contents.

[0031]

[Means for Solving the Problems]

According to a first aspect of the present invention, there is provided a storage device comprising: (a) a plurality of word line groups; (b) a plurality of bit line groups; and (c) a plurality of memory cells. Each of the line groups has (a-1) write word lines, and each of the bit line groups has (b-1) write bit lines and (b-2) write provided corresponding to the write bit lines. (C) each of the memory cells is provided corresponding to one word line group and one bit line group, and (c-1) a storage including a first storage node A cell, (c-2) connected between the write bit line of the corresponding one bit line group and the first storage node, and the write word line of the corresponding one word line group; , Conductive only when any of the write control lines is activated And a first switch that. Then, the write control line in the selected bit line group is activated, and the write control line in the unselected bit line group is not activated.

[0032]

AndEach of the bit line groups further includes (b-3) a write complementary bit line provided corresponding to the write bit line, and each of the storage cells includes (c-1-1) the Each of the memory cells includes: (c-3) the write complementary bit line of the corresponding one bit line group; and a second storage node provided with a logic complementary to the logic in the one storage node. A second switch connected between the second storage node and conducting only when both the write word line of the corresponding one word line group and the write control line are activated; The write bit line and the write complementary bit line adopt complementary logic to each other when the bit line group to which the write bit line belongs are selected, and adopt equal logic to each other when not selected. The bit In the lines, the write control line takes the exclusive OR of the write bit line and write complementary bit line.

[0033]

Claim of the invention2The claim is1The exclusive OR is obtained after non-inverting amplification of the potentials of the write bit line and the write complementary bit line.

[0037]

According to a third aspect of the present invention, there is provided a storage device comprising (a) a plurality of word line groups, (b) a plurality of bit line groups, and (c) a plurality of memory cells, wherein the word Each of the line groups has (a-1) write word lines, and each of the bit line groups has (b-1) write bit lines and (b-2) write provided corresponding to the write bit lines. (C) each of the memory cells is provided corresponding to one word line group and one bit line group, and (c-1) a storage including a first storage node A cell, (c-2) connected between the write bit line of the corresponding one bit line group and the first storage node, and the write word line of the corresponding one word line group; , Conductive only when any of the write control lines is activated And a first switch that. Then, the write control line in the selected bit line group is activated, and the write control line in the unselected bit line group is not activated.

AndThe first switch includes (c-2-1) a control electrode, a first current electrode connected to the write bit line, and a second current electrode connected to the first storage node. (C-2-2) a control electrode connected to the write control line, a first current electrode connected to the control electrode of the first transistor, and a write word line And a second transistor having a second current electrode formed thereon.

[0038]

According to a fourth aspect of the present invention, there is provided a storage device comprising (a) a plurality of word line groups, (b) a plurality of bit line groups, and (c) a plurality of memory cells, wherein the word Each of the line groups has (a-1) write word lines, and each of the bit line groups has (b-1) write bit lines and (b-2) write provided corresponding to the write bit lines. (C) each of the memory cells is provided corresponding to one word line group and one bit line group, and (c-1) a storage including a first storage node A cell, (c-2) connected between the write bit line of the corresponding one bit line group and the first storage node, and the write word line of the corresponding one word line group; , Conductive only when any of the write control lines is activated And a first switch that. Then, the write control line in the selected bit line group is activated, and the write control line in the unselected bit line group is not activated.

AndThe first switch includes (c-2-1) a control electrode to which the write word line is connected, a first current electrode, and a second current electrode connected to the write control line. A first transistor; and (c-2-2) a control electrode connected to the first current electrode of the first transistor; a first current electrode connected to the write bit line; and the first memory. And a second transistor having a second current electrode connected to the node.

[0044]

Claim of the invention5The claim is3The first transistor is an NMOS transistor formed on an SOI substrate, and the inactive write word line is connected to the first current electrode and the body of the first transistor. A potential to reduce forward bias is applied.

[0051]

DETAILED DESCRIPTION OF THE INVENTION

In the present embodiment, unless otherwise specified, logic “H” corresponds to a state in which a word line is activated, that is, selected, and “L” represents that it is not activated, that is, not selected. A description will be given assuming that it corresponds. Even if these relations are reversed, the following explanation is valid if the conductivity type of the transistor used is appropriately changed.

[0052]

1 is a conceptual diagram showing a configuration around a memory cell array of an SRAM according to a first embodiment of the present invention. A

[0053]

FIG. 2 is a circuit diagram illustrating one configuration of the memory cell MC shown in FIG. As in the prior art, subscripts indicating row positions and column positions are omitted. The memory cell MC includes a storage cell SC, a read circuit RK, and pass transistors MN9, MN10, MN11, and MN12, all of which are NMOS transistors, a

[0054]

The storage cell SC has inverters L1 and L2 connected in antiparallel, and nodes N1 and N2 exist as output terminals of the storage cells SC. The inverter L1 has a potential VDD, A PMOS transistor QP1 including a source connected to the node N1, a drain connected to the node N1, a gate connected to the node N2, and a potential VSSAnd an NMOS transistor QN1 including a drain connected to the node N1 and a gate connected to the node N2. Similarly, the inverter L2 has the potential VDD, A PMOS transistor QP2 including a source connected to the node N2, a drain connected to the node N2, a gate connected to the node N1, and a potential VSSAnd an NMOS transistor QN2 including a drain connected to the node N2, and a gate connected to the node N1.

[0055]

The read circuit RK has a potential VDDA PMOS transistor QP3 including a gate connected to the node N1, a drain connected to the read

[0056]

FIG. 3 is a circuit diagram illustrating the configuration of the tri-state inverter, and substantially shows the configuration of the readout circuit RK. Logic A is common to one gate of the pair of NMOS transistors and one gate of the pair of PMOS transistors, logic B is assigned to the other gate of the pair of NMOS transistors, and logic B is assigned to the other gate of the pair of PMOS transistors. Bars (which are complementary to B and are indicated by adding an upper line to B in the figure: the same applies to the other logics). If the logic B is “L”, the output logic Z is not determined by the tristate inverter (tristate condition). However, if the logic B is “H”, the logic Z obtained by inverting the logic A is output.

[0057]

Returning to FIG. 2, the pass transistors MN9 and MN10 are connected in series between the node N4 on the

[0058]

Similarly, the pass transistors MN11 and MN12 are connected in series between the node N5 on the write

[0059]

The operations of the pass transistors MN10 and MN12 depend on the logic in the

[0060]

The write operation for the memory cell having such a configuration is as follows. The selected

[0061]

Therefore, the node N1 of the storage cell SC is connected to the

[0062]

In order to consider the magnitude of the potential, the threshold voltages of the pass transistors MN9 and MN10 are set to the potential V.thnThe

[0063]

Potential difference (VDD-VSS) Becomes 1V or less, the inverters L1 and L2 of the storage cell SC are at the potential (VDD-2Vthn) May be recognized as “L” instead of “H”. In order to prevent this, the potential applied as “H” to the

[0064]

Now, the operation of the memory cells MC arranged in the row corresponding to the selected

[0065]

4 to 9 are circuit diagrams illustrating an XOR circuit that obtains the exclusive OR of both from the logics A and B as the logic Z. FIG. These XOR circuits can be employed to obtain the exclusive OR of the logic applied to the

[0066]

For example, the operation of the XOR circuit shown in FIG. 7 will be described. When the logic A is “H”, the inverter composed of the PMOS transistor TP1 and the NMOS transistor TN1 gives the logic “L” to the node J1. On the other hand, a logic A, that is, “H” is given to the node J2. The PMOS transistor TP2 and the NMOS transistor TN2 are connected in series between the nodes J2 and J1, and both function as an inverter. This inverter inputs logic B and outputs a logic B bar as logic Z to node J3. At this time, since the transmission gate formed by the PMOS transistor TP3 and the NMOS transistor TN3 is off, the collision between the logic B and the logic B bar does not occur at the node J3.

[0067]

When the logic A is “L”, the nodes J1 and J2 are “H” and “L”, respectively. Accordingly, both the transistors TP3 and TN3 are turned on, and the logic B is supplied as the logic Z to the node J3. On the other hand, when the logic B is “H”, the logic “H” at the node J1 is transmitted to the node J3 by the NMOS transistor TN2, and when the logic B is “L”, the logic “H” at the node J2 is transmitted by the PMOS transistor TP2. L ″ is transmitted to the node J3. Therefore, in any case, the logic B is given as the logic Z at the node J3.

[0068]

From the above operation, the circuit of FIG. 7 gives the XOR of logic A and B. In order to obtain a value complementary to the exclusive OR (XNOR: exclusive NOR), the output may be further inverted, or only one of the logic A and the logic B is inverted to obtain the XOR. May be input to the circuit.

[0069]

FIG. 10 is a circuit diagram showing a modification of the present embodiment. Compared to the configuration shown in FIG. 2, the transistor MN9 whose switching is controlled by the logic of the

[0070]

FIG. 11 is a schematic view illustrating the configuration of the pass transistors MN9, MN10, MN11, and MN12. For simplicity, the storage cell SC has inverters L1 and L2 indicated by symbols, while the pass transistors MN9, MN10, MN11, and MN12 have

[0071]

FIG. 11 will be described in accordance with the configuration shown in FIG. Pass transistors MN9 and MN10 are formed in the active region R1. One of the current electrode pairs of the pass transistor MN9 is connected to the node N1, and one of the current electrode pairs of the pass transistor MN10 is connected to the

[0072]

A gate line G1 that functions as the gates of the pass transistors MN9 and MN11 and a gate line G2 that functions as the gates of the pass transistors MN10 and MN12 are located above the active regions R1 and R2 via a gate insulating film (not shown). It is laid on the front side of the page. The

[0073]

Since the pass transistors MN9 and MN10 share the source / drain region SD1 and the pass transistors MN11 and MN12 share the source / drain region SD2 as described above, they can be arranged in a small area.

[0074]

The

[0075]

FIG. 12 is a conceptual diagram showing a configuration around the memory cell array of the SRAM according to the second embodiment of the present invention. In contrast to the SRAM configuration shown in the first embodiment, a

[0076]

Write

[0077]

FIG. 13 is a circuit diagram illustrating one configuration of the memory cell MC shown in FIG. As in the prior art, subscripts indicating row positions and column positions are omitted. Compared with the configuration shown in FIG. 2, the memory cell MC is additionally provided with pass transistors MP9, MP10, MP11, and MP12 which are PMOS transistors, and a write

[0078]

The pass transistors MP9, MP10, MP11, and MP12 are connected in parallel with the pass transistors MN9, MN10, MN11, and MN12, respectively. The logic given to the gates of the pass transistors MP9, MP10, MP11, MP12 is complementary to the logic given to the gates of the pass transistors MN9, MN10, MN11, MN12, respectively. That is, the gates of the pass transistors MP9 and MP11 are connected to the write

[0079]

Therefore, the pass transistors MP9, MP10, MP11, and MP12 constitute a transmission gate together with the pass transistors MN9, MN10, MN11, and MN12, respectively. Therefore, as compared with the configuration shown in FIG. 2, when logic “H” is transmitted from the

[0080]

FIG. 14 is a circuit diagram showing a modification of the present embodiment, and corresponds to FIG. 10 according to the first embodiment. That is, in the configuration shown in FIG. 14, the positions of the transmission gates formed by the pass transistors MN9 and MP9 and the transmission gates formed by the pass transistors MN10 and MP10 are compared with the configuration shown in FIG. , N4, and the positions of the transmission gate formed by the pass transistors MN11 and MP11 and the transmission gate formed by the pass transistors MN12 and MP12 are switched between the nodes N2 and N5. It is natural that the effects of the present embodiment can be obtained even with such a configuration.

[0081]

Of course, similarly to the pass transistors MN9 and MN10, the pass transistors MP9 and MP10 can also share a source / drain region to save a necessary area. The same applies to the pass transistors MP11 and MP12.

[0082]

Even if the access transistor is replaced with a transmission gate, the threshold value V due to the substrate effect is applied.thnA decrease in minutes can be avoided. FIG. 15 is a circuit diagram of FIG. 52 in which a write

[0083]

Similarly to the configuration shown in FIG. 14, the conduction of the transistors MN10 and MN12 is controlled by the logic of the

[0084]

FIG. 16 is a circuit diagram illustrating one configuration of the memory cell MC according to the present embodiment. As in the prior art, the subscripts indicating the row position and the column position are omitted, but the MC shown in FIG.ijCan be adopted as each of.

[0085]

Compared to the configuration shown in FIG. 52, memory cell MC is provided with access transistors MN2 and MN4 and control transistors MN1 and MN3, both of which are NMOS transistors, instead of access transistors QN3 and QN4.

[0086]

Similar to access transistor QN3, access transistor MN2 controls conduction between nodes N1 and N4. The gate is common to the access transistor QN3 in that a

[0087]

Since the gates of the control transistors MN1 and MN3 are connected to the

[0088]

The above configuration is disadvantageous compared to the configuration described in the first embodiment in that the control transistor MN1 and the access transistor MN2 or the control transistor MN3 and the access transistor MN4 cannot share the source and drain.

[0089]

However, the control transistors MN1 and MN3 are both turned on depending on the logic on the

[0090]

FIG. 18 is a circuit diagram illustrating one configuration of the memory cell MC according to the present embodiment. As in the prior art, the subscripts indicating the row position and the column position are omitted, but the MC shown in FIG.ijCan be adopted as each of. In the memory cell MC, the control transistors MN1 and MN3 are replaced with control transistors MN5 and MN6 as compared to the configuration shown in FIG.

[0091]

The gates of the control transistors MN5 and MN6 are commonly connected to the

[0092]

The above configuration is disadvantageous compared to the configuration described in the first embodiment in that the control transistor MN5 and the access transistor MN2 or the control transistor MN6 and the access transistor MN4 cannot share the source and drain.

[0093]

However, the control transistors MN5 and MN6 are both turned on depending on the logic on the

[0094]

Embodiment 5 FIG.

FIG. 20 is a circuit diagram illustrating one configuration of the memory cell MC according to this embodiment. As in the prior art, the subscripts indicating the row position and the column position are omitted, but the MC shown in FIG.ijCan be adopted as each of. However, the auxiliary

[0095]

As a first difference, the transistor QN9 is not directly connected to the node N1, and the pass transistor MN9 is interposed between the two. Similarly, the transistor QN11 is not directly connected to the node N2, and a pass transistor MN11 is interposed between the two. As in the first embodiment, the gates of the pass transistors MN9 and MN11 are connected to the

[0096]

The second difference is that the potential VDDPotential point (hereinafter “potential point VDD) And the node N8, transistors MP3 and MP4, both of which are PMOS transistors, are connected in series. Similarly, the potential point VDDTransistors MP5 and MP6, both of which are PMOS transistors, are connected in series between the node N9 and the node N9. In either of the transistors MP4 and MP6, the potential V is applied to one of the current electrode pairs.DDIs applied, and a write

[0097]

In the above configuration, the transistors MP3 and MP4 that can set the node N1 to “H” from the outside of the storage cell SC and the transistors MP5 and MP6 that can set the node N2 to “H” are provided. Thus, it is possible to quickly perform writing to invert the stored contents. Moreover, the conduction between the nodes N1 and N8 and the conduction between the nodes N2 and N9 depend on the logic of the

[0098]

Transistors MP3, MP4, QN9, and QN10 and transistors MP5, MP6, QN11, and QN12 constitute a tri-state inverter having nodes N8 and N9 as output terminals, respectively. The operation of the memory cell MC according to the present embodiment will be described below from the viewpoint of the operation of these tristate inverters.

[0099]

These tri-state inverters function as inverters only when the

[0100]

In the

[0101]

In the memory cells MC arranged in the row corresponding to the selected

[0102]

In order to avoid a voltage drop corresponding to the threshold value of the pass transistors MN9 and MN10 due to the substrate effect, these may be replaced with a transmission gate. Alternatively, the potential of the

[0103]

FIG. 21 is a circuit diagram showing a configuration of the memory cell MC according to the first modification of the present embodiment. The configuration shown in FIG. 20 has a configuration in which the order of series connection of transistors QN9 and QN10 is changed, and the order of series connection of transistors QN11 and QN12 is changed. Naturally, the effect of the present embodiment can be obtained even in such a modification.

[0104]

FIG. 22 is a circuit diagram showing a configuration of the memory cell MC according to the second modification of the present embodiment. In contrast to the configuration shown in FIG. 21, the transistors MP3, MP4, MP5, and MP6 that supply the logic “H” to the storage cell SC are deleted. Further, the order of series connection of the pass transistor MN9 and the transistor QN10 and the order of series connection of the pass transistor MN11 and the transistor QN12 are interchanged.

[0105]

Or, compared with the circuit shown in FIG. 53, the node N1 and the potential point VV of the transistors QN9 and QN10.SSA pass transistor MN9 whose conduction is controlled by logic in the

[0106]

In such a configuration, “H” cannot be set to the storage cell SC from the outside. Therefore, it is disadvantageous in that writing that reverses the contents stored in the storage cell SC cannot be performed quickly. However, as compared with the configuration shown in FIGS. 20 and 21, there is an advantage that the write

[0107]

Of course, there are six series connection orders of the transistors QN10, MN9, and QN9, and it is natural that the above-described effects can be obtained regardless of which order is employed. The same applies to the order of series connection of the transistors QN12, MN11, and QN11.

[0108]

FIG. 23 is a circuit diagram of a dual write port type static memory cell according to a third modification of the present embodiment. Here, two sets of tri-state inverters corresponding to the word line group (excluding the read

[0109]

Even in such a dual write port type static memory cell, it is natural that when the stored contents of the storage cell SC are inverted, it can be stored quickly, and unnecessary power consumption due to potential collision can be reduced.

[0110]

FIG. 24 is a circuit diagram showing a configuration of the memory cell MC according to the fourth modification of the present embodiment. In contrast to the configuration shown in FIG. 21, the configuration of an element interposed between the node N8 serving as the output terminal of the tristate inverter and the transistors MP3 and QN9 and the node N1, and the node N9 serving as the output terminal of another tristate inverter. The configuration of the elements interposed between the transistors MP5 and QN11 and the node N2 is changed.

[0111]

The node N8 is connected to the transistor MP3 via the PMOS transistor MP9, to the transistor QN9 via the NMOS transistor MN9, and via the NMOS transistor QN10.TenoAre connected to the node N1, respectively. The node N9 is connected to the transistor MP5 via the PMOS transistor MP11, to the transistor QN11 via the NMOS transistor MN11, and via the NMOS transistor QN12.TenoAre connected to the node N2, respectively.

[0112]

In this modification, the write

[0113]

In the selected row, the

[0114]