JP4624207B2 - Film forming method and film forming apparatus - Google Patents

Film forming method and film forming apparatus Download PDFInfo

- Publication number

- JP4624207B2 JP4624207B2 JP2005225709A JP2005225709A JP4624207B2 JP 4624207 B2 JP4624207 B2 JP 4624207B2 JP 2005225709 A JP2005225709 A JP 2005225709A JP 2005225709 A JP2005225709 A JP 2005225709A JP 4624207 B2 JP4624207 B2 JP 4624207B2

- Authority

- JP

- Japan

- Prior art keywords

- gas

- film

- gate electrodes

- film forming

- oxygen

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Formation Of Insulating Films (AREA)

- Chemical Vapour Deposition (AREA)

Description

本発明は、例えば層間絶縁膜として用いられるシリコン酸化膜の成膜方法及び成膜装置に関するものである。 The present invention relates to a method and apparatus for forming a silicon oxide film used as, for example, an interlayer insulating film.

MOSFETトランジスタでは、ソース領域とドレイン領域との間のゲート絶縁膜上にゲート電極が形成され、このゲート電極により、ソースードレイン領域間に流れる電流が制御される。前記ゲート電極としては、低抵抗化を図るために金属製のゲート電極が主流になりつつあり、本発明者らは、図6に示すように、ポリシリコン層10と、窒化タングステン(WN)層11と、タングステン(W)層12とを下側からこの順番で積層した金属製ゲート電極1A,1Bを用いることを検討している。なお図中18はゲート絶縁膜である。

In a MOSFET transistor, a gate electrode is formed on a gate insulating film between a source region and a drain region, and a current flowing between the source and drain regions is controlled by the gate electrode. As the gate electrode, a metal gate electrode is becoming mainstream in order to reduce the resistance. As shown in FIG. 6, the present inventors have made a

ところでMOSFETトランジスタでは、ゲート電極1A,1Bを形成した後、これらゲート電極1A,1B間に層間絶縁膜13を形成しているが、近年のデバイスの微細化や高集積化に伴い、これらゲート電極1A,1B間の凹部14のアスペクト比が例えば4以上と大きくなっている。このようなアスペクト比の高いゲート電極1A,1B間の凹部14を埋め込むための層間絶縁膜13としては従来よりBPSG膜が広く用いられている。このBPSG膜は、ボロン(B)及びリン(P)がドープされたシリケートガラス膜である。

By the way, in the MOSFET transistor, after forming the

しかしながらこのBPSG膜13は、成膜温度は600℃程度であるが、前記ゲート電極1A,1B間の凹部14にメルティングさせて埋め込むために850℃程度の高温で処理を行うことが必要であり、この処理時に金属製のゲート電極1A,1Bが高温に晒されると、形成されたMOSFETトランジスタの全体の抵抗が大きくなるという問題がある。

However, the BPSG

この理由については、前記ゲート電極1A,1Bでは、WN層11は抵抗が大きいので、それ程厚くできず、このため前記WN層11は厚さ5nm程度と薄くせざるを得ないが、このように薄いとゲート電極1A,1Bが高温に晒されたときに、このWN層11のWとポリシリコン層10とが反応してしまい、これにより抵抗の高いWSiが生成されてしまうためと推察される。

For this reason, in the

そこで、前記層間絶縁膜13をより低温で形成するために、BPSG膜の代わりとして、原料ガスとして有機シラン系のガス例えばTEOS(テトラエチルオルソシリケート)ガスと、アミノシラン系のガス例えばビスターシャルブチルアミノシランガスとを用いて化学気相成長法(CVD法)によりSiO2膜を形成することも検討したが、このプロセスでの成膜温度は680℃であって、低温化が不十分である上、この手法により形成されたSiO2膜は、図7(a)に示すボイド15や、図7(b)に示すシーム16等の空隙が形成されやすいという問題がある。図7中17はシリコン基板である。

Therefore, in order to form the

この理由については、このCVDプロセスは、TEOSガスを気相中で分解して、SiO2をゲート電極1A,1B間の凹部14に埋め込むものであるが、例えば図8(a)に示すように、気相中にて発生したTEOSガスの分解物18はゲート電極1A,1B上に降り積もるように付着するため、図8(b)に示すように、ゲート電極1A,1Bの上面や、これらの間の凹部14の底部には付着しやすいが、ゲート電極1A,1Bの側面には付着しにくい。このため図8(b),(c)に示すように、2つのゲート電極1A,1Bの上面の膜厚は大きく、側面の膜厚は小さくなってしまうので、上面からせり出したようにSiO2が付着しやすく、結果として図8(d)に示すように、2つのゲート電極間1A,1Bにボイド15が形成されてしまうためと推察される。

For this reason, this CVD process decomposes TEOS gas in the gas phase and embeds SiO2 in the

また仮にゲート電極間1A,1Bの凹部14にボイド15を形成せずにSiO2膜を埋め込んだ場合であっても、このSiO2膜の形成後に、SiO2膜が埋め込まれた凹部14のソース電極とドレイン電極の上部にコンタクトホールと呼ばれる貫通孔を形成し、フッ酸(HF)にて当該ホールの底面を洗浄する工程を行なう際に、この工程にて使用したフッ酸がコンタクトホールから染み出し、これによりこのフッ酸によって凹部14の中央部付近においてSiO2膜がエッチングされて、シーム16と呼ばれる空隙が形成されてしまう。

Even if the SiO2 film is embedded without forming the

ここでTEOSガスを用いたCVDプロセスでは、SiO2生成とアルコール等の不純物の脱離が同時に起こってSiO2が成膜されていくが、SiO2膜は既述のようにゲート電極1A,1B間の凹部14に対して、この凹部14の両側(夫々のゲート電極1A,1Bの側壁側)から凹部14の中央に向かって順に埋め込まれていくので、最後の埋め込みの瞬間は、凹部14の両側から形成されたSiO2膜の壁が両側から閉じる状態となり、不純物が抜け出して行きにくい。このためこの部分については膜が不純物を含む状態であって脆いので、前記フッ酸がアタックしやすくなり、結果としてフッ酸によりエッチングされてシーム16が形成してしまうものと考えられる。

Here, in the CVD process using the TEOS gas, SiO2 formation and desorption of impurities such as alcohol occur at the same time to form SiO2, but the SiO2 film has a concave portion between the

ここで層間絶縁膜の形成方法としては、原料ガスとしてTEOSガスとO3(オゾン)ガスとを用いて、2.66kPa(20Torr)未満の圧力、300℃以上500℃未満の温度でCVD処理を行う技術(特許文献1)や、TEOSガスと、オゾン含有酸素ガス(O3含有O2ガス)と、O2と組み合わせてH2Oを生成するガス例えばH2O2ガス等を用い、圧力1.33Pa(10Torr)、成膜温度200℃の処理条件でプラズマCVD処理を行う技術(特許文献2)等の種々の特許文献が存在する。 Here, as a method for forming an interlayer insulating film, a CVD process is performed at a pressure of less than 2.66 kPa (20 Torr) and a temperature of 300 ° C. or more and less than 500 ° C. using TEOS gas and O 3 (ozone) gas as source gases. Using a technology (Patent Document 1), a TEOS gas, an ozone-containing oxygen gas (O3-containing O2 gas), and a gas that generates H2O in combination with O2, such as H2O2 gas, a pressure of 1.33 Pa (10 Torr) is used. There are various patent documents such as a technique (Patent Document 2) for performing a plasma CVD process under a process condition of a temperature of 200 ° C.

しかしながら特許文献1の技術は、当該文献1中にもTEOS含有ガスとO3含有ガスが気相中で反応しやすいと記載されるように、気相中にてTEOSを分解してCVD処理を行なうものであるので、結局図8に示すメカニズムにて成膜が進行し、アスペクト比が4以上の高アスペクト比のゲート電極1A,1B間を、ボイド15やシーム16を形成せずに埋め込むには不十分である。

However, the technique of Patent Document 1 performs the CVD process by decomposing TEOS in the gas phase as described in the document 1 that the TEOS-containing gas and the O 3 -containing gas easily react in the gas phase. Therefore, in the end, the film formation proceeds by the mechanism shown in FIG. 8 and the gap between the high aspect

また特許文献2の技術は、プラズマCVDであって、TEOSガスとO3含有O2ガスとH2O2ガスとはプラズマにより分解されるので、この場合においても結局気相中にてTEOSを分解して成膜を行なっており、このため図8に示すメカニズムにて成膜が進行し、高アスペクト比のゲート電極1A,1B間を、ボイド15やシーム16を形成せずに埋め込むには不十分である。

The technique of Patent Document 2 is plasma CVD, in which TEOS gas, O3-containing O2 gas, and H2 O2 gas are decomposed by plasma. Even in this case, TEOS is eventually decomposed in the gas phase to form a film. For this reason, film formation proceeds by the mechanism shown in FIG. 8, which is insufficient for embedding between the high aspect

そこで、集積回路の多層配線構造のゲート電極1A,1Bが形成された層の層間絶縁膜13として、ゲート電極1A,1Bへの悪影響を抑制するために例えば500℃以下の低い温度で成膜することができ、ゲート電極1A,1B間の高アスペクト比の凹部14を隙間なく埋め込めるようにカバレッジが良好であり、さらにフッ酸等のフッ素(F)を含む薬液に対して耐性が十分にあるという要請を満足する層間絶縁膜の開発が求められている。

Therefore, the

本発明は、このような事情の下になされたものであり、その目的は、低い成膜温度で、カバレッジ性が良好なシリコン酸化膜を形成することができる技術を提供することにある。 The present invention has been made under such circumstances, and an object of the present invention is to provide a technique capable of forming a silicon oxide film with good coverage at a low film formation temperature.

このため本発明の成膜方法は、被処理体が載置された処理容器内を減圧雰囲気及び加熱雰囲気にして、有機系シリコンソースの蒸気を用いて被処理体にシリコン酸化膜を形成する方法において、

前記処理容器内を前記有機系シリコンソースの蒸気の分解温度よりも低くかつ酸素ガス及び水素ガスにより水酸基活性種及び酸素活性種が発生する温度に加熱し、

前記処理容器内に供給された前記有機系シリコンソースを、前記処理容器内に供給された酸素ガス及び水素ガスにより発生した水酸基活性種及び酸素活性種により分解して、前記被処理体にシリコン酸化膜を形成することを特徴とする。

有機系シリコンソースは、例えばテトラエチルオルソシリケートガス及びビスターシャルアミノシランガスから選択されるものである。

For this reason, the film forming method of the present invention is a method of forming a silicon oxide film on a target object by using a vapor of an organic silicon source in a reduced pressure atmosphere and a heated atmosphere in a processing container in which the target object is placed. In

The inside of the processing vessel is heated to a temperature lower than the decomposition temperature of the vapor of the organic silicon source and to generate hydroxyl active species and oxygen active species by oxygen gas and hydrogen gas ,

The organic silicon source supplied into the processing vessel is decomposed by hydroxyl active species and oxygen active species generated by the oxygen gas and hydrogen gas supplied into the processing vessel, and silicon dioxide is oxidized on the object to be processed. A film is formed.

The organic silicon source is selected from, for example, tetraethylorthosilicate gas and binary aminosilane gas .

また前記被処理体は例えば複数のゲート電極が形成されたものであり、前記シリコン酸化膜は、例えばこれらゲート電極間を埋め込むように、ゲート電極の上に形成される層間絶縁膜として用いることができる。 Further, the object to be processed is formed, for example, with a plurality of gate electrodes, and the silicon oxide film is used as an interlayer insulating film formed on the gate electrodes so as to embed between the gate electrodes, for example. it can.

また本発明の成膜装置は、内部に被処理体が載置される処理容器と、

前記処理容器内を減圧雰囲気に設定する圧力調整手段と、

前記処理容器内を加熱するための加熱手段と、

前記処理容器内に有機系シリコンソースの蒸気を供給するための成膜ガス供給路と、

前記処理容器内に酸素ガスを供給するための酸化性ガス供給路と、

前記処理容器内に水素ガスを供給するための還元性ガス供給路と、

前記成膜ガス供給路と、酸化性ガス供給路と、還元性ガス供給路とに夫々設けられ、夫々有機系シリコンソースの蒸気と酸素ガスと水素ガスとの流量を調整するための流量調整手段と、

前記圧力調整手段と加熱手段と流量調整手段とを制御するための制御部と、を備え、

前記制御部は、前記処理容器内を減圧雰囲気に設定すると共に、有機系シリコンソースの蒸気の分解温度よりも低い温度で加熱することにより、酸素ガス及び水素ガスにより発生した水酸基活性種及び酸素活性種を用いて、前記被処理体の上にシリコン酸化膜を形成するように、前記圧力調整手段と加熱手段と流量調整手段とを制御することを特徴とする。

Further, the film forming apparatus of the present invention includes a processing container in which an object to be processed is placed,

Pressure adjusting means for setting the inside of the processing vessel to a reduced pressure atmosphere;

Heating means for heating the inside of the processing vessel;

A film forming gas supply path for supplying vapor of the organic silicon source into the processing container;

An oxidizing gas supply path for supplying oxygen gas into the processing vessel;

A reducing gas supply path for supplying hydrogen gas into the processing vessel;

Flow rate adjusting means provided in the film forming gas supply path, the oxidizing gas supply path, and the reducing gas supply path, respectively, for adjusting the flow rates of the vapor , oxygen gas, and hydrogen gas of the organic silicon source. When,

A control unit for controlling the pressure adjusting means, the heating means, and the flow rate adjusting means,

The control unit sets the inside of the processing container to a reduced pressure atmosphere and heats it at a temperature lower than the decomposition temperature of the vapor of the organic silicon source to thereby generate hydroxyl active species and oxygen activity generated by oxygen gas and hydrogen gas. The pressure adjusting means, the heating means, and the flow rate adjusting means are controlled so as to form a silicon oxide film on the object to be processed using a seed.

本発明によれば、有機系シリコンソースの蒸気と、酸素ガスと、水素ガスとを用い、減圧雰囲気の下で有機系シリコンソースの蒸気の分解温度よりも低い温度で加熱することにより、酸素ガス及び水素ガスにより発生した水酸基活性種及び酸素活性種を用いて、シリコン酸化膜を形成しているので、前記有機系シリコンソースの蒸気の分解温度よりも低い成膜温度でシリコン酸化膜を形成することができる。

According to the present invention, a vapor of organic silicon source, and oxygen gas, a hydrogen gas, by heating at a temperature lower than the decomposition temperature of the vapor of the organic silicon source under a reduced pressure atmosphere, an oxygen gas Since the silicon oxide film is formed using hydroxyl active species and oxygen active species generated by hydrogen gas , the silicon oxide film is formed at a deposition temperature lower than the vapor decomposition temperature of the organic silicon source. be able to.

この際、シリコン酸化膜は、被処理体の上に有機系シリコンソースの蒸気を分解させずに吸着させ、次いで水酸基活性種及び酸素活性種により被処理体に吸着された有機系シリコンソースの蒸気を分解することにより形成されるものと推察され、このように形成されたシリコン酸化膜はカバレッジ性が良好である。またラジカル酸化にて形成されるので膜質が強固であり、こうして形成されたシリコン酸化膜はフッ素を含む薬液に対する耐性が大きい。

At this time, the silicon oxide film adsorbs the organic silicon source vapor on the object to be processed without decomposing, and then the organic silicon source vapor adsorbed on the object by the hydroxyl active species and oxygen active species. It is presumed that the silicon oxide film is formed by decomposing, and the silicon oxide film thus formed has good coverage. Further, since the film is formed by radical oxidation, the film quality is strong, and the silicon oxide film thus formed has a high resistance to a chemical solution containing fluorine.

このため例えばこのようなシリコン酸化膜を複数のゲート電極が形成された層の層間絶縁膜として用いる場合には、隣接する2つのゲート電極間の埋め込み特性が良好である。また前記成膜ガスを分解させない程度の低温で処理が行われるため、ゲート電極が金属を含むものであっても、ゲート電極が高温に晒されることにより発生する悪影響の発生を抑えることができる。 Therefore, for example, when such a silicon oxide film is used as an interlayer insulating film of a layer in which a plurality of gate electrodes are formed, the filling characteristics between two adjacent gate electrodes are good. Further, since the processing is performed at a low temperature that does not decompose the film forming gas, even if the gate electrode contains a metal, it is possible to suppress an adverse effect that occurs when the gate electrode is exposed to a high temperature.

本発明の手法により形成されるシリコン酸化膜である二酸化シリコン膜(SiO2膜)は、例えば集積回路の多層配線構造の金属製のゲート電極が形成された層の層間絶縁膜として用いられる。ここで金属製のゲート電極を備えたMOSFETトランジスタにおける、ゲート電極が形成された層の構造について図1を用いて簡単に説明する。このMOSFETトランジスタはP型Si基板20に、Nウェル21とPウェル22とが形成され、前記Nウェル21の表面近傍には、P+型のソース/ドレイン領域21a,21bが形成され、その上にゲート電極3Aが設けられている。また前記Pウェル22の表面近傍には、N+型のソース/ドレイン領域22a,22bが形成され、その上にゲート電極3Bが設けられている。

A silicon dioxide film (SiO2 film) which is a silicon oxide film formed by the method of the present invention is used as an interlayer insulating film of a layer in which a metal gate electrode of a multilayer wiring structure of an integrated circuit is formed, for example. Here, a structure of a layer in which a gate electrode is formed in a MOSFET transistor having a metal gate electrode will be briefly described with reference to FIG. In this MOSFET transistor, an N well 21 and a P well 22 are formed on a P

図中23はSiO2膜、24a、25aは夫々P+型のソース領域21a,N+型のソース領域22aに接続するソース電極であり、24b、25bは夫々P+型のドレイン領域21b,N+型のドレイン領域22bに接続するドレイン電極であって、これらソース電極24a,25a、ドレイン電極24b,25bは例えばアルミニウム(Al)により構成される。図中26はNウェル21とPウェル22との間に形成されるフィールドSiO2膜である。

In the figure,

前記ゲート電極3A,3Bは共に、ポリシリコン層31とWN層32とW層33とを下側からこの順序で積層して構成され、ゲート電極3A,3Bの側壁にはサイドスペーサ34が形成されている。前記ゲート電極3A,3Bのポリシリコン層31は厚さ60nm、WN層32は厚さ5nm、W層33は厚さ40nm程度に形成され、これらゲート電極3A、3B間に形成される凹部35の幅は例えば60nm程度、各ゲート電極3A、3Bの高さは例えば250nm程度に夫々設定され、これにより前記ゲート電極3A,3B間の凹部35のアスペクト比は4以上となる。

Both the

このようなゲート電極3A,3Bの間は例えば本発明の手法により形成されたSiO2膜よりなる層間絶縁膜4が埋め込まれており、この層間絶縁膜4は例えば厚さが65nm程度に設定される。図中37は、ゲート電極3A,3Bの上面に接触するように形成されたビアホールと呼ばれる貫通孔、38はP+型のソース電極24a,N+型のソース電極25a、P+型のドレイン電極24b、N+型のドレイン電極24bの上面に接触するように形成されたコンタクトホールと呼ばれる貫通孔である。

An interlayer insulating film 4 made of, for example, a SiO2 film formed by the method of the present invention is buried between the

続いて本発明の成膜方法を実施するための成膜装置の一例について図2を用いて説明する。図2中5は、例えば石英により縦型の円筒状に形成された処理容器を成す反応容器であり、この反応容器5の下端は、炉口として開口され、その開口部51の周縁部にはフランジ52が一体に形成されている。前記反応容器5の下方には、フランジ52の下面に当接して開口部51を気密に閉塞する、例えば石英製の蓋体53が図示しないボートエレベータにより上下方向に開閉可能に設けられている。蓋体53の中央部には、回転軸54が貫通して設けられ、その上端部には、被処理体保持具であるウエハボート55が搭載されている。

Next, an example of a film forming apparatus for carrying out the film forming method of the present invention will be described with reference to FIG. In FIG. 2, 5 is a reaction vessel that forms a processing vessel formed of, for example, quartz in a vertical cylindrical shape, and the lower end of the reaction vessel 5 is opened as a furnace port, The

このウエハボート55は、3本以上例えば4本の支柱56を備えており、複数枚例えば125枚の被処理体である半導体ウエハ(以下「ウエハ」という)Wを棚状に保持できるように、前記支柱56に溝(スロット)が形成されている。但し、125枚のウエハWの保持領域の内、上下両端部については複数枚のダミーウエハが保持され、その間の領域に製品ウエハが保持されることになる。前記回転軸54の下部には、当該回転軸54を回転させる駆動部をなすモータMが設けられており、従ってウエハボート55はモータMにより回転することになる。また蓋体53の上には前記回転軸54を囲むように保温ユニット57が設けられている。

The

前記反応容器5の下部のフランジ52には、反応容器5内のウエハWにガスを供給するためのL字型のインジェクタ61が挿入して設けられている。インジェクタ61の基端側には、ガス供給路であるガス供給管62が接続されており、ガス供給管62の他端側は、夫々流量調整手段をなす流量調整バルブV1,V2,V3を介して成膜ガス供給源63と、酸化性ガス例えば酸素(O2)ガスの供給源64と、還元性ガス例えば水素(H2)ガスの供給源65とに接続され、前記ガス供給管62、インジェクタ61を介して反応容器5の中に成膜に必要なガスを供給できるようになっている。ここでガス供給管62、成膜ガス供給源63、酸素ガスの供給源64、水素ガスの供給源65、流量調整バルブV1,V2,V3によりガス供給部6が構成されている。またガス供給部6の成膜ガス供給源63の下流側が成膜ガス供給路、ガス供給部6の酸素ガス供給源64の下流側が酸化性ガス供給路、ガス供給部6の水素ガス供給源65の下流側が還元性ガス供給路に夫々相当する。

An L-shaped

前記成膜ガスとしては、有機系シリコンソースの蒸気、例えばTEOSガス、BTBAS(ビスターシャルアミノシラン)ガス等や、無機系シリコンソースの蒸気、例えばモノシランガス、クロロシランガス、ヘキサクロロジシラン(HCD)ガス等を用いることができる。さらに酸化性ガスとしては酸素ガスの他に、N2Oガス、NOガス、NO2ガスよりなる群から選択される1つ以上のガスを用いることができ、還元性ガスとしては水素ガスの他に、NH3ガス、CH4ガス、HClガスよりなる群から選択される1つ以上のガスを用いることができる。 As the film forming gas, an organic silicon source vapor, for example, TEOS gas, BTBAS (Bistal aminosilane) gas, or the like, or an inorganic silicon source vapor, for example, monosilane gas, chlorosilane gas, hexachlorodisilane (HCD) gas, or the like is used. be able to. Furthermore, as the oxidizing gas, in addition to oxygen gas, one or more gases selected from the group consisting of N 2 O gas, NO gas, and NO 2 gas can be used, and the reducing gas can be hydrogen gas or the like. In addition, one or more gases selected from the group consisting of NH 3 gas, CH 4 gas, and HCl gas can be used.

さらに反応容器5の上方には、反応容器5内を排気するための排気口7が形成されている。この排気口7には、反応容器5内を所望の真空度に減圧排気可能な真空排気手段をなす真空ポンプ71及び圧力調整手段72を備えた排気管73が接続されている。反応容器5の周囲には、反応容器5内を加熱するための加熱手段であるヒータ74を備えた加熱炉75が設けられている。前記ヒータ74としては、コンタミネーションがなく昇降温特性が優れたカーボンワイヤー等を用いることが好ましい。

Further, an exhaust port 7 for exhausting the inside of the reaction vessel 5 is formed above the reaction vessel 5. Connected to the exhaust port 7 is an

さらにこの成膜装置は、コンピュータからなる制御部100を備えている。この制御部100は、処理プログラムを起動し、図示しないメモリ内のプロセスレシピの記載事項を読み出して、そのレシピに基づいて処理条件を制御する機能を有し、ヒータ74、圧力調整手段72及びガス供給部6を夫々制御するための制御信号を出力する。

Further, this film forming apparatus includes a

次に上述の成膜装置を用いて実施する成膜方法の一例について説明する。先ず被処理体である半導体ウエハW、例えば図1に示すようなP型Si基板20上にゲート電極3A,3Bやソース電極24a,25a、ドレイン電極24b,25bが形成されたウエハWを所定枚数ウエハボート55に保持させて、例えば温度が100℃程度に維持された反応容器5内に、図示しないボートエレベータを上昇させることにより搬入(ロード)する。

Next, an example of a film formation method performed using the above-described film formation apparatus will be described. First, a predetermined number of semiconductor wafers W to be processed, such as wafers W on which

続いてウエハボート55が搬入されて反応容器5の下端開口部51が蓋体53により塞がれた後、反応容器5内の温度を例えば200℃/分の昇温速度で、TEOSガスの分解温度よりも低い温度例えば500℃程度まで昇温させると共に、反応容器5内を排気口7を通じて真空ポンプ71により例えば266Pa(2Torr)程度の真空度に真空排気する。

Subsequently, after the

ここで前記TEOSガスの分解温度よりも低い温度とは、当該減圧雰囲気でTEOSガスが分解せず、かつ酸素ガス及び水素ガスにより活性種が生成される温度をいい、例えば266PaでのTEOSガスの分解温度が例えば550℃程度であり、酸素ガス及び水素ガスは例えば1.33kPa(10Torr)以下の減圧下で水酸基活性種や酸素活性種等の活性種を生成するので、当該減圧雰囲気では例えば350℃以上550℃未満の温度をいう。 Here, the temperature lower than the decomposition temperature of the TEOS gas means a temperature at which the TEOS gas is not decomposed in the reduced pressure atmosphere and active species are generated by the oxygen gas and the hydrogen gas. For example, the temperature of the TEOS gas at 266 Pa is The decomposition temperature is about 550 ° C., for example, and oxygen gas and hydrogen gas generate active species such as hydroxyl active species and oxygen active species under a reduced pressure of, for example, 1.33 kPa (10 Torr) or less. It means a temperature of not lower than ℃ and lower than 550 ° C.

またTEOSガスと酸素ガス、水素ガスの流量については、TEOSガスと酸素ガスと水素ガスの流量比が、0.1〜0.2:2:1程度とするのが好ましく、減圧雰囲気とは1.33kPa(10Torr)以下が好ましい。 Regarding the flow rates of TEOS gas, oxygen gas and hydrogen gas, the flow rate ratio of TEOS gas, oxygen gas and hydrogen gas is preferably about 0.1 to 0.2: 2: 1. .33 kPa (10 Torr) or less is preferable.

そして反応容器5内の温度を例えば500℃に安定させた後、成膜ガス供給源63から例えばTEOSガスを所定の流量例えば150sccm、酸素ガス供給源64から酸素ガスを所定の流量例えば2000sccm、水素ガス供給源65から水素ガスを所定の流量例えば1000sccmで反応容器5内に供給し、更に圧力調整手段72により反応容器5内を例えば266Pa(2Torr)の減圧雰囲気に調整して成膜工程を10分程度行う。このようにすると反応容器5内では、後述するように、SiO2膜がウエハW上のゲート電極3A,3B間を埋め込むように成膜される。

Then, after stabilizing the temperature in the reaction vessel 5 at, for example, 500 ° C., for example, a TEOS gas from the film forming

これら一連の工程を行っている間、ウエハボート55はモータMにより回転している。こうしてゲート電極3A,3B上に所定の厚さ例えば50nmでSiO2膜を形成した後、反応容器5内への成膜ガスの供給を停止する。また、図示しない窒素ガス源からN2ガスの供給を開始してパージを行い、反応容器5内の圧力を大気圧に戻すと共に、反応容器5内の温度を例えば200℃の設定された温度まで下降させ、ウエハボート55を反応容器5から搬出(アンロード)する。ここでこの成膜装置において行なわれるSiO2膜の形成のための一連の工程は、制御部100に格納されたプロセスレシピに基づいて、ヒータ74、圧力調整手段72及びガス供給部6等を制御して行なわれる。

During the series of steps, the

そして搬出されたウエハWは、その後、ビアホール37やコンタクトホール38が形成され、さらにこれらホール37,38の底面をフッ酸で洗浄し、しかる後これらビアホール37,コンタントホール38に導電体材料例えばTiNが埋め込まれて、半導体装置であるMOSFETトランジスタが製造される。

The unloaded wafer W is then formed with via

この手法は、成膜ガスであるTEOSガスを分解させずに成膜対象である固体表面に吸着させると共に、前記固体表面にてTEOSを分解する活性種を生成させ、この活性種により前記固体表面に吸着したTEOSを分解することが可能な条件を見出した結果なされたものである。 In this method, the TEOS gas that is a film forming gas is adsorbed on the solid surface to be formed without being decomposed, and active species that decompose TEOS on the solid surface are generated, and the solid surface is generated by the active species. It was made as a result of finding a condition capable of decomposing TEOS adsorbed on the surface.

つまりTEOSガスと酸素ガスと水素ガスとを用い、減圧雰囲気下で、TEOSガスの分解温度よりも低い温度で加熱することによりSiO2膜を形成しているので、後述するように、ウエハWのゲート電極3A,3Bの上にTEOSガスを分解させずに吸着させ、次いで酸素ガス及び水素ガスにより生成される活性種である水酸基活性種(OH*)と酸素活性種(O*)により、前記ゲート電極3A,3Bに吸着されたTEOSが分解されてSiO2膜よりなる層間絶縁膜4が形成される。

That is, since the SiO2 film is formed by heating at a temperature lower than the decomposition temperature of the TEOS gas under a reduced pressure atmosphere using TEOS gas, oxygen gas, and hydrogen gas, the gate of the wafer W will be described later. The TEOS gas is adsorbed on the

このためTEOSガスの分解温度より低い温度である500℃以下の低温でSiO2膜を成膜することができ、カバレッジ性が良好であって、例えばアスペクト比が4以上と大きい凹部に対してもボイドを形成することなくSiO2膜を埋め込むことができる。また既述のように500℃以下の温度で成膜処理を行なっているので、例えばポリシリコン層31とWN層32とW層33とを積層して形成した金属製のゲート電極3A,3Bを備えるトランジスタであっても、例えばゲート電極を600℃以上の高温に晒すことによって生じる、例えば抵抗が大きくなること等の悪影響の発生を抑えてゲート電極3A,3B間に層間絶縁膜4を埋め込むことができる。

For this reason, the SiO2 film can be formed at a low temperature of 500 ° C. or lower, which is a temperature lower than the decomposition temperature of the TEOS gas, and the coverage is good. The SiO2 film can be embedded without forming the film. Further, since the film forming process is performed at a temperature of 500 ° C. or less as described above, for example, the

また本発明の成膜プロセスでは、TEOSを水酸基活性種と酸素活性種により前記固体表面にて分解するというラジカル酸化によりSiO2膜を形成していると推察されるので、TEOSガスを用いてCVDプロセスにて形成されたSiO2膜よりも膜質が強固である。このため後の工程でビアホール37やコンタクトホール38の底面をフッ酸で洗浄する際にも、フッ酸に対する対抗性が大きいので、フッ酸の凹部35への浸み込みが防止でき、シームの発生を抑えることができる。

Further, in the film forming process of the present invention, it is presumed that the SiO2 film is formed by radical oxidation in which TEOS is decomposed on the solid surface by hydroxyl active species and oxygen active species. Therefore, the CVD process is performed using TEOS gas. The film quality is stronger than that of the SiO2 film formed in (1). For this reason, even when the bottom surfaces of the via

次いで本発明の経緯について説明する。先ず本発明者らは、従来のTEOSガスとO2ガスとを用いたCVDプロセスにより、アスペクト比が4以上のゲート電極間の凹部にSiO2膜を埋め込む場合にボイドが形成されるメカニズムについて検討した。この結果、背景技術の欄に記載したように、気相中でTEOSガスが分解し、この分解物が前記ゲート電極や凹部に降り積もるように付着するため、前記分解物がゲート電極の上面には付着しやすいが、側壁には付着しにくく、このため凹部の中央部においてボイドが形成されやすいのではないかと推察した。 Next, the background of the present invention will be described. First, the present inventors examined a mechanism by which voids are formed when a SiO2 film is embedded in a recess between gate electrodes having an aspect ratio of 4 or more by a conventional CVD process using TEOS gas and O2 gas. As a result, as described in the background art section, the TEOS gas is decomposed in the gas phase, and this decomposed product adheres to the gate electrode and the recess, so that the decomposed product is deposited on the upper surface of the gate electrode. Although it adheres easily, it is hard to adhere to a side wall, Therefore It was guessed that a void might be easy to be formed in the center part of a recessed part.

そこで本発明者は、TEOSガスを分解させない状態でウエハW上のゲート電極3A,3Bに付着させ、こうしてゲート電極3A,3Bに付着させた後にTEOSを分解するようにすれば、ゲート電極3A,3Bの上面や側壁、凹部35の底面に均一な厚さでTEOSが付着されるので、前記ゲート電極3A,3Bの上面や側壁、凹部35の底面に均一な厚さでSiO2膜が形成でき、ボイドの形成が抑えられるのではないかと考え、この手法の実現性について検討することとした。

Therefore, the present inventor attaches the TEOS gas to the

このため先ずTEOSガスを分解させずにゲート電極3A,3B等に吸着させるために、成膜処理の温度を反応容器5の減圧雰囲気下でTEOSガスが分解しない温度とし、前記減圧雰囲気下にてこの温度でゲート電極3A,3Bの表面において、前記ゲート電極3A,3B表面に付着したTEOSを分解するラジカル種を生成するガスを、種々の実験を行なうことにより選択した。この結果、TEOSガスを成膜ガスとし、酸素ガスと水素ガスとを添加することにより、後述の実験例からも明らかなように、前記ゲート電極3A,3Bの上面や側壁、凹部35の底面に均一な厚さでSiO2膜が形成できることを見出した。

Therefore, first, in order to adsorb the TEOS gas to the

このようにTEOSと酸素ガスと水素ガスによってSiO2膜が形成されるメカニズムについては、TEOSガスは266Paの減圧下では500℃では分解しないので、この温度では図3(a)に示すようにゲート電極3A,3B等の固体表面に分解しない状態でそのまま供給される。このため気相中にてTEOSガスが分解し、この分解物が固体表面に供給される場合に比べて、供給種が大きく、重いので、分解していないTEOSガスは降り積もるようには供給されず、これにより前記ゲート電極3A,3Bの上面や側壁、凹部35の底面に均一な厚さでTEOS41が吸着される。

Regarding the mechanism by which the SiO2 film is formed by TEOS, oxygen gas, and hydrogen gas in this way, TEOS gas does not decompose at 500 ° C. under a reduced pressure of 266 Pa. Therefore, at this temperature, as shown in FIG. It is supplied as it is without being decomposed into a solid surface such as 3A or 3B. For this reason, the TEOS gas decomposes in the gas phase, and the decomposition product is larger and heavier than when the decomposition product is supplied to the solid surface. Therefore, the undecomposed TEOS gas is not supplied so as to accumulate. Thus, the TEOS 41 is adsorbed with a uniform thickness on the top and side walls of the

一方酸素ガスや水素ガスは、例えば図3(b)に示すように、500℃、266Paの減圧雰囲気下では、ゲート電極3A,3B等の固体表面にて酸素と水素とが燃焼して、種々の活性種を生成する。そしてこの活性種のうち、特に水酸基活性種(OH*)や酸素活性種(O*)により、前記固体表面に吸着されているTEOSが分解され、SiO2に変わるものと考えられる。このように前記ゲート電極3A,3Bの上面や側壁、凹部35の底面に均一な厚さでSiO2膜42が形成されると、図3(c)に示すように、ゲート電極3A,3Bの上面と側面とに同じ厚さでSiO2膜42が形成される。このため2つのゲート電極3A,3Bの間の凹部35には、ゲート電極3A,3Bの上面から迫り出すようにSiO2膜が形成されることがなく、前記凹部35の両側面から徐々に内側に向かってSiO2膜が形成されるので、図3(d)に示すようにボイドを形成することなく、SiO2膜42を凹部35に埋め込むことができるものと推察される。

On the other hand, oxygen gas and hydrogen gas, for example, as shown in FIG. 3B, in a reduced pressure atmosphere of 500 ° C. and 266 Pa, oxygen and hydrogen burn on the solid surfaces of the

また本発明のSiO2膜は、既述のように、ウエハW等の固体上で発生したラジカル種とTEOSとの反応によるラジカル酸化により形成されるため、形成されるSiO2膜の膜質が強固であり、フッ素を含む薬液に対して耐性が大きいと考えられる。 Further, as described above, the SiO2 film of the present invention is formed by radical oxidation by reaction of radical species generated on a solid such as the wafer W and TEOS, so that the film quality of the formed SiO2 film is strong. The resistance to chemicals containing fluorine is considered high.

これに対してTEOSガスとO2ガスを用いてCVDによりSiO2膜を形成するプロセスや、あるいはTEOSガスとOラジカルとを用いてCVDによりSiO2を形成するプロセスでは、既述のようにTEOSガスが気相中にて分解して降り積もるように成膜されるのでボイドができる。またTEOSガスとO3含有O2ガスとH2O2ガスとを用いてプラズマCVDによりSiO2を形成するプロセスにおいても、プラズマによりTEOSやO3、O2、H2O2が分解されるので、結果として既述のようにTEOSガスが気相中にて分解して降り積もるように成膜されると推察される。またプラズマを用いてH2O2ガスを分解しているので、OHラジカルを生成せずに、Oラジカル、Hラジカルが生成されると考えられる。 On the other hand, in the process of forming a SiO2 film by CVD using TEOS gas and O2 gas, or in the process of forming SiO2 by CVD using TEOS gas and O radical, the TEOS gas is vaporized as described above. Voids are formed because the film is deposited so that it decomposes and accumulates in the phase. Also, in the process of forming SiO2 by plasma CVD using TEOS gas, O3-containing O2 gas, and H2O2 gas, TEOS, O3, O2, and H2O2 are decomposed by plasma, and as a result, TEOS gas as described above. It is inferred that the film is decomposed and deposited in the gas phase. Further, since H2O2 gas is decomposed using plasma, it is considered that O radicals and H radicals are generated without generating OH radicals.

上述の例では、層間絶縁膜を例に挙げているが、層間絶縁膜以外の絶縁膜であってもよい。 In the above example, the interlayer insulating film is taken as an example, but an insulating film other than the interlayer insulating film may be used.

続いて本発明の効果を確認するために行なった実験例について説明する。 Next, experimental examples performed to confirm the effects of the present invention will be described.

<実験例1>

(実施例1)

上述の装置を用いて、上述の条件、つまり反応容器5にTEOSガスと水素ガスと酸素ガスとを夫々150sccm、1000sccm、2000sccmの流量で供給し、成膜温度500℃、圧力266Pa(2.0Torr)の下で、アスペクト比が2.5の凹部を埋め込むように、厚さ30nmのSiO2膜を形成した後、このSiO2膜に対して50重量%HFとH2Oよりなるエッチング液により、1分間ウェットエッチングを行い、そのときのエッチングレートを測定した。ここで前記エッチング液の組成は、50重量%HF/H2O=1/399とした。

<Experimental example 1>

Example 1

Using the above-mentioned apparatus, TEOS gas, hydrogen gas, and oxygen gas are supplied to the reaction vessel 5 at the flow rates of 150 sccm, 1000 sccm, and 2000 sccm, respectively, the film forming temperature is 500 ° C., and the pressure is 266 Pa (2.0 Torr). ), An SiO 2 film having a thickness of 30 nm is formed so as to fill a recess having an aspect ratio of 2.5, and then wetted with an etching solution containing 50 wt% HF and H 2 O for 1 minute. Etching was performed, and the etching rate at that time was measured. Here, the composition of the etching solution was 50 wt% HF / H2O = 1/399.

(比較例1)

実施例1と同様の装置を用いて、従来のCVDプロセスにより前記アスペクト比が2.5の凹部を埋め込むように、厚さ50nmのSiO2膜を形成し、このSiO2膜に対して、実施例1と同様の条件でウェットエッチングを行い、そのときのエッチングレートを測定した。ここで成膜条件は、TEOSガス流量190sccm、成膜温度680℃、圧力53Paとした。

(Comparative Example 1)

Using an apparatus similar to that in Example 1, a SiO2 film having a thickness of 50 nm is formed by a conventional CVD process so as to fill the concave portion having the aspect ratio of 2.5. Wet etching was performed under the same conditions as above, and the etching rate at that time was measured. The film formation conditions here were a TEOS gas flow rate of 190 sccm, a film formation temperature of 680 ° C., and a pressure of 53 Pa.

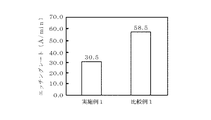

この結果を図4に示す。この結果、HFを含むエッチング液によるエッチングレートは、本発明のプロセスにて形成されたSiO2膜(実施例1)の方が、従来のCVD法にて形成されたSiO2膜(比較例1)よりも小さくなり、実施例1のSiO2膜のエッチングレートは比較例1のSiO2膜のエッチングレートのほぼ半分であることが認められた。ここでエッチングレートが小さいということは、膜質が強固であり、フッ素を含むエッチング液に対して耐性が大きいことを示している。 The result is shown in FIG. As a result, the etching rate by the etching solution containing HF is higher in the SiO2 film (Example 1) formed by the process of the present invention than in the SiO2 film (Comparative Example 1) formed by the conventional CVD method. It was confirmed that the etching rate of the SiO2 film of Example 1 was almost half that of the SiO2 film of Comparative Example 1. Here, the low etching rate indicates that the film quality is strong and the resistance to the etching solution containing fluorine is high.

これにより本発明のプロセスは、従来のCVDプロセス(比較例1)の成膜温度よりも低い500℃という成膜温度で処理を行ないながらも、従来のCVDプロセスにて得られたSiO2膜よりも、膜質を強固なものとし、フッ酸に対する耐性が大きいことが認められる。またフッ酸に対する耐性が大きいので、フッ酸がSiO2膜に浸み込むことにより形成されるシームの発生が抑えられることが理解される。 As a result, the process of the present invention is performed at a film formation temperature of 500 ° C., which is lower than the film formation temperature of the conventional CVD process (Comparative Example 1), but more than the SiO 2 film obtained by the conventional CVD process. It is recognized that the film quality is strong and the resistance to hydrofluoric acid is high. Further, it is understood that since the resistance to hydrofluoric acid is high, the generation of seams formed by the permeation of hydrofluoric acid into the SiO2 film can be suppressed.

<実験例2>

(実施例2)

上述の装置を用いて、上述の条件、つまり反応容器にTEOSガスと水素ガスと酸素ガスとを夫々150sccm、1000sccm、2000sccmの流量で供給し、成膜温度500℃、圧力266Pa(2.0Torr)の下で、アスペクト比が2.4の凹部を埋め込むようにSiO2膜を形成した後、このSiO2膜の上に厚さ100nmのポリシリコン膜を形成し、このSiO2膜とポリシリコン膜との断層写真をSEM(電子顕微鏡)により撮影した。ここでSiO2膜の上にポリシリコン膜を形成したのは、SiO2膜の断層写真を撮影するためである。

<Experimental example 2>

(Example 2)

Using the above-described apparatus, TEOS gas, hydrogen gas, and oxygen gas are supplied to the reaction vessel at the flow rates of 150 sccm, 1000 sccm, and 2000 sccm, respectively, the film forming temperature is 500 ° C., and the pressure is 266 Pa (2.0 Torr). After forming a SiO2 film so as to fill a recess having an aspect ratio of 2.4, a polysilicon film having a thickness of 100 nm is formed on the SiO2 film, and a fault between the SiO2 film and the polysilicon film is formed. The photograph was taken with an SEM (electron microscope). The reason why the polysilicon film is formed on the SiO2 film is to take a tomographic photograph of the SiO2 film.

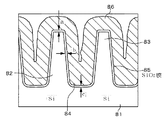

このSiO2膜の断層写真をトレースしたものを図5に示す。図5中81はシリコン基板、82,83はシリコン基板上に形成されたゲート電極、84はゲート電極の間に形成された凹部であり、この凹部84のアスペクト比は2.4である。また図中85はSiO2膜、86はポリシリコン膜を夫々示している。

A trace of the tomographic image of this SiO2 film is shown in FIG. In FIG. 5, 81 is a silicon substrate, 82 and 83 are gate electrodes formed on the silicon substrate, 84 is a recess formed between the gate electrodes, and the aspect ratio of the

そして形成されたSiO2膜85の厚さを、ゲート電極82の上部aと、側壁部bと、凹部84の底部cとについて測定したところ、SiO2膜の厚さは、上部a:34nm、側壁部b:35nm、底部c:34nm、つまりb/a=1.029、c/a=1.0であり、本発明の方法によりゲート電極82の上部と側壁部と凹部84の底部とにSiO2膜をほぼ均一な厚さで形成できることが認められる。

Then, when the thickness of the formed

(比較例3)

実施例1と同様の装置を用いて、TEOSガスとO3ガスとを用いて、図5に示す前記アスペクト比が2.4の凹部84を埋め込むようにSiO2膜を形成し、実施例2と同様に、このSiO2膜の断層写真を撮影した。この例の成膜条件は、TEOSガス流量190sccm、O3ガス流量200sccm、成膜温度500℃、圧力266Paとした。

(Comparative Example 3)

Using an apparatus similar to that in Example 1, a SiO2 film is formed using TEOS gas and O3 gas so as to fill the

前記断層写真に基づいて、ゲート電極82の上部a、側壁部b、凹部84の底部cについて、形成されたSiO2膜の厚さを測定したところ、b/a=1.05、c/a=0.95であった。

Based on the tomographic image, when the thickness of the formed SiO2 film was measured for the upper part a of the

(比較例4)

実施例1と同様の装置を用いて、TEOSガスとO3ガスとを用いて、図5に示す前記アスペクト比が2.4の凹部84を埋め込むようにSiO2膜を形成し、実施例2と同様に、このSiO2膜の断層写真を撮影した。この例の成膜条件は、TEOSガス流量190sccm、O3ガス流量 200sccm、成膜温度550℃、圧力133Paとした。

(Comparative Example 4)

Using an apparatus similar to that in Example 1, a SiO2 film is formed using TEOS gas and O3 gas so as to fill the

前記断層写真に基づいて、ゲート電極82の上部a、側壁部b、凹部84の底部cについて、形成されたSiO2膜の厚さを測定したところ、b/a=1.0、c/a=0.93であった。

Based on the tomographic image, the thickness of the formed SiO2 film was measured for the upper part a of the

(比較例5)

実施例1と同様の装置を用いて、TEOSガスとO2ガスとを用いて、図5に示す前記アスペクト比が2.4の凹部84を埋め込むようにSiO2膜を形成し、実施例2と同様に、このSiO2膜の断層写真を撮影した。この例の成膜条件は、TEOSガス流量130sccm、O2ガス流量100sccm、成膜温度600℃、圧力266Paとした。

(Comparative Example 5)

Using the same apparatus as in the first embodiment, a SiO2 film is formed using TEOS gas and O2 gas so as to fill the

前記断層写真に基づいて、ゲート電極の上部a、側壁部b、凹部84の底部cについて、形成されたSiO2膜の厚さを測定したところ、b/a=1.0、c/a=0.97であった。

Based on the tomographic image, when the thickness of the formed SiO2 film was measured for the upper part a of the gate electrode, the side wall part b, and the bottom part c of the

ここでこの実験例2は、アスペクト比が高い凹部84へのSiO2膜の埋め込み特性を間接的に評価したものである。この実験の結果、本発明のプロセスにて形成されたSiO2膜(実施例2)は、比較例3,4よりも成膜温度が低いながらも、SiO2膜をゲート電極82の上部、側壁部、凹部84の底部に均一に形成できることが理解される。

Here, in Experimental Example 2, the embedding characteristic of the SiO2 film in the

このようにゲート電極82,83の上面のSiO2膜の厚さと、ゲート電極82,83の側面のSiO2膜の厚さと、凹部84の底面のSiO2膜の厚さがほぼ同じであるということは、既述のようにゲート電極82の上面と側面とに同じように徐々に膜が形成されていくので、ゲート電極82の上面から迫り出すようにSiO2膜が形成されないため、ボイドが形成されにくいことを示唆している。

Thus, the thickness of the SiO2 film on the top surfaces of the

またこのことにより、本発明のプロセスにて形成されるSiO2膜の形成メカニズムについては、気相中にてTEOSガスが分解し、この分解物がゲート電極上に降り積もることによって、膜が形成されるタイプとは異なるものであることを示している。 In addition, as for the formation mechanism of the SiO2 film formed by the process of the present invention, the film is formed by the decomposition of the TEOS gas in the gas phase and the decomposition product falling on the gate electrode. It is different from the type.

さらにこの実験により、比較例5については、実施例2とほぼ同じ程度に、SiO2膜をゲート電極の上部、側壁部、凹部の底部に均一に形成できることが認められ、このことから成膜温度が高くなると、SiO2膜をゲート電極の上部、側壁部、凹部の底部に均一に形成しやすくなる傾向にあることが理解される。 Furthermore, this experiment shows that in Comparative Example 5, the SiO2 film can be uniformly formed on the top of the gate electrode, the side wall, and the bottom of the recess, almost the same as in Example 2. It is understood that when the height is increased, the SiO2 film tends to be easily formed uniformly on the top of the gate electrode, the side wall, and the bottom of the recess.

以上の実験から、本発明の成膜方法のように、TEOSガスと酸素ガスと水素ガスとを用い、減圧雰囲気下で、TEOSガスの分解温度よりも低い温度で加熱することにより、例えば500℃以下の低温であっても、高アスペクト比の凹部に対するカバレッジ性が良好であり、かつフッ素を含むガスに対して耐性が良好なSiO2膜を形成することができることが認められる。 From the above experiment, by using TEOS gas, oxygen gas, and hydrogen gas and heating at a temperature lower than the decomposition temperature of TEOS gas in a reduced pressure atmosphere as in the film forming method of the present invention, for example, 500 ° C. It can be seen that even at the following low temperatures, it is possible to form a SiO2 film that has good coverage with respect to a high aspect ratio recess and good resistance to fluorine-containing gas.

W 半導体ウエハ

20 P型Si基板

21a P+型ソース領域

21b P+型ドレイン領域

22a N+型ソース領域

21b N+型ドレイン領域

24a P+型ソース電極

24b P+型ドレイン電極

25a N+型ソース電極

25b N+型ドレイン電極

3A,3B ゲート電極

31 ポリシリコン層

32 WN層

33 W層

37 ビアホール

38 コンタクトホール

5 反応容器

55 ウエハボート

6 ガス供給部

62 ガス供給管

63 成膜ガス供給源

64 酸素ガス供給源

65 水素ガス供給源

71 真空ポンプ

74 ヒータ

75 加熱炉

W Semiconductor wafer 20 P

Claims (4)

前記処理容器内を前記有機系シリコンソースの蒸気の分解温度よりも低くかつ酸素ガス及び水素ガスにより水酸基活性種及び酸素活性種が発生する温度に加熱し、

前記処理容器内に供給された前記有機系シリコンソースを、前記処理容器内に供給された酸素ガス及び水素ガスにより発生した水酸基活性種及び酸素活性種により分解して、前記被処理体にシリコン酸化膜を形成することを特徴とする成膜方法。 In a method of forming a silicon oxide film on a target object by using a vapor of an organic silicon source in a reduced pressure atmosphere and a heated atmosphere inside a processing container in which the target object is placed,

The inside of the processing vessel is heated to a temperature lower than the decomposition temperature of the vapor of the organic silicon source and to generate hydroxyl active species and oxygen active species by oxygen gas and hydrogen gas ,

The organic silicon source supplied into the processing vessel is decomposed by hydroxyl active species and oxygen active species generated by the oxygen gas and hydrogen gas supplied into the processing vessel, and silicon dioxide is oxidized on the object to be processed. A film forming method comprising forming a film.

前記処理容器内を減圧雰囲気に設定する圧力調整手段と、

前記処理容器内を加熱するための加熱手段と、

前記処理容器内に有機系シリコンソースの蒸気を供給するための成膜ガス供給路と、

前記処理容器内に酸素ガスを供給するための酸化性ガス供給路と、

前記処理容器内に水素ガスを供給するための還元性ガス供給路と、

前記成膜ガス供給路と、酸化性ガス供給路と、還元性ガス供給路とに夫々設けられ、夫々有機系シリコンソースの蒸気と酸素ガスと水素ガスとの流量を調整するための流量調整手段と、

前記圧力調整手段と加熱手段と流量調整手段とを制御するための制御部と、を備え、

前記制御部は、前記処理容器内を減圧雰囲気に設定すると共に、有機系シリコンソースの蒸気の分解温度よりも低い温度で加熱することにより、酸素ガス及び水素ガスにより発生した水酸基活性種及び酸素活性種を用いて、前記被処理体の上にシリコン酸化膜を形成するように、前記圧力調整手段と加熱手段と流量調整手段とを制御することを特徴とする成膜装置。 A processing container in which an object to be processed is placed;

Pressure adjusting means for setting the inside of the processing vessel to a reduced pressure atmosphere;

Heating means for heating the inside of the processing vessel;

A film forming gas supply path for supplying vapor of the organic silicon source into the processing container;

An oxidizing gas supply path for supplying oxygen gas into the processing vessel;

A reducing gas supply path for supplying hydrogen gas into the processing vessel;

Flow rate adjusting means provided in the film forming gas supply path, the oxidizing gas supply path, and the reducing gas supply path, respectively, for adjusting the flow rates of the vapor , oxygen gas, and hydrogen gas of the organic silicon source. When,

A control unit for controlling the pressure adjusting means, the heating means, and the flow rate adjusting means,

The control unit sets the inside of the processing container to a reduced pressure atmosphere and heats it at a temperature lower than the decomposition temperature of the vapor of the organic silicon source to thereby generate hydroxyl active species and oxygen activity generated by oxygen gas and hydrogen gas. A film forming apparatus, wherein the pressure adjusting means, the heating means, and the flow rate adjusting means are controlled so as to form a silicon oxide film on the object to be processed using a seed.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005225709A JP4624207B2 (en) | 2005-08-03 | 2005-08-03 | Film forming method and film forming apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005225709A JP4624207B2 (en) | 2005-08-03 | 2005-08-03 | Film forming method and film forming apparatus |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007042884A JP2007042884A (en) | 2007-02-15 |

| JP2007042884A5 JP2007042884A5 (en) | 2008-08-14 |

| JP4624207B2 true JP4624207B2 (en) | 2011-02-02 |

Family

ID=37800586

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005225709A Expired - Fee Related JP4624207B2 (en) | 2005-08-03 | 2005-08-03 | Film forming method and film forming apparatus |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4624207B2 (en) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5559988B2 (en) | 2009-06-03 | 2014-07-23 | 東京エレクトロン株式会社 | Film forming material for silicon oxide film and method for forming silicon oxide film using the same |

| DE102010015149A1 (en) * | 2010-04-16 | 2011-10-20 | Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V. | Apparatus for coating a substrate within a vacuum chamber by plasma assisted chemical vapor deposition |

| JP5679581B2 (en) | 2011-12-27 | 2015-03-04 | 東京エレクトロン株式会社 | Deposition method |

| JP6196106B2 (en) | 2013-09-13 | 2017-09-13 | 東京エレクトロン株式会社 | Method for manufacturing silicon oxide film |

| JP2015056632A (en) | 2013-09-13 | 2015-03-23 | 東京エレクトロン株式会社 | Method for manufacturing silicone oxide film |

| JP2014064039A (en) * | 2013-12-25 | 2014-04-10 | Tokyo Electron Ltd | Film deposition method and film deposition device |

| US10458016B2 (en) | 2015-12-25 | 2019-10-29 | Tokyo Electron Limited | Method for forming a protective film |

| JP6523185B2 (en) | 2016-01-29 | 2019-05-29 | 東京エレクトロン株式会社 | Deposition method |

| JP6602261B2 (en) | 2016-05-23 | 2019-11-06 | 東京エレクトロン株式会社 | Deposition method |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005123275A (en) * | 2003-10-14 | 2005-05-12 | Tokyo Electron Ltd | Method and equipment forming film |

| JP2006054432A (en) * | 2004-07-15 | 2006-02-23 | Tokyo Electron Ltd | Film forming method, film forming apparatus, and storage medium |

| JP2006190787A (en) * | 2005-01-05 | 2006-07-20 | Hitachi Kokusai Electric Inc | Substrate treatment apparatus and method of manufacturing semiconductor device |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08115911A (en) * | 1994-08-25 | 1996-05-07 | Sony Corp | Manufacture of semiconductor device |

| JPH08227888A (en) * | 1995-02-21 | 1996-09-03 | Sony Corp | Forming method of dielectric film |

| US5710079A (en) * | 1996-05-24 | 1998-01-20 | Lsi Logic Corporation | Method and apparatus for forming dielectric films |

-

2005

- 2005-08-03 JP JP2005225709A patent/JP4624207B2/en not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005123275A (en) * | 2003-10-14 | 2005-05-12 | Tokyo Electron Ltd | Method and equipment forming film |

| JP2006054432A (en) * | 2004-07-15 | 2006-02-23 | Tokyo Electron Ltd | Film forming method, film forming apparatus, and storage medium |

| JP2006190787A (en) * | 2005-01-05 | 2006-07-20 | Hitachi Kokusai Electric Inc | Substrate treatment apparatus and method of manufacturing semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007042884A (en) | 2007-02-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102627584B1 (en) | Cyclical deposition method and apparatus for filling a recess formed within a substrate surface | |

| KR100861851B1 (en) | Method and apparatus for forming silicon oxide film | |

| US9349587B2 (en) | Method of manufacturing semiconductor device and method of processing substrate and substrate processing apparatus | |

| US7220461B2 (en) | Method and apparatus for forming silicon oxide film | |

| KR101498960B1 (en) | Thin film formation method and film formation apparatus | |

| JP6457101B2 (en) | Semiconductor device manufacturing method, substrate processing apparatus, and program | |

| TWI331364B (en) | ||

| KR102415040B1 (en) | Method and apparatus for forming silicon oxide film | |

| JP7598992B2 (en) | Processing method, semiconductor device manufacturing method, processing device, and program | |

| JP2010251654A (en) | Deposition method and manufacturing method of semiconductor device | |

| KR102295441B1 (en) | Method and apparatus for forming silicon oxide film on tungsten film | |

| JP6583064B2 (en) | Mask structure forming method and film forming apparatus | |

| KR20190030169A (en) | Method and apparatus for forming silicon oxide film, and storage medium | |

| KR100860683B1 (en) | Film forming method and heat treating device | |

| JP4039385B2 (en) | Removal method of chemical oxide film | |

| KR102396170B1 (en) | Semiconductor device manufacturing method and film forming apparatus | |

| JP4624207B2 (en) | Film forming method and film forming apparatus | |

| KR102360687B1 (en) | Semiconductor device manufacturing method, substrate processing apparatus and program | |

| JP2019029576A (en) | Method and apparatus for forming silicon film | |

| JP7047117B2 (en) | Manufacturing method of semiconductor device, substrate processing device and recording medium | |

| JP2007035740A (en) | Film deposition method, film deposition equipment, and storage medium | |

| US11728165B2 (en) | Method of processing substrate, substrate processing apparatus, recording medium, and method of manufacturing semiconductor device | |

| JP2018207075A (en) | Substrate processing method and substrate processing device | |

| JP4112591B2 (en) | Semiconductor device manufacturing method and substrate processing apparatus | |

| JP7462065B2 (en) | SUBSTRATE PROCESSING METHOD, SEMICONDUCTOR DEVICE MANUFACTURING APPARATUS, PROGRAM, AND SUBSTRATE PROCESSING APPARATUS |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080627 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080627 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100617 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100629 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100830 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101026 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101102 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131112 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |