JP4620522B2 - 半導体回路 - Google Patents

半導体回路 Download PDFInfo

- Publication number

- JP4620522B2 JP4620522B2 JP2005138776A JP2005138776A JP4620522B2 JP 4620522 B2 JP4620522 B2 JP 4620522B2 JP 2005138776 A JP2005138776 A JP 2005138776A JP 2005138776 A JP2005138776 A JP 2005138776A JP 4620522 B2 JP4620522 B2 JP 4620522B2

- Authority

- JP

- Japan

- Prior art keywords

- terminal

- mos transistor

- transistor

- potential

- source

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Electronic Switches (AREA)

- Logic Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

また、本願発明は、後述するようにMOSトランジスタの動作時のしきい値電圧の絶対値及びばらつき幅の低減を図り、低電圧動作可能な半導体回路を提供するものであるが、同様の技術に、低電圧用途ではないもののSRAM回路において、特許文献2に開示されるしきい値電圧を検出してバルク電位を制御することで、しきい値電圧の変動を抑制し所望のしきい値電圧を得る方法などがある。

その動作安定性のためには、しきい値電圧のばらつきの小さい高価な高性能MOSトランジスタが必要となってしまうので、コスト面を考えると適切でない。

この構成によれば、被制御側の第2のMOSトランジスタに、バルク電位制御用の第1のMOSトランジスタのしきい値電圧に応じたバルク電位を与えることで、第2のMOSトランジスタのしきい値電圧の絶対値の調整及びしきい値電圧のばらつき幅の低減が可能となる。

ここで、電源端子は、前記第1のMOSトランジスタがn型MOSトランジスタの場合にはアースの端子であり、p型MOSトランジスタの場合には正電源の端子である。

この構成によれば、第2のMOSトランジスタのしきい値電圧の絶対値及びばらつき幅の低減効果が小さすぎて所望のものでない場合に、その効果を増大させることができる。

ここで、電源端子は、前記第1のMOSトランジスタがn型MOSトランジスタの場合にはアースの端子であり、p型MOSトランジスタの場合には正電源の端子である。

この構成によれば、第2のMOSトランジスタのしきい値電圧の絶対値及びばらつき幅の低減効果が小さすぎて所望のものでない場合に、その効果を増大させることができる。

この構成によれば、第1のMOSトランジスタのドレイン端子と、第2のMOSトランジスタのバルク端子との双方の端子を、安定的に同電位(第1のMOSトランジスタのしきい値電圧)とすることができる。

この構成のように、バルク電位制御が行なわれるトランジスタが複数接続されたトランジスタ群であっても、しきい値電圧の低減効果を調整することが可能なので、低電圧電源であっても動作マージンを得ることができる。

この構成によれば、第1のMOSトランジスタによる被バルク電位制御対象のMOSトランジスタが差動増幅回路構成とされていても、しきい値電圧の低減効果を調整することが可能なので、その差動増幅回路を低電圧電源での動作に有利な回路とすることができる。

ここで、電源端子は、前記第1のMOSトランジスタがn型MOSトランジスタの場合には正電源の端子であり、p型MOSトランジスタの場合にはアースの端子である。

この構成によれば、第1のMOSトランジスタによる被バルク電位制御対象のMOSトランジスタが電流ミラー回路構成とされていても、しきい値電圧の低減効果を調整することが可能なので、その電流ミラー回路を低電圧電源での動作に有利な回路とすることができる。

ここで、電源端子は、前記第1のMOSトランジスタがn型MOSトランジスタの場合にはアースの端子であり、p型MOSトランジスタの場合には正電源の端子である。

この構成によれば、第2のトランジスタのドレイン−ソース間に第4の電流源にて所定電流を流すことで、ゲート端子に入力される信号及び第2のMOSトランジスタのしきい値電圧に応じてソース端子から任意の電圧を出力することができるが、第2のMOSトランジスタのしきい値電圧の調整を行うことで、そのソースフォロワ回路を低電圧電源での動作に有利な回路とすることができる。

また、以下の説明に使用する文字記号の意味は次のとおりである。

Vgs:ゲート−ソース間電圧

Vg:接地電位VSS基準のゲート電位

Vbs:ソース−バルク間電圧

Vb:接地電位VSS基準のバルク電位

Vs:接地電位VSS基準のソース電位

Vth:動作時のしきい値電圧

VT:Vbs=0時のしきい値電圧

Ids:ドレイン電流

W:トランジスタのゲート長

L:トランジスタのゲート幅

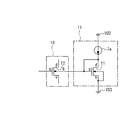

図1は、本発明の第1の実施の形態に係る半導体回路の構成を示す回路図である。

この半導体回路におけるしきい値電圧の調整について説明する。本半導体回路は、MOSトランジスタ(単に、トランジスタとも略す)T1及び電流源Iaを有するバルク電位制御回路11と、トランジスタT2による被バルク電位制御MOSトランジスタ(被制御トランジスタとも略す)10と備えて構成されている。

トランジスタT1のゲート端子g及びドレイン端子dと、トランジスタT2のバルク端子bとは電流源Iaに接続されており、トランジスタT1のソース端子はソース電源VSSに接続されている。

これをグラフに表すと図2のようになるが、ソース−バルク間電圧Vbsのある領域に限ればおよそ直線近似で表す事ができ、破線で示すように動作時のしきい値電圧Vth=VT+γVbs(γ:直線近似時の基板係数)となる。

このことから、電流源Iaから供給されるトランジスタT1のドレイン電流をIds1とすると、Ids1=K×(W1/L1)×(Vgs1−VT1)2であり、トランジスタT1のゲート電位はVg1=Vgs1=VT1+√{Ids1/(K×W1/L1)}のようになる。

トランジスタT2のしきい値電圧Vth2は、Vth=VT+γVbsに従ってソース−バルク間電圧Vbsにより変化し、Vth2=VT2+γVbs2=VT2+γ(Vs2−VT1−α1)となる。

図3は、本発明の第2の実施の形態に係る半導体回路の構成を示す回路図である。

この半導体回路におけるしきい値電圧の調整について説明する。本半導体回路は、MOSトランジスタT3,T4及び電流源Ibを有するバルク電位制御回路31と、トランジスタT5による被制御トランジスタ30とを備えて構成されている。

トランジスタT3及びT4は各々自体のゲート端子g及びドレイン端子dが短絡されており(ダイオード接続)、トランジスタT3のドレイン端子dは電流源Ibに接続され、トランジスタT4のソース端子sはVSSに接地されている。

電流源Ib及びn個の直列接続されたダイオード接続型トランジスタT3,…,T4の回路がバルク電位制御回路31であり、トランジスタT5が被バルク電位制御MOSトランジスタ30である。

このように第2の実施の形態の半導体回路によれば、上記第1の実施の形態で得られるしきい値電圧の絶対値及びばらつき幅の低減効果が小さすぎて所望のものでない場合、その効果を増大させることができる。

図4は、本発明の第3の実施の形態に係る半導体回路の構成を示す回路図である。

この半導体回路におけるしきい値電圧の調整について説明する。本半導体回路は、MOSトランジスタT6と、電流源Icと、抵抗器Ra及びRbとを有するバルク電位制御回路41と、トランジスタT7による被制御トランジスタ40とを備えて構成されている。

Vth7=VT7+γVbs7=VT7+γ{Vs7−Rb/(Ra+Rb)×(VT6+α6)}であるが、トランジスタT6及びT7をVT6=VT7となるように選択すると、Vth7={1−γ×Rb/(Ra+Rb)}×VT7+γ{Vs7−Rb/(Ra+Rb)×α6}となる。

但し、上記では抵抗器Ra及びRbの互いの接続端子以外の他の端子は、トランジスタT6のドレイン端子dと、VSSとの間に接続したが、この他に、同ドレイン端子dと、電源電位、接地電位と電源電位との任意の分割電位、任意の固定電位の何れか1つの電位を有する端子との間に接続してもよい。

図5は、本発明の第4の実施の形態に係る半導体回路の構成を示す回路図である。

この半導体回路におけるしきい値電圧の調整について説明する。本半導体回路は、MOSトランジスタT8と、電流源Idと、抵抗器Rc及びRdとを有するバルク電位制御回路51と、トランジスタT9による被制御トランジスタ50とを備えて構成されている。

トランジスタT8のゲート端子gはドレイン端子dに短絡されており、ドレイン端子dは電流源Idに接続され、ソース端子sはVSSに接地されている。

このように第4の実施の形態の半導体回路によれば、上記第1の実施の形態で得られるしきい値電圧の絶対値及びばらつき幅の低減効果が所望のものでない場合、その効果を調整することができる。

図6は、本発明の第5の実施の形態に係る半導体回路の構成を示す回路図である。

この半導体回路におけるしきい値電圧の調整について説明する。本半導体回路は、MOSトランジスタT10,T11と、電流源Ieと、抵抗器Rc及びRdとを有するバルク電位制御回路61と、トランジスタT12による被制御トランジスタ60とを備えて構成されている。

トランジスタT10及びT11は、各々自体のゲート端子g及びドレイン端子dが短絡されており(ダイオード接続)、トランジスタT10のドレイン端子dは電流源Ieに接続され、トランジスタT11のソース端子sはVSSに接地されている。

抵抗器Re及びRfは互いに直列に接続され、抵抗器Reの他方の端子はトランジスタT10のゲート端子に接続され、抵抗器Rfの他方の端子はVSSに接続されており、抵抗器Re・Rf間の接続部分はトランジスタT10のゲート端子の電位を分割した電位を出力している。トランジスタT12のバルク端子bは抵抗器Re・Rf間の接続部分と接続されている。

但し、α10=√{Ids10/(K×W10/L10)}。抵抗器Re及びRfの抵抗分割によりトランジスタT12のバルク電位はVb12=n×Rf/(Re+Rf)×(VT10+α10)となり、ソース−バルク間電圧はbs12=Vs12−n×Rf/(Re+Rf)×(VT10+α10)となる。

また、本実施の形態についても上記第3の実施の形態で述べたように、抵抗器の接続先を接地電位VSSから電源電圧VDD、もしくはVDDとVSSの任意の分割電位、電源電圧に依存しない固定電位の何れかに変更してもよく、このように参照する電位を変える事で、しきい値電圧Vth12にはVT12に依存しない任意のオフセット量をもたせることができる。

このように第5の実施の形態の半導体回路によれば、上記第1の実施の形態で得られるしきい値電圧の絶対値及びばらつき幅の低減効果が大き過ぎるもしくは小さ過ぎるなど所望のものでない場合、その効果を調整することができる。

図7は、本発明の第6の実施の形態に係る半導体回路の構成を示す回路図である。

この半導体回路におけるしきい値電圧の調整について説明する。本半導体回路は、MOSトランジスタT13及び電流源Ifを有するバルク電位制御回路71と、トランジスタT14,T15,T16による被制御トランジスタ70とを備えて構成されている。

トランジスタT13及び電流源Ifは、それぞれ図1に示したトランジスタT1及び電流源Iaに該当し、トランジスタT14、T15及びT16は図1のトランジスタT2に該当しており、同じ回路構成となっている。異なる個所は、トランジスタT14、T15及びT16のソース端子がVSSに接地されていることである。

また、トランジスタT13及び電流源Ifで構成されるバルク電位制御回路71は、図4に示したバルク電位制御回路41でもよく、しきい値電圧の低減効果を調整することが可能である。

上述のように、第1〜第6の実施の形態の半導体回路においては、バルク電位制御回路を付加していない半導体回路に比べ、低電源電圧時の動作マージンを持たせることができる。

また、従来技術に比べ構成が簡便で回路面積を小さくすることができ、低電圧動作に向くので安定した低電圧動作を行うことができ、しきい値電圧Vthの変動に対して連続的に制御がかかり、使用可能な半導体回路の範囲が広くなるなどの効果がある。

図8は、本発明の第7の実施の形態に係る被制御トランジスタが差動増幅回路である場合の半導体回路の構成を示す回路図である。

本半導体回路は、MOSトランジスタT17及び電流源Igを有するバルク電位制御回路81と、差動対のトランジスタT18,T19による被制御トランジスタ80と、電流源Ihとを備えて構成されている。トランジスタT17及び電流源Igはそれぞれ図1のトランジスタT1及び電流源Iaに該当し、同じ回路構成となっている。

差動対のトランジスタT18,T19は、互いのバルク端子b及びソース端子sがそれぞれ結合されており、それらのバルク端子bがトランジスタT17のゲート端子gに接続され、ソース端子sが電流源Ihを介してVSSに接続されている。

また、差動対のトランジスタT18,T19をVT17=VT18となるように選択すると、Vth18=VT18+γ(Vs18−VT18−α17)であり、しきい値電圧Vth18が減じるとソース電位Vs18が上がり、更にしきい値電圧Vth18が減じる事になる。この結果、Vth18=(1−γ)/(1+γ)×VT18+γ/(1+γ)×(Vin−α18−α17)となり、しきい値電圧のばらつき幅を特に抑制することができる。

従って、第7の実施の形態の半導体回路によれば、差動増幅回路を低電圧電源での動作に有利な回路とすることができる。

図9は、本発明の第8の実施の形態に係る被制御トランジスタが電流ミラー回路である場合の半導体回路の構成を示す回路図である。

本半導体回路は、MOSトランジスタT20及び電流源Iiを有するバルク電位制御回路91と、一対のトランジスタT21,T22による被制御トランジスタ90と、電流源Ijとを備えて構成されている。トランジスタT20及び電流源Iiはそれぞれ図1のトランジスタT1及び電流源Iaに該当し、同じ回路構成となっている。

また、トランジスタT20及び電流源Iiで構成されるバルク電位制御回路91は、図4に示したバルク電位制御回路41でもよく、しきい値電圧の低減効果を調整することが可能である。

従って、第8の実施の形態の半導体回路によれば、電流ミラー回路を低電圧電源での動作に有利な回路とすることができる。

図10は、本発明の第9の実施の形態に係る被制御トランジスタがソースフォロワ回路である場合の半導体回路の構成を示す回路図である。

本半導体回路は、MOSトランジスタT23及び電流源Ikを有するバルク電位制御回路101と、トランジスタT24による被制御トランジスタ90と、電流源Ilとを備えて構成されている。トランジスタT23及び電流源Ilはそれぞれ図1のトランジスタT1及び電流源Iaに該当し、同じ回路構成となっている。

トランジスタT24のソース端子は、電流源Ilを介してVSSに接地されることによってソースフォロワ回路構成とされている。

また、トランジスタT23及び電流源Ikで構成されるバルク電位制御回路101は、図4に示したバルク電位制御回路41でもよく、しきい値電圧の低減効果を調整することが可能である。

11,31,41,51,61,71,81,91,101 バルク電位制御回路

T1,T3,T4,T6,T8,T10,T11,T13,T17,T20,T23 バルク電位制御側のMOSトランジスタ

T2,T5,T7,T9,T12,T14,T15,T16,T18,T19,T21,T22,T24 被バルク電位制御側のMOSトランジスタ

Ra,Rb,Rc,Rd,Re,Rf 抵抗器

Ia,Ib,Ic,Id,Ie,If,Ig,Ih,Ii,Ij,Ik,Il 電流源

VDD 電源

VSS アース

Claims (9)

- ゲート端子とドレイン端子が短絡され、バルク端子とソース端子とに同電位が供給される第1のMOSトランジスタと、

前記第1のMOSトランジスタと同伝導型で且つ第1のMOSトランジスタのドレイン端子に、バルク端子が接続された第2のMOSトランジスタと、

前記第1のMOSトランジスタのドレイン端子に接続され、当該第1のMOSトランジスタに電流を供給する電流源とを備え、

前記第1のMOSトランジスタのソース端子は、電源端子に電気的に接続され、

前記第1のMOSトランジスタのドレイン端子及び前記第2のMOSトランジスタのバルク端子は、当該第1のMOSトランジスタのしきい値電圧に応じた電位を有することを特徴とする半導体回路。 - 前記第1のMOSトランジスタと同様にゲート端子とドレイン端子が短絡されたMOSトランジスタを、前記第1のMOSトランジスタのソース端子と前記電源端子との間に複数個接続したことを特徴とする請求項1に記載の半導体回路。

- ゲート端子とドレイン端子が短絡され、バルク端子とソース端子とに同電位が供給される第1のMOSトランジスタと、

接地電位、電源電位、接地電位と電源電位との任意の分割電位、電源電位に依存しない任意の固定電位、前記第1のMOSトランジスタのソース電位の何れか1つの電位と、前記第1のMOSトランジスタのドレイン端子の電位とを分割するように接続された分割抵抗器と、

前記第1のMOSトランジスタと同伝導型であって前記分割抵抗器の分割電位の出力端子に接続されたバルク端子を有する第2のMOSトランジスタと、

前記第1のMOSトランジスタのドレイン端子に接続され、当該第1のMOSトランジスタに電流を供給する電流源と、

を備え、

前記第1のMOSトランジスタのソース端子は、電源端子に電気的に接続されることを特徴とする半導体回路。 - 前記第1のMOSトランジスタと同様にゲート端子とドレイン端子が短絡されたMOSトランジスタを、前記第1のMOSトランジスタのソース端子と前記電源端子との間に複数個接続したことを特徴とする請求項3に記載の半導体回路。

- 前記第1のMOSトランジスタのドレイン端子及び前記第2のMOSトランジスタのバルク端子は、当該ドレイン端子及びバルク端子を同電位とする能動素子回路を介して接続されていることを特徴とする請求項1から4の何れか1項に記載の半導体回路。

- 前記第2のMOSトランジスタを、当該第2のMOSトランジスタを複数個用い、これらトランジスタ群のバルク端子を前記第1のトランジスタのドレイン端子に接続し、当該第2のトランジスタ群のソース端子同士を接続した

ことを特徴とする請求項1から5の何れか1項に記載の半導体回路。 - 前記第2のMOSトランジスタを、当該第2のMOSトランジスタを2個用い、互いのバルク端子及びソース端子をそれぞれ結合し、各バルク端子を前記第1のMOSトランジスタのドレイン端子に接続し、各ソース端子を第2の電流源を介して前記電源端子に接続した差動増幅回路構成とした

ことを特徴とする請求項1から5の何れか1項に記載の半導体回路。 - 前記トランジスタ群のゲート端子を互いに接続し、これら接続されたゲート端子に当該トランジスタ群の何れか1つのトランジスタのドレイン端子を接続し、この接続点を第3の電流源を介して前記電源端子に接続した電流ミラー回路構成とした

ことを特徴とする請求項6に記載の半導体回路。 - 前記第2のMOSトランジスタのソース端子を第4の電流源を介して前記電源端子に接続したソースフォロワ回路構成とした

ことを特徴とする請求項1から5の何れか1項に記載の半導体回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005138776A JP4620522B2 (ja) | 2005-05-11 | 2005-05-11 | 半導体回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005138776A JP4620522B2 (ja) | 2005-05-11 | 2005-05-11 | 半導体回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006319557A JP2006319557A (ja) | 2006-11-24 |

| JP4620522B2 true JP4620522B2 (ja) | 2011-01-26 |

Family

ID=37539838

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005138776A Expired - Fee Related JP4620522B2 (ja) | 2005-05-11 | 2005-05-11 | 半導体回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4620522B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101510769B (zh) * | 2009-04-03 | 2011-07-06 | 浙江大学 | 体电位调制器和c类反向器 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0680824B2 (ja) * | 1984-05-29 | 1994-10-12 | 株式会社東芝 | Mosトランジスタ閾値の自動設定装置 |

| JPH06324753A (ja) * | 1993-05-13 | 1994-11-25 | Fujitsu Ltd | 定電圧発生回路及び半導体記憶装置 |

| JPH09129831A (ja) * | 1995-11-01 | 1997-05-16 | Fujitsu Ltd | 半導体装置 |

| JP3814385B2 (ja) * | 1997-10-14 | 2006-08-30 | 株式会社ルネサステクノロジ | 半導体集積回路装置 |

| JP2001203568A (ja) * | 2000-01-24 | 2001-07-27 | Nec Ic Microcomput Syst Ltd | バッファ装置 |

| JP2004165649A (ja) * | 2002-10-21 | 2004-06-10 | Matsushita Electric Ind Co Ltd | 半導体集積回路装置 |

| CN100340062C (zh) * | 2003-02-25 | 2007-09-26 | 松下电器产业株式会社 | 半导体集成电路 |

-

2005

- 2005-05-11 JP JP2005138776A patent/JP4620522B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006319557A (ja) | 2006-11-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7479821B2 (en) | Cascode circuit and semiconductor device | |

| JP4150326B2 (ja) | 定電圧回路 | |

| US7973525B2 (en) | Constant current circuit | |

| CN108351662B (zh) | 具有曲率补偿的带隙参考电路 | |

| US8476967B2 (en) | Constant current circuit and reference voltage circuit | |

| CN107256062A (zh) | 一种无电阻式基准源 | |

| US20090096510A1 (en) | Reference voltage generating circuit for use of integrated circuit | |

| US11086348B2 (en) | Bandgap reference circuit | |

| CN1080742A (zh) | 使用cmos晶体管的基准电压发生器 | |

| JP2008015925A (ja) | 基準電圧発生回路 | |

| US9767861B2 (en) | Regulated voltage supply with low power consumption and small chip area | |

| JPH10116129A (ja) | 基準電圧発生回路 | |

| CN118732775A (zh) | 一种带隙电压基准电路及电子设备 | |

| WO2008144722A2 (en) | Class ab output stage and method for providing wide supply voltage range | |

| JP2002108465A (ja) | 温度検知回路および加熱保護回路、ならびにこれらの回路を組み込んだ各種電子機器 | |

| US20110169551A1 (en) | Temperature sensor and method | |

| CN116633116B (zh) | 低功耗电流源、电流源电路、芯片及具有其的电子设备 | |

| JPH1167931A (ja) | 基準電圧発生回路 | |

| JP4703406B2 (ja) | 基準電圧発生回路および半導体集積装置 | |

| CN115145345A (zh) | 基准电流源 | |

| JP4620522B2 (ja) | 半導体回路 | |

| JP2005044051A (ja) | 基準電圧発生回路 | |

| JP5482096B2 (ja) | 定電流生成回路、集積回路装置及び電子機器 | |

| CN108508960B (zh) | 一种高电源抑制比的电源管理电路 | |

| JP4761361B2 (ja) | リファレンス回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20070402 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20070402 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080326 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100803 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100928 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101026 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101028 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131105 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4620522 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |