JP4618639B2 - Manufacturing method of semiconductor device - Google Patents

Manufacturing method of semiconductor device Download PDFInfo

- Publication number

- JP4618639B2 JP4618639B2 JP2005045284A JP2005045284A JP4618639B2 JP 4618639 B2 JP4618639 B2 JP 4618639B2 JP 2005045284 A JP2005045284 A JP 2005045284A JP 2005045284 A JP2005045284 A JP 2005045284A JP 4618639 B2 JP4618639 B2 JP 4618639B2

- Authority

- JP

- Japan

- Prior art keywords

- imaging

- light receiving

- semiconductor device

- protective film

- circuit board

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 223

- 238000004519 manufacturing process Methods 0.000 title claims description 37

- 238000003384 imaging method Methods 0.000 claims description 112

- 239000011347 resin Substances 0.000 claims description 71

- 229920005989 resin Polymers 0.000 claims description 71

- 230000001681 protective effect Effects 0.000 claims description 60

- 238000000034 method Methods 0.000 claims description 37

- 239000006059 cover glass Substances 0.000 claims description 22

- 238000005498 polishing Methods 0.000 claims description 18

- 238000007789 sealing Methods 0.000 claims description 11

- 239000011521 glass Substances 0.000 claims description 8

- 238000005520 cutting process Methods 0.000 claims description 7

- 230000003287 optical effect Effects 0.000 description 29

- 239000000428 dust Substances 0.000 description 14

- 239000000463 material Substances 0.000 description 7

- 239000000758 substrate Substances 0.000 description 7

- 230000015572 biosynthetic process Effects 0.000 description 5

- 239000000853 adhesive Substances 0.000 description 4

- 230000001070 adhesive effect Effects 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 4

- 238000001020 plasma etching Methods 0.000 description 4

- 238000001444 catalytic combustion detection Methods 0.000 description 3

- 238000000465 moulding Methods 0.000 description 3

- 229920002120 photoresistant polymer Polymers 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- 239000004593 Epoxy Substances 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 230000003449 preventive effect Effects 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 238000005266 casting Methods 0.000 description 1

- 238000012790 confirmation Methods 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 238000005304 joining Methods 0.000 description 1

- WABPQHHGFIMREM-UHFFFAOYSA-N lead(0) Chemical compound [Pb] WABPQHHGFIMREM-UHFFFAOYSA-N 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 239000003566 sealing material Substances 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85909—Post-treatment of the connector or wire bonding area

- H01L2224/8592—Applying permanent coating, e.g. protective coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

本発明は、半導体装置の製造方法、特に、デジタルビデオカメラ、携帯電話等に実装して好適な光学モジュールに用いる撮像用半導体素子を備えた撮像用半導体装置や光ディスク装置に用いる光電変換素子を備えた光検出半導体装置の製造方法に関する。 The present invention includes a method for manufacturing a semiconductor device, in particular, an imaging semiconductor device including an imaging semiconductor element used for an optical module suitable for mounting on a digital video camera, a mobile phone, or the like, or a photoelectric conversion element used for an optical disk device. The present invention relates to a method for manufacturing a photodetection semiconductor device.

近年、デジタルビデオカメラや携帯電話等に装填する光学モジュールは、高画素化、小型化が進んでおり、中でも携帯電話にカメラ機能が搭載され、その結果、レンズ、パッケージを含めた光学モジュールとしての小型化、薄型化の要求が高まっている。これに伴ってレンズを含めた小型化、薄型化を図った撮像装置が提案がなされている(特許文献1、特許文献2参照)。 In recent years, optical modules to be installed in digital video cameras, mobile phones, etc. have been increasing in size and size, and in particular, mobile phones are equipped with camera functions. As a result, as optical modules including lenses and packages, There is an increasing demand for downsizing and thinning. Along with this, an imaging apparatus that includes a lens and is reduced in size and thickness has been proposed (see Patent Document 1 and Patent Document 2).

また、最近では光学モジュールが携帯電話、デジタルカメラ、PCカメラ等の民生機器や自動車の前後左右確認のために車体にカメラを搭載した自動車が登場してきている。 したがって、小型、薄型の要求に加え、耐環境性等の信頼性への要求も高まり、このような要求に応えるため、撮像用半導体素子を実装した次のような構造の光学モジュールが実施されている。 In addition, recently, optical modules have appeared in consumer equipment such as mobile phones, digital cameras, and PC cameras, and automobiles equipped with a camera on the vehicle body for front / rear / left / right confirmation. Therefore, in addition to demands for small size and thinness, there is an increasing demand for reliability such as environmental resistance, and in order to meet such demand, an optical module having the following structure mounted with an imaging semiconductor element has been implemented. Yes.

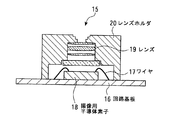

図11に示すように、光学モジュール15は、回路基板16上にワイヤ17で接続された撮像用半導体素子18を実装し、さらに回路基板16上にレンズ19が取り付けられたレンズホルダ20を取り付け、前記撮像用半導体素子18を封止している。

As shown in FIG. 11, the

また、図12に示すように、セラミックスや樹脂を成型して作られた空洞部22aを備えた回路基板22にワイヤ23でワイヤボンディングされた撮像用半導体素子24を実装し、前記空洞部22aをガラス板25で封止し、さらにレンズ26が取り付けられたレンズホルダ27を前記空洞部22aを囲むように取り付けた光学モジュールも実施されている。

In addition, as shown in FIG. 12, an

また、図8に示すように、ガラス基板28上の受光部とは反対側のパターニングされた面に撮像用半導体素子29をフリップチップボンディング30し、前記撮像用半導体素子29を樹脂封止(図示せず)した光学モジュールも実施されている。 Further, as shown in FIG. 8, the imaging semiconductor element 29 is flip-chip bonded 30 to the patterned surface of the glass substrate 28 opposite to the light receiving portion, and the imaging semiconductor element 29 is resin-sealed (see FIG. 8). An optical module (not shown) is also implemented.

また、光ディスク装置に代表されるように、光ピックアップパッケージについても高密度記録媒体の読み取りができるパッケージの要求が高まっている。したがって、記録読み取りに使用する光の波長は短くなっており、図9に示すように、回路基板30に金ワイヤ31で接続された受光用半導体素子32を実装し、受光面側から透明な樹脂33で封止した樹脂封止型のパッケージが提案されているが、このパッケージでは樹脂が透明といえども光エネルギーによる樹脂の劣化によって透明度が低下し、光量の減衰が大きくなる。

また、樹脂封止の際入射側表面の樹脂の厚みを薄くする方法(特許文献3、特許文献4参照)、図10に示すように、回路基板34に実装した受光用半導体素子35の受光面側に空洞部36を形成して樹脂37で封止し、空洞部36をカバーガラス38で封止して光量の減衰を少なくした光ピックアップパッケージが提案されている。

Further, as represented by an optical disc apparatus, there is an increasing demand for a package capable of reading a high-density recording medium for an optical pickup package. Therefore, the wavelength of light used for recording and reading is shortened. As shown in FIG. 9, a light

Also, a method of reducing the thickness of the resin on the incident side surface during resin sealing (see Patent Document 3 and Patent Document 4), as shown in FIG. 10, the light receiving surface of the light receiving

前記回路基板に利用する絶縁基板としてガラスエポキシ基板やセラミック基板が汎用されてきたが、これらの絶縁基板は発塵し易く、ダイシング等の加工途中での塵埃の発生、光学モジュール完成後の振動による塵埃の発生等による異物の付着があり、歩留の向上に限界があった。また、レンズホルダーを組み付ける場合、半導体素子の受光部、受光部から光学レンズまでの距離がピントとなり、半導体素子の厚さのばらつき、実装時の接着剤の厚さのばらつき、レンズホルダの高さのばらつき等がピント合わせの精度を左右する。

また、半導体素子の厚みにも限界があり、半導体素子の厚みと絶縁基板の厚みが光学モジュールの総厚となるため、現状では光学モジュールに用いる半導体素子の薄型化にも限界がある。

Glass epoxy substrates and ceramic substrates have been widely used as insulating substrates used for the circuit board. However, these insulating substrates are likely to generate dust, which is caused by generation of dust during processing such as dicing and vibration after completion of the optical module. There was a foreign matter adhering due to generation of dust and the like, and there was a limit in improving the yield. Also, when assembling the lens holder, the light receiving part of the semiconductor element, the distance from the light receiving part to the optical lens becomes the focus, the semiconductor element thickness variation, the adhesive thickness variation during mounting, the lens holder height Variations in image quality affect the accuracy of focusing.

Further, there is a limit to the thickness of the semiconductor element, and the thickness of the semiconductor element and the thickness of the insulating substrate are the total thickness of the optical module.

ところで、前記ダイシングにより発生する塵埃の影響を避けるために、ダイシング中に固体撮像素子の表面に塵埃が付着しないようにした半導体装置の製造方法が提案されている。

該半導体装置の製造方法は、ダイシング時の固体撮像素子表面の傷付きや塵埃の付着を少なくするために、半導体ウェハに複数のCCDを形成した後、ダイシングにより半導体ウェハを個々のCCDに分割するに際し、半導体ウェハ表面にアクリル系樹脂材料でなる加工保護被膜を1μm〜3μmの膜厚となるよう被着した後に回転ブレードでダイシングを行ない、ダイシング後に加工保護被膜をアルカリ水溶液又は有機溶剤で剥離、除去し、半導体ウェハを個々のCCDに分割するものである(特許文献5参照)。

By the way, in order to avoid the influence of the dust generated by the dicing, there has been proposed a semiconductor device manufacturing method in which the dust is not attached to the surface of the solid-state imaging device during the dicing.

In the semiconductor device manufacturing method, a plurality of CCDs are formed on a semiconductor wafer and then the semiconductor wafer is divided into individual CCDs by dicing in order to reduce scratches on the surface of the solid-state imaging device and adhesion of dust during dicing. At that time, a processing protective film made of an acrylic resin material is applied to the surface of the semiconductor wafer so as to have a film thickness of 1 μm to 3 μm, and then dicing is performed with a rotating blade. After the dicing, the processing protective film is peeled off with an alkaline aqueous solution or an organic solvent. The semiconductor wafer is removed and divided into individual CCDs (see Patent Document 5).

また、他の例として、基材の一方の面に、受光面を露出面側として複数個の固体撮像素子を所定間隔をあけて整列して接合する工程と、各々の固体撮像素子の露出面の受光領域を個片に形成された柔軟性を有する保護膜により被覆する工程と、保護膜を被着した固体撮像素子を基材とともに平坦な挟圧面を有する金型により挟圧し、金型の挟圧面と保護膜および隣接する固体撮像素子によって囲まれた空隙部分に封止材を充填して樹脂成形した後、固体撮像素子の受光面から保護膜を除去する工程と、成形された封止材を介して各固体撮像素子の露出する受光面を覆うように基材の全面にわたって透光板を接着する工程と、隣接する固体撮像素子間に沿って個片の半導体装置に切断する工程とを含み、固体撮像素子の受光面に異物が付着するのを防止するようにした半導体装置の製造方法が提案されている(特許文献6参照)。 As another example, a step of aligning and joining a plurality of solid-state image sensors with a predetermined interval on one surface of a base material with the light-receiving surface as an exposed surface side, and an exposed surface of each solid-state image sensor A step of covering the light receiving region with a flexible protective film formed in a piece, and a solid-state imaging device coated with the protective film is clamped with a mold having a flat clamping surface together with a base material. A step of removing the protective film from the light-receiving surface of the solid-state image sensor after filling the sealing portion with a sealing material in a gap surrounded by the sandwiching surface, the protective film, and the adjacent solid-state image sensor and molding the resin, and molding A step of adhering a translucent plate over the entire surface of the substrate so as to cover the exposed light receiving surface of each solid-state image sensor through a material, and a step of cutting into individual semiconductor devices along adjacent solid-state image sensors Foreign matter adheres to the light receiving surface of the solid-state image sensor The method of manufacturing a semiconductor device designed to prevent has been proposed (see Patent Document 6).

前記特許文献5に記載の半導体装置の製造方法は、ダイシング時に発生する塵埃が半導体素子表面に付着するのを防止することができる。一方、製造された半導体素子が樹脂モールド等他の製造工程を経る際、半導体素子表面への塵埃の付着、汚染の除去までは解決されていない。

The manufacturing method of the semiconductor device described in

また、特許文献6に記載の半導体装置の製造方法では、金型で固体撮像素子と保護膜を挟み型締めして、その空隙部分に樹脂を充填しているが、このように金型で挟み込むと保護膜が設けられていても撮像素子表面に多大な荷重がかかる。このとき型締め圧を弱めると保護膜と金型の隙間に樹脂が回り込み、保護膜剥離後に樹脂バリが発生し、後工程において異物の原因となる。

Further, in the method of manufacturing a semiconductor device described in

本発明は、前記各種問題点を総合的に解決できる半導体装置の製造方法を提案するものである。 The present invention proposes a method of manufacturing a semiconductor device that can comprehensively solve the various problems.

第1に半導体素子の受光面への塵埃の付着を防止するという課題があるが、該防止策として(1)発塵の少ない材料の選択、(2)発塵させない加工方法、(3)工程内の異物付着の防止が考えられるが、(1)及び(2)の方法は有効な防止策であるが、現状では材料が制約され、また発塵させない物理的加工の知見に困難を伴う。

そこで、本願の発明では前記(3)の方法を採用し、撮像用半導体素子又は光電変換半導体素子などの受光用半導体素子(以下、半導体素子という。)が形成された半導体ウェハの状態からダイシング工程を経て空洞部を有する密閉状態に組み立てる直前まで半導体素子の表面を塵埃等の異物から保護し、製造中に異物が発生しても半導体素子の表面に異物が付着しない製造方法を提案するものである。

First, there is a problem of preventing dust from adhering to the light receiving surface of the semiconductor element. As the preventive measures, (1) selection of a material that generates less dust, (2) a processing method that does not generate dust, and (3) process Although it is conceivable to prevent adhesion of foreign matter inside, the methods (1) and (2) are effective preventive measures, but at present, the materials are limited and the knowledge of physical processing that does not generate dust is difficult.

Therefore, in the invention of the present application, the method (3) is adopted, and a dicing process is performed from a state of a semiconductor wafer on which a light receiving semiconductor element (hereinafter referred to as a semiconductor element) such as an imaging semiconductor element or a photoelectric conversion semiconductor element is formed. Through this process, the surface of the semiconductor element is protected from foreign matters such as dust until it is assembled in a sealed state having a cavity, and a manufacturing method is proposed in which foreign matter does not adhere to the surface of the semiconductor element even if foreign matter is generated during manufacturing. is there.

第2の課題として、前記半導体素子を有する半導体装置の信頼性の問題があるが、多くの場合、光学モジュールは空洞部を有するため、電気的な引き出し線である金ワイヤ等の配線、半導体素子の表面等、多くの領域が外部にむき出しの状態となる。

金ワイヤ等の接続のため半導体素子の表面にアルミニウムなどの電極を設けているのが一般的であるが、樹脂パッケージ内への水分の侵入等によりむき出しの電極が腐食する可能性が高い。また広いむき出しのため異物を排除しなければならない領域が広くなる。

As a second problem, there is a problem of reliability of the semiconductor device having the semiconductor element. However, in many cases, since the optical module has a hollow portion, wiring such as a gold wire which is an electrical lead wire, semiconductor element Many areas such as the surface of the surface are exposed to the outside.

In general, an electrode made of aluminum or the like is provided on the surface of the semiconductor element for connection of a gold wire or the like, but the exposed electrode is highly likely to be corroded due to intrusion of moisture into the resin package. Moreover, the area | region which must exclude a foreign material becomes large because of a large exposure.

そこで、本発明では、信頼性を確保するために、光学的に使用する領域を除き半導体素子の表面を樹脂で覆い、該半導体素子から電気的に引き出される金ワイヤ等の配線を外力や水分から遮断し、樹脂パッケージとしての信頼性を向上させるものである。後述する樹脂封止の工程で詳述する。 Therefore, in the present invention, in order to ensure reliability, the surface of the semiconductor element is covered with a resin except for the optically used region, and the wire such as a gold wire that is electrically drawn from the semiconductor element is protected from external force or moisture. It shuts off and improves the reliability as a resin package. This will be described in detail in the resin sealing step described later.

また、前記空洞部を有する光学モジュールの場合、カバーガラスを取り付けるためには接続用のワイヤーループの高さに加えて間隙が必要となる。このとき間隙量はワイヤがむき出して保護されていないため外力に弱く、十分な距離をとる必要がある。

そこで、本発明では、組み立て時に樹脂パッケージを研摩して均一な厚みを確保するとともに、必要最低限の薄型パッケージにし、前記樹脂パッケージに比べて薄型化を図るもので、後述する。

In addition, in the case of the optical module having the hollow portion, in order to attach the cover glass, a gap is required in addition to the height of the wire loop for connection. At this time, the gap amount is weak against external force because the wire is exposed and not protected, and it is necessary to take a sufficient distance.

Therefore, in the present invention, the resin package is polished at the time of assembly to ensure a uniform thickness, and the required minimum thin package is made thinner than the resin package, which will be described later.

さらに、空洞部を有する構造の場合、ワイヤー引き出しに加えてカバーガラスの貼り付けしろのスペースが必要となりその分寸法が大きくならざるをえない。

これに対して、本発明では、ワイヤー引き出し部は樹脂で覆われているため、ワイヤー引き出し部と光学的に透明な部材、例えばガラス板の貼り付け部を立体的に共有し、それだけ樹脂パッケージを小型にすることができる。

Furthermore, in the case of a structure having a hollow portion, a space for pasting the cover glass is required in addition to the wire drawer, and the size must be increased accordingly.

On the other hand, in the present invention, since the wire lead-out portion is covered with resin, the wire lead-out portion and an optically transparent member, for example, a glass plate attaching portion are shared three-dimensionally, and the resin package is correspondingly shared. It can be made small.

以上の課題を総合的に解決するために、本発明の半導体装置の製造方法は、

半導体ウェハーに形成された複数の半導体素子の各受光部に保護膜を形成する工程と、

前記半導体ウエハーを半導体素子毎に分割する工程と、前記分割された半導体素子を大判の回路基板へ実装する工程と、

前記各半導体素子と前記大判の回路基板の配線とをワイヤにてボンディングする工程と、前記保護膜、前記ワイヤ及び前記複数の半導体素子全体を覆うように樹脂で封止する工程と、前記保護膜の表面が露出するまで前記樹脂を研摩する工程と、

前記保護膜を除去する工程と、前記半導体素子、前記研摩された樹脂上にカバーを貼り付ける工程と、前記大判の回路基板を切断して個別の半導体装置に分割する工程と、

を有する。

In order to comprehensively solve the above problems, a method for manufacturing a semiconductor device of the present invention includes:

Forming a protective film on each light receiving portion of a plurality of semiconductor elements formed on a semiconductor wafer;

Dividing the semiconductor wafer into semiconductor elements, and mounting the divided semiconductor elements on a large circuit board;

Bonding each of the semiconductor elements and the wiring of the large circuit board with a wire, sealing the resin with a resin so as to cover the protective film, the wires, and the plurality of semiconductor elements, and the protective film Polishing the resin until the surface of is exposed;

Removing the protective film, pasting a cover on the semiconductor element, the polished resin, cutting the large circuit board and dividing it into individual semiconductor devices,

Have

半導体装置が受光した画質を劣化させる塵埃、水分等の異物の侵入を妨げて受光部に異物が付着するのを防止することができる。また、樹脂パッケージを研摩にて均一に薄くすので、半導体装置の薄型化及び該半導体装置を用いた光学モジュールの小型化、薄型化が可能となる。 It is possible to prevent foreign matter from adhering to the light receiving portion by preventing entry of foreign matter such as dust and moisture that degrade the image quality received by the semiconductor device. In addition, since the resin package is uniformly thinned by polishing, the semiconductor device can be made thinner and the optical module using the semiconductor device can be made smaller and thinner.

以下、本発明の撮像用半導体装置又は受光用半導体装置の製造方法の第1の実施の形態及び該製造方法で製造した半導体装置を説明する。

以下、撮像用半導体素子を備えた撮像用半導体装置を例に挙げながら説明するが、本発明の半導体装置の製造方法は、光ディスク装置に用いる受光用半導体装置の製造にも適用可能である。

A first embodiment of a method for manufacturing an imaging semiconductor device or a light receiving semiconductor device according to the present invention and a semiconductor device manufactured by the manufacturing method will be described below.

Hereinafter, an imaging semiconductor device provided with an imaging semiconductor element will be described as an example, but the method for manufacturing a semiconductor device of the present invention is also applicable to manufacturing a light receiving semiconductor device used in an optical disk device.

[工程1]撮像用半導体素子の受光部への保護膜の形成

図1に示すように、撮像用半導体素子の受光部への保護膜の形成は、複数の撮像用半導体素子が形成された半導体ウエハー1の全面に均一にレジスト塗布機にて厚さ0.1mm以上のフォトレジストを塗布し、露光、現像及びエッチングにて撮像用半導体素子の受光部の領域のみフォトレジストにてレジスト保護膜2を形成する。

前記レジスト保護膜2の厚みは後述するワイヤボンディング時のワイヤループが十分隠れる程度の一定高さが必要である。ちなみに0.1mm以上あれば十分であり、後の工程で研摩にて樹脂パッケージの厚みを整えるため、厳密な膜厚管理は必要としない。

[Step 1] Formation of Protective Film on Light-Receiving Portion of Imaging Semiconductor Element As shown in FIG. 1, the formation of the protective film on the light-receiving portion of the imaging semiconductor element is a semiconductor in which a plurality of imaging semiconductor elements are formed. A photoresist having a thickness of 0.1 mm or more is uniformly coated on the entire surface of the wafer 1 by a resist coater, and a resist

The thickness of the resist

[工程2] 半導体ウエハーのダイシング

図1に示すように、前記半導体ウエハー1の裏面にテープ3を貼り付け、前記半導体ウエハー1を撮像用半導体素子毎に前記テープ3に達するまで回転ブレード等でダイシング4を行い、分割する。

この時、ダイシングすることで前記半導体ウエハー1のかす等の切削くずが発生するが、ダイシング前に前記レジスト保護膜2が施されているため、このような異物が前記レジスト保護膜2下の受光部まで回り込まず、異物付着の要因を排除することができる。

[Step 2] Dicing of Semiconductor Wafer As shown in FIG. 1, tape 3 is attached to the back surface of the semiconductor wafer 1, and the semiconductor wafer 1 is diced with a rotating blade or the like until reaching the tape 3 for each imaging semiconductor element.

At this time, cutting chips such as debris of the semiconductor wafer 1 are generated by dicing. However, since the resist

[工程3」分割された撮像用半導体素子の大判の回路基板への実装

図2に示すように、個々に分割された撮像用半導体素子5を撮像用半導体素子5毎に配線された領域を有する大判の回路基板6上にそれぞれ実装する。

この実装は、前記ダイシング4で前記テープ3(図1)上に分割された各撮像用半導体素子5を1個ずつ吸着手段で吸着して前記大判の回路基板6上の実装場所に移動させて行う。

この時、撮像用半導体素子5の受光部の表面には前記レジスト保護膜2が施されているので、撮像用半導体素子5の表面を吸着しても傷や異物を付けることがなく、安定して吸着でき、前記テープ3(図1)から容易に剥離できる。

ここで、実装する大判の回路基板として用途にもよるが、リードフレーム、電鋳シート回路基板、ガラスエポキシ回路基板、フレキシブル回路基板等が使用でき、樹脂パッケージに適した基板であればマトリクス状に多数個の製品が取れるようにリードを配置したものを利用できる。

[Step 3] Mounting Divided Imaging Semiconductor Elements on Large Circuit Board As shown in FIG. 2, each divided

In this mounting, each

At this time, since the resist

Here, lead frames, electroformed sheet circuit boards, glass epoxy circuit boards, flexible circuit boards, etc. can be used as large circuit boards to be mounted. A lead can be used so that a large number of products can be obtained.

[工程4]撮像用半導体素子と回路基板の配線とのワイヤボンディング

ワイヤボンディングの前処理としてプラズマエッチングを必要に応じて行う。このプラズマエッチングは、撮像用半導体素子5のボンディングパッドやバンプ等の電極の表面の金属酸化物を除去するために行うものである。

図3に示すように、撮像用半導体素子5の電極(図示せず)と回路基板6の配線(図示せず)とのワイヤ7によるワイヤボンディングは低ループでボンディングするのが好適である。これは後述する樹脂パッケージの薄型化を図るためで、後工程で樹脂パッケージを研摩するが、前記ワイヤ7のループが低いほど樹脂パッケージを薄く研摩できるからである。したがって、低ループにすれば前記研摩によって薄い樹脂パッケージを容易に得ることができる。

[Step 4] Wire Bonding of Imaging Semiconductor Element and Circuit Board Wiring Plasma etching is performed as necessary as a pre-process for wire bonding. This plasma etching is performed in order to remove metal oxides on the surfaces of electrodes such as bonding pads and bumps of the

As shown in FIG. 3, it is preferable that the wire bonding of the electrode 7 (not shown) of the

[工程5]樹脂パッケージの形成

図4に示すように、樹脂8にて前記レジスト保護膜2及びワイヤ7及び複数の撮像用半導体素子5全体を覆うように封止する。

この樹脂8による封止は、金型による型締めは大判の回路基板6を挟むことで封止が可能であるため、撮像用半導体素子5への荷重も分散し、また隣接する撮像用半導体素子間においてバリが発生することがない。

金型を用いる場合、例えばフィルムアシスト方式を用いても良い。例えば撮像用半導体素子の厚みが0.4mmの場合、半導体素子の厚み+0.2mm、つまり厚み0.6mmの金型を使用する。また、印刷方式やディスペンス方式で封止することもできる。

[Step 5] Formation of Resin Package As shown in FIG. 4, the resist

Since the sealing with the resin 8 can be performed by clamping the large-

When using a mold, for example, a film assist method may be used. For example, when the thickness of the semiconductor element for imaging is 0.4 mm, a mold having a thickness of the semiconductor element + 0.2 mm, that is, a thickness of 0.6 mm is used. Further, it can be sealed by a printing method or a dispensing method.

ここで後工程で光学的に透明な部材、例えばカバー用ガラスを貼り合わせるため、図5に示すように、該工程で隣接する半導体素子間の樹脂の上面にダイサーを利用して浅溝9をそれぞれ形成する。この浅溝9の形成は後の工程6の樹脂の研摩後にしても良い。また、前記浅溝は省略しても良い。この浅溝9を設けることで後述するガラスカバー接着を行う接着剤を流し込むための溝となり、さらにダイシング用の位置決め用のマークとしても利用する。

Here, in order to bond an optically transparent member such as a cover glass in a later step, a

[工程6]樹脂パッケージの研摩

図5に示すように、前記工程5で成形された樹脂8の表面全体を研摩機で研摩し、前記レジスト保護膜2の表面が完全に露出する所定の高さまで一様に研摩する。後に研摩を行った樹脂8にカバーガラスを貼り合わせるため、隣接する半導体素子間の樹脂部に前記浅溝9を必要に応じて形成する。

この樹脂研摩工程において、撮像用半導体素子5及びワイヤ7を完全に封止するような厚みまで樹脂8を研摩して薄くすることで、撮像用半導体装置の樹脂パッケージの薄型化を容易に実現することができる。

[Step 6] Polishing of Resin Package As shown in FIG. 5, the entire surface of the resin 8 molded in

In this resin polishing step, the resin 8 of the imaging semiconductor device can be easily thinned by polishing and thinning the resin 8 to a thickness that completely seals the

[工程7]レジスト保護膜の除去

各撮像用半導体素子5の受光面に設けられた前記レジスト保護膜2をエッチングにより除去し(図6)、除去後、純水で洗浄する。この工程ではレジスト保護膜2の除去後に純水で洗浄するため、レジスト保護膜2がなくても異物が付着することはない。また、仮に何らかの要因で異物が付着していても洗浄により除去することができる。

このレジスト保護膜2を設けることによって半導体ウエハーのダイシング工程から樹脂パッケージの研磨までの工程において、前記撮像用半導体素子5の受光面に異物や傷が付くのを防止することができる。このレジスト保護膜2の除去でできた空洞部10の高さは、樹脂研摩後の厚みのみで決まるため、極めて低く形成でき、光学モジュールなどのレンズと撮像用半導体素子の距離を近接する構造にすることが可能となる。

[Step 7] Removal of Resist Protective Film The resist

By providing the resist

[工程8]カバーガラスの貼り付け

図6に示すように、前記工程7でレジスト保護膜2を除去した後、前記接着剤流し込み浅溝9内にUV接着剤等を流し込みし、光学的に透明で平坦な大判のカバーガラス11を一括で全体に貼り付けて、前記空洞部10内にある撮像用半導体素子5の受光部が密閉された撮像用半導体装置を形成する。これにより前記空洞部10に新たな異物の侵入を防止することができる。カバーガラスの貼り付けは、撮像用半導体素子5毎に個別に貼り付けても良い。

[Step 8] Affixing the cover glass As shown in FIG. 6, after removing the resist

[工程9]大判の回路基板のダイシング

前記カバーガラス11を一括貼り付けた後、大判の回路基板6とカバーガラス11を前記溝9の中央部を基準位置AーA’に採って前記回路基板6に向けてフルカットでダイシングし、個別の撮像用半導体装置に分割する。カバーガラスを撮像用半導体素子毎に個別に貼り付けた場合は、大判の回路基板6のみをダイシングして個別の撮像用半導体装置になるように分割する。このダイシング時、空洞部10はカバーガラス11で覆われているため、撮像用半導体素子5の受光面に異物が付着することがない。

[Step 9] Dicing of Large Circuit Board After the cover glass 11 is pasted together, the

以上の工程を経て製造された撮像用半導体装置13を図7に示している。

完成した撮像用半導体装置13のワイヤボンディング部を含むワイヤ7全体が前記研摩された樹脂パッケージ8aで封止されているので、薄型化が可能な撮像用半導体装置が得られる。

また、回路基板6aの裏側に該回路基板6aのボンディングランドに繋がる外部端子12のパターンを予め形成しておくことで撮像用半導体装置13をフラットケーブルやプリント配線板に搭載して外部回路との接続を行うことができる。

The imaging semiconductor device 13 manufactured through the above steps is shown in FIG.

Since the

In addition, by forming a pattern of the

図7に示すように、本発明の製造方法で製造された撮像用半導体装置13は、回路基板6a上に実装された撮像用半導体素子5、樹脂パッケージ8a、空洞部10及びカバーガラス11aを備えている。前記工程を経て製造されたので撮像用半導体素子5の受光部(カバーガラス側)表面には異物が付着することがない。

As shown in FIG. 7, an imaging semiconductor device 13 manufactured by the manufacturing method of the present invention includes an

また、前記空洞部10は前記レジスト保護膜2を除去した部分のみ残り、したがって前記空洞部10の高さは前記レジスト保護膜2の厚みのみで決まるため、前記空洞部10の高さを低くすることができ、撮像用半導体装置13を全体として従来の撮像用半導体装置よりも薄型に形成することができる。したがって、この撮像用半導体装置を光学モジュールに利用すると、従来の光学モジュールよりも小型化、薄型化が可能となる。

前記実施の形態では、前記空洞部を光学的に透明なカバーガラスで覆うようにしたが、光学モジュールを構成するレンズホルダー内に半導体装置を組み込むと、該カバーガラスは必ずしも必要としないので、以下、第2の実施の形態について説明する。

Further, only the portion where the resist

In the embodiment, the cavity is covered with an optically transparent cover glass. However, when a semiconductor device is incorporated in a lens holder constituting an optical module, the cover glass is not necessarily required. A second embodiment will be described.

以下、本発明の第2の実施の形態について、前記第1の実施の形態の図を援用しながら説明する。 Hereinafter, the second embodiment of the present invention will be described with reference to the drawings of the first embodiment.

[工程1]撮像用半導体素子の受光部への保護膜の形成

図1に示すように、撮像用半導体素子の表面への保護膜の形成は、複数の撮像用半導体素子が形成された半導体ウエハー1の全面に均一にレジスト塗布機にて厚さ0.1mm以上のフォトレジストを塗布し、露光、現像及びエッチングにて撮像用半導体素子の受光部の領域のみレジストにてレジスト保護膜2を形成する。

前記レジスト保護膜2の厚みは後述するワイヤボンディング時のワイヤループが十分隠れる程度の一定高さが必要である。ちなみに0.1mm以上あれば十分であり、後の工程で研摩にて樹脂パッケージの厚みを整えるため、厳密な膜厚管理は必要としない。

[Step 1] Formation of Protective Film on Light Receiving Section of Imaging Semiconductor Element As shown in FIG. 1, the protective film is formed on the surface of the imaging semiconductor element by a semiconductor wafer on which a plurality of imaging semiconductor elements are formed. 1. Photoresist having a thickness of 0.1 mm or more is uniformly applied to the entire surface of 1 with a resist coater, and a resist

The thickness of the resist

[工程2] 半導体ウエハーのダイシング

図1に示すように、前記半導体ウエハー1の裏面にテープ3を貼り付け、前記半導体ウエハー1を撮像用半導体素子毎に前記テープ3に達するまで回転ブレード等でダイシング4を行い、分割する。

[Step 2] Dicing of Semiconductor Wafer As shown in FIG. 1, tape 3 is attached to the back surface of the semiconductor wafer 1, and the semiconductor wafer 1 is diced with a rotating blade or the like until reaching the tape 3 for each imaging semiconductor element.

[工程3」分割された撮像用半導体素子の大判の回路基板への実装

図2に示すように、個々に分割された撮像用半導体素子5を撮像用半導体素子5毎に配線された領域を有する大判の回路基板6上にそれぞれ実装する。

この実装は、前記ダイシング4で前記テープ3(図1)上に分割された各撮像用半導体素子5を1個ずつ吸着手段で吸着して前記大判の回路基板6上の実装場所に移動させて行う。

[Step 3] Mounting Divided Imaging Semiconductor Elements on Large Circuit Board As shown in FIG. 2, each divided

In this mounting, each

[工程4]撮像用半導体素子と回路基板の配線とのワイヤボンディング

ワイヤボンディングの前処理としてプラズマエッチングを必要に応じて行う。このプラズマエッチングは、撮像用半導体素子5のボンディングパッドやバンプ等の電極の表面の金属酸化物を除去するために行うものである。

図3に示すように、撮像用半導体素子5の電極と回路基板6の配線とのワイヤ7によるワイヤボンディングは低ループで行う。

[Step 4] Wire Bonding of Imaging Semiconductor Element and Circuit Board Wiring Plasma etching is performed as necessary as a pre-process for wire bonding. This plasma etching is performed in order to remove metal oxides on the surfaces of electrodes such as bonding pads and bumps of the

As shown in FIG. 3, the wire bonding of the electrode of the

[工程5]樹脂パッケージの形成

図4に示すように、樹脂8にて前記レジスト保護膜2及びワイヤ7及び複数の撮像用半導体素子5全体を覆うように封止する。

[Step 5] Formation of Resin Package As shown in FIG. 4, the resist

[工程6]樹脂パッケージの研摩

図5に示すように、前記工程5で成形された樹脂8の表面全体を研摩機で研摩し、前記レジスト保護膜2の表面が完全に露出する所定の高さまで一様に研摩する。

[Step 6] Polishing of Resin Package As shown in FIG. 5, the entire surface of the resin 8 molded in

[工程7]レジスト保護膜の除去

各撮像用半導体素子5の受光部に設けられた前記レジスト保護膜2をエッチングにより除去し(図6)、除去後、前記撮像用半導体素子の表面を純水で洗浄する。

以上の工程までは、前記第1の実施の形態と同様である。また、以下の工程は、前記カバーガラスの貼り付けに代えてカバー用テープを貼り付ける工程となる。

[Step 7] Removal of resist protective film The resist

The processes up to the above are the same as in the first embodiment. In addition, the following process is a process of attaching a cover tape instead of attaching the cover glass.

[工程8]カバー用テープの貼り付け

図6に示すように、前記工程7でレジスト保護膜2を除去した後、前記第1の実施の形態におけるカバーガラスに代えて大判のカバー用テープ11を全体に貼り付け、撮像用半導体素子5の受光部を密閉し前記空洞部10を有する半導体装置を形成する。これにより前記中空洞10に新たな異物の侵入を防止することができる。このカバー用テープの貼り付けの工程では記浅溝9を省略することができる。

[Step 8] Affixing the cover tape As shown in FIG. 6, after removing the resist

[工程9]大判の回路基板のダイシング

前記カバー用テープ11を一括貼り付けた後、大判の回路基板6と樹脂8を基準位置AーA’に採ってフルカットでダイシングし、個別の撮像用半導体装置に分割する。このダイシング時、空洞部10はカバー用テープ11で覆われているため、撮像用半導体素子5の受光部に異物が付着することがない。

[Step 9] Dicing large-sized circuit board After the cover tape 11 is pasted together, the large-

図7に示すように、本発明の第2の実施の形態の製造方法で製造された半導体装置13は、回路基板6a上に実装された撮像半導体素子5、樹脂パッケージ8a、空洞部10を備えている。前記工程を経て製造されたので撮像用半導体素子5の受光部の表面に異物が付着することがない。

この第2の実施の形態で製造された撮像用半導体装置は、空洞部10がカバーガラスで覆われていないが、前記カバー用テープを剥離して前記撮像用半導体装置を直接レンズホルダー内に組み込むことで撮像用半導体素子の受光部に異物が付着するのを防止できる。

As shown in FIG. 7, the semiconductor device 13 manufactured by the manufacturing method according to the second embodiment of the present invention includes the

In the imaging semiconductor device manufactured in the second embodiment, the

また、前記空洞部10は前記レジスト保護膜2を形成し除去した部分のみ残り、したがって前記空洞部10の高さは前記レジスト保護膜2の厚みでのみ決まるため、前記空洞部10の高さを低くすることができ、撮像用半導体装置13を全体として従来の撮像用半導体装置よりも薄型に形成することができる。したがって、この撮像用半導体装置を光学モジュールに利用すると、従来の光学モジュールよりも小型化、薄型化が可能となる。

前記各実施の形態では、半導体素子として撮像用半導体素子を例に挙げて説明したが、撮像用半導体素子に代えて、光ディスク装置の光ピックアップ等に利用する受光用半導体装置の製造にも適用することができる。

Further, the

In each of the above-described embodiments, the imaging semiconductor element has been described as an example of the semiconductor element, but the present invention is also applicable to the manufacture of a light receiving semiconductor device used for an optical pickup of an optical disc device or the like instead of the imaging semiconductor element. be able to.

1・・半導体ウェハー 2・・レジスト保護膜 5・・半導体素子

6・・大判の回路基板 8・・研摩された樹脂 8a・・樹脂パッケージ

10・・空洞部 11、11a・・カバーガラス、カバー用テープ 13・・半導体装置

DESCRIPTION OF SYMBOLS 1 ....

Claims (10)

前記半導体ウエハーを撮像用半導体素子毎に分割する工程と、

前記分割された撮像用半導体素子を大判の回路基板へ実装する工程と、

前記各撮像用半導体素子と前記大判の回路基板の配線とをワイヤにてボンディングする工程と、

前記保護膜、前記ワイヤ及び前記複数の撮像用半導体素子全体を覆うように樹脂で封止する工程と、

前記保護膜の表面が露出するまで前記樹脂を研摩する工程と、

前記保護膜を除去する工程と、

前記撮像用半導体素子、前記研摩された樹脂上にカバーを貼り付ける工程と、

前記大判の回路基板を切断して個別の撮像用半導体装置に分割する工程と、

前記カバーを剥離する工程と

を有することを特徴とする撮像用半導体装置の製造方法。 Forming a protective film on each light receiving portion of a plurality of semiconductor elements for imaging formed on a semiconductor wafer;

Dividing the semiconductor wafer for each imaging semiconductor element;

Mounting the divided imaging semiconductor elements on a large circuit board;

Bonding each of the imaging semiconductor elements and the wiring of the large circuit board with a wire;

Sealing with a resin so as to cover the protective film, the wire, and the plurality of imaging semiconductor elements,

Polishing the resin until the surface of the protective film is exposed;

Removing the protective film;

A step of affixing a cover on the imaging semiconductor element and the polished resin;

Cutting the large circuit board and dividing it into individual imaging semiconductor devices;

A method for manufacturing an imaging semiconductor device, comprising: a step of peeling the cover .

前記半導体ウエハーを撮像用半導体素子毎に分割する工程と、

前記分割された撮像用半導体素子を大判の回路基板へ実装する工程と、

前記各撮像用半導体素子と前記大判の回路基板の配線とをワイヤにてボンディングする工程と、

前記保護膜、前記ワイヤ及び前記複数の撮像用半導体素子全体を覆うように樹脂で封止する工程と、

前記保護膜の表面が露出するまで前記樹脂を研摩する工程と、

前記保護膜を除去する工程と、

前記撮像用半導体素子、前記研摩された樹脂上に光学的に透明なカバー部材を貼り付ける工程と、

前記大判の回路基板を切断して個別の撮像用半導体装置に分割する工程と、

を有することを特徴とする撮像用半導体装置の製造方法。 Forming a protective film on each light receiving portion of a plurality of semiconductor elements for imaging formed on a semiconductor wafer;

Dividing the semiconductor wafer for each imaging semiconductor element;

Mounting the divided imaging semiconductor elements on a large circuit board;

Bonding each of the imaging semiconductor elements and the wiring of the large circuit board with a wire;

Sealing with a resin so as to cover the protective film, the wire, and the plurality of imaging semiconductor elements,

Polishing the resin until the surface of the protective film is exposed;

Removing the protective film;

A step of attaching an optically transparent cover member on the imaging semiconductor element and the polished resin;

Cutting the large circuit board and dividing it into individual imaging semiconductor devices;

A method for manufacturing an imaging semiconductor device, comprising:

前記半導体ウエハーを受光用半導体素子毎に分割する工程と、

前記分割された受光用半導体素子を大判の回路基板へ実装する工程と、

前記各受光用半導体素子と前記大判の回路基板の配線とをワイヤにてボンディングする工程と、

前記保護膜、前記ワイヤ及び前記複数の受光用半導体素子全体を覆うように樹脂で封止する工程と、

前記保護膜の表面が露出するまで前記樹脂を研摩する工程と、

前記保護膜を除去する工程と、

前記受光用半導体素子、前記研摩された樹脂上にカバーを貼り付ける工程と、

前記大判の回路基板を切断して個別の受光用半導体装置に分割する工程と、

を有することを特徴とする受光用半導体装置の製造方法。 Forming a protective film on each light receiving portion of a plurality of light receiving semiconductor elements formed on a semiconductor wafer;

Dividing the semiconductor wafer into light receiving semiconductor elements;

Mounting the divided light receiving semiconductor element on a large circuit board;

Bonding each light receiving semiconductor element and the wiring of the large circuit board with a wire;

Sealing with a resin so as to cover the protective film, the wire and the plurality of light receiving semiconductor elements,

Polishing the resin until the surface of the protective film is exposed;

Removing the protective film;

A step of affixing a cover on the light-receiving semiconductor element and the polished resin;

Cutting the large circuit board and dividing it into individual light receiving semiconductor devices;

A method of manufacturing a light-receiving semiconductor device, comprising:

前記半導体ウエハーを受光用半導体素子毎に分割する工程と、

前記分割された受光用半導体素子を大判の回路基板へ実装する工程と、

前記各受光用半導体素子と前記大判の回路基板の配線とをワイヤにてボンディングする工程と、

前記保護膜、前記ワイヤ及び前記複数の受光用半導体素子全体を覆うように樹脂で封止する工程と、

前記保護膜の表面が露出するまで前記樹脂を研摩する工程と、

前記保護膜を除去する工程と、

前記受光用半導体素子、前記研摩された樹脂上に光学的に透明なカバー部材を貼り付ける工程と、

前記大判の回路基板を切断して個別の受光用半導体装置に分割する工程と、

を有することを特徴とする受光用半導体装置の製造方法。 Forming a protective film on each light receiving portion of a plurality of light receiving semiconductor elements formed on a semiconductor wafer;

Dividing the semiconductor wafer into light receiving semiconductor elements;

Mounting the divided light receiving semiconductor element on a large circuit board;

Bonding each light receiving semiconductor element and the wiring of the large circuit board with a wire;

Sealing with a resin so as to cover the protective film, the wire and the plurality of light receiving semiconductor elements,

Polishing the resin until the surface of the protective film is exposed;

Removing the protective film;

A step of attaching an optically transparent cover member on the light-receiving semiconductor element and the polished resin;

Cutting the large circuit board and dividing it into individual light receiving semiconductor devices;

A method of manufacturing a light-receiving semiconductor device, comprising:

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005045284A JP4618639B2 (en) | 2005-02-22 | 2005-02-22 | Manufacturing method of semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005045284A JP4618639B2 (en) | 2005-02-22 | 2005-02-22 | Manufacturing method of semiconductor device |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006237051A JP2006237051A (en) | 2006-09-07 |

| JP2006237051A5 JP2006237051A5 (en) | 2008-04-03 |

| JP4618639B2 true JP4618639B2 (en) | 2011-01-26 |

Family

ID=37044413

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005045284A Expired - Fee Related JP4618639B2 (en) | 2005-02-22 | 2005-02-22 | Manufacturing method of semiconductor device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4618639B2 (en) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4200463B2 (en) * | 2006-07-07 | 2008-12-24 | Tdk株式会社 | Light receiving element, optical head using the same, and optical recording / reproducing apparatus using the same |

| US8270177B2 (en) * | 2007-07-27 | 2012-09-18 | Renesas Electronics Corporation | Electronic device and method for manufacturing electronic device |

| JP2009047949A (en) * | 2007-08-21 | 2009-03-05 | Alps Electric Co Ltd | Manufacturing method of optical element |

| KR100885505B1 (en) | 2007-09-28 | 2009-02-26 | 삼성전기주식회사 | Camera module and manufacturing method thereof |

| JP4694602B2 (en) * | 2008-09-02 | 2011-06-08 | シャープ株式会社 | Solid-state imaging device and electronic apparatus including the same |

| JP2010062232A (en) * | 2008-09-02 | 2010-03-18 | Nec Electronics Corp | Method of manufacturing semiconductor device with element function part exposed |

| KR20180056165A (en) * | 2016-11-18 | 2018-05-28 | 지투지솔루션(주) | Structure of cis package |

| DE102018210680A1 (en) * | 2018-06-29 | 2020-01-02 | Trumpf Laser Gmbh | Optical element with removable protective film |

| KR102248527B1 (en) | 2019-05-02 | 2021-05-06 | 삼성전기주식회사 | Image sensor package |

| KR20200142366A (en) * | 2019-06-12 | 2020-12-22 | 삼성전기주식회사 | Image sensor package |

| JP7328939B2 (en) * | 2020-07-15 | 2023-08-17 | アオイ電子株式会社 | Semiconductor device manufacturing method and wafer |

| JP2022155336A (en) | 2021-03-30 | 2022-10-13 | ミツミ電機株式会社 | Detection device and manufacturing method thereof |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6132535A (en) * | 1984-07-25 | 1986-02-15 | Sanyo Electric Co Ltd | Manufacture of sensor |

| JPH07221278A (en) * | 1994-01-24 | 1995-08-18 | Lg Semicon Co Ltd | Solid-state image pickup element and its preparation |

| JP2003219284A (en) * | 2002-01-24 | 2003-07-31 | Fujitsu Ltd | Camera module and manufacturing method thereof |

| JP2003332542A (en) * | 2002-05-09 | 2003-11-21 | Shinko Electric Ind Co Ltd | Semiconductor device and method of manufacturing the same |

| JP2006186288A (en) * | 2004-09-14 | 2006-07-13 | Sony Chem Corp | Functional element mounted module and manufacturing method thereof |

-

2005

- 2005-02-22 JP JP2005045284A patent/JP4618639B2/en not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6132535A (en) * | 1984-07-25 | 1986-02-15 | Sanyo Electric Co Ltd | Manufacture of sensor |

| JPH07221278A (en) * | 1994-01-24 | 1995-08-18 | Lg Semicon Co Ltd | Solid-state image pickup element and its preparation |

| JP2003219284A (en) * | 2002-01-24 | 2003-07-31 | Fujitsu Ltd | Camera module and manufacturing method thereof |

| JP2003332542A (en) * | 2002-05-09 | 2003-11-21 | Shinko Electric Ind Co Ltd | Semiconductor device and method of manufacturing the same |

| JP2006186288A (en) * | 2004-09-14 | 2006-07-13 | Sony Chem Corp | Functional element mounted module and manufacturing method thereof |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006237051A (en) | 2006-09-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4618639B2 (en) | Manufacturing method of semiconductor device | |

| KR100604190B1 (en) | Solid state imaging device, semiconductor wafer, optical device module, method of solid state imaging device fabrication, and method of optical device module fabrication | |

| JP4686400B2 (en) | Optical device, optical device apparatus, camera module, and optical device manufacturing method | |

| KR100575094B1 (en) | Module for optical device, and manufacturing method therefor | |

| JP4863026B2 (en) | Manufacturing method of camera module and camera module | |

| JP5047243B2 (en) | Optical element wafer module, optical element module, optical element module manufacturing method, electronic element wafer module, electronic element module manufacturing method, electronic element module, and electronic information device | |

| JP4764941B2 (en) | Optical element, optical element wafer, optical element wafer module, optical element module, optical element module manufacturing method, electronic element wafer module, electronic element module manufacturing method, electronic element module, and electronic information device | |

| JP4819152B2 (en) | Optical element wafer, optical element wafer module, optical element module, method for manufacturing optical element module, electronic element wafer module, method for manufacturing electronic element module, electronic element module, and electronic information device | |

| JP5676171B2 (en) | Solid-state imaging device, manufacturing method thereof, and electronic apparatus | |

| JP7289286B2 (en) | Photosensitive assembly and camera module and manufacturing method thereof | |

| JP2001351997A (en) | Structure mounted with light-receiving sensor and method using the same | |

| US7655505B2 (en) | Manufacturing method of semiconductor device | |

| KR20060056870A (en) | Image pickup module and manufacturing method of image pickup module | |

| JPH07202152A (en) | Solid-state image pickup device | |

| JP2008092417A (en) | Semiconductor imaging element, its manufacturing method, semiconductor imaging apparatus, and semiconductor imaging module | |

| WO2013075650A1 (en) | Encapsulation method for image sensor chip and camera module | |

| JP2002329850A (en) | Chip size package and its manufacturing method | |

| KR20200063102A (en) | Filming assembly and its packaging method, lens module, electronic device | |

| JP2005317745A (en) | Solid-state imaging apparatus and method for manufacturing the same | |

| CN111131663A (en) | Photosensitive assembly and forming method thereof, lens module and electronic equipment | |

| JP2008277593A (en) | Circuit board, optical device employing the same, camera module, and manufacturing method for the circuit board | |

| JP2003332542A (en) | Semiconductor device and method of manufacturing the same | |

| JP2011187482A (en) | Solid-state imaging apparatus, module for optical device, and method of manufacturing solid-state imaging apparatus | |

| JP2002009265A (en) | Solid-state image pickup device | |

| JP2006080597A (en) | Image pickup module and method of manufacturing the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080214 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080214 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101020 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101021 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101020 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131105 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4618639 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |