JP4610075B2 - 受光装置 - Google Patents

受光装置 Download PDFInfo

- Publication number

- JP4610075B2 JP4610075B2 JP2000369557A JP2000369557A JP4610075B2 JP 4610075 B2 JP4610075 B2 JP 4610075B2 JP 2000369557 A JP2000369557 A JP 2000369557A JP 2000369557 A JP2000369557 A JP 2000369557A JP 4610075 B2 JP4610075 B2 JP 4610075B2

- Authority

- JP

- Japan

- Prior art keywords

- effect transistor

- field effect

- source

- drain

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Amplifiers (AREA)

Description

【発明の属する技術分野】

本発明は、デジタルカメラやビデオカメラ等に用いる光信号を電気信号に変換する受光装置に関するものである。

【0002】

【従来の技術】

従来の受光装置の回路図を図4に示す。フォトダイオード1は、アノードがグランドGNDに接続されており、カソードが演算増幅器2の反転入力端子(−)に接続されている。演算増幅器2は、非反転入力端子(+)には所定の直流電圧Vrefが印加されており、出力端子が抵抗3を介して反転入力端子(−)に接続されている。そして、演算増幅器2の出力端子が外部端子OUTに接続されている。

【0003】

フォトダイオード1には入射光の強度に応じた光電流IPDが図4に矢印で示す方向に流れる。そして、この光電流IPDは、演算増幅器2の出力端子から抵抗3を介して流れると見なすことができる。また、演算増幅器2には負帰還がかかっているので、演算増幅器2の非反転入力端子(+)と反転入力端子(−)との電圧は等しいと見なすことができる。したがって、外部端子OUTに発生する電圧VOは、抵抗3の抵抗値をRとすると、

VO=IPD・R+Vref

となる。

【0004】

【発明が解決しようとする課題】

しかしながら、上記構成の受光装置では、受光感度を良くするためには、抵抗3の抵抗値を大きくしなければならず、集積化する場合には、チップサイズが大きくなるとともに、時定数が大きくなって周波数特性が悪化するという問題を招く。特に、本構成の受光装置を1つの画素として多数有する画像装置の場合、チップサイズの増大を抑える必要がある。

【0005】

そこで、本発明は、チップサイズの増大を抑えながら、周波数特性の悪化を伴うことなく、受光感度を向上させることができるようにした受光装置を提供することを目的とする。

【0006】

【課題を解決するための手段】

上記の目的を達成するため、本発明の受光装置では、ゲート及びドレインが接続された第1の電界効果トランジスタと、該第1の電界効果トランジスタのドレインに接続されることによって該第1の電界効果トランジスタのドレイン−ソース間に入射光の強度に応じた電流を供給する光電変換部と、オフセット部と、該光電変換部から供給される電流により該第1の電界効果トランジスタのドレイン−ソース間に生成する電圧と該オフセット部で得られた電圧との和がゲート−ソース間に印加される第2の電界効果トランジスタと、該第2の電界効果トランジスタのドレインに反転入力端子が接続されるとともに非反転入力端子に所定の直流電圧が入力される差動増幅器および該差動増幅器の出力端子と反転入力端子間の負帰還路に接続されることにより該第2の電界効果トランジスタのドレイン電流が流れる抵抗とを持つ電流電圧変換部と、を備えている。

【0007】

この構成により、上記オフセット部の電圧を適切に設定しておけば、入射光の強度に応じて光電変換部に発生する光電流よりも大きな値の電流が電流/電圧変換部の抵抗に流れる。

【0008】

【発明の実施の形態】

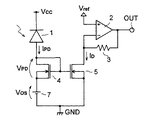

以下に、本発明の実施形態を図面を参照しながら説明する。本発明の第1実施形態である受光装置の回路図を図1に示す。尚、同図に示す全ての構成要素が1チップに集積化されている。フォトダイオード1は、カソードが電源電圧VCCに接続されており、アノードがnチャネルのMOS型の電界効果トランジスタ4のドレインに接続されている。

【0009】

演算増幅器2は、非反転入力端子(+)に所定の直流電圧Vrefが印加されており、反転入力端子(−)がnチャネルのMOS型の電界効果トランジスタ5のドレインに接続されており、出力端子が外部端子OUTに接続されている。演算増幅器2の反転入力端子(−)と出力端子とが抵抗3を介して接続されている。

【0010】

トランジスタ4は、ドレインがフォトダイオード1のアノードに接続されており、ソースはオフセット電圧VOSの電源7の+電極側に接続されており、ゲート−ドレイン間が短絡されている。電源7の−電極側はグランドGNDに接続されている。

【0011】

トランジスタ5は、ゲートがフォトダイオード1のアノードとトランジスタ4のドレインとの接続中点に接続されており、ソースがグランドGNDに接続されており、ドレインが演算増幅器2の反転入力端子(−)と抵抗3との接続中点に接続されている。

【0012】

以上の構成により、外部端子OUTに発生する電圧VOは、トランジスタ5のドレイン電流をID、抵抗3の値をRとすると、

VO=ID・R+Vref

となる。

【0013】

このようにして、トランジスタ5のゲートには、入射光の強度に応じてフォトダイオード1に流れる光電流IPD がゲート−ドレイン間が短絡されたトランジスタ4のドレイン−ソース間を流れることによって生成する電圧VPDとオフセット電圧VOSとの和が印加される。

【0014】

したがって、オフセット電圧VOSの値を適切に設定しておけば、光電流IPDよりも大きな値の電流をトランジスタ5のドレイン電流IDとして得ることができる。これにより、抵抗3の値を大きくすることなく、すなわち、チップサイズの増大、及び、周波数特性の悪化を伴うことなく、受光感度を向上させることができる。

【0016】

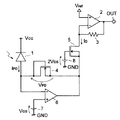

本発明の第2実施形態である受光装置の回路図を図2に示す。尚、同図に示す全ての構成要素が1チップに集積化されている。フォトダイオード1は、カソードが電源電圧VCCに接続されており、アノードがnチャネルのMOS型の電界効果トランジスタ4のドレイン、及び、演算増幅器6の反転入力端子(−)に接続されている。

【0017】

演算増幅器2は、非反転入力端子(+)に所定の直流電圧Vrefが印加されており、反転入力端子(−)がnチャネルのMOS型の電界効果トランジスタ5のドレインに接続されており、出力端子が外部端子OUTに接続されている。演算増幅器2の反転入力端子(−)と出力端子とが抵抗3を介して接続されている。

【0018】

トランジスタ4は、ドレインがフォトダイオード1のアノードと演算増幅器6の非反転入力端子(+)との接続中点に接続されており、ソースが演算増幅器6の出力端子、及び、トランジスタ5のソースに接続されており、ゲート−ドレイン間が短絡されている。

【0019】

トランジスタ5は、ゲートがオフセット電圧VOSの2倍の電源8の+電極側に接続されており、ドレインが演算増幅器2の反転入力端子(−)と抵抗3との接続中点に接続されており、ソースがトランジスタ4のソース及び演算増幅器6の出力端子に接続されている。電源8の−電極側はグランドに接続されている。

【0020】

演算増幅器6は、非反転入力端子(+)がオフセット電圧VOSの電源7の+電極側に接続されており、反転入力端子(−)がフォトダイオード1のアノード、及び、トランジスタ4のドレインに接続されており、出力端子がトランジスタ4のソース及びトランジスタ5のソースに接続されている。電源7の−電極側はグランドGNDに接続されている。

【0021】

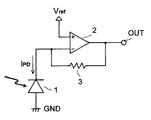

本発明の第3実施形態である受光装置の回路図を図3に示す。尚、同図に示す全ての構成要素が1チップに集積化されている。この第3実施形態では、上記第2実施形態において、演算増幅器6の非反転入力端子(+)に接続されていたオフセット電源をなくすとともに、トランジスタ4のソースにオフセット電圧VOSの電源7の+電極側を接続し、この電源7の−電極側をトランジスタ5のソース、及び、演算増幅器6の出力端子に接続し、トランジスタ5のゲートをグランドGNDに接続した構成である。

【0022】

これらの第2、第3実施形態においても、トランジスタ5のゲート−ソース間には、入射光の強度に応じてフォトダイオード1に流れる光電流IPD がゲート−ドレイン間が短絡されたトランジスタ4のドレイン−ソース間を流れることによって生成する電圧VPDとオフセット電圧VOSとの和が印加されるので、オフセット電圧VOS の値を適切に設定しておけば、光電流IPDよりも大きな値の電流がトランジスタ5のドレイン電流ID として得られるようになり、チップサイズの増大、周波数特性の悪化を伴うことなく、受光感度を向上させることができる。

【0023】

【発明の効果】

以上説明したように、本発明の受光装置によれば、入射光の強度に応じて光電変換部に発生する光電流よりも大きな値の電流を電流/電圧変換部の抵抗に流すことができるので、受光感度を向上させるにあたって上記抵抗の値を大きくすることによるチップサイズの増大を抑えながら、周波数特性の悪化を伴うことなく、受光感度を向上させることができるようになる。また、第1及び第2の実施形態の受光装置を用いた画像装置では、オフセット電圧源を共通化することができ、チップサイズの増大がさらに少なくて済むようになる。

【図面の簡単な説明】

【図1】 本発明の第1実施形態である受光装置の回路図である。

【図2】 本発明の第2実施形態である受光装置の回路図である。

【図3】 本発明の第3実施形態である受光装置の回路図である。

【図4】 従来の受光装置の回路図である。

【符号の説明】

1 フォトダイオード

2 演算増幅器

3 抵抗

4 nチャネルのMOS型の電界効果トランジスタ

5 nチャネルのMOS型の電界効果トランジスタ

6 演算増幅器

7 電源

8 電源

Claims (6)

- ゲート及びドレインが接続された第1の電界効果トランジスタと、

該第1の電界効果トランジスタのドレインに接続されることによって該第1の電界効果トランジスタのドレイン−ソース間に入射光の強度に応じた電流を供給する光電変換部と、

オフセット部と、

該光電変換部から供給される電流により該第1の電界効果トランジスタのドレイン−ソース間に生成する電圧と該オフセット部で得られた電圧との和がゲート−ソース間に印加される第2の電界効果トランジスタと、

該第2の電界効果トランジスタのドレインに反転入力端子が接続されるとともに非反転入力端子に所定の直流電圧が入力される差動増幅器および該差動増幅器の出力端子と反転入力端子間の負帰還路に接続されることにより該第2の電界効果トランジスタのドレイン電流が流れる抵抗とを持つ電流電圧変換部と、

を備えることを特徴とする受光装置。 - 該オフセット部はその正極が該第1の電界効果トランジスタのソースに接続されるとともに、

該第2の電界効果トランジスタのソースが該オフセット部の負極に接続され、該第2の電界効果トランジスタのゲートに該第1の電界効果トランジスタのゲートが接続されることにより、

該光電変換部から供給される電流により該第1の電界効果トランジスタのドレイン−ソース間に生成する電圧と該オフセット部で得られた電圧との和が該第2の電界効果トランジスタのゲート−ソース間に印加されることを特徴とする請求項1記載の受光装置。 - 基準電圧からみて該オフセット部で得られた電圧から該第1の電界効果トランジスタのドレイン−ソース間に生成する電圧を減じた電圧を該第2の電界効果トランジスタのソースに印加すると共に、該第2の電界効果トランジスタのゲートに基準電圧からみて該オフセット部で得られた電圧の2倍の電圧の第2のオフセット部を接続することにより、

該光電変換部から供給される電流により該第1の電界効果トランジスタのドレイン−ソース間に生成する電圧と該オフセット部で得られた電圧との和が該第2の電界効果トランジスタのゲート−ソース間に印加されることを特徴とする請求項1記載の受光装置。 - 基準電圧から該オフセット部で得られた電圧および該第1の電界効果トランジスタのドレイン−ソース間に生成する電圧を減じた電圧を該第2の電界効果トランジスタのソースに印加すると共に、該第2の電界効果トランジスタのゲートに基準電圧を印加することにより、

該光電変換部から供給される電流により該第1の電界効果トランジスタのドレイン−ソース間に生成する電圧と該オフセット部で得られた電圧との和が該第2の電界効果トランジスタのゲート−ソース間に印加されることを特徴とする請求項1記載の受光装置。 - 反転入力端が前記第1の電界効果トランジスタのドレインに接続し、非反転入力端が前記オフセット部の正極に接続し、出力が前記第1の電界効果トランジスタのソース及び前記第2の電界効果トランジスタのソースに接続する第2の差動増幅器を備えることにより、

該光電変換部から供給される電流により該第1の電界効果トランジスタのドレイン−ソース間に生成する電圧と該オフセット部で得られた電圧との和が該第2の電界効果トランジスタのゲート−ソース間に印加されることを特徴とする請求項3記載の受光装置。 - 反転入力端が前記第1の電界効果トランジスタのドレインに接続し、非反転入力端が基準電圧に接続し、出力が前記オフセット部の負極に接続する第2の差動増幅器を備え、前記オフセット部は正極が前記第1の電界効果トランジスタのソースに接続され、負極が前記第2の電界効果トランジスタのソースに接続されることにより、

該光電変換部から供給される電流により該第1の電界効果トランジスタのドレイン−ソース間に生成する電圧と該オフセット部で得られた電圧との和が該第2の電界効果トランジスタのゲート−ソース間に印加されることを特徴とする請求項4記載の受光装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000369557A JP4610075B2 (ja) | 2000-12-05 | 2000-12-05 | 受光装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000369557A JP4610075B2 (ja) | 2000-12-05 | 2000-12-05 | 受光装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002171142A JP2002171142A (ja) | 2002-06-14 |

| JP4610075B2 true JP4610075B2 (ja) | 2011-01-12 |

Family

ID=18839572

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000369557A Expired - Fee Related JP4610075B2 (ja) | 2000-12-05 | 2000-12-05 | 受光装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4610075B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100509907B1 (ko) * | 2003-01-08 | 2005-08-24 | 주식회사 에이디텍 | 포토 다이오드 회로 |

| US7253391B2 (en) * | 2003-09-19 | 2007-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Optical sensor device and electronic apparatus |

| JP2009060424A (ja) | 2007-08-31 | 2009-03-19 | Rohm Co Ltd | 光電変換回路及びこれを用いた固体撮像装置 |

| JP2012065277A (ja) * | 2010-09-17 | 2012-03-29 | Ntt Docomo Inc | 光受信機 |

| EP2797228B1 (en) * | 2013-04-26 | 2016-04-20 | Xenics N.V. | Method for detecting a photocurrent |

| WO2016046994A1 (en) * | 2014-09-25 | 2016-03-31 | Hamamatsu Photonics K.K. | Thermal infrared image sensor |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5006815A (en) * | 1988-10-26 | 1991-04-09 | U.S. Philips Corporation | Linear-gain amplifier arrangement |

| JPH04174566A (ja) * | 1990-11-07 | 1992-06-22 | Canon Inc | 光検出装置 |

| JP3526238B2 (ja) * | 1999-05-13 | 2004-05-10 | シャープ株式会社 | 信号入力回路 |

-

2000

- 2000-12-05 JP JP2000369557A patent/JP4610075B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002171142A (ja) | 2002-06-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP1492334A4 (en) | TUBE-FREE IMAGE ASSEMBLY | |

| US6275541B1 (en) | Digital receiver circuit | |

| WO2014156028A1 (ja) | 固体撮像装置及び撮像装置 | |

| JPH11340745A (ja) | トランスインピーダンス型増幅回路 | |

| US9609249B2 (en) | Solid-state imaging device, imaging apparatus, and electronic apparatus with negative feedback circuit | |

| JP4610075B2 (ja) | 受光装置 | |

| US20130068935A1 (en) | Light receiving circuit | |

| KR100678981B1 (ko) | 고체 촬상 장치 | |

| WO2019214400A1 (zh) | 光检测电路、其驱动方法和平板探测器 | |

| EP1503496A1 (en) | Photocurrent-to-voltage conversion apparatus including non-diode-connected clamping MOS transistor | |

| JP4127480B2 (ja) | 測光回路 | |

| JP4300654B2 (ja) | 固体撮像装置 | |

| US7280144B2 (en) | Solid-state image sensing device with reduced leak current | |

| US20090084942A1 (en) | Light receiving circuit | |

| US7619667B2 (en) | Solid-state image device and camera including solid-state image device for selective outputs | |

| US7605853B2 (en) | Solid-state image sensing device and camera | |

| US11356622B1 (en) | Single-ended capacitive trans-impedance amplifier (CTIA) unit cell for two-color applications | |

| US11480464B2 (en) | Optical sensor | |

| KR100440189B1 (ko) | 신호 증폭 장치 | |

| EP1081858A2 (en) | Current-voltage converter | |

| JP2536842B2 (ja) | 光電変換装置 | |

| US20130038393A1 (en) | Amplifier circuit, integrating circuit, and light-detection device | |

| TWI786955B (zh) | 主動畫素感測電路 | |

| JP2001078093A (ja) | 固体撮像装置 | |

| JP4797600B2 (ja) | 固体撮像素子の出力バッファ回路およびこれを用いた固体撮像装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071205 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100216 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100416 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101012 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101012 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131022 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4610075 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees | ||

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D03 |