JP4608794B2 - High frequency module device and manufacturing method thereof - Google Patents

High frequency module device and manufacturing method thereof Download PDFInfo

- Publication number

- JP4608794B2 JP4608794B2 JP2001081727A JP2001081727A JP4608794B2 JP 4608794 B2 JP4608794 B2 JP 4608794B2 JP 2001081727 A JP2001081727 A JP 2001081727A JP 2001081727 A JP2001081727 A JP 2001081727A JP 4608794 B2 JP4608794 B2 JP 4608794B2

- Authority

- JP

- Japan

- Prior art keywords

- dielectric insulating

- layer

- base substrate

- forming

- frequency module

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Coils Or Transformers For Communication (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、例えばパーソナルコンピュータ、携帯電話機、オーディオ機器等の各種電子機器に好適に搭載され、情報通信機能やストレージ機能等を有して超小型通信機能モジュールを構成する高周波モジュール装置及びその製造方法に関する。

【0002】

【従来の技術】

例えば、音楽、音声或いは画像等の各種情報は、近年、データのデジタル化に伴ってパーソナルコンピュータやモバイルコンピュータ等によっても手軽に扱えるようになっている。また、これらの情報は、音声コーデック技術や画像コーデック技術により帯域圧縮が図られて、デジタル通信やデジタル放送により各種の通信端末機器に対して容易にかつ効率的に配信される環境が整いつつある。例えば、オーディオ・ビデオデータ(AVデータ)は、携帯電話機によって屋外での受信も可能である。

【0003】

ところで、データ等の送受信システムは、家庭を始めとして小規模な地域内においても好適なネットワークシステムの提案によって、様々に活用されるようになっている。ネットワークシステムとしては、例えばIEEE802.11aで提案されているような5GHz帯域の狭域無線通信システム、IEEE802.11bで提案されているような2.45GHz帯域の無線LANシステム或いはBluetoothと称される近距離無線通信システム等の種々の次世代ワイヤレスシステムが注目されている。

【0004】

データ等の送受信システムは、かかるワイヤレスネットワークシステムを有効に利用して、家庭内や屋外等の様々な場所において手軽にかつ中継装置等を介することなく様々なデータの授受、インターネット網へのアクセスやデータの送受信が可能となっている。

【0005】

一方、データ等の送受信システムにおいては、小型軽量で携帯可能であり上述した通信機能を有する通信端末機器の実現が必須となる。通信端末機器においては、送受信部においてアナログの高周波信号の変復調処理を行うことが必要であることから、一般に図27に示すような送受信信号からいったん中間周波数に変換するようにしたスーパーへテロダイン方式による高周波送受信回路100が備えられる。

【0006】

高周波送受信回路100には、アンテナや切替スイッチを有して情報信号を受信或いは送信するアンテナ部101と、送信と受信との切替を行う送受信切替器102とが備えられる。高周波送受信回路100には、周波数変換回路部103や復調回路部104等からなる受信回路部105が備えられる。高周波送受信回路100には、パワーアンプ106やドライブアンプ107及び変調回路部108等からなる送信回路部109が備えられる。高周波送受信回路100には、受信回路部105や送信回路部109に基準周波数を供給する基準周波数生成回路部が備えられる。

【0007】

以上のような構成の高周波送受信回路100においては、詳細を省略するが、各段間にそれぞれ介挿された種々のフィルタ、局発装置(VCO)、SAWフィルタ等の大型機能部品や、整合回路或いはバイアス回路等の高周波アナログ回路に特有なインダクタ、抵抗、キャパシタ等の受動部品の点数が非常に多い構成となっている。したがって、高周波送受信回路100は、全体に大型となり、通信端末機器の小型軽量化に大きな障害となっていた。

【0008】

一方、通信端末機器には、図28に示すように中間周波数への変換を行わずに情報信号の送受信を行うようにしたダイレクトコンバージョン方式による高周波送受信回路110も用いられる。高周波送受信回路110においては、アンテナ部111によって受信された情報信号が送受信切替器112を介して復調回路部113に供給されて直接ベースバンド処理が行われる。高周波送受信回路110においては、ソース源で生成された情報信号が変調回路部114において中間周波数に変換されることなく直接所定の周波数帯域に変調され、アンプ115と送受信切替器112を介してアンテナ部111から送信される。

【0009】

以上のような構成の高周波送受信回路110においては、情報信号について中間周波数の変換を行うことなくダイレクト検波を行うことによって送受信する構成であることから、フィルタ等の部品点数が低減されて全体構成の簡易化が図られ、より1チップ化に近い構成が見込まれるようになる。しかしながら、高周波送受信回路110においても、後段に配置されたフィルタ或いは整合回路の対応が必要となる。また、高周波送受信回路110は、高周波段で一度の増幅を行うことから充分なゲインを得ることが困難となり、ベースバンド部でも増幅操作を行う必要がある。したがって、高周波送受信回路110は、DCオフセットのキャンセル回路や余分なローパスフィルタを必要とし、さらに全体の消費電力が大きくなるといった問題があった。

【0010】

【発明が解決しようとする課題】

従来の高周波送受信回路は、上述したようにスーパーへテロダイン方式及びダイレクトコンバージョン方式のいずれにおいても、通信端末機器の小型軽量化等の要求仕様に対して充分な特性を満足し得ないものであった。このため、高周波送受信回路については、例えばSi−CMOS回路等をベースとして簡易な構成によって小型化を図ったモジュール化について種々の試みが図られている。すなわち、試みの1つは、例えば特性のよい受動素子をSi基板上に形成するとともにフィルタ回路や共振器等をLSI上に作り込み、さらにベースバンド部分のロジックLSIも集積化することで、いわゆる1チップ化高周波モジュールを製作する方法である。

【0011】

しかしながら、この1チップ化高周波モジュールにおいては、図29に示すように、いかにして性能のよいインダクタ部120をLSI上に形成するかが極めて重要となる。かかる1チップ化高周波モジュールでは、Si基板121及びSiO2絶縁層122のインダクタ部形成部位123に対応して大きな凹部124を形成する。1チップ化高周波モジュールは、凹部124に臨ませて第1の配線層125を形成するとともに凹部124を閉塞する第2の配線層126が形成されてコイル部127を構成する。また、1チップ化高周波モジュールは、他の対応として配線パターンの一部を基板表面から立ち上げて空中に浮かすといった対応を図ることによってインダクタ部120が形成されていた。しかしながら、この1チップ化高周波モジュールは、いずれもインダクタ部120を形成する工程が極めて面倒であり、工程の増加によってコストがアップするといった問題があった。

【0012】

また、この1チップ化高周波モジュールにおいては、アナログ回路の高周波回路部と、デジタル回路のベースバンド回路部との間に介在するSi基板の電気的干渉が大きな問題となった。

【0013】

以上のような欠点を改善する高周波モジュールとしては、例えば図30に示したSi基板をベース基板に用いた高周波モジュール130や、図31に示したガラス基板をベース基板に用いた高周波モジュール140が提案されている。

【0014】

この高周波モジュール130は、Si基板131上にSiO2層132を形成した後に、リソグラフィ技術によって受動素子形成層133が成膜形成されてなる。

【0015】

受動素子形成層133には、詳細を省略するが、その内部に配線パターンとともにインダクタ部、抵抗体部或いはキャパシタ部等の受動素子が薄膜形成技術や厚膜形成技術によって多層に形成されている。

【0016】

高周波モジュール130は、受動素子形成層133上にビア(中継スルーホール)等を介して内部配線パターンと接続された端子部が形成され、これら端子部にフリップチップ実装法等により高周波ICやLSI等の回路素子134が直接実装されて構成される。この高周波モジュール130は、例えばマザー基板等に実装することで、高周波回路部とベースバンド回路部とを区分して両者の電気的干渉を抑制することが可能とされる。

【0017】

ところで、かかる高周波モジュール130においては、導電性を有するSi基板131が、受動素子形成層133内に各受動素子を形成する際に機能するが、各受動素子の良好な高周波特性にとって邪魔になるといった問題があった。

【0018】

一方、高周波モジュール140は、上述した高周波モジュール130におけるSi基板131の問題を解決するために、ベース基板にガラス基板141が用いられている。高周波モジュール140も、ガラス基板141上にリソグラフィ技術によって受動素子形成層142が成膜形成されてなる。受動素子形成層142には、詳細を省略するが、その内部に配線パターンとともにインダクタ部、抵抗体部或いはキャパシタ部等の受動素子が薄膜形成技術や厚膜形成技術によって多層に形成されている。

【0019】

高周波モジュール140は、受動素子形成層142上にビア等を介して内部配線パターンと接続された端子部が形成され、これら端子部にフリップチップ実装法等により高周波ICやLSI等の回路素子143が直接実装されて構成される。この高周波モジュール140は、導電性を有しないガラス基板141を用いることで、ガラス基板141と受動素子形成層142との容量的結合度が抑制され受動素子形成層142内に良好な高周波特性を有する受動素子を形成することが可能である。

【0020】

ところで、高周波モジュール140においては、例えばマザー基板等に実装するために、受動素子形成層142の表面に端子パターンを形成するとともにワイヤボンディング法等によってマザー基板との接続が行われる。したがって、高周波モジュール140は、端子パターン形成工程やワイヤボンディング工程が必要となる。

【0021】

これらの1チップ化高周波モジュールにおいては、上述したようにベース基板上に高精度の受動素子形成層が形成される。ベース基板には、受動素子形成層を薄膜形成する際に、スパッタリング時の表面温度の上昇に対する耐熱特性、リソグラフィ時の焦点深度の保持、マスキング時のコンタクトアライメント特性が必要となる。ベース基板は、このために高精度の平坦性が必要とされるとともに、絶縁性、耐熱性或いは耐薬品性等が要求される。

【0022】

上述したSi基板131やガラス基板141は、かかる特性を有しておりLSIと別プロセスにより低コストで低損失な受動素子の形成を可能とする。また、Si基板131やガラス基板141は、従来のセラミックモジュール技術で用いられる印刷によるパターン等の形成方法或いはプリント配線基板に配線パターンを形成する湿式エッチング法等と比較して、高精度の受動素子の形成が可能であるとともに、素子サイズをその面積が1/100程度まで縮小することを可能とする。さらに、Si基板131やガラス基板141は、受動素子の使用限界周波数帯域を20GHzまで高めることも可能とする。

【0023】

ところで、かかる1チップ化高周波モジュールにおいては、上述したようなSi基板131やガラス基板141上に受動素子とともに配線やグランド等が薄膜形成技術や厚膜形成技術によって多層に形成されている。このため、図32に示す高周波モジュール200においては、Si基板131やガラス基板141上に形成された受動素子とグランド部201、ここでは主に、インダクタ部202とグランド部201との間の距離が近いことから寄生容量の影響によりインダクタ部202のインダクタンスのQ値が劣化するといった問題があった。

【0024】

高周波モジュール200においては、かかる問題を防止するために、例えば第1の薄膜層203及び第2の薄膜層204を厚くしてインダクタ部202とグランド部201との距離を離し、インダクタ部202に対する寄生容量の影響を低減する方法が提案されている。また、高周波モジュール200においては、図33に示すように、インダクタ部202の下方にグランド部201が形成されない配線禁止領域Aを施すことによりインダクタ部202に対する寄生容量の影響を低減する方法も提案されている。

【0025】

しかしながら、第1の方法は、インダクタ部202と配線205とを配線するためのビア206を形成する際に第1の薄膜層203が厚くなったためにビア206の径が大きくなってしまい、高周波モジュール200の厚みや面積が大型化するといった問題がある。

【0026】

一方、第2の方法は、グランド部201がマイクロストリップ線路のシールド、RF電流が他の配線への干渉や不要な結合をすることを防ぐシールドとして機能していることから、配線禁止領域Aでこれらのシールドが機能しなくなる。また、第2の方法は、グランド部201を電源や受動素子を電気的に接続させる配線としても機能させていることから、配線禁止領域Aを避けて配線を施すことにより、高周波モジュール200の面積が大型化するといった問題がある。

【0027】

そこで、本発明は、ベース基板上に形成された配線層の受動素子に対する寄生容量の影響を低減するとともに、高機能化及び小面積化、小型化を図った高周波モジュール装置及びその製造方法を提供することを目的に提案されたものである。

【0028】

【課題を解決するための手段】

上述した目的を達成する本発明にかかる高周波モジュール装置は、主面上に配線層を有するベース基板と、ベース基板上に、誘電絶縁材料をスピンコート法で塗布することにより形成された誘電絶縁層と、当該誘電絶縁層上に薄膜形成された受動素子とを有する高周波素子部とを備え、誘電絶縁層の形成面上に設けた誘電絶縁材料の流れを抑制する流動抑制部により、誘電絶縁層に厚みが部分的に大となる肉厚部が形成され、この誘電絶縁層の肉厚部上に受動素子が形成されていることを特徴としている。

【0029】

以上のように構成された本発明にかかる高周波モジュール装置によれば、ベース基板の誘電絶縁層の形成面上に流動抑制部が設けられたことにより、回転操作された状態のベース基板に滴下された誘電絶縁材料の周面へと広がる流れが流動抑制部により抑制されて、誘電絶縁層に厚みが部分的に大となる肉厚部が形成される。したがって、高周波モジュール装置によれば、誘電絶縁層の肉厚部上に形成された受動素子とベース基板上に形成された配線層との距離が保持され、受動素子に対する配線層からの寄生容量の影響が低減される。

【0030】

また、上述した目的を達成する本発明にかかる高周波モジュール装置の製造方法は、主面上に配線層を有するベース基板を形成するベース基板形成工程と、ベース基板上にスピンコート法により誘電絶縁材料を塗布することにより形成された誘電絶縁層と、当該誘電絶縁層上に薄膜形成される受動素子とを有する高周波素子部を形成する高周波素子部形成工程とを経て高周波モジュール装置を製造する。高周波素子部形成工程は、ベース基板上にスピンコート法により塗布される誘電絶縁材料の流れを抑制する流動抑制部を形成する流動抑制部形成工程と、流動抑制部が形成されたベース基板上に、スピンコート法により塗布された誘電絶縁材料の流れが流動抑制部により抑制されることで部分的に厚みが大となる肉厚部を有する誘電絶縁層を形成する誘電絶縁層形成工程と、誘電絶縁層の肉厚部上に受動素子を形成する受動素子形成工程とを有することを特徴とする。

【0031】

以上のように構成された本発明にかかる高周波モジュール装置の製造方法によれば、流動抑制部形成工程によりベース基板上に形成された流動抑制部が、誘電絶縁層形成工程でスピンコート法により塗布された誘電絶縁材料の流れを抑制して誘電絶縁層に部分的な肉厚部を形成する。これにより、高周波モジュール装置の製造方法では、受動素子形成工程により誘電絶縁層の肉厚部上に形成された受動素子とベース基板上に形成された配線層との距離が保持され、受動素子に対する配線層からの寄生容量が低減された高周波モジュール装置が製造される。

【0032】

【発明の実施の形態】

以下、本発明の実施の形態について、図面を参照して詳細に説明する。実施の形態として図1に示した高周波モジュール装置1は、詳細を後述するベース基板部製作工程で形成されたベース基板部2の最上層が高精度の平坦面からなる高周波素子層形成面3として構成されているとともに、この高周波素子層形成面3上に詳細を後述する高周波素子層部製作工程によって高周波素子層部4が形成されてなる。高周波モジュール装置1は、ベース基板部2が、上層に形成された高周波素子層部4に対する電源系の配線部や制御系の配線部或いはグランド部を構成する。高周波モジュール装置1には、図1に示すように、高周波素子層部4の上面に高周波IC90やチップ部品91が実装されるとともにシールドカバー92によって封装される。高周波モジュール装置1は、いわゆる1チップ部品としてマザー基板93上に実装される。

【0033】

ベース基板部2は、両面基板からなるコア基板5と、このコア基板5をコアとしてその第1の主面5a側に形成された第1のパターン配線層6と、第2の主面5b側に形成された第2のパターン配線層7とからなる。ベース基板部2には、コア基板5に対して第1の樹脂付銅箔8及び第2の樹脂付銅箔9が接合される。第1の樹脂付銅箔8は、コア基板5の第1の主面5a側に接合されて、このコア基板5とともに2層からなる第1のパターン配線層6を形成する。第2の樹脂付銅箔9は、コア基板5の第2の主面5b側に接合されて、このコア基板5とともに2層からなる第2のパターン配線層7を形成する。

【0034】

ベース基板部2の構成並びに作製工程について、以下図2乃至図10を参照しながら詳細に説明する。

【0035】

ベース基板部2の製作工程は、図2に示すように、コア基板5の第1の主面5a及び第2の主面5bに適宜の第1のパターン配線層12及び第2のパターン配線層13やコア基板5を貫く複数のビアホール14を形成する第1のパターン配線層形成工程s−1と、コア基板5の第1の主面5a及び第2の主面5bに第1の樹脂付銅箔8と第2の樹脂付銅箔9とをそれぞれ接合する第1の銅箔接合工程s−2と、これら樹脂付銅箔8、9とにビア15、16を形成するビア形成工程s−3とを有する。ベース基板部2の製作工程は、接合された樹脂付銅箔8、9にそれぞれ適宜の第3のパターン配線層17及び第4のパターン配線層18とを形成する第2のパターン配線層形成工程s−4とを経て、ベース基板中間体19を製作する。

【0036】

ベース基板部2の製作工程は、ベース基板中間体19に対して第3のパターン配線層17及び第4のパターン配線層18を被覆する第3の樹脂付銅箔10と第2の樹脂付銅箔11とをそれぞれ接合する第2の銅箔接合工程s−5を有する。ベース基板部2の製作工程は、第3の樹脂付銅箔10と第4の樹脂付銅箔11とに対して研磨処理を施して第1の主面5a側の最上層に高周波素子層形成面3を形成する研磨工程s−6を経てベース基板部2を製作する。

【0037】

コア基板5は、低誘電率で低いTanδ、すなわち高周波特性に優れた基材、例えばポリフェニレンエーテル(PPE)、ビスマレイドトリアジン(BT−resin)、ポリテトラフルオロエチレン(商標名テフロン)、ポリイミド、液晶ポリマ(LCP)、ポリノルボルネン(PNB)、セラミック或いはセラミックと有機基材の混合体等が用いられて形成される。コア基板5は、機械的剛性とともに耐熱性、耐薬品性を有し、例えば上述した基材よりもさらに廉価なエポキシ系基板FR−5等も用いられる。コア基板5は、上述した基材によって形成されることで、高精度に形成されることによって比較的高価となるSi基板やガラス基板と比較して廉価であり、材料コストの低減が図られる。

【0038】

コア基板5には、図3に示すように、第1の主面5aと第2の主面5bの全面に銅箔層20a、20bが形成されている。コア基板5には、図4に示すように、第1のパターン配線層形成工程s−1が施される。コア基板5は、ドリルやレーザによる孔穿加工が施されて所定の位置にそれぞれビアホール14が形成される。コア基板5には、メッキ等によって内壁に導通処理が施されたビアホール14内に、導電ペースト21を埋め込んだ後にメッキ法によって蓋形成が行われる。コア基板5は、銅箔層20a、20bに対してフォトリソグラフ処理が施されることによって、第1の主面5aと第2の主面5bとにそれぞれ所定の第1のパターン配線層12及び第2のパターン配線層13とが形成される。

【0039】

以上の工程を経たコア基板5には、第1の銅箔接合工程s−2によって、図5に示すように、第1のパターン配線層12及び第2のパターン配線層13をそれぞれ被覆して第1の樹脂付銅箔8と第2の樹脂付銅箔9とが第1の主面5aと第2の主面5bに接合される。第1の樹脂付銅箔8と第2の樹脂付銅箔9には、それぞれ銅箔層8a、9aの一方主面の全体に樹脂層8b、9bが裏打ちされたいわゆる樹脂付銅箔が用いられる。

【0040】

第1の樹脂付銅箔8及び第2の樹脂付銅箔9は、樹脂層8b、9b側を接合面として、コア基板5の第1の主面5aと第2の主面5bとに接着樹脂(プリプレグ)によって接合される。なお、これら第1の樹脂付銅箔8及び第2の樹脂付銅箔9は、樹脂層8b、9bが熱可塑性樹脂によって形成される場合には、接着樹脂を不要としてコア基板5に接合される。

【0041】

第1の樹脂付銅箔8と第2樹脂付銅箔9には、コア基板5に接合された状態においてビア形成工程s−3が施されて、図6に示すように、上述した各ビアホール14に対応する部位に対してフォトリソグラフ処理が施されることにより、それぞれビア15、16が形成される。ビア形成工程s−3は、ビア15、16の形成部位にフォトリソグラフ処理を施した後、湿式エッチングを行って第1の樹脂付銅箔8と第2樹脂付銅箔9とに開口部22a、22bを形成し、これら開口部22a、22bをマスクとしてレーザ加工を施こすことによって第1のパターン配線層12或いは第2のパターン配線層13のランド部が受けとなってそれぞれにビア15、16を形成する。

【0042】

第1の樹脂付銅箔8と第2樹脂付銅箔9には、図7に示すように、ビアメッキ等によりビア15、16の内壁に導通処理が施されるとともにメッキ法や導電ペーストの埋め込みにより導電材23a、23bが充填される。第1の樹脂付銅箔8及び第2樹脂付銅箔9には、第2のパターン配線層形成工程s−4により、銅箔層8a、9aにそれぞれ所定のパターンニングが施されて、第3のパターン配線層17及び第4のパターン配線層18とが形成される。第2のパターン配線層形成工程s−4は、上述した第1のパターン配線層形成工程s−1と同様に、銅箔層8a、9aに対してフォトリソグラフ処理を施こすことにより樹脂層8b、9b上にそれぞれ第3のパターン配線層17と第4のパターン配線層18とを形成してベース基板中間体19を製作する。

【0043】

ベース基板部製作工程においては、ベース基板部2に後述する高周波素子層部4を形成するために、ベース基板中間体19に対して高精度の平坦性を有する高周波素子層形成面3を形成する研磨工程が施される。ベース基板中間体19には、第2の銅箔接合工程s−5により、図8に示すように第3のパターン配線層17及び第4のパターン配線層18をそれぞれ被覆して第3の樹脂付銅箔10と第4の樹脂付銅箔11とが第1の主面5a及び第2の主面5bにそれぞれ接合される。第3の樹脂付銅箔10及び第4の樹脂付銅箔11も、上述した第1の樹脂付銅箔8や第2の樹脂付銅箔9と同様に、それぞれ銅箔層10a、11aの一方主面の全体に亘って樹脂層10b、11bが裏打ちされたいわゆる樹脂付銅箔が用いられる。

【0044】

第3の樹脂付銅箔10及び第4の樹脂付銅箔11は、図9に示すように、樹脂層10b、11bを接合面として、ベース基板中間体19の表裏主面に接着樹脂(プリプレグ)によって接合される。なお、第3の樹脂付銅箔10及び第4の樹脂付銅箔11も、樹脂層10b、11bが熱可塑性樹脂によって形成される場合には、接着樹脂を不要としてベース基板中間体19に接合される。

【0045】

ベース基板中間体19には、研磨工程s−6により、接合した第3の樹脂付銅箔10と第4の樹脂付銅箔10とに対して研磨処理が施される。研磨工程s−6は、例えばアルミナとシリカの混合液からなる研磨材により第3の樹脂付銅箔10と第4の樹脂付銅箔11の全体を研磨することによってベース基板中間体19の両面を精度の高い平坦面に形成する。研磨工程s−6においては、図10に示すように、第3の樹脂付銅箔10側、換言すれば高周波素子層形成面3については第3のパターン配線層17が露呈するまでの研磨を施す。また、研磨工程s−6においては、第4の樹脂付銅箔11側については第4のパターン配線層18を露呈させずに樹脂層11bが所定の厚みΔxを残すようにして研磨を施す。

【0046】

ベース基板部製作工程は、上述した各工程によりコア基板5からベース基板中間体19を経て、良好な平坦精度を有する高周波素子層形成面3が形成されてなるベース基板部2を製作する。ベース基板部製作工程は、ベース基板中間体19を製作する工程を従来の多層基板の製作工程と同様とすることで、多層基板の製作プロセスをそのまま適用可能であるとともに、量産性も高いといった特徴を有している。なお、ベース基板部製作工程については、上述した工程に限定されるものではなく、従来採用されている種々の多層基板の製作工程が採用されてもよいことは勿論である。

【0047】

ベース基板部2は、上述したようにコア基板5の第1の主面5a側に接合された第1の樹脂付銅箔8によって、第3のパターン配線層17が形成されている。ベース基板部2は、この第3のパターン配線層17が、第3の樹脂付銅箔10の樹脂層10bを第3のパターン配線層17が露呈するまで研磨が施された構造となっている。ベース基板部2は、後述する高周波素子層部製作工程において、第3のパターン配線層17上に高周波素子層部4を形成することで、第3のパターン配線層17を薬品、機械的或いは熱的負荷から保護する樹脂層10bが不要となる。ベース基板部2は、かかる構成によって後述する高周波素子層部製作工程において、第3のパターン配線層17が高周波素子層部に対する電源系の配線部や制御系の配線部或いはグランド部を構成する。

【0048】

ベース基板部2は、上述したようにコア基板5の第2の主面5b側に接合された第2の樹脂付銅箔9によって、第4のパターン配線層18が形成されている。ベース基板部2は、この第4のパターン配線層18が、第4の樹脂付銅箔11の樹脂層11bの研削量を制限することによって第4のパターン配線層18が露呈されない構造となっている。ベース基板部2は、かかる構成によって後述する高周波素子層部製作工程において、第4のパターン配線層18が残された樹脂層11b(誘電体層)によって薬品や機械的或いは熱的負荷から保護されるようにする。第4のパターン配線層18は、高周波素子層部4を形成した後に、上述した樹脂層11bが切削除去されることで露呈されて入出力端子部24を構成する。

【0049】

以上のようにして製作されたベース基板部2には、後述する高周波素子層形成工程を経て高周波素子層形成面3上に高周波素子層部4が積層形成される。高周波素子層部4には、平坦化されたベース基板部2の高周波素子層形成面3上に、誘電絶縁材料からなる第1の誘電絶縁層30乃至第3の誘電絶縁層32と、誘電絶縁材料の流れを抑制する流動抑制部33と、薄膜形成技術を用いて形成されたキャパシタ部26、レジスタ部27等の受動素子が内蔵された素子形成層部28と、一部にインダクタ部25が形成された配線層部29とが形成されてなる。高周波素子層部4には、配線層部29上に高周波IC90やチップ部品91が実装されるとともに、全体がシールドカバー92によって覆われる。

【0050】

なお、ベース基板部製作工程においては、コア基板5に対して第2の樹脂付銅箔9を介して接合される第4の樹脂付銅箔11が、銅箔部11aを研磨されることになる。ベース基板部製作工程においては、接合された各構成部材がプレス機によってプレスされて一体化される。ベース基板部製作工程においては、金属製のプレス面と第4の樹脂付銅箔11とのなじみがよく、精度のよいプレスが行われるようになる。したがって、第4の樹脂付銅箔11については、銅箔部が配線層を構成しないことから、銅貼りでなく他の樹脂付金属箔であってもよい。

【0051】

上述したベース基板部製作工程においては、両面基板からなるコア基板5をコアとしてその第1の主面5aと第2の主面5bとに第1の樹脂付銅箔8乃至第4の樹脂付銅箔11とを接合して4層構成のベース基板部2を製作する工程を採用したが、本発明はかかるベース基板部の製作工程に限定されるものではないことは勿論である。ベース基板部の製作工程としては、例えば2枚の両面基板を接着樹脂(プリプレグ)によって接合されることで上述したベース基板部2と同様のベース基板部が製作される。

【0052】

高周波素子層部4の構成並びに作製工程について、以下図11乃至図20を参照しながら詳細に説明する。

【0053】

高周波素子層部4の製作工程は、上述した工程を経て製作されたベース基板部2の平坦化された高周波素子層形成面3上に、第1の誘電絶縁層30を成膜形成する第1の誘電絶縁層形成工程s−7と、第1の誘電絶縁層30上に誘電絶縁材料の流れを抑制する流動抑制部33を形成する流動抑制部形成工程s−8と、流動抑制部33が形成された第1の誘電絶縁層30上に第2の誘電絶縁層31を成膜形成する第2の誘電絶縁層形成工程s−9と、第2の誘電絶縁層31上に素子形成層部28を形成するための下地処理を施す下地処理工程s−10と、素子形成層部28内に各受動素子を形成する受動素子形成工程s−11との工程を経る。高周波素子層部4の製作工程は、素子形成層部28を被覆するとともに配線層部29を形成するための第3の誘電絶縁層32を成膜形成する第3の誘電絶縁層形成工程s−12と、配線層部29に所定のパターン配線34や受動素子を形成する配線層形成工程s−13と、表裏主面を被覆するレジスト層35a、35bを形成するレジスト層形成工程s−14とを経て、高周波モジュール装置1を製作する。

【0054】

ベース基板部2には、第1の誘電絶縁層形成工程s−7において、図12に示すように、高周波素子層形成面3上に誘電絶縁材料が供給されて例えばスピンコート法により第1の誘電絶縁層30が成膜形成される。誘電絶縁材料には、コア基板5と同様に低誘電率で低いTanδ、すなわち高周波特性に優れかつ耐熱性や耐薬品性に優れた基材が用いられる。誘電絶縁材料には、具体的には、ベンゾシクロブテン(BCB)、ポリイミド、ポリノルボルネン(PNB)、液晶ポリマ(LCP)或いはエポキシ樹脂やアクリル系樹脂が用いられる。

【0055】

第1の誘電絶縁層30上には、流動抑制部作製工程s−8において、図13に示すように、例えばメッキ法により金属膜からなる流動抑制部33が厚膜形成される。流動抑制部33は、詳細な構成については後述するが、厚みが50μm乃至100μm程度に厚膜形成されてなる。なお、流動抑制部33の作製は、必ずしもメッキ法に限定されることはなく、金属膜の厚膜形成が可能とされる、例えばスクリーン印刷法等を適用して成膜してもよい。

【0056】

第1の誘電絶縁層の主面に形成された流動抑制部33上には、第2の誘電絶縁層形成工程s−9において、図14に示すように、誘電絶縁材料が供給されて例えばスピンコート法により第2の誘電絶縁層31が成膜形成される。誘電絶縁材料には、第1の誘電絶縁層30と同様に低誘電率で低いTanδ、すなわち高周波特性に優れかつ耐熱性や耐薬品性に優れた基材が用いられる。

【0057】

第2の誘電絶縁層形成工程s−9においては、図14に示すように、回転操作されるベース基板部2に滴下された誘電絶縁材料が外周方向へと広がる際に、第1の誘電絶縁層30上に形成された流動抑制部33によって流れが抑制されて部分的に厚みが大となる肉厚部36を有する第2の誘電絶縁層31が形成される。第2の誘電絶縁層形成工程s−9においては、第2の誘電絶縁層31に対して第1の誘電絶縁層30を貫通する多数のビア37が形成される。各ビア37は、高周波素子層形成面3に露呈された第3のパターン配線層17の所定のランド17aに対応して形成され、ランド17aを外方に臨ませる。各ビア37は、誘電絶縁材料として感光性樹脂を用いた場合には、所定のパターンニングに形成されたマスクを第2の誘電絶縁層31に取り付けてフォトリソグラフ法により形成される。各ビア37は、その他適宜の方法によっても形成される。

【0058】

下地処理工程s−10においては、図15に示すように、各ビア37を含む第2の誘電絶縁層31の表面上に、例えばスパッタリング法等によって全面に亘って例えばニッケル層と銅層とからなる配線層38が成膜形成されて素子形成層部28となる。配線層38は、ニッケル層と銅層の厚みがそれぞれ50nm乃至500nm程度に成膜されてなる。下地処理工程s−10においては、配線層38のレジスタ部27の形成部位をレジストでマスキングした状態で硝酸/硫酸/酢酸の混合液からなるエッチング液によってエッチング処理を施すことにより、配線層38を除去する処理を行う。

【0059】

配線層38には、受動素子層形成工程s−11が施されてレジスタ部27やキャパシタ部26が形成される。配線層38には、図15に示すように、除去された部位にリフトオフ法によって窒化タンタル層39が形成される。この窒化タンタル層39は、レジスト処理された全面に窒化タンタル(TaN)がスパッタリングされ、レジスト層部分の窒化タンタルが取り去られることにより配線層38が除去されたレジスタ部27の対応部位にのみ形成される。

【0060】

配線層38には、図15に示すようにキャパシタ部26の形成部位にも窒化タンタル層40が形成される。配線層38には、キャパシタ部形成部位を除く全面にレジストコーティングが行われた状態で、ホウ酸アンモニウム等の電解液中で窒化タンタルが陽極となるように電界がかけられる、いわゆる陽極酸化が施される。この陽極酸化処理は、100V、30分程度の電界印加により行われることにより、窒化タンタル層40が酸化して、タンタルオキサイト(TaO2)層41を形成する。

【0061】

配線層38には、必要な配線パターンだけを残すようにフォトリソグラフ処理によってレジストパターンニングが行われる。タンタルオキサイト層41には、レジストを取り去った後にマスキングが施され、例えばリフトオフ法によってニッケル層と銅層とからなる上部電極42が形成される。高周波素子層部製作工程においては、以上の工程を経て、図16に示すベース基板部2上に流動抑制部33や受動素子等が形成された高周波モジュール装置中間体43が製作される。

【0062】

高周波素子層部製作工程においては、以上の工程を経て製作された高周波モジュール装置中間体43に対して、第3の誘電絶縁層形成工程s−12によって図17に示すように第3の誘電絶縁層32が成膜形成される。第3の誘電絶縁層形成工程s−12は、上述した第1の誘電絶縁層30及び第2の誘電絶縁層31と同様の方法によって第3の誘電絶縁層32を形成するとともに、この第3の誘電絶縁層32に配線層38に形成された所定のパターンやキャパシタ部26の上部電極42を外方に臨ませる複数のビアホール44を形成する。

【0063】

高周波素子層部製作工程においては、配線層形成工程s−13により、第3の誘電絶縁層32上にパターン配線34が形成される。配線層形成工程s−13は、具体的にはスパッタリング法等によって第3の誘電絶縁層32上にニッケル層及び銅層とかなるスパッタ層を成膜形成し、このスパッタ層に対してフォトリソグラフ処理を施して所定のパターンニングを行う。配線層形成工程s−13は、さらにスパッタ層に対して電界メッキにより数μm程度の厚みを有する銅メッキを選択的に行った後に、メッキ用レジストを除去しさらにスパッタ層を全面的にエッチングすることによって図18に示すように配線層部29を形成する。

【0064】

配線層部29の一部には、第2の誘電絶縁層作製工程s−9にて形成された肉厚部36の上方にインダクタ部25が形成される。インダクタ部25は、肉厚部36の上方に形成されることで、電源系の配線部や制御系の配線部或いはグランド部を構成する第3のパターン配線層17に対する距離が大となり、第3のパターン配線層17から受ける寄生容量の影響が低減されてインダクタンスのQ値の劣化が抑制される。インダクタ部25は、直列抵抗値が問題となるが、上述したようにスパッタ層に対して電解メッキを施す厚膜形成技術によって形成することで充分な厚みを以って形成され、損失の低下が抑制される。

【0065】

高周波素子層部製作工程においては、後述するレジスト層形成工程s−14により第4のパターン配線層18の主面にレジスト層35bを形成することで、第4のパターン配線層18を薬品、機械的或いは熱的負荷から保護する樹脂層11bが不要となる。高周波素子層部製作工程においては、樹脂層11bに対して研磨加工を施すことにより、第4のパターン配線層18を露呈させる。

【0066】

高周波素子層部製作工程においては、レジスト層形成工程s−14により、図19に示すように、高周波素子層部4の表面全体とベース基板部2の第4のパターン配線層18とにレジスト層35a、35bをそれぞれコーティングする。高周波素子層部製作工程においては、これらレジスト層35a、35bに対してマスクパータンを介してフォトリソグラフ処理を施し、所定の位置に開口部45a、45bを形成する。高周波素子層部製作工程においては、図20に示すように、これら開口部45a、45bに無電解ニッケル/銅メッキを施してそれぞれ電極端子46a、46bを形成することにより、ベース基板部2上に高周波素子層部4が形成された高周波モジュール装置1を製作する。

【0067】

高周波モジュール装置1は、図1に示すように、高周波素子層部4側に形成された電極端子46aが、高周波IC90やチップ部品91を搭載して接続する接続端子を構成する。高周波モジュール装置1は、ベース基板部2の第4のパターン配線層18側に形成された電極端子46bが、例えばマザー基板93に搭載される際の接続端子及び入出力端子部24を構成する。高周波IC90は、例えばフリップチップ94を介するフリップチップ法によって実装される。

【0068】

なお、高周波モジュール装置1は、高周波素子層部4の表面に搭載される高周波IC90やチップ部品91が、シールドカバー92によって覆われている。このため、高周波モジュール装置1においては、高周波IC90やチップ部品91からの発熱がシールドカバー92内にこもるために、例えば図21に示すような高周波IC90の上面とシールドカバー92の内面との間に、熱伝導性樹脂材70等を充填する放熱構造を設けることが好ましい。

【0069】

以上のように構成される高周波モジュール装置1においては、上述したように、第1の誘電絶縁層30上に誘電絶縁材料の流れを抑制する流動抑制部33が形成されることにより、第2の誘電絶縁層31の厚みが部分的に大となる肉厚部36が形成される。高周波モジュール装置1においては、第2の誘電絶縁層31の肉厚部36の上方にインダクタ部25が形成されていることから、インダクタ部25とグランド部を構成する第3のパターン配線層17との距離が大となる。したがって、高周波モジュール装置1においては、第3のパターン配線層17のインダクタ部25に対する寄生容量の影響が低減されることから、インダクタ部25のインダクタンスのQ値の劣化が抑制される。なお、高周波モジュール装置1においては、肉厚部36の上方に形成される受動素子をインダクタ部25にすることに必ずしも限定されず、例えば、キャパシタ素子、レジスタ素子、分布定数素子等を形成してもこれらの受動素子に対する寄生容量の影響を低減することが可能である。

【0070】

高周波モジュール装置1においては、メッキ法により厚膜形成された金属膜からなる流動抑制部33が形成されている。このため、流動抑制部33は、ベース基板部2及び高周波素子層部4の金属配線層と電気的に接続させた場合、配線として機能させてもよい。これにより、高周波モジュール装置1においては、流動抑制部33を配線として例えば受動素子等の電源供給配線をして用いることができることから、余剰な配線を削減でき小面積化、小型化が図られる。

【0071】

高周波モジュール装置1において、流動抑制部33が、図22に示すように、インダクタ部25を形成する領域の周囲を囲む略矩形をなす枠状に形成されている。これにより、流動抑制部33は、第2の誘電絶縁層31を形成する際に、インダクタ部25が形成される領域に肉厚部36が適切に形成されるように誘電絶縁材料の流れを抑制する。また、流動抑制部33は、インダクタ部25を形成する領域の周囲を囲む形状が略矩形をなす枠状であることに必ずしも限定されるものでなく、例えば図23乃至図25に示すようなインダクタ部25が形成される領域で誘電絶縁材料の流れを抑制する枠の周壁が不連続に形成される流動抑制部33a乃至流動抑制部33cであってもよい。これにより、高周波モジュール装置1においては、流動抑制部33a乃至流動抑制部33cを配線としても用いた際に、所望の配線パターンの一部を構成することができることから、小面積化、小型化が図られる。なお、流動抑制部33は、インダクタ部25が形成される領域に肉厚部36が適切に形成されるように誘電絶縁材料の流れを抑制する例えば図26に示すような略円環をなす枠状を呈する流動抑制部33dであっても良い。この流動抑制部33dは、略円環をなす枠の周壁が不連続に形成された形状であっても良いことは勿論である。

【0072】

高周波モジュール装置1においては、配線層38とインダクタ部25との距離を大となることなく、第2の誘電絶縁層31における肉厚部36だけでインダクタ部25とグランド部を構成する第3のパターン配線層17との距離が大となるようにしている。これにより、高周波モジュール装置1においては、配線層38とインダクタ部25とを電気的に接続させるビアホール44の径を大きくすることなく小面積化、小型化が図られる。

【0073】

高周波モジュール装置1においては、従来のように、インダクタ部25とグランド部を構成する第3のパターン配線層17との距離を離すためのグランド部における配線禁止領域Aを施すことがないことから、第3のパターン配線層17をマイクロストリップ線路のシールド、RF電流が他の配線への干渉や不要な結合をすることを防ぐシールドとして十分に機能させることができる。また、高周波モジュール装置1においては、第3のパターン配線層17に配線禁止領域Aがなく配線の引き回しに制約がないことから小面積化、小型化が図られる。

【0074】

高周波モジュール装置1においては、有機基材等からなるベース基板部2上に形成された高周波素子層部4がインダクタ部25と第3のパターン配線層17との距離を大とすることから、インダクタ部25に対するインダクタンスのQ値の劣化を抑制するとともに、小面積化、小型化を図ることができる。これにより、高周波モジュール装置1においては、高周波素子層部4が形成されるベース基板部2として上述した有機基材等を用いることに必ずしも限定されることはなく、ベース基板部2に例えば、Si基板、ガラス基板等を用いてもインダクタ部25に対するインダクタンスのQ値の劣化を抑制するとともに、小面積化、小型化を図ることができる。

【0075】

【発明の効果】

以上で説明したように、本発明によれば、ベース基板の誘電絶縁層の形成面上に流動抑制部が設けられたことにより、回転操作された状態のベース基板に滴下された誘電絶縁材料の周面へと広がる流れが流動抑制部により抑制されて、誘電絶縁層に厚みが部分的に大となる肉厚部が形成された高周波モジュール装置が得られるようになる。したがって、本発明によれば、誘電絶縁層の肉厚部上に形成された受動素子とベース基板上に形成された配線層との距離が保持され、受動素子に対する配線層からの寄生容量の影響が低減されることから、特性の良い受動素子を有する高周波モジュール装置が得られるようになる。本発明によれば、受動素子を形成する領域だけが誘電絶縁層の肉厚部であることから、ベース基板及び高周波素子部の電気的な接続を担うビアの径を大きくすることなく小面積化、小型化が図られた高周波モジュール装置が得られるようになる。本発明によれば、グランド部に配線禁止領域を施すことなく配線の引き回しに制約がないことから小面積化、小型化が図られた高周波モジュール装置が得られるようになる。本発明によれば、高周波素子部を形成する際に、メッキ法といった簡易な厚膜形成工程を追加するだけで、簡便に高機能化及び小面積化、小型化が図られた高周波モジュール装置が得られるようになる。

【図面の簡単な説明】

【図1】本発明にかかる高周波モジュール装置の縦断面図である。

【図2】同高周波モジュール装置のベース基板部製作工程図である。

【図3】同高周波モジュール装置に用いられるコア基板の縦断面図である。

【図4】コア基板のパターンニング工程説明図である。

【図5】第1の樹脂付銅箔及び第2の樹脂付銅箔の接合工程説明図である。

【図6】ビア形成の工程説明図である。

【図7】第1のパターン配線層及び第2のパターン配線層の形成工程説明図である。

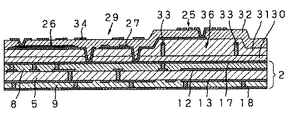

【図8】第3の樹脂付銅箔及び第4の樹脂付銅箔の接合工程説明図である。

【図9】第3の樹脂付銅箔及び第4の樹脂付銅箔を接合した状態の工程説明図である。

【図10】第3の樹脂付銅箔及び第4の樹脂付銅箔の研磨工程説明図である。

【図11】同高周波モジュール装置の高周波素子層部製作工程図である。

【図12】第1の誘電絶縁層の形成工程説明図である。

【図13】流動抑制部の形成工程説明図である。

【図14】第2の誘電絶縁層の形成工程説明図である。

【図15】配線層の形成工程説明図である。

【図16】受動素子の形成工程説明図である。

【図17】第3の誘電絶縁層の形成工程説明図である。

【図18】配線層部の形成工程説明図である。

【図19】レジスト層の形成工程説明図である。

【図20】高周波モジュール装置の縦断面図である。

【図21】放熱構造を備えた高周波モジュール装置の縦断面図である。

【図22】高周波モジュール装置のインダクタ部の下層における流動抑制部の配置の一例を示した透視平面図である。

【図23】高周波モジュール装置のインダクタ部の下層における流動抑制部の配置の一例を示した透視平面図である。

【図24】高周波モジュール装置のインダクタ部の下層における流動抑制部の配置の一例を示した透視平面図である。

【図25】高周波モジュール装置のインダクタ部の下層における流動抑制部の配置の一例を示した透視平面図である。

【図26】高周波モジュール装置のインダクタ部の下層における流動抑制部の配置の一例を示した透視平面図である。

【図27】スーパーへテロダイン方式による高周波送受信回路の構成図である。

【図28】ダイレクトコンバージョン方式による高周波送受信回路の構成図である。

【図29】従来の高周波モジュールに備えられるインダクタ部の説明図であり、同図(a)は要部斜視図、同図(b)は要部縦断面図である。

【図30】従来のシリコン基板を用いた高周波モジュールの縦断面図である。

【図31】従来のガラス基板を用いた高周波モジュールの縦断面図である。

【図32】従来の高周波モジュールの要部を示した縦断面図である。

【図33】従来の高周波モジュールのグランド部に配線禁止領域が施された状態を示す要部縦断面図である。

【符号の説明】

1 高周波モジュール装置、2 ベース基板部、3 高周波素子層形成面、4 高周波素子層部、5 コア基板、6 第1のパターン配線層、7 第2のパターン配線層、8 第1の樹脂付銅箔、9 第2の樹脂付銅箔、10 第3の樹脂付銅箔、11 第4の樹脂付銅箔、12 第1のパターン配線層、13 第2のパターン配線層、14 ビアホール、15,16 ビア、17 第3のパターン配線層、17a ランド、18 第4のパターン配線層、19 ベース基板中間体、20a,20b 銅箔層、21 導電ペースト、22a,22b 開口部、23a,23b 導電材、24 入出力端子部、25 インダクタ部、26 キャパシタ部、27 レジスタ部、28 素子形成層部、29 配線層部、30 第1の誘電絶縁層、31 第2の誘電絶縁層、32 第3の誘電絶縁層、33,33a,33b,33c,33d 流動抑制部、34 パターン配線、35a,35b レジスト層、36 肉厚部、37 ビア、38 配線層、39,40 窒化タンタル層、41 タンタルオキサイト層、42 上部電極、43 高周波モジュール装置中間体、44 ビアホール、45a,45b 開口部、46a,46b 電極端子、70 導電性樹脂材、90 高周波IC、91 チップ部品、92 シールドカバー、93 マザー基板[0001]

BACKGROUND OF THE INVENTION

The present invention is suitably mounted on various electronic devices such as a personal computer, a mobile phone, and an audio device, and has a data communication function, a storage function, etc., and constitutes a microminiature communication function module, and a method for manufacturing the same About.

[0002]

[Prior art]

For example, various types of information such as music, voice, and images can be easily handled by personal computers, mobile computers, and the like in recent years as data is digitized. In addition, these information are band-compressed by audio codec technology and image codec technology, and an environment is being prepared in which digital communication and digital broadcasting are easily and efficiently distributed to various communication terminal devices. . For example, audio / video data (AV data) can be received outdoors by a mobile phone.

[0003]

By the way, a data transmission / reception system has been used in various ways by proposing a suitable network system even in a small area such as a home. As the network system, for example, a narrow band wireless communication system of 5 GHz band proposed in IEEE802.11a, a wireless LAN system of 2.45 GHz band as proposed in IEEE802.11b, or a near-field called Bluetooth. Various next-generation wireless systems such as distance wireless communication systems are attracting attention.

[0004]

A data transmission / reception system effectively uses such a wireless network system to easily send and receive various data in various places such as homes and outdoors, without using a relay device, and to access the Internet network. Data can be sent and received.

[0005]

On the other hand, in a data transmission / reception system, it is essential to realize a communication terminal device that is small and light and portable and has the communication function described above. In a communication terminal device, since it is necessary to perform modulation / demodulation processing of an analog high-frequency signal in a transmission / reception unit, in general, a superheterodyne method in which a transmission / reception signal as shown in FIG. 27 is once converted to an intermediate frequency is used. A high frequency transmission /

[0006]

The high-frequency transmission /

[0007]

In the high-frequency transmission /

[0008]

On the other hand, as shown in FIG. 28, a high-frequency transmission /

[0009]

In the high-frequency transmission /

[0010]

[Problems to be solved by the invention]

As described above, conventional high-frequency transmission / reception circuits cannot satisfy sufficient characteristics with respect to required specifications such as miniaturization and weight reduction of communication terminal equipment in both the superheterodyne method and the direct conversion method. . For this reason, various attempts have been made to make the high-frequency transmission / reception circuit into a module that is reduced in size with a simple configuration based on, for example, a Si-CMOS circuit. That is, one of the trials is to form a passive element with good characteristics on the Si substrate, build a filter circuit, a resonator, etc. on the LSI, and also integrate a logic LSI in the baseband part, so-called This is a method of manufacturing a one-chip high-frequency module.

[0011]

However, in this one-chip high-frequency module, as shown in FIG. 29, how to form a high-

[0012]

Further, in this one-chip high-frequency module, electrical interference between the Si substrate interposed between the high-frequency circuit section of the analog circuit and the baseband circuit section of the digital circuit has become a serious problem.

[0013]

For example, a

[0014]

This

[0015]

Although details are omitted in the passive

[0016]

In the

[0017]

By the way, in such a

[0018]

On the other hand, the

[0019]

In the

[0020]

By the way, in the

[0021]

In these one-chip high-frequency modules, a highly accurate passive element forming layer is formed on a base substrate as described above. When forming a passive element formation layer as a thin film on the base substrate, it is necessary to have heat resistance characteristics against an increase in surface temperature during sputtering, maintenance of the depth of focus during lithography, and contact alignment characteristics during masking. For this reason, the base substrate is required to have high precision flatness, and is required to have insulation, heat resistance, chemical resistance, and the like.

[0022]

The above-described

[0023]

By the way, in such a one-chip high-frequency module, wirings, grounds, etc. are formed in multiple layers on the

[0024]

In the high-

[0025]

However, in the first method, the first thin film layer is formed when the via 206 for wiring the

[0026]

On the other hand, in the second method, the

[0027]

Accordingly, the present invention provides a high-frequency module device that reduces the influence of parasitic capacitance on the passive elements of the wiring layer formed on the base substrate, and that achieves higher functionality, smaller area, and smaller size, and a method for manufacturing the same. It was proposed for the purpose of doing.

[0028]

[Means for Solving the Problems]

A high-frequency module device according to the present invention that achieves the above-described object includes a base substrate having a wiring layer on a main surface, and a dielectric insulating layer formed by applying a dielectric insulating material on the base substrate by a spin coating method. And a high-frequency element portion having a passive element formed as a thin film on the dielectric insulating layer, and the dielectric insulating layer is formed by a flow suppressing portion that suppresses the flow of the dielectric insulating material provided on the formation surface of the dielectric insulating layer. A thick portion having a partially increased thickness is formed, and a passive element is formed on the thick portion of the dielectric insulating layer.

[0029]

According to the high-frequency module device of the present invention configured as described above, the flow suppression unit is provided on the surface of the base substrate on which the dielectric insulating layer is formed, so that it is dropped on the base substrate in the rotated state. The flow that spreads to the peripheral surface of the dielectric insulating material is suppressed by the flow suppressing portion, and a thick portion having a partially increased thickness is formed in the dielectric insulating layer. Therefore, according to the high frequency module device, the distance between the passive element formed on the thick portion of the dielectric insulating layer and the wiring layer formed on the base substrate is maintained, and the parasitic capacitance from the wiring layer to the passive element is maintained. Impact is reduced.

[0030]

In addition, a method of manufacturing a high-frequency module device according to the present invention that achieves the above-described object includes a base substrate forming step of forming a base substrate having a wiring layer on a main surface, and a dielectric insulating material by spin coating on the base substrate. A high-frequency module device is manufactured through a high-frequency element part forming step of forming a high-frequency element part having a dielectric insulating layer formed by coating and a passive element formed as a thin film on the dielectric insulating layer. The high-frequency element unit forming step includes a flow suppressing unit forming step for forming a flow suppressing unit that suppresses the flow of the dielectric insulating material applied by spin coating on the base substrate, and the base substrate on which the flow suppressing unit is formed. A dielectric insulating layer forming step of forming a dielectric insulating layer having a thick portion that is partially thickened by suppressing a flow of the dielectric insulating material applied by a spin coating method by the flow suppressing portion; A passive element forming step of forming a passive element on the thick part of the insulating layer.

[0031]

According to the method of manufacturing a high-frequency module device according to the present invention configured as described above, the flow suppressing portion formed on the base substrate by the flow suppressing portion forming step is applied by the spin coat method in the dielectric insulating layer forming step. The partial thickness of the dielectric insulating layer is formed by suppressing the flow of the dielectric insulating material. Thus, in the method of manufacturing the high frequency module device, the distance between the passive element formed on the thick portion of the dielectric insulating layer and the wiring layer formed on the base substrate by the passive element forming step is maintained, and A high-frequency module device with reduced parasitic capacitance from the wiring layer is manufactured.

[0032]

DETAILED DESCRIPTION OF THE INVENTION

Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. The high-

[0033]

The

[0034]

The configuration and manufacturing process of the

[0035]

As shown in FIG. 2, the manufacturing process of the

[0036]

The manufacturing process of the

[0037]

The

[0038]

As shown in FIG. 3, copper foil layers 20 a and 20 b are formed on the entire surface of the first

[0039]

The

[0040]

The first resin-coated

[0041]

The first resin-attached

[0042]

As shown in FIG. 7, the first resin-coated

[0043]

In the base substrate manufacturing process, a high-frequency element

[0044]

As shown in FIG. 9, the third resin-attached

[0045]

The base substrate intermediate 19 is subjected to a polishing process by the polishing step s-6 on the third resin-attached

[0046]

In the base substrate part manufacturing process, the

[0047]

In the

[0048]

In the

[0049]

In the

[0050]

In the base substrate portion manufacturing process, the copper foil portion 11 a is polished by the fourth resin-attached

[0051]

In the base substrate part manufacturing process described above, the first resin-attached

[0052]

The configuration and manufacturing process of the high-frequency

[0053]

The high-frequency

[0054]

In the first dielectric insulating layer forming step s-7, the

[0055]

On the first dielectric insulating

[0056]

On the

[0057]

In the second dielectric insulating layer forming step s-9, as shown in FIG. 14, when the dielectric insulating material dropped on the

[0058]

In the ground processing step s-10, as shown in FIG. dielectric On the surface of the insulating

[0059]

The

[0060]

In the

[0061]

The

[0062]

In the high-frequency element layer manufacturing step, the third dielectric insulation is performed on the high-frequency module device intermediate 43 manufactured through the above steps by the third dielectric insulating layer forming step s-12 as shown in FIG.

[0063]

In the high frequency element layer manufacturing process, the

[0064]

In part of the

[0065]

In the high frequency element layer manufacturing process, the main surface of the fourth

[0066]

In the high-frequency element layer manufacturing process, as shown in FIG. 19, the entire surface of the high-

[0067]

In the high

[0068]

In the high

[0069]

In the high-

[0070]

In the high

[0071]

In the high

[0072]

In the high-

[0073]

In the high-

[0074]

In the high

[0075]

【The invention's effect】

As described above, according to the present invention, since the flow suppressing portion is provided on the surface of the base substrate on which the dielectric insulating layer is formed, the dielectric insulating material dropped on the base substrate in the rotated state is provided. The flow spreading to the peripheral surface is suppressed by the flow suppressing portion, and a high-frequency module device in which a thick portion whose thickness is partially increased is formed in the dielectric insulating layer can be obtained. Therefore, according to the present invention, the distance between the passive element formed on the thick portion of the dielectric insulating layer and the wiring layer formed on the base substrate is maintained, and the influence of the parasitic capacitance from the wiring layer on the passive element is maintained. Therefore, a high-frequency module device having passive elements with good characteristics can be obtained. According to the present invention, since only the region where the passive element is formed is the thick part of the dielectric insulating layer, the area can be reduced without increasing the diameter of the via that is responsible for the electrical connection between the base substrate and the high-frequency element part. Thus, a high-frequency module device with a reduced size can be obtained. According to the present invention, since there is no restriction on the routing of wiring without providing a wiring prohibition region in the ground portion, a high-frequency module device with reduced area and size can be obtained. According to the present invention, when forming a high frequency element portion, a high frequency module device that is simply improved in function, area, and size can be achieved by simply adding a simple thick film forming process such as a plating method. It will be obtained.

[Brief description of the drawings]

FIG. 1 is a longitudinal sectional view of a high-frequency module device according to the present invention.

FIG. 2 is a manufacturing process diagram of a base substrate portion of the high-frequency module device.

FIG. 3 is a longitudinal sectional view of a core substrate used in the high frequency module device.

FIG. 4 is an explanatory diagram of a patterning process of a core substrate.

FIG. 5 is an explanatory diagram of a joining process of a first resin-attached copper foil and a second resin-attached copper foil.

FIG. 6 is an explanatory diagram of a process of forming a via.

FIG. 7 is an explanatory diagram of a process of forming a first pattern wiring layer and a second pattern wiring layer.

FIG. 8 is an explanatory diagram of a joining process of a third resin-attached copper foil and a fourth resin-attached copper foil.

FIG. 9 is a process explanatory diagram of a state in which a third resin-attached copper foil and a fourth resin-attached copper foil are joined together.

FIG. 10 is an explanatory diagram of a polishing process for a third resin-attached copper foil and a fourth resin-attached copper foil.

FIG. 11 is a manufacturing process diagram of a high-frequency element layer portion of the high-frequency module device.

FIG. 12 is a diagram illustrating a process for forming a first dielectric insulating layer.

13 is a forming process explanatory view of the flow suppressing portion.

14 is a forming process explanatory view of a second dielectric insulating layer.

15 is a forming process explanatory view of a wiring layer.

16 is a forming process explanatory view of a passive element.

17 is a forming process explanatory view of a third dielectric insulating layer.

18 is a forming process explanatory view of a wiring layer portion.

19 is a forming process explanatory view of the resist layer.

Figure 20 is a longitudinal sectional view of a high frequency module device.

21 is a longitudinal sectional view of a high frequency module device having a heat dissipation structure.

FIG. 22 is a perspective plan view showing an example of the arrangement of the flow suppressing portion in the lower layer of the inductor portion of the high-frequency module device.

FIG. 23 is a perspective plan view showing an example of the arrangement of the flow suppression unit in the lower layer of the inductor unit of the high-frequency module device.

FIG. 24 is a perspective plan view showing an example of the arrangement of the flow suppression unit in the lower layer of the inductor unit of the high-frequency module device.

FIG. 25 is a perspective plan view showing an example of the arrangement of the flow suppression unit in the lower layer of the inductor unit of the high-frequency module device.

FIG. 26 is a perspective plan view showing an example of the arrangement of the flow suppression unit in the lower layer of the inductor unit of the high-frequency module device.

FIG. 27 is a configuration diagram of a high frequency transmission / reception circuit using a superheterodyne method.

28 is a configuration diagram of a high-frequency transmission and reception circuit by the direct conversion system.

29A and 29B are explanatory diagrams of an inductor portion provided in a conventional high-frequency module, where FIG. 29A is a perspective view of a main part, and FIG. 29B is a vertical sectional view of the main part.

Figure 30 is a longitudinal sectional view of a high-frequency module using the conventional silicon substrate.

Figure 31 is a longitudinal sectional view of a high-frequency module using the conventional glass substrate.

32 is a longitudinal sectional view showing a main part of a conventional high-frequency module.

FIG. 33 is a vertical cross-sectional view of a main part showing a state where a wiring prohibition region is provided in a ground portion of a conventional high-frequency module.

[Explanation of symbols]

DESCRIPTION OF SYMBOLS 1 High frequency module apparatus, 2 Base board | substrate part, 3 High frequency element layer formation surface, 4 High frequency element layer part, 5 Core board | substrate, 6 1st pattern wiring layer, 7 2nd pattern wiring layer, 8 1st copper with resin Foil, 9 2nd resin-attached copper foil, 10 3rd resin-attached copper foil, 11 4th resin-attached copper foil, 12 1st pattern wiring layer, 13 2nd pattern wiring layer, 14 Via hole, 15, 16 via, 17 third pattern wiring layer, 17a land, 18 fourth pattern wiring layer, 19 base substrate intermediate, 20a, 20b copper foil layer, 21 conductive paste, 22a, 22b opening, 23a, 23b conductive material , 24 I / O terminal section, 25 inductor section, 26 capacitor section, 27 register section, 28 element formation layer section, 29 wiring layer section, 30 first dielectric insulating layer, 31 second dielectric insulating layer, 32 third Dielectric insulation 33, 33a, 33b, 33c, 33d Flow suppressing portion, 34 pattern wiring, 35a, 35b resist layer, 36 thick portion, 37 via, 38 wiring layer, 39, 40 tantalum nitride layer, 41 tantalum oxide layer, 42 upper electrode, 43 a high frequency module device intermediate, 44 via hole 45a, 45b Opening, 46a, 46b Electrode terminal, 70 Conductive resin material, 90 High frequency IC, 91 Chip component, 92 Shield cover, 93 Mother board

Claims (10)

上記ベース基板上に、誘電絶縁材料をスピンコート法で塗布することにより形成された誘電絶縁層と、当該誘電絶縁層上に薄膜形成された受動素子とを有する高周波素子部とを備え、

上記誘電絶縁層の形成面上に上記誘電絶縁材料の流れを抑制する流動抑制部が配置されることにより、上記誘電絶縁層に厚みが部分的に大となる肉厚部が形成されており、

上記受動素子が、上記誘電絶縁層の肉厚部上に形成されている高周波モジュール装置。A base substrate having a wiring layer on the main surface;

A high-frequency element unit including a dielectric insulating layer formed by applying a dielectric insulating material by spin coating on the base substrate, and a passive element formed as a thin film on the dielectric insulating layer,

By disposing a flow suppressing portion that suppresses the flow of the dielectric insulating material on the formation surface of the dielectric insulating layer, a thick portion having a partially increased thickness is formed in the dielectric insulating layer,

The passive elements, the dielectric insulating layer thickness portion high frequency module device that is formed on.

上記ベース基板上にスピンコート法により誘電絶縁材料を塗布することにより形成された誘電絶縁層と、当該誘電絶縁層上に薄膜形成された受動素子とを有する高周波素子部を形成する高周波素子部形成工程とを有し、

上記高周波素子部形成工程が、

上記ベース基板上に上記スピンコート法により塗布される上記誘電絶縁材料の流れを抑制する流動抑制部を形成する流動抑制部形成工程と、

上記流動抑制部が形成される上記ベース基板上に、上記スピンコート法により塗布された上記誘電絶縁材料の流れが上記流動抑制部により抑制されることで部分的に厚みが大となる肉厚部を有する上記誘電絶縁層を形成する誘電絶縁層形成工程と、

上記誘電絶縁層の肉厚部上に上記受動素子を形成する受動素子形成工程と

を有する高周波モジュール装置の製造方法。A base substrate forming step of forming a base substrate having a wiring layer on the main surface;

Formation of a high-frequency element part for forming a high-frequency element part having a dielectric insulating layer formed by applying a dielectric insulating material on the base substrate by spin coating and a passive element formed as a thin film on the dielectric insulating layer A process,

The high-frequency element part forming step is

A flow suppressing part forming step of forming a flow suppressing part for suppressing the flow of the dielectric insulating material applied by the spin coating method on the base substrate;

A thick part whose thickness is partially increased by suppressing the flow of the dielectric insulating material applied by the spin coating method on the base substrate on which the flow suppressing part is formed, by the flow suppressing part. A dielectric insulating layer forming step of forming the dielectric insulating layer having:

Process for producing a high frequency module device that having a passive element forming step of forming the passive elements on the thick portion of the dielectric insulating layer.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001081727A JP4608794B2 (en) | 2001-03-21 | 2001-03-21 | High frequency module device and manufacturing method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001081727A JP4608794B2 (en) | 2001-03-21 | 2001-03-21 | High frequency module device and manufacturing method thereof |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002280745A JP2002280745A (en) | 2002-09-27 |

| JP4608794B2 true JP4608794B2 (en) | 2011-01-12 |

Family

ID=18937778

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001081727A Expired - Fee Related JP4608794B2 (en) | 2001-03-21 | 2001-03-21 | High frequency module device and manufacturing method thereof |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4608794B2 (en) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4835131B2 (en) * | 2005-12-02 | 2011-12-14 | ソニー株式会社 | Passive device package and manufacturing method thereof, semiconductor module, and mounting structure thereof |

| US8941457B2 (en) | 2006-09-12 | 2015-01-27 | Cooper Technologies Company | Miniature power inductor and methods of manufacture |

| US8378777B2 (en) | 2008-07-29 | 2013-02-19 | Cooper Technologies Company | Magnetic electrical device |

| US7791445B2 (en) | 2006-09-12 | 2010-09-07 | Cooper Technologies Company | Low profile layered coil and cores for magnetic components |

| US8466764B2 (en) | 2006-09-12 | 2013-06-18 | Cooper Technologies Company | Low profile layered coil and cores for magnetic components |

| US8659379B2 (en) | 2008-07-11 | 2014-02-25 | Cooper Technologies Company | Magnetic components and methods of manufacturing the same |

| US9859043B2 (en) | 2008-07-11 | 2018-01-02 | Cooper Technologies Company | Magnetic components and methods of manufacturing the same |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5775715U (en) * | 1980-10-29 | 1982-05-11 | ||

| JPS57108316U (en) * | 1980-12-24 | 1982-07-03 | ||

| JPH05235554A (en) * | 1992-02-25 | 1993-09-10 | Hitachi Ltd | Multilayer wiring board with printed inductor |

| JPH06120659A (en) * | 1992-10-06 | 1994-04-28 | Toray Ind Inc | Multilayer wiring structure |

| JPH0832244A (en) * | 1994-07-12 | 1996-02-02 | Toshiba Corp | Multilayer wiring board |

| JP2001028474A (en) * | 1999-05-12 | 2001-01-30 | Tdk Corp | Electronic part and manufacture thereof |

-

2001

- 2001-03-21 JP JP2001081727A patent/JP4608794B2/en not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5775715U (en) * | 1980-10-29 | 1982-05-11 | ||

| JPS57108316U (en) * | 1980-12-24 | 1982-07-03 | ||

| JPH05235554A (en) * | 1992-02-25 | 1993-09-10 | Hitachi Ltd | Multilayer wiring board with printed inductor |

| JPH06120659A (en) * | 1992-10-06 | 1994-04-28 | Toray Ind Inc | Multilayer wiring structure |

| JPH0832244A (en) * | 1994-07-12 | 1996-02-02 | Toshiba Corp | Multilayer wiring board |

| JP2001028474A (en) * | 1999-05-12 | 2001-01-30 | Tdk Corp | Electronic part and manufacture thereof |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002280745A (en) | 2002-09-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4529262B2 (en) | High frequency module device and manufacturing method thereof | |

| JP3925378B2 (en) | A method for manufacturing a high-frequency module device. | |

| JP4318417B2 (en) | High frequency module board device | |

| US7599190B2 (en) | High-frequency module, and method of producing same | |

| US7057279B2 (en) | High-frequency circuit block, its manufacturing method, high-frequency module device, and its manufacturing method | |

| JP3666411B2 (en) | High frequency module device | |

| JP3941416B2 (en) | High frequency module device and manufacturing method thereof | |

| KR20040034575A (en) | Thin film circuit board device and its manufacturing method | |

| JP4604398B2 (en) | High frequency module substrate device, high frequency module device and manufacturing method thereof | |

| JP4608794B2 (en) | High frequency module device and manufacturing method thereof | |

| JP2003051567A (en) | High-frequency module substrate unit therefor and manufacturing method therefor | |

| JP4595240B2 (en) | High frequency module substrate device and manufacturing method thereof | |

| JP2002374069A (en) | High-frequency module device and manufacturing method therefor |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080111 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100722 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100727 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100824 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100914 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100927 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131022 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131022 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |