JP4599655B2 - Electro-optical device and projector - Google Patents

Electro-optical device and projector Download PDFInfo

- Publication number

- JP4599655B2 JP4599655B2 JP2000122601A JP2000122601A JP4599655B2 JP 4599655 B2 JP4599655 B2 JP 4599655B2 JP 2000122601 A JP2000122601 A JP 2000122601A JP 2000122601 A JP2000122601 A JP 2000122601A JP 4599655 B2 JP4599655 B2 JP 4599655B2

- Authority

- JP

- Japan

- Prior art keywords

- shielding film

- light

- electro

- optical device

- region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、アクティブマトリクス駆動方式の電気光学装置の技術分野に属し、特に画素電極に対し蓄積容量を付加するための一対の容量電極と、画素スイッチング用の薄膜トランジスタ(Thin Film Transistor:以下適宜、TFTと称す)とを、基板上の積層構造中に備えた形式の電気光学装置の技術分野に属する。

【0002】

【背景技術】

従来、TFT駆動によるアクティブマトリクス駆動方式の電気光学装置においては、TFTのゲート電極に走査線を介して走査信号が供給されると、TFTはオン状態とされ、半導体層のソース領域にデータ線を介して供給される画像信号が当該TFTのソース−ドレイン間を介して画素電極に供給される。このような画像信号の供給は、各TFTを介して画素電極毎に極めて短時間しか行われないので、TFTを介して供給される画像信号の電圧を、このオン状態とされた時間よりも遥かに長時間に亘って保持するために、各画素電極には(液晶容量等と並列に)蓄積容量が付加されるのが一般的である。

【0003】

係る蓄積容量は一般に、画素電極に接続されたTFTのドレイン領域を構成する導電性のポリシリコン膜等から延設され画素電極電位とされる第1容量電極と、この第1容量電極に誘電体膜を介して対向配置された第2容量電極を含み固定電位とされる容量線とを備えて構成されている。そして、このような容量線は、走査線と同一導電膜(例えば、導電性のポリシリコン膜)から構成され、走査線に平行して横並びに配線されるのが一般的である。

【0004】

他方、この種の電気光学装置では、相隣接する画素電極の間隙を表示光が素通りしてしまうと(所謂光抜けにより)コントラスト比が低下し、画質が低下する。このため、一般に透明なポリシリコン膜等からなる走査線及び容量線に沿った画素電極の間隙を覆うように対向基板にストライプ状の遮光膜を設けたり、データ線に沿った画素電極の間隙を覆うように、当該データ線をAl(アルミニウム)膜等の反射膜から幅広に形成したりする。このように、対向基板上の遮光膜やデータ線を組み合わせることにより各画素の開口領域(即ち、各画素において表示に有効に寄与する光が通過する領域)を規定している。

【0005】

【発明が解決しようとする課題】

この種の電気光学装置においては、表示画像の高品位化という一般的な要請が強く、このためには、画素ピッチを微細化しつつ、画素開口率化を高める(即ち、各画素において、表示光が透過しない各画素における非開口領域に対して、表示光が透過する開口領域を広げる)ことが重要となる。

【0006】

しかしながら、画像表示領域内において走査線と容量線とが横並びに配線された前述の背景技術によれば、このように微細ピッチな画素の高開口率化に伴い走査線や容量線を配線可能な各画素の非開口領域は狭くなる。このため、画素ピッチの微細化が進む程、十分な大きさの蓄積容量を作り込むことや、走査線や容量線に十分な導電性を与えることが困難になるという問題点がある。そして、十分な蓄積容量が得られなかったり、走査線や容量線に十分な導電性が得られなかったりすると、最終的には、表示画像中におけるクロストークやゴーストが増大して画質劣化するという問題点が生じる。即ち、微細ピッチな画素の高開口率化に伴ってこのような画質劣化が顕在化してくるという画質向上のために解決困難な問題点がある。

【0007】

他方、前述のように対向基板上の遮光膜やデータ線を組み合わせることにより各画素の開口領域を規定する技術によれば、斜めの入射光に対する遮光や特にプロジェクタ用途の如く強力な入射光に対する遮光を十分に行うことは困難である。即ち、この技術によれば、斜めの入射光に対する遮光や、裏面反射光や当該電気光学装置をライトバルブとして複板式のプロジェクタに組み合わせて使用する場合に合成光学系を突き抜けてくる光などの戻り光に対する遮光は十分でなく、更にこのような斜めの入射光や戻り光により内面反射光や多重反射光が発生するのを阻止することも困難である。従って、このような斜めの入射光、戻り光、内面反射光や多重反射光により、コントラスト比が低下するという問題点がある。加えて、このような斜めの入射光、戻り光、内面反射光や多重反射光が、画素スイッチング用のTFTのチャネル領域に侵入すると、光電効果によりTFTのトランジスタ特性の劣化(光リーク)が生じて、最終的に画質劣化を引き起こすという問題点もある。

【0008】

本発明は上述の問題点に鑑みなされたものであり、画素開口率を高めると同時に蓄積容量の増大を図る(或いは蓄積容量の減少を抑制する)ことができると共に表示に寄与しない斜めの入射光や戻り光に対する遮光性能を向上でき、クロストークやゴーストが低減されると共にコントラスト比が向上されており、高品位の画像表示が可能な電気光学装置を提供することを課題とする。

【0009】

【課題を解決するための手段】

本発明の電気光学装置は上記課題を解決するために、基板上に、相交差する走査線及びデータ線と、前記走査線及びデータ線の交差に対応して設けられた薄膜トランジスタと、絶縁膜を介して前記薄膜トランジスタの半導体層と異なる層に設けられた中間導電層と、前記薄膜トランジスタに前記中間導電層を中継して接続された画素電極と、平面的に見て前記データ線に重なる領域に配置された蓄積容量と、画素の開口領域を少なくとも部分的に規定すると共に前記走査線と重なるように形成された導電性の遮光膜とを備えており、前記蓄積容量は、前記薄膜トランジスタに電気的に接続されると共に平面的に見て前記遮光膜と重なる部分と前記遮光膜から前記開口領域に向かって突出する突出部とを有する第1容量電極と、前記第1容量電極に誘電体膜を介して対向配置されると共に前記遮光膜に接続されて固定電位とされる第2容量電極とを備え、前記中間導電層は、前記突出部において前記第1容量電極と電気的に接続されることを特徴とする。

また、本発明の電気光学装置は上記課題を解決するために、基板上に、相交差する走査線及びデータ線と、該走査線及びデータ線の交差に対応して設けられた薄膜トランジスタと、該薄膜トランジスタに中間導電層を中継して接続された画素電極と、平面的に見て前記データ線に重なる領域に配置された蓄積容量と、各画素の開口領域を少なくとも部分的に規定する導電性の遮光膜とを備える。そして、前記蓄積容量は、前記走査線と同一膜からなると共に前記画素電極に電気的に接続されて画素電極電位とされる第1容量電極と、該第1容量電極に誘電体膜を介して対向配置され且つ前記中間導電層と同一膜からなると共に前記遮光膜に接続されて固定電位とされる第2容量電極とを備える。

【0010】

本発明の電気光学装置によれば、平面的に見てデータ線に重なる領域を利用して蓄積容量を構築することができる。この際、前述した背景技術の如く容量線或いは容量電極を走査線に横並びに配線する必要が無いので、当該横並びの走査線及び容量線或いは容量電極の存在により、各画素の非開口領域を広げないで済む。即ち、基板上で第1容量電極及び第2容量電極をデータ線に立体的に重ねて形成することにより各画素の開口領域を広げつつ相対的に蓄積容量を増大させることが可能となる。

【0011】

しかも、画素電極電位とされる第1容量電極は、走査線と同一膜からなり、固定電位とされる第2容量電極は、薄膜トランジスタを画素電極に中継接続する中間導電層と同一膜からなるので、このような蓄積容量をデータ線に重なる領域に構築するために専用の導電膜を追加形成する必要はなく、装置構成及び製造工程を簡略化する上でも大変有利である。特に、データ線に重なる領域(走査線に重ならない領域)における、走査線と同一膜の有効利用が図られ、走査線形成時におけるパターンニングに変更を加えるだけで第1容量電極を形成できるので実用上便利である。更に、このような中間導電層は、画素電極と薄膜トランジスタとの層間距離が長いため一つのコンタクトホールで両者を接続する技術的困難性を回避し、比較的小径の二つの直列なコンタクトホールで両者を接続することを可能ならしめ、両者を接続するために必要な平面領域を低減でき且つ装置信頼性を高めることができる。そして、このような中間導電層形成時におけるパターンニングに変更を加えるだけで第2容量電極を形成できるので実用上便利である。

【0012】

これらに加えて、第2容量電極は、各画素の開口領域を少なくとも部分的に規定する導電性の遮光膜に接続されて固定電位とされる、即ち、当該遮光膜を固定電位に落とすための容量線としても用いるので、走査線と横並びに、固定電位とされる容量線を配線する必要がなくなり、画素開口率を向上することができる。更に、特にプロジェクタ用途のように強力な入射光を扱う場合でも、第2容量電極を固定電位にする遮光膜により、前述の如き斜めの入射光、戻り光、内面反射光、多重反射光等の表示に悪影響を及ぼす光に対する遮光性能を向上できる。

【0013】

以上の結果、本発明の電気光学装置により、画素開口率を高めると同時に蓄積容量を増大できると共に遮光性能を向上でき、最終的には、クロストークやゴーストが低減され且つコントラスト比が向上された高品位の画像表示が可能となる。

【0014】

本発明の電気光学装置の一態様では、前記第1容量電極と前記データ線との間に、前記第2容量電極が配置されている。

【0015】

この態様によれば、画素電極電位とされる第1容量電極と画像信号が供給されるデータ線との間で、固定電位とされる第2容量電極が電磁シールドとして機能する。このため、データ線と第1容量電極との間の容量カップリングにより、データ線における電位変動が第1容量電極(更には画素電極)に悪影響を及ぼしたり、或いは第1容量電極における電位変動がデータ線に悪影響を及ぼすことを未然防止できる。逆に、このような容量カップリングによる悪影響を低減するために両者間の層間絶縁膜を厚くしないで済む。

【0016】

本発明の電気光学装置の他の態様では、前記遮光膜は、前記基板上で前記薄膜トランジスタの下層側に配置され且つ前記薄膜トランジスタの少なくともチャネル領域を前記基板側から見て覆う導電性の下層遮光膜からなり、該下層遮光膜と前記第2容量電極とは、平面的に見て前記第1容量電極の形成されていない領域に開孔されたコンタクトホールを介して接続されている。

【0017】

この態様によれば、下層遮光膜が薄膜トランジスタの少なくともチャネル領域を基板側から見て覆うので、薄膜トランジスタの下層側からの戻り光(即ち、裏面反射光や当該電気光学装置をライトバルブとして複板式のプロジェクタに組み合わせて使用する場合に合成光学系を突き抜けてくる光など)に対してチャネル領域を遮光でき、戻り光による薄膜トランジスタの特性劣化を低減できる。そして、第2容量電極は、平面的に見て第1容量電極の形成されていない領域に開孔されたコンタクトホールを介して、このような導電性の下層遮光膜に接続されて、固定電位とされる。従って、下層遮光膜を容量線としても利用して、蓄積容量をデータ線に重なる領域に構築できる。

【0018】

この下層遮光膜を備えた態様では、前記薄膜トランジスタの上層側に前記各画素の開口領域を少なくとも部分的に規定する上層遮光膜を更に備えてもよい。

【0019】

このように構成すれば、薄膜トランジスタの上層側に備えられた上層遮光膜により、薄膜トランジスタの上層側からの斜めの入射光に対する遮光を、例えば対向基板に設けられた遮光膜と比べて薄膜トランジスタの直近で行うことが可能となり、特にプロジェクタ用途のように強力な入射光の場合にも、斜めの入射光による光抜けを効果的に防止でき、更に斜めの入射光や更にこれや戻り光に基づく内面反射光や多重反射光をも有効に遮光可能となる。尚、この場合には、上層遮光膜が導電性である必要はない。

【0020】

この場合には更に、前記上層遮光膜は、前記基板上で前記データ線よりも上層側に積層され且つ平面的に見て格子状に形成されてもよい。

【0021】

このように構成すれば、データ線と薄膜トランジスタとの間に上層遮光膜が存在しないため、平面的に見てデータ線と薄膜トランジスタとを接続するためのコンタクトホールを上層遮光膜に重なる位置に開孔できる。即ち、係るコンタクトホールを開孔する隙間を確保するために、上層遮光膜に括れや開口を設けたり、上層遮光膜をストライプ状に分断形成する必要が無くなり、上層遮光膜をデータ線及び走査線を完全に覆う格子状に形成できる。これにより、各画素の開口領域を上層遮光膜のみにより規定することが可能となり、遮光性能を一層高められる。

【0022】

本発明の電気光学装置の他の態様では、前記遮光膜は、前記基板上で前記薄膜トランジスタの上層側に配置された導電性の上層遮光膜からなる。

【0023】

この態様によれば、薄膜トランジスタの上層側に備えられた上層遮光膜により、薄膜トランジスタの上層側からの斜めの入射光に対する遮光を行うことが可能となり、特にプロジェクタ用途のように強力な入射光の場合にも、斜めの入射光による光抜けを効果的に防止でき、更に斜めの入射光や更にこれや戻り光に基づく内面反射光や多重反射光をも有効に遮光可能となる。そして、第2容量電極は、このような導電性の上層遮光膜に接続されて、固定電位とされる。従って、上層遮光膜を容量線としても利用して、蓄積容量をデータ線に重なる領域に構築できる。

【0024】

この上層遮光膜を備えた態様では、前記上層遮光膜は、前記基板上で前記データ線よりも下層側に積層され且つ平面的に見て前記走査線に沿った本線部と該本線部から前記データ線に沿って突出した突出部とを含むストライプ状に形成されており、前記データ線と前記薄膜トランジスタとは、平面的に見て前記ストライプ状の上層遮光膜が形成されていない領域に開孔されたコンタクトホールを介して接続されてもよい。

【0025】

このように構成すれば、走査線に沿った本線部と該本線部からデータ線に沿って突出した突出部とを含むストライプ状に形成された上層遮光膜により、走査線の全部とデータ線の大部分とにおける画素の開口領域を規定できる。そして、上層遮光膜がデータ線と薄膜トランジスタとの間に積層されているものの、ストライプ状の上層遮光膜が形成されていない領域(即ち、突出部の先にある領域)に、データ線と薄膜トランジスタとを接続するコンタクトホールを何ら問題なく開孔できる。

【0026】

或いは、この上層遮光膜を備えた態様では、前記上層遮光膜は、前記基板上で前記データ線よりも上層側に積層され且つ平面的に見て格子状に形成されており、前記上層遮光膜と前記第2容量電極とは、平面的に見て前記データ線が形成されていない領域に開孔されたコンタクトホールを介して接続されてもよい。

【0027】

このように構成すれば、データ線と薄膜トランジスタとの間に上層遮光膜が存在しないため、データ線と薄膜トランジスタとを接続するためのコンタクトホールを開孔する隙間を確保するために、上層遮光膜に括れや開口を設けたり、上層遮光膜をストライプ状に分断形成する必要が無くなり、上層遮光膜をデータ線及び走査線を完全に覆う格子状に形成できる。これにより、各画素の開口領域を上層遮光膜のみにより規定することが可能となり、遮光性能を一層高められる。そして、データ線が上層遮光膜と第2容量電極との間に積層されているものの、データ線が形成されていない領域に(平面的に見てデータ線の形成領域から第2容量電極を若干突出して形成することにより)上層遮光膜と第2容量電極とを接続するコンタクトホールを何ら問題なく開孔できる。

【0028】

この上層遮光膜を備えた態様では、前記薄膜トランジスタの下層側に前記薄膜トランジスタの少なくともチャネル領域を前記基板側から見て覆う下層遮光膜を更に備えてもよい。

【0029】

このように構成すれば、下層遮光膜が薄膜トランジスタの少なくともチャネル領域を基板側から見て覆うので、薄膜トランジスタの下層側からの戻り光に対してチャネル領域を遮光でき、戻り光による薄膜トランジスタの特性劣化を低減できる。尚、この場合には、下層遮光膜が導電性である必要はない。

【0030】

上述した上層遮光膜及び下層遮光膜の両者を備えた態様では、前記下層遮光膜、前記走査線、前記データ線及び前記薄膜トランジスタは、前記基板上で平面的に見て前記上層遮光膜の形成領域からはみ出さないのが好ましい。

【0031】

このように構成すれば、基板上に入射した入射光が上層遮光膜の形成領域からはみ出した走査線、データ線、薄膜トランジスタ又は下層遮光膜の上面で反射することで、当該電気光学装置の内部における内面反射光や多重反射光が発生することを効果的に未然防止できる。尚、戻り光が下層遮光膜の形成領域からはみ出した上層遮光膜の下面で反射することで、当該電気光学装置の内部における内面反射光や多重反射光は若干発生するが、戻り光は入射光に比べて遥かに光強度が低いために、戻り光による内面反射や多重反射光の悪影響は入射光のそれ比べて軽微である。従って、このように下層遮光膜が上層遮光膜からはみ出さない(即ち、上層遮光膜が下層遮光膜よりも一回り大きい)方が好ましい。

【0032】

本発明の電気光学装置の他の態様では、前記蓄積容量は、平面的に見て前記データ線に重なる領域に加えて、前記走査線に沿った領域にも部分的に配置されている。

【0033】

この態様によれば、基板上で第1容量電極及び第2容量電極を、データ線に立体的に重ねて形成するのみならずデータ線に沿った領域にも形成することにより、各画素の開口領域を広げつつ相対的に蓄積容量を増大させることが可能となる。

【0034】

本発明の電気光学装置の他の態様では、前記遮光膜は、画像表示領域内から該画像表示領域外に延設されており、該画像表示領域外で固定電位に落とされている。

【0035】

この態様によれば、画像表示領域内において第2容量電極と接続された遮光膜は、画像表示領域外に延設されて固定電位に落とされているので、容量線として良好に機能する。この際特に、画像表示領域外の周辺領域にある周辺回路や駆動回路用の定電位線或いは定電位源を利用して、遮光膜を比較的簡単且つ確実に固定電位にできる。

【0036】

本発明のこのような作用及び他の利得は次に説明する実施の形態から明らかにされる。

【0037】

【発明の実施の形態】

以下、本発明の実施形態を図面に基づいて説明する。以下の各実施形態は、本発明の電気光学装置を液晶装置に適用したものである。

【0038】

(第1実施形態)

本発明の第1実施形態における電気光学装置の構成について、図1から図5を参照して説明する。図1は、電気光学装置の画像表示領域を構成するマトリクス状に形成された複数の画素における各種素子、配線等の等価回路である。図2は、データ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図であり、図3は、図2のA−A’断面図であり、図4は、図2のB−B’断面図である。また図5は、遮光膜を抽出して示すTFTアレイ基板の画素の平面図である。尚、図3及び図4においては夫々、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材毎に縮尺を異ならしめてある。

【0039】

図1において、本実施形態における電気光学装置の画像表示領域を構成するマトリクス状に形成された複数の画素は、画素電極9aと当該画素電極9aを制御するためのTFT30が形成されており、画像信号が供給されるデータ線6aが当該TFT30のソースに電気的に接続されている。データ線6aに書き込む画像信号S1、S2、…、Snは、この順に線順次に供給しても構わないし、相隣接する複数のデータ線6a同士に対して、グループ毎に供給するようにしても良い。また、TFT30のゲートに走査線3aが電気的に接続されており、所定のタイミングで、走査線3aにパルス的に走査信号G1、G2、…、Gmを、この順に線順次で印加するように構成されている。画素電極9aは、TFT30のドレインに電気的に接続されており、スイッチング素子であるTFT30を一定期間だけそのスイッチを閉じることにより、データ線6aから供給される画像信号S1、S2、…、Snを所定のタイミングで書き込む。画素電極9aを介して電気光学物質の一例として液晶に書き込まれた所定レベルの画像信号S1、S2、…、Snは、対向基板(後述する)に形成された対向電極(後述する)との間で一定期間保持される。液晶は、印加される電圧レベルにより分子集合の配向や秩序が変化することにより、光を変調し、階調表示を可能にする。ノーマリーホワイトモードであれば、印加された電圧に応じて入射光の通過光量が低減され、ノーマリーブラックモードであれば、印加された電圧に応じて入射光の通過光量が増大され、全体として電気光学装置からは画像信号に応じたコントラストを持つ光が出射する。ここで、保持された画像信号がリークするのを防ぐために、画素電極9aと対向電極との間に形成される液晶容量と並列に蓄積容量70を付加する。蓄積容量70は、TFT30のドレインと定電位を供給する容量線300との間に形成されている。

【0040】

図2において、電気光学装置のTFTアレイ基板上には、マトリクス状に複数の透明な画素電極9aが設けられており、画素電極9aの縦横の境界に各々沿ってデータ線6a及び走査線3aが設けられている。

【0041】

また、半導体層1aのうち図中右下がりの斜線領域で示したチャネル領域1a’に対向するように走査線3aが配置されており、走査線3aはゲート電極として機能する。このように、走査線3aとデータ線6aとの交差する個所には夫々、チャネル領域1a’に走査線3aがゲート電極として対向配置された画素スイッチング用TFT30が設けられている。

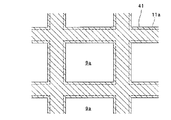

【0042】

本実施形態では、上層遮光膜の一例たる内蔵遮光膜41と下層遮光膜の一例たる第1遮光膜11aとが夫々、図中太線で示したように、走査線3a及びデータ線6aに沿って格子状に形成されており、各画素の開口領域を規定している。尚、各画素電極9aの縁は、図示されていないが、第1遮光膜11a及び内臓遮光膜41の縁に僅かに重なるように平面配置されている。

【0043】

図2から図4に示すように、第1遮光膜11aは、TFT30をTFTアレイ基板10側(図3及び図4中、下側)から覆う部分を含み、更に平面的に見て走査線3a及びデータ線6aに沿って格子状に形成されている。第1遮光膜11aは、TFTアレイ基板10の裏面や投射光学系からの戻り光を遮光し、この光に基づく光励起によりTFT30のオフ時のリーク電流が原因でTFT30の特性が変化するのを有効に防止する。このような第1遮光層11aは、例えば、CVD又はスパッタリングにより形成したTi(チタン)、Cr(クロム)、W(タングステン)、Ta(タンタル)、Mo(モリブデン)、Pb(鉛)等の高融点金属のうちの少なくとも一つを含む、金属単体、合金、金属シリサイド等からなる。またその膜厚は、例えば50〜300nm程度である。特に、複板式のカラー表示用のプロジェクタ等で複数の電気光学装置をプリズム等を介して組み合わせて一つの光学系を構成する場合には、他の電気光学装置からプリズム等を突き抜けて来る投射光部分からなる戻り光は強力であるので、このようにTFT30の下側に第1遮光膜11aを設けることは大変有効である。他方、内臓遮光膜41も、第1遮光膜11aと同様に、膜厚50〜300nm程度の高融点金属を含む、金属単体、合金、金属シリサイド等からなる。或いは、データ線6aと同様に、膜厚50〜500nm程度のAl膜からなる。

【0044】

図3に示すように、TFTアレイ基板10上で、データ線6aは、コンタクトホールACNTを介して例えばポリシリコン膜からなる半導体層1aのうち高濃度ソース領域1dに電気的に接続されている。

【0045】

他方、図4に示すように、画素電極9aは、中間導電層の一例たるバリア層34を中継することにより、コンタクトホールICNT及びBCNTを介して半導体層1aのうち高濃度ドレイン領域1eに電気的に接続されている。バリア層34は、図2に示すように、画素電極9aの角部に走査線3aに沿って島状に形成されている。このようにバリア層34を用いることにより、画素電極9aとTFT30を構成する半導体層1aとの間の層間距離が例えば1000nm程度に長くても、両者間を一つのコンタクトホールで接続する技術的困難性を回避しつつ比較的小径の二つの直列なコンタクトホールICNT及びBCNTで両者間を良好に接続でき、画素開口率を高めることが可能となる。特にこのようなバリア層34を用いれば、コンタクトホール開孔時におけるエッチングの突き抜け防止にも役立つ。このようなバリア層34は、例えばCVDにより形成した導電性のポリシリコン膜からなる。或いは、CVD又はスパッタリングにより形成したTi、Cr、W、Ta、Mo、Pb等の高融点金属のうちの少なくとも一つを含む、金属単体、合金、金属シリサイド等からなる。このような高融点金属から構成することにより、バリア層34を各画素の開口領域の一部を規定する遮光膜として機能させることも可能となる。但し、このようなバリア層34は、高融点金属以外のAl(アルミニウム)等の金属膜から構成されてもよいし、更に、これらの膜(例えば、ポリシリコン膜と金属膜と)を複数含む多層膜から構成されてもよい。いずれの場合にも、バリア層34の膜厚は、例えば50〜450nm程度とされる。

【0046】

図2から図4に示すように、走査線3aと同一膜(例えば、導電性のポリシリコン膜)からなる第1容量電極13-1と、バリア層34と同一膜からなる第2容量電極33-1とが誘電体膜42を介して対向配置されることにより、平面的に見てデータ線6aに重なる領域に、蓄積容量70(図1参照)の一例たる蓄積容量70-1が構築されている。すなわち、第1容量電極13-1は平面的に見て、走査線3aとデータ線6aとの交差部位に隣接した部位からデータ線6aに沿って延び、その一部がバリア層34の領域に延びる突出部を有する島状の電極で形成されている。そして、第2容量電極33-1は第1容量電極13-1に重なるように、走査線3aとデータ線6aとの交差部位に隣接した部位から第1容量電極13-1を越えて半導体層1aに隣接する部位までデータ線6aに沿って延び、その一部がバリア層34の領域に延びる突出部を有する島状の電極で形成されている。

【0047】

第1容量電極13-1は、誘電体膜42が除去されたコンタクトホールBCNTの隣接領域でバリア層34と面接触しており、バリア層34を中継して画素電極9aと接続されて(同時にコンタクトホールBCNTで高濃度ドレイン領域1eと接続されて)、画素電極電位とされる。

【0048】

第2容量電極33-1は、コンタクトホールSCNTを介して導電性の第1遮光膜11aに接続されている。格子状の第1遮光膜11aは、画素電極9aが配置された画像表示領域からその周囲に延設され、定電位源と電気的に接続されて、固定電位とされる。即ち、第2容量電極33-1は、第1遮光膜11aに接続されて固定電位とされる。このように本実施形態では、第1遮光膜11aが、図1に示した容量線300として機能する。そして、画像表示領域から周辺領域に延設される第1遮光膜11aが接続される定電位源としては、TFT30を駆動するための走査信号を走査線3aに供給するための走査線駆動回路(後述する)や画像信号をデータ線6aに供給するサンプリング回路を制御するデータ線駆動回路(後述する)に供給される正電源や負電源の定電位源でも良いし、対向基板20側に供給される定電位でも構わない。

【0049】

蓄積容量70-1の誘電体膜42は、例えば膜厚5〜200nm程度の比較的薄いBHTO膜やHTO膜から構成される。蓄積容量70-1を増大させる観点からは、膜厚の信頼性が十分に得られる限りにおいて、誘電体膜42は薄い程良い。

【0050】

図3に示すように、電気光学装置は、透明なTFTアレイ基板10と、これに対向配置される透明な対向基板20とを備えている。TFTアレイ基板10は、例えば石英基板、ガラス基板、シリコン基板からなり、対向基板20は、例えばガラス基板や石英基板からなる。TFTアレイ基板10には、画素電極9aが設けられており、その上側には、ラビング処理等の所定の配向処理が施された配向膜16が設けられている。画素電極9aは例えば、ITO(Indium Tin Oxide)膜などの透明導電性薄膜からなる。また配向膜16は例えば、ポリイミド薄膜などの有機薄膜からなる。

【0051】

他方、対向基板20には、その全面に渡って対向電極21が設けられており、その下側には、ラビング処理等の所定の配向処理が施された配向膜22が設けられている。対向電極21は例えば、ITO膜などの透明導電性薄膜からなる。また配向膜22は、ポリイミド薄膜などの有機薄膜からなる。

【0052】

TFTアレイ基板10には、各画素電極9aに隣接する位置に、各画素電極9aをスイッチング制御する画素スイッチング用TFT30が設けられている。

【0053】

対向基板20には、更に図3及び図4に示すように、格子状或いはストライプ状の第2遮光膜23を設けるようにしてもよい。このような構成を採ることで、対向基板20側からの入射光に対する遮光をより確実に行える。しかも、第2遮光膜23は、入射光が照射される面を高反射な膜で形成することにより、電気光学装置の温度上昇を防ぐ働きをする。

【0054】

このように構成され、画素電極9aと対向電極21とが対面するように配置されたTFTアレイ基板10と対向基板20との間には、後述のシール材により囲まれた空間に電気光学物質の一例である液晶が封入され、液晶層50が形成される。液晶層50は、画素電極9aからの電界が印加されていない状態で配向膜16及び22により所定の配向状態をとる。液晶層50は、例えば一種又は数種類のネマティック液晶を混合した液晶からなる。シール材は、TFTアレイ基板10及び対向基板20をそれらの周辺で貼り合わせるための、例えば光硬化性樹脂や熱硬化性樹脂からなる接着剤であり、両基板間の距離を所定値とするためのグラスファイバー或いはガラスビーズ等のギャップ材が混入されている。

【0055】

更に、画素スイッチング用TFT30の下には、下地絶縁膜12が設けられている。下地絶縁膜12は、第1遮光膜11aからTFT30を絶縁すると共に、TFTアレイ基板10の全面に形成されることにより、TFTアレイ基板10の表面の研磨時における荒れや、洗浄後に残る汚れ等で画素スイッチング用TFT30の特性の劣化を防止する機能を有する。

【0056】

図3において、画素スイッチング用TFT30は、LDD(Lightly Doped Drain)構造を有しており、走査線3a、当該走査線3aからの電界によりチャネルが形成される半導体層1aのチャネル領域1a’、走査線3aと半導体層1aとを絶縁するゲート絶縁膜を含む絶縁薄膜2、データ線6a、半導体層1aの低濃度ソース領域1b及び低濃度ドレイン領域1c、半導体層1aの高濃度ソース領域1d並びに高濃度ドレイン領域1eを備えている。高濃度ドレイン領域1eには、図4に示すように複数の画素電極9aのうちの対応する一つが、コンタクトホールICNT及びBCNTを介してバリア層34により中継接続されている。

【0057】

図3及び図4に示すように、走査線3aの上には、高濃度ソース領域1dへ通じるコンタクトホールACNT及び高濃度ドレイン領域1eへ通じるコンタクトホールICNTが各々形成された第1層間絶縁膜4が形成されている。データ線6a上には、バリア層34へ通じるコンタクトホールICNTが形成された第2層間絶縁膜7が形成されている。第2層間絶縁膜7上には、内臓遮光膜41が形成されており、この上には更に、バリア層34へのコンタクトホールICNTが形成された第3層間絶縁膜8が形成されている。前述の画素電極9aは、このように構成された第3層間絶縁膜8の上面に設けられている。

【0058】

以上説明したように本実施形態によれば、TFTアレイ基板10上で第1容量電極13-1及び第2容量電極33-1をデータ線6aに立体的に重ねて形成することにより、前述した背景技術の如く容量線或いは容量電極を走査線に横並びに配線する必要が無いので各画素の非開口領域を広げないで済み、大きな蓄積容量が得られる。しかも、第1容量電極13-1は、走査線3aと同一膜からなり、第2容量電極33-1は、バリア層34と同一膜からなるので、このような蓄積容量70-1をデータ線6aに重なる領域に構築するために専用の導電膜を追加形成する必要はなく、装置構成及び製造工程を簡略化する上でも大変有利である。特に、走査線3aの形成時におけるパターンニングに変更を加えるだけで第1容量電極13-1を形成でき、バリア層34の形成時におけるパターンニングに変更を加えるだけで第2容量電極33-1を形成できる。これらに加えて、各画素の開口領域を規定する第1遮光膜11aを、第2容量電極33-1を固定電位に落とすための容量線300(図1参照)としても用いるので、走査線3aと横並びに容量線を配線する必要もない。更に、データ線6a、走査線3a、TFT30等を上下から覆う格子状の内蔵遮光膜41及び第1遮光膜11aにより、プロジェクタ用途のように強力な入射光を扱う場合でも、斜めの入射光、戻り光、内面反射光、多重反射光等の表示に悪影響を及ぼす光に対して十分な遮光を行える。

【0059】

以上説明した実施形態では、多数の導電層を積層することにより、データ線6aや走査線3aに沿った領域に段差が生じるが、TFTアレイ基板10、下地絶縁膜12、第1層間絶縁膜4、第2層間絶縁膜7に溝を掘って、データ線6a等の配線やTFT30等を埋め込むことにより平坦化処理を行ってもよいし、第3層間絶縁膜8や第2層間絶縁膜7の上面の段差をCMP(Chemical Mechanical Polishing)処理等で研磨することにより、或いは有機SOGを用いて平らに形成することにより、当該平坦化処理を行ってもよい。

【0060】

更に以上説明した実施形態では、画素スイッチング用TFT30は、好ましくは図3に示したようにLDD構造を持つが、低濃度ソース領域1b及び低濃度ドレイン領域1cに不純物の打ち込みを行わないオフセット構造を持ってよいし、走査線3aの一部からなるゲート電極をマスクとして高濃度で不純物を打ち込み、自己整合的に高濃度ソース及びドレイン領域を形成するセルフアライン型のTFTであってもよい。また本実施形態では、画素スイッチング用TFT30のゲート電極を高濃度ソース領域1d及び高濃度ドレイン領域1e間に1個のみ配置したシングルゲート構造としたが、これらの間に2個以上のゲート電極を配置してもよい。このようにデュアルゲート或いはトリプルゲート以上でTFTを構成すれば、チャネルとソース及びドレイン領域との接合部のリーク電流を防止でき、オフ時の電流を低減することができる。

【0061】

尚、第1実施形態及び以下に説明する各実施形態の電気光学装置において導電膜間を絶縁する各層間絶縁膜は、例えば、常圧、減圧CVD法、プラズマCVD法等によりTEOS(テトラ・エチル・オルソ・シリケート)ガス、TEB(テトラ・エチル・ボートレート)ガス等を用いて、NSG(ノンドープト・シリケート・ガラス)、PSG(リン・シリケート・ガラス)などのシリケートガラス膜、窒化シリコン膜や酸化シリコン膜等から構成すればよい。また、各層間絶縁膜の膜厚は、100〜1000nm程度である。

【0062】

本実施形態では特に、画素電極電位とされる第1容量電極13-1とデータ線6aとの間に、固定電位とされる第2容量電極33-1が配置されているので、データ線6aと第1容量電極13-1との間の容量カップリングにより、両者の電位変動が相互に悪影響を及ぼすことを未然防止できる。逆に、このような容量カップリングによる悪影響を低減するために両者間の第1層間絶縁膜4を厚くしないで済む。

【0063】

また本実施形態では、前述のように容量線300としての機能を有する第1遮光膜11a及び内蔵遮光膜41は、共に格子状に形成されているが、第1遮光膜11aは容量線300としての機能を果たす限りにおいてストライプ状に形成されていてもよい。更に、両方の遮光膜が重なることで格子状の非開口領域となるように構成されてもよい。加えて本実施形態では、第1遮光膜11a及び内蔵遮光膜41を抽出して示す図5のように、第1遮光膜11a及び内蔵遮光膜41が共に格子状に形成されており且つ第1遮光膜11aが平面的に見て内蔵遮光膜41の形成領域からはみ出さないように(即ち、一回り小さく)構成するのが好ましい。この際更に、両者間にある不図示の走査線、データ線及びTFT等は、平面的に見て第1遮光膜11aの形成領域からはみ出さないように構成されるのが好ましい。このように構成すれば、対向基板20側からの入射光が内蔵遮光膜41の形成領域からはみ出した第1遮光膜11a(更に、走査線、データ線等)で反射することで、当該電気光学装置の内部における内面反射光や多重反射光が発生することを効果的に未然防止できる。尚、このように内蔵遮光膜41を第1遮光膜11aよりも一回り大きく形成すると、TFTアレイ基板10側からの戻り光が第1遮光膜11aの形成領域からはみ出した内蔵遮光膜41部分で反射することで、当該電気光学装置の内部における内面反射光や多重反射光は若干発生する。しかしながら、戻り光は入射光に比べて遥かに光強度が低いために、戻り光による内面反射や多重反射光の悪影響は入射光のそれに比べて軽微である。従って本実施形態の構成は有利である。

【0064】

尚、本実施形態では、第1遮光膜11aを容量線300として利用し、内蔵遮光膜41を容量線300として利用しないので、内蔵遮光膜41は導電性である必要はない。

【0065】

(第2実施形態)

次に、図6を参照して本発明の電気光学装置の第2実施形態について説明する。ここに、図6は、データ線、走査線、画素電極等が形成されたTFTアレイ基板の画素の平面図である。また、図6において、図2から図5(第1実施形態)と同様の構成要素には、同様の参照符号を付し、その説明は省略する。

【0066】

図6に示すように、第2実施形態では、第1実施形態と比べて、平面的に見て図1に示した蓄積容量70の他の一例たる蓄積容量70-2が、データ線6aに重なる領域のみならず走査線3aに沿った領域にも形成されている点が異なる。より具体的には、第2実施形態では、第1容量電極13-2は、データ線6aに重なる部分に加えて走査線3aに沿って伸びる部分からなり(即ち、図6中で略T字状に形成されており)、第2容量電極33-2は、データ線6aに重なる部分に加えて走査線3aに沿って伸びる部分からなる(即ち、図6中で略L字状に形成されている)。そして、内蔵遮光膜41’は、このような蓄積容量70-2を隠すように、走査線3aに沿って伸びる部分が幅広に形成され且つコンタクトホールICNTを形成可能なようにコンタクトホールICNTに対応する個所が括れて形成されている。更に、この内蔵遮光膜41’の括れ部分における遮光性能の低下を補うべく、コンタクトホールICNTの周囲には、走査線3a或いは第1用容量電極13-2と同一膜からなる島状の導電層3bが形成されている。また、バリア層34は走査線3aに沿って配置されている。その他の構成については、第1実施形態の場合と同様である。

【0067】

従って、第2実施形態によれば、TFTアレイ基板10上で第1容量電極13-2及び第2容量電極33-2をデータ線6aに立体的に重ねて形成することに加えて、走査線3aに沿った領域にも形成することにより、より大きな蓄積容量が得られる。

【0068】

(第3実施形態)

次に、図7から図9を参照して本発明の電気光学装置の第3実施形態について説明する。ここに、図7は、データ線、走査線、画素電極等が形成されたTFTアレイ基板の画素の平面図であり、図8は、図7のA−A’断面図であり、図9は、図7のB−B’断面図である。尚、図8及び図9においては夫々、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材毎に縮尺を異ならしめてある。また、図7から図9において、図2から図5(第1実施形態)と同様の構成要素には、同様の参照符号を付し、その説明は省略する。

【0069】

図7から図9に示すように、第3実施形態では、第1実施形態と比べて、TFT30の下側にある第1遮光膜11aに代えて、TFT30の上側にある導電性の内蔵遮光膜43を容量線300(図1参照)として用いている。更に、内蔵遮光膜43は、第1実施形態における内蔵遮光膜41のようにデータ線6aの上側ではなく、データ線6aの下側に積層されており、コンタクトホールACNTを開孔するためにコンタクトホールACNTに対応する個所で分断されている。即ち、内蔵遮光膜43は、格子状ではなく、走査線3aに沿って伸びる本線部とこの本線部からデータ線6aに沿って(図7中上側に)突出した突出部とを含むストライプ状に形成されている。更に、第2容量電極33-3と容量線300としての内蔵遮光膜43との間には、第1容量電極13-3が介在しないため、平面的に見て第2容量電極33-3と内蔵遮光膜43(容量線300)とを接続するコンタクトホールBMCNTを開孔する個所にも、蓄積容量70-3が形成されている。即ち、第2容量電極33-1と第1遮光膜11a(容量線300)とを接続するコンタクトホールSCNTを開孔する個所に蓄積容量を形成できない第1実施形態の場合と比べて、蓄積容量の面積が増大している。その他の構成については、第1実施形態の場合と同様である。

【0070】

このように第3実施形態によれば、TFTアレイ基板10上で第1容量電極13-3及び第2容量電極33-3をデータ線6aに立体的に重ねて形成することにより、大きな蓄積容量が得られる。

【0071】

また第3実施形態において、データ線6aの下側に代えてデータ線6aの上側に、容量線300としての内蔵遮光膜43を配置することも可能である。この場合には、コンタクトホールACNTを避けて内蔵遮光膜43を分断させる必要はなく格子状の内蔵遮光膜により遮光性能を向上できる。他方、コンタクトホールBMCNTについては、データ線6aの形成領域から外して開孔すればよい。

【0072】

尚、本実施形態では、内蔵遮光膜43を容量線300として利用し、第1遮光膜11aを容量線300として利用しないので、第1遮光膜11aは導電性である必要はない。

【0073】

(第4実施形態)

次に、図10を参照して本発明の電気光学装置の第4実施形態について説明する。ここに、図10は、データ線、走査線、画素電極等が形成されたTFTアレイ基板の画素の平面図である。また、図10において、図2から図5(第1実施形態)或いは図7から図9(第3実施形態)と同様の構成要素には、同様の参照符号を付し、その説明は省略する。

【0074】

図10に示すように、第4実施形態では、第3実施形態と比べて、平面的に見て図1に示した蓄積容量70の他の一例たる蓄積容量70-4が、データ線6aに重なる領域のみならず走査線3aに沿った領域にも形成されている点が異なる。より具体的には、第4実施形態では、第1容量電極13-4は、データ線6aに重なる部分に加えて走査線3aに沿って伸びる部分からなり(即ち、図10中で略T字状に形成されており)、第2容量電極33-4は、データ線6aに重なる部分に加えて走査線3aに沿って伸びる部分からなる(即ち、図10中で略L字状に形成されている)。そして、内蔵遮光膜43’は、このような蓄積容量70-4を隠すように、走査線3aに沿って伸びる部分が幅広に形成され且つコンタクトホールICNTを形成可能なようにコンタクトホールICNTに対応する個所が括れて形成されている。更に、この内蔵遮光膜43’の括れ部分における遮光性能の低下を補うべく、コンタクトホールICNTの周囲には、走査線3a或いは第1用容量電極13-4と同一膜からなる島状の導電層3bが形成されている。その他の構成については、第3実施形態の場合と同様である。

【0075】

従って、第4実施形態によれば、TFTアレイ基板10上で第1容量電極13-4及び第2容量電極33-4をデータ線6aに立体的に重ねて形成することに加えて、走査線3aに沿った領域にも形成することにより、より大きな蓄積容量が得られる。

【0076】

ここで、以上説明した第1から第4実施形態における第1容量電極13(13-1〜13-4)と高濃度ドレイン領域1eとの電気的接続について、図11を参照して説明を加える。ここに、図11(a)は、図4或いは図9に示したB−B’断面のうち、この電気的接続に係る部分を拡大して示す断面図である。

【0077】

図11(a)に示すように、第1容量電極13(13-1〜13-4)は、バリア層34を介して高濃度ドレイン領域1eに電気的に接続されて、画素電極電位とされる。このような接続は、“バリア層34の膜厚>絶縁薄膜2(ゲート絶縁膜)の膜厚”とすることで、コンタクトホールBCONTを形成する際に、比較的簡単に得られる。

【0078】

但し、図11(b)に示すように、第1容量電極13を形成する前に絶縁薄膜2(ゲート絶縁膜)にコンタクトホールBCNT’を開孔することで、第1容量電極13と高濃度ドレイン領域1eとを直接接続してもよい。このような接続のためには、コンタクトホールBCNT’の底にポリシリコン膜等からなる高濃度ドレイン領域1eが露出した際における、当該高濃度ドレイン領域1eの表面酸化が障害となり得るが、このような酸化膜は、フッ酸でライトエッチングすれば比較的簡単に除去できる。但し、絶縁薄膜2(ゲート絶縁膜)に対して、フッ酸でライトエッチングすると、ピンホール等の欠陥が発生する可能性があるので、図11(a)に示したように第1容量電極13を、バリア層34を介して高濃度ドレイン領域1eに電気的に接続した方が、装置信頼性を高める上で有利である。

【0079】

或いは、図11(c)に示すように、第1容量電極13を形成する前に絶縁薄膜2(ゲート絶縁膜)にコンタクトホールBCNT’を開孔することで、第1容量電極13と高濃度ドレイン領域1eとを直接接続すると共に、バリア層34を中継することなく第1容量電極13を画素電極9aに直接接続してもよい。即ち、図11(a)及び図11(b)に示した例では、第1容量電極13は、バリア層34に接続され且つ図中右方に延設されたバリア層34がコンタクトホールICNTにより画素電極9aに接続されるが(図4及び図9参照)、図11(c)に示した例では、第1容量電極13そのものが図中右方に延設され、当該延設された第1容量電極13上に形成されたコンタクトホールICNTにより、第1容量電極13が画素電極9aに接続される。この場合、バリア層34は、例えば図6に示した略L字状の第2容量電極33-2のコーナー領域から延設して設ければよく、図11(c)中の誘電体膜42を、第1容量電極13とバリア層34との間に介在する誘電体膜として利用することで、この領域にも蓄積容量を形成できる。

【0080】

(電気光学装置の全体構成)

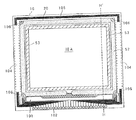

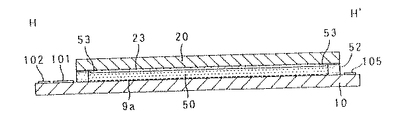

以上のように構成された各実施形態における電気光学装置の全体構成を図12及び図13を参照して説明する。尚、図12は、TFTアレイ基板10をその上に形成された各構成要素と共に対向基板20の側から見た平面図であり、図13は、図12のH−H’断面図である。

【0081】

図12において、TFTアレイ基板10の上には、シール材52がその縁に沿って設けられており、その内側に並行して、例えば第2遮光膜23と同じ或いは異なる材料から成る画像表示領域10aの周辺を規定する額縁としての第3遮光膜53が設けられている。シール材52の外側の領域には、データ線6aに画像信号を所定タイミングで供給することによりデータ線6aを駆動するデータ線駆動回路101及び外部回路接続端子102がTFTアレイ基板10の一辺に沿って設けられており、走査線3aに走査信号を所定タイミングで供給することにより走査線3aを駆動する走査線駆動回路104が、この一辺に隣接する2辺に沿って設けられている。走査線3aに供給される走査信号遅延が問題にならないのならば、走査線駆動回路104は片側だけでも良いことは言うまでもない。また、データ線駆動回路101を画像表示領域10aの辺に沿って両側に配列してもよい。更にTFTアレイ基板10の残る一辺には、画像表示領域10aの両側に設けられた走査線駆動回路104間をつなぐための複数の配線105が設けられている。また、対向基板20のコーナー部の少なくとも1箇所においては、TFTアレイ基板10と対向基板20との間で電気的に導通をとるための導通材106が設けられている。そして、図13に示すように、図12に示したシール材52とほぼ同じ輪郭を持つ対向基板20が当該シール材52によりTFTアレイ基板10に固着されている。

【0082】

尚、TFTアレイ基板10上には、これらのデータ線駆動回路101、走査線駆動回路104等に加えて、複数のデータ線6aに画像信号を所定のタイミングで印加するサンプリング回路、複数のデータ線6aに所定電圧レベルのプリチャージ信号を画像信号に先行して各々供給するプリチャージ回路、製造途中や出荷時の当該電気光学装置の品質、欠陥等を検査するための検査回路等を形成してもよい。

【0083】

以上図1から図13を参照して説明した各実施形態では、データ線駆動回路101及び走査線駆動回路104をTFTアレイ基板10の上に設ける代わりに、例えばTAB(Tape Automated bonding)基板上に実装された駆動用LSIに、TFTアレイ基板10の周辺部に設けられた異方性導電フィルムを介して電気的及び機械的に接続するようにしてもよい。また、対向基板20の投射光が入射する側及びTFTアレイ基板10の出射光が出射する側には各々、例えば、TNモード、VA(Vertically Aligned)モード、PDLC(Polymer Dispersed Liquid Crystal)モード等の動作モードや、ノーマリーホワイトモード/ノーマリーブラックモードの別に応じて、偏光フィルム、位相差フィルム、偏光板などが所定の方向で配置される。

【0084】

以上説明した各実施形態における電気光学装置は、プロジェクタに適用されるため、3枚の電気光学装置がRGB用のライトバルブとして各々用いられ、各ライトバルブには各々RGB色分解用のダイクロイックミラーを介して分解された各色の光が投射光として各々入射されることになる。従って、各実施形態では、対向基板20に、カラーフィルタは設けられていない。しかしながら、第2遮光膜23の形成されていない画素電極9aに対向する所定領域にRGBのカラーフィルタをその保護膜と共に、対向基板20上に形成してもよい。このようにすれば、プロジェクタ以外の直視型や反射型のカラー電気光学装置について、各実施形態における電気光学装置を適用できる。また、対向基板20上に1画素1個対応するようにマイクロレンズを形成してもよい。あるいは、TFTアレイ基板10上のRGBに対向する画素電極9a下にカラーレジスト等でカラーフィルタ層を形成することも可能である。このようにすれば、入射光の集光効率を向上することで、明るい電気光学装置が実現できる。更にまた、対向基板20上に、何層もの屈折率の相違する干渉層を堆積することで、光の干渉を利用して、RGB色を作り出すダイクロイックフィルタを形成してもよい。このダイクロイックフィルタ付き対向基板によれば、より明るいカラー電気光学装置が実現できる。

【0085】

本発明は、上述した各実施形態に限られるものではなく、請求の範囲及び明細書全体から読み取れる発明の要旨或いは思想に反しない範囲で適宜変更可能であり、そのような変更を伴なう電気光学装置もまた本発明の技術的範囲に含まれるものである。

【図面の簡単な説明】

【図1】本発明の第1実施形態の電気光学装置における画像表示領域を構成するマトリクス状の複数の画素に設けられた各種素子、配線等の等価回路である。

【図2】第1実施形態の電気光学装置におけるデータ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図である。

【図3】図2のA−A’断面図である。

【図4】図2のB−B’断面図である。

【図5】第1実施形態における遮光膜を抽出して示すTFTアレイ基板の画素の平面図である。

【図6】第2実施形態の電気光学装置におけるデータ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図である。

【図7】第3実施形態の電気光学装置におけるデータ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図である。

【図8】図7のA−A’断面図である。

【図9】図8のB−B’断面図である。

【図10】第4実施形態の電気光学装置におけるデータ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図である。

【図11】第1容量電極と高濃度ドレイン領域との電気的接続の一例を示す断面図(図11(a))及び他の例を示す断面図(図11(b)、図11(c))である。

【図12】各実施形態の電気光学装置におけるTFTアレイ基板をその上に形成された各構成要素と共に対向基板の側から見た平面図である。

【図13】図12のH−H’断面図である。

【符号の説明】

1a…半導体層

1a’…チャネル領域

1b…低濃度ソース領域

1c…低濃度ドレイン領域

1d…高濃度ソース領域

1e…高濃度ドレイン領域

2…絶縁薄膜(ゲート絶縁膜)

3a…走査線

4…第1層間絶縁膜

6a…データ線

7…第2層間絶縁膜

8…第3層間絶縁膜

9a…画素電極

10…TFTアレイ基板

11a…第1遮光膜

12…下地絶縁膜

13(13-1〜13-4)…第1容量電極

16…配向膜

20…対向基板

21…対向電極

22…配向膜

23…第2遮光膜

30…TFT

33(33-1〜33-4)…第2容量電極

34…バリア層

41、41’、43、43’…内蔵遮光膜

50…液晶層

70(70-1〜70-4)…蓄積容量

300…容量線

SCNT、BCNT、ICNT、ACNT、BMCNT…コンタクトホール[0001]

BACKGROUND OF THE INVENTION

The present invention belongs to the technical field of an electro-optical device of an active matrix driving system, and in particular, a pair of capacitor electrodes for adding a storage capacitor to a pixel electrode, a thin film transistor (Thin Film Transistor: hereinafter referred to as a TFT as appropriate) In the technical field of an electro-optical device of a type provided in a laminated structure on a substrate.

[0002]

[Background]

Conventionally, in an active matrix driving type electro-optical device using TFT driving, when a scanning signal is supplied to the gate electrode of the TFT via the scanning line, the TFT is turned on, and the data line is connected to the source region of the semiconductor layer. An image signal supplied through the TFT is supplied to the pixel electrode through the source and drain of the TFT. Since such an image signal is supplied only for a very short time for each pixel electrode through each TFT, the voltage of the image signal supplied through the TFT is set to be much longer than the time in which it is turned on. In general, a storage capacitor is added to each pixel electrode (in parallel with a liquid crystal capacitor or the like) so that the pixel electrode can be held for a long time.

[0003]

Such a storage capacitor generally includes a first capacitor electrode extending from a conductive polysilicon film or the like constituting a drain region of a TFT connected to the pixel electrode and having a pixel electrode potential, and a dielectric on the first capacitor electrode. The capacitor line is configured to include a second capacitor electrode arranged opposite to each other with a fixed potential through the film. Such a capacitor line is generally made of the same conductive film as the scanning line (for example, a conductive polysilicon film), and is generally wired side by side in parallel with the scanning line.

[0004]

On the other hand, in this type of electro-optical device, if the display light passes through the gap between adjacent pixel electrodes (due to so-called light leakage), the contrast ratio is lowered and the image quality is lowered. For this reason, a stripe-shaped light shielding film is provided on the counter substrate so as to cover the gap between the pixel electrodes along the scanning line and the capacitance line, which are generally made of a transparent polysilicon film, etc., or the gap between the pixel electrodes along the data line is provided. The data line is formed to be wide from a reflective film such as an Al (aluminum) film so as to cover it. As described above, the opening region of each pixel (that is, the region through which light that effectively contributes to display passes) is defined by combining the light shielding film and the data line on the counter substrate.

[0005]

[Problems to be solved by the invention]

In this type of electro-optical device, there is a strong general demand for high-quality display images. For this purpose, the pixel aperture ratio is increased while the pixel pitch is reduced (that is, the display light in each pixel is increased). It is important to widen the opening area through which the display light is transmitted with respect to the non-opening area in each pixel through which no light is transmitted.

[0006]

However, according to the above-described background art in which the scanning lines and the capacitance lines are wired side by side in the image display region, the scanning lines and the capacitance lines can be wired in accordance with the increase in the aperture ratio of the fine pitch pixels. The non-opening area of each pixel becomes narrow. For this reason, there is a problem that as the pixel pitch is further miniaturized, it becomes difficult to create a sufficiently large storage capacitor and to provide sufficient conductivity to the scanning line and the capacitor line. If sufficient storage capacity cannot be obtained or sufficient conductivity is not obtained for the scanning lines and the capacity lines, eventually, crosstalk and ghosts in the display image increase and image quality deteriorates. Problems arise. That is, there is a problem that is difficult to solve in order to improve the image quality such that such image quality deterioration becomes obvious as the aperture ratio of the fine pitch pixels increases.

[0007]

On the other hand, according to the technique for defining the opening area of each pixel by combining the light shielding film and the data line on the counter substrate as described above, the light shielding against the oblique incident light or the strong incident light especially for the projector use is performed. It is difficult to do enough. In other words, according to this technique, light incident on obliquely incident light, back-surface reflected light, or light that penetrates the composite optical system when the electro-optical device is used as a light valve in combination with a double-plate projector are returned. The light is not sufficiently shielded, and it is also difficult to prevent the internal reflection light and the multiple reflection light from being generated by such oblique incident light and return light. Therefore, there is a problem that the contrast ratio is lowered by such oblique incident light, return light, internal reflection light, and multiple reflection light. In addition, when such oblique incident light, return light, internal reflection light and multiple reflection light enter the channel region of the pixel switching TFT, the TFT transistor characteristics deteriorate (light leakage) due to the photoelectric effect. Finally, there is also a problem that image quality deterioration is caused.

[0008]

The present invention has been made in view of the above-mentioned problems, and oblique incident light that can increase the pixel aperture ratio and simultaneously increase the storage capacity (or suppress the decrease in the storage capacity) and does not contribute to display. It is another object of the present invention to provide an electro-optical device capable of improving the light shielding performance against return light, reducing crosstalk and ghost, improving the contrast ratio, and capable of displaying a high-quality image.

[0009]

[Means for Solving the Problems]

In order to solve the above problems, an electro-optical device of the present invention includes a scanning line and a data line intersecting each other on a substrate, a thin film transistor provided corresponding to the intersection of the scanning line and the data line, and an insulating film. An intermediate conductive layer provided in a layer different from the semiconductor layer of the thin film transistor, a pixel electrode connected to the thin film transistor through the intermediate conductive layer, and a region overlapping the data line in plan view And a conductive light-shielding film formed so as to overlap the scanning line and at least partially define an opening area of the pixel, and the storage capacitor is electrically connected to the thin film transistor. A first capacitor electrode having a portion that is connected and overlaps the light-shielding film in plan view, and a projecting portion that projects from the light-shielding film toward the opening region; and And a second capacitive electrode connected to the light-shielding film and having a fixed potential. The intermediate conductive layer is electrically connected to the first capacitive electrode at the projecting portion. It is connected to.

Also,In order to solve the above problems, an electro-optical device of the present invention includes a scanning line and a data line intersecting each other on a substrate, a thin film transistor provided corresponding to the intersection of the scanning line and the data line, and the thin film transistor. A pixel electrode connected via an intermediate conductive layer, a storage capacitor disposed in a region overlapping the data line in plan view, and a conductive light shielding film that at least partially defines an opening region of each pixel With. The storage capacitor is made of the same film as the scanning line and is electrically connected to the pixel electrode to be a pixel electrode potential, and the first capacitor electrode via a dielectric film And a second capacitor electrode which is disposed opposite to the intermediate conductive layer and is made of the same film as the intermediate conductive layer and connected to the light-shielding film to have a fixed potential.

[0010]

According to the electro-optical device of the present invention, it is possible to construct a storage capacitor by using a region that overlaps the data line when viewed in plan. At this time, it is not necessary to wire the capacitor lines or the capacitor electrodes side by side with the scanning lines as in the background art described above. You don't have to. That is, by forming the first capacitor electrode and the second capacitor electrode three-dimensionally on the data line on the substrate, it is possible to relatively increase the storage capacity while expanding the opening area of each pixel.

[0011]

In addition, the first capacitor electrode that is set to the pixel electrode potential is made of the same film as the scanning line, and the second capacitor electrode that is set to the fixed potential is made of the same film as the intermediate conductive layer that relay-connects the thin film transistor to the pixel electrode. In order to construct such a storage capacitor in a region overlapping the data line, it is not necessary to additionally form a dedicated conductive film, which is very advantageous for simplifying the device configuration and the manufacturing process. In particular, the same film as the scanning line can be effectively used in the region overlapping the data line (the region not overlapping the scanning line), and the first capacitor electrode can be formed simply by changing the patterning when forming the scanning line. It is practically convenient. Furthermore, since such an intermediate conductive layer has a long interlayer distance between the pixel electrode and the thin film transistor, it avoids the technical difficulty of connecting the two with a single contact hole, and the two series contact holes with relatively small diameters both Can be connected, the plane area required to connect the two can be reduced, and the device reliability can be improved. Since the second capacitor electrode can be formed simply by changing the patterning when forming the intermediate conductive layer, it is practically convenient.

[0012]

In addition to these, the second capacitor electrode is connected to a conductive light-shielding film that at least partially defines the opening region of each pixel to be a fixed potential, that is, for dropping the light-shielding film to a fixed potential. Since it is also used as a capacitor line, it is not necessary to arrange a capacitor line that is at a fixed potential side by side with the scanning line, and the pixel aperture ratio can be improved. Furthermore, even when handling strong incident light, such as for projector applications, the light shielding film for setting the second capacitor electrode to a fixed potential enables oblique incident light, return light, internal reflection light, multiple reflection light, etc. as described above. The light shielding performance against light that adversely affects the display can be improved.

[0013]

As a result of the above, the electro-optical device of the present invention can increase the pixel aperture ratio and simultaneously increase the storage capacity, improve the light shielding performance, and finally reduce the crosstalk and ghost and improve the contrast ratio. High-quality image display is possible.

[0014]

In one aspect of the electro-optical device of the present invention, the second capacitor electrode is disposed between the first capacitor electrode and the data line.

[0015]

According to this aspect, the second capacitor electrode set to the fixed potential functions as an electromagnetic shield between the first capacitor electrode set to the pixel electrode potential and the data line to which the image signal is supplied. For this reason, due to the capacitive coupling between the data line and the first capacitive electrode, the potential fluctuation in the data line adversely affects the first capacitive electrode (and also the pixel electrode), or the potential fluctuation in the first capacitive electrode It can prevent the data line from being adversely affected. Conversely, in order to reduce the adverse effects due to such capacitive coupling, it is not necessary to thicken the interlayer insulating film between them.

[0016]

In another aspect of the electro-optical device according to the aspect of the invention, the light shielding film is disposed on a lower layer side of the thin film transistor on the substrate and covers at least a channel region of the thin film transistor when viewed from the substrate side. The lower-layer light-shielding film and the second capacitor electrode are connected via a contact hole opened in a region where the first capacitor electrode is not formed in plan view.

[0017]

According to this aspect, since the lower light shielding film covers at least the channel region of the thin film transistor when viewed from the substrate side, the return light from the lower layer side of the thin film transistor (that is, the back-surface reflected light or the electro-optical device as a light valve is a double plate type When used in combination with a projector, the channel region can be shielded against light penetrating the combining optical system, etc., and the deterioration of characteristics of the thin film transistor due to return light can be reduced. The second capacitor electrode is connected to such a conductive lower-layer light-shielding film through a contact hole opened in a region where the first capacitor electrode is not formed in plan view, and has a fixed potential. It is said. Therefore, the storage capacitor can be constructed in a region overlapping the data line by using the lower light shielding film also as the capacitor line.

[0018]

In the aspect including the lower-layer light-shielding film, an upper-layer light-shielding film that at least partially defines an opening region of each pixel may be further provided on the upper layer side of the thin film transistor.

[0019]

According to this configuration, the upper light shielding film provided on the upper layer side of the thin film transistor prevents light incident on the obliquely incident light from the upper layer side of the thin film transistor, for example, closer to the thin film transistor than the light shielding film provided on the counter substrate. In particular, even in the case of strong incident light, such as projector applications, it is possible to effectively prevent light leakage due to oblique incident light, and further, internal reflection based on oblique incident light and further this and return light. Light and multiple reflected light can be effectively shielded. In this case, the upper light shielding film does not need to be conductive.

[0020]

In this case, the upper light-shielding film may be further laminated on the substrate on the upper layer side than the data line and may be formed in a lattice shape in plan view.

[0021]

With this configuration, since there is no upper light shielding film between the data line and the thin film transistor, a contact hole for connecting the data line and the thin film transistor in a plan view is opened at a position overlapping the upper light shielding film. it can. That is, in order to secure a gap for opening the contact hole, it is not necessary to provide a constriction or an opening in the upper light shielding film, or to form the upper light shielding film in a stripe shape. Can be formed in a lattice shape that completely covers the surface. As a result, the opening area of each pixel can be defined only by the upper light shielding film, and the light shielding performance can be further enhanced.

[0022]

In another aspect of the electro-optical device according to the aspect of the invention, the light-shielding film includes a conductive upper-layer light-shielding film disposed on an upper layer side of the thin film transistor on the substrate.

[0023]

According to this aspect, the upper light shielding film provided on the upper layer side of the thin film transistor makes it possible to shield the oblique incident light from the upper layer side of the thin film transistor, particularly in the case of strong incident light as in a projector application. In addition, light omission due to oblique incident light can be effectively prevented, and oblique incident light, and also internal reflection light and multiple reflection light based on this and return light can be effectively shielded. The second capacitor electrode is connected to such a conductive upper-layer light-shielding film and is set at a fixed potential. Therefore, the storage capacitor can be constructed in a region overlapping the data line by using the upper light shielding film also as the capacitor line.

[0024]

In the aspect including the upper light-shielding film, the upper light-shielding film is stacked on the lower layer side of the data line on the substrate and the main line portion along the scanning line as viewed in plan and the main line portion from the main line portion. The data line and the thin film transistor are opened in a region where the stripe-shaped upper light-shielding film is not formed in a plan view. It may be connected through a contact hole.

[0025]

With this configuration, all of the scanning lines and the data lines are formed by the upper-layer light-shielding film formed in a stripe shape including a main line portion along the scanning line and a protruding portion protruding from the main line portion along the data line. It is possible to define the opening area of the pixel in the majority. Then, although the upper light shielding film is laminated between the data line and the thin film transistor, the data line, the thin film transistor, and the thin film are formed in a region where the upper light shielding film in the stripe shape is not formed (that is, the region beyond the protruding portion). Can be opened without any problem.

[0026]

Alternatively, in an aspect including the upper light shielding film, the upper light shielding film is laminated on the substrate on the upper layer side than the data line and is formed in a lattice shape in plan view. And the second capacitor electrode may be connected via a contact hole opened in a region where the data line is not formed in plan view.

[0027]

With this configuration, since there is no upper light shielding film between the data line and the thin film transistor, the upper light shielding film is formed in order to secure a gap for opening a contact hole for connecting the data line and the thin film transistor. It is not necessary to provide a constriction or an opening, or to form the upper light shielding film in a stripe shape, and the upper light shielding film can be formed in a lattice shape that completely covers the data lines and the scanning lines. As a result, the opening area of each pixel can be defined only by the upper light shielding film, and the light shielding performance can be further enhanced. Then, although the data line is laminated between the upper light shielding film and the second capacitor electrode, the second capacitor electrode is slightly formed from the data line formation region to the region where the data line is not formed. A contact hole connecting the upper light-shielding film and the second capacitor electrode can be opened without any problem (by projecting).

[0028]

In the aspect including the upper light-shielding film, a lower light-shielding film that covers at least the channel region of the thin film transistor when viewed from the substrate side may be further provided on the lower layer side of the thin film transistor.

[0029]

With this configuration, since the lower light shielding film covers at least the channel region of the thin film transistor when viewed from the substrate side, the channel region can be shielded against the return light from the lower layer side of the thin film transistor, and the characteristics of the thin film transistor are deteriorated due to the return light. Can be reduced. In this case, the lower light shielding film does not need to be conductive.

[0030]

In the aspect provided with both the upper-layer light-shielding film and the lower-layer light-shielding film described above, the lower-layer light-shielding film, the scanning line, the data line, and the thin film transistor are formed in the upper-layer light-shielding film as viewed in plan on the substrate. It is preferable not to protrude.

[0031]

With this configuration, incident light incident on the substrate is reflected by the upper surface of the scanning line, the data line, the thin film transistor, or the lower light shielding film that protrudes from the formation region of the upper light shielding film. Generation of internally reflected light and multiple reflected light can be effectively prevented. The return light is reflected by the lower surface of the upper light shielding film that protrudes from the lower light shielding film formation region, so that some internal reflection light and multiple reflected light are generated inside the electro-optical device, but the return light is incident light. Since the light intensity is much lower than that of the light, the adverse effect of the internal reflection and the multiple reflected light due to the return light is less than that of the incident light. Therefore, it is preferable that the lower light shielding film does not protrude from the upper light shielding film (that is, the upper light shielding film is slightly larger than the lower light shielding film).

[0032]

In another aspect of the electro-optical device according to the aspect of the invention, the storage capacitor is partially disposed in a region along the scanning line in addition to a region overlapping the data line when seen in a plan view.

[0033]

According to this aspect, the first capacitor electrode and the second capacitor electrode are formed on the substrate not only in a three-dimensionally overlapping manner on the data line but also in a region along the data line, thereby opening each pixel. It is possible to relatively increase the storage capacity while expanding the area.

[0034]

In another aspect of the electro-optical device of the present invention, the light-shielding film extends from the image display area to the outside of the image display area, and is dropped to a fixed potential outside the image display area.

[0035]

According to this aspect, the light-shielding film connected to the second capacitor electrode in the image display region extends outside the image display region and drops to a fixed potential, and thus functions well as a capacitor line. At this time, in particular, the light shielding film can be set to a fixed potential relatively easily and reliably by using a constant potential line or a constant potential source for a peripheral circuit or a drive circuit in a peripheral region outside the image display region.

[0036]

Such an operation and other advantages of the present invention will become apparent from the embodiments described below.

[0037]

DETAILED DESCRIPTION OF THE INVENTION

Hereinafter, embodiments of the present invention will be described with reference to the drawings. In each of the following embodiments, the electro-optical device of the invention is applied to a liquid crystal device.

[0038]

(First embodiment)

The configuration of the electro-optical device according to the first embodiment of the invention will be described with reference to FIGS. 1 to 5. FIG. 1 is an equivalent circuit of various elements, wirings, and the like in a plurality of pixels formed in a matrix that forms an image display region of an electro-optical device. 2 is a plan view of a plurality of adjacent pixel groups of a TFT array substrate on which data lines, scanning lines, pixel electrodes, and the like are formed, and FIG. 3 is a cross-sectional view taken along line AA ′ of FIG. 4 is a cross-sectional view taken along the line BB ′ of FIG. FIG. 5 is a plan view of the pixel of the TFT array substrate, showing the light shielding film extracted. In FIGS. 3 and 4, the scale of each layer and each member is different in order to make each layer and each member large enough to be recognized on the drawing.

[0039]

In FIG. 1, a plurality of pixels formed in a matrix that forms an image display area of the electro-optical device according to the present embodiment includes a

[0040]

In FIG. 2, a plurality of

[0041]

In addition, the

[0042]

In the present embodiment, the built-in light-shielding

[0043]

As shown in FIGS. 2 to 4, the first light-shielding

[0044]

As shown in FIG. 3, on the

[0045]

On the other hand, as shown in FIG. 4, the

[0046]

As shown in FIGS. 2 to 4, the first capacitor electrode 13-1 made of the same film as the

[0047]

The first capacitor electrode 13-1 is in surface contact with the

[0048]

The second capacitor electrode 33-1 is connected to the conductive first light-shielding

[0049]

The

[0050]

As shown in FIG. 3, the electro-optical device includes a transparent

[0051]

On the other hand, a

[0052]

The

[0053]

As shown in FIGS. 3 and 4, the

[0054]

Between the

[0055]

Further, a

[0056]

In FIG. 3, the

[0057]

As shown in FIG. 3 and FIG. 4, a first

[0058]

As described above, according to the present embodiment, the first capacitor electrode 13-1 and the second capacitor electrode 33-1 are formed on the

[0059]

In the embodiment described above, by stacking a large number of conductive layers, steps are generated in regions along the

[0060]

Further, in the embodiment described above, the

[0061]

In each of the electro-optical devices according to the first embodiment and the following embodiments, each interlayer insulating film that insulates between the conductive films is formed by TEOS (tetra-ethyl) by, for example, normal pressure, low pressure CVD, plasma CVD, or the like.・ Silicate glass films such as NSG (non-doped silicate glass) and PSG (phosphorus silicate glass), silicon nitride films and oxides using ortho silicate gas, TEB (tetraethyl boat rate) gas, etc. What is necessary is just to comprise from a silicon film etc. Moreover, the film thickness of each interlayer insulation film is about 100-1000 nm.

[0062]

Particularly in the present embodiment, since the second capacitor electrode 33-1 having a fixed potential is disposed between the first capacitor electrode 13-1 having the pixel electrode potential and the

[0063]

In the present embodiment, as described above, the first

[0064]

In the present embodiment, since the first

[0065]

(Second Embodiment)

Next, a second embodiment of the electro-optical device of the invention will be described with reference to FIG. FIG. 6 is a plan view of a pixel of the TFT array substrate on which data lines, scanning lines, pixel electrodes and the like are formed. In FIG. 6, the same components as those in FIGS. 2 to 5 (first embodiment) are denoted by the same reference numerals, and the description thereof is omitted.

[0066]

As shown in FIG. 6, in the second embodiment, as compared with the first embodiment, the storage capacitor 70-2 as another example of the

[0067]

Therefore, according to the second embodiment, in addition to forming the first capacitor electrode 13-2 and the second capacitor electrode 33-2 on the

[0068]

(Third embodiment)

Next, a third embodiment of the electro-optical device according to the invention will be described with reference to FIGS. FIG. 7 is a plan view of a pixel on the TFT array substrate on which data lines, scanning lines, pixel electrodes, and the like are formed. FIG. 8 is a cross-sectional view taken along line AA ′ of FIG. FIG. 8 is a cross-sectional view taken along the line BB ′ of FIG. In FIGS. 8 and 9, the scales of the layers and the members are different from each other in order to make the layers and the members large enough to be recognized on the drawings. In FIGS. 7 to 9, the same components as those in FIGS. 2 to 5 (first embodiment) are denoted by the same reference numerals, and the description thereof is omitted.

[0069]

As shown in FIGS. 7 to 9, in the third embodiment, a conductive built-in light shielding film on the upper side of the

[0070]

As described above, according to the third embodiment, the first capacitor electrode 13-3 and the second capacitor electrode 33-3 are three-dimensionally superimposed on the

[0071]

In the third embodiment, the built-in

[0072]

In the present embodiment, since the built-in

[0073]

(Fourth embodiment)

Next, a fourth embodiment of the electro-optical device of the invention will be described with reference to FIG. FIG. 10 is a plan view of a pixel on the TFT array substrate on which data lines, scanning lines, pixel electrodes and the like are formed. In FIG. 10, the same components as those in FIGS. 2 to 5 (first embodiment) or FIGS. 7 to 9 (third embodiment) are denoted by the same reference numerals, and the description thereof is omitted. .

[0074]

As shown in FIG. 10, in the fourth embodiment, as compared with the third embodiment, the storage capacitor 70-4 as another example of the

[0075]

Therefore, according to the fourth embodiment, in addition to forming the first capacitor electrode 13-4 and the second capacitor electrode 33-4 on the

[0076]

Here, the electrical connection between the first capacitor electrode 13 (13-1 to 13-4) and the high-

[0077]

As shown in FIG. 11A, the first capacitor electrode 13 (13-1 to 13-4) is electrically connected to the high-

[0078]

However, as shown in FIG. 11 (b), by forming a contact hole BCNT ′ in the insulating thin film 2 (gate insulating film) before forming the

[0079]

Alternatively, as shown in FIG. 11C, the contact hole BCNT ′ is formed in the insulating thin film 2 (gate insulating film) before the

[0080]

(Overall configuration of electro-optical device)

The overall configuration of the electro-optical device according to each embodiment configured as described above will be described with reference to FIGS. 12 is a plan view of the

[0081]

In FIG. 12, a sealing

[0082]

On the

[0083]

In each of the embodiments described above with reference to FIGS. 1 to 13, instead of providing the data line driving

[0084]

Since the electro-optical device in each embodiment described above is applied to a projector, three electro-optical devices are respectively used as RGB light valves, and each light valve has a dichroic mirror for RGB color separation. The light of each color resolved through the light enters as projection light. Therefore, in each embodiment, the

[0085]

The present invention is not limited to each of the above-described embodiments, and can be appropriately changed without departing from the spirit or concept of the invention that can be read from the claims and the entire specification. An optical device is also included in the technical scope of the present invention.

[Brief description of the drawings]

FIG. 1 is an equivalent circuit of various elements, wirings, and the like provided in a plurality of matrix pixels that form an image display region in an electro-optical device according to a first embodiment of the invention.

FIG. 2 is a plan view of a plurality of pixel groups adjacent to each other on a TFT array substrate on which data lines, scanning lines, pixel electrodes, and the like are formed in the electro-optical device according to the first embodiment.

FIG. 3 is a cross-sectional view taken along the line A-A ′ of FIG. 2;

4 is a cross-sectional view taken along line B-B ′ of FIG. 2;

FIG. 5 is a plan view of a pixel of a TFT array substrate in which a light shielding film in the first embodiment is extracted and shown.

6 is a plan view of a plurality of pixel groups adjacent to each other on a TFT array substrate on which data lines, scanning lines, pixel electrodes, and the like are formed in the electro-optical device according to the second embodiment. FIG.

7 is a plan view of a plurality of pixel groups adjacent to each other on a TFT array substrate on which data lines, scanning lines, pixel electrodes, and the like are formed in the electro-optical device according to the third embodiment. FIG.

FIG. 8 is a cross-sectional view taken along the line A-A ′ of FIG.

9 is a cross-sectional view taken along line B-B ′ of FIG.

FIG. 10 is a plan view of a plurality of adjacent pixel groups on a TFT array substrate on which data lines, scanning lines, pixel electrodes, and the like are formed in the electro-optical device of the fourth embodiment.

11A and 11B are a cross-sectional view showing an example of electrical connection between the first capacitor electrode and the high-concentration drain region (FIG. 11A), and cross-sectional views showing other examples (FIGS. 11B and 11C). )).

FIG. 12 is a plan view of a TFT array substrate in the electro-optical device according to each embodiment as viewed from the counter substrate side together with the components formed on the TFT array substrate.

13 is a cross-sectional view taken along the line H-H ′ of FIG.

[Explanation of symbols]

1a ... Semiconductor layer

1a '... channel region

1b ... low concentration source region

1c: low concentration drain region

1d ... High concentration source region

1e ... High concentration drain region

2. Insulating thin film (gate insulating film)

3a ... scan line

4. First interlayer insulating film

6a ... Data line

7. Second interlayer insulating film

8 ... Third interlayer insulating film

9a: Pixel electrode

10 ... TFT array substrate

11a ... 1st light shielding film

12 ... Underlying insulating film

13 (13-1 to 13-4): First capacitor electrode

16 ... Alignment film

20 ... Counter substrate

21 ... Counter electrode

22 ... Alignment film

23. Second light shielding film

30 ... TFT

33 (33-1 to 33-4) ... second capacitor electrode

34 ... Barrier layer

41, 41 ', 43, 43' ... Built-in light shielding film

50 ... Liquid crystal layer

70 (70-1 to 70-4) ... Storage capacity

300 ... capacity line

SCNT, BCNT, ICNT, ACNT, BMCNT ... Contact hole

Claims (11)

相交差する走査線及びデータ線と、

前記走査線及びデータ線の交差に対応して設けられた薄膜トランジスタと、

絶縁膜を介して前記薄膜トランジスタの半導体層と異なる層に設けられた中間導電層と、

前記薄膜トランジスタに前記中間導電層を中継して接続された画素電極と、

平面的に見て前記データ線に重なる領域に配置された蓄積容量と、

画素の開口領域を少なくとも部分的に規定すると共に前記走査線と重なるように形成された導電性の遮光膜とを備えており、

前記蓄積容量は、前記薄膜トランジスタに電気的に接続されると共に平面的に見て前記遮光膜と重なる部分と前記遮光膜から前記開口領域に向かって突出する突出部とを有する第1容量電極と、前記第1容量電極に誘電体膜を介して対向配置されると共に前記遮光膜に接続されて固定電位とされる第2容量電極とを備え、

前記中間導電層は、前記突出部において前記第1容量電極と電気的に接続される

ことを特徴とする電気光学装置。On the board

Crossing scan lines and data lines;

A thin film transistor provided corresponding to the intersection of the scanning line and the data line;

An intermediate conductive layer provided in a layer different from the semiconductor layer of the thin film transistor via an insulating film;

A pixel electrode connected to relay the intermediate conductive layer on the thin film transistor,

A storage capacitor disposed in a region overlapping the data line in plan view;

A conductive light shielding film that at least partially defines an opening area of the pixel and is formed so as to overlap the scanning line;

The storage capacitor is electrically connected to the thin film transistor and has a first capacitor electrode having a portion overlapping the light shielding film in plan view and a protruding portion protruding from the light shielding film toward the opening region ; A second capacitor electrode disposed opposite to the first capacitor electrode via a dielectric film and connected to the light-shielding film to have a fixed potential;

The electro-optical device, wherein the intermediate conductive layer is electrically connected to the first capacitor electrode at the protruding portion.

該下層遮光膜と前記第2容量電極とは、平面的に見て前記第1容量電極の形成されていない領域に開孔されたコンタクトホールを介して接続されていることを特徴とする請求項1又は2に記載の電気光学装置。The light shielding film is composed of a lower shielding film of the conductive covering at least the channel region of and the thin film transistor is arranged on the lower layer side of the thin film tiger Njisuta on the substrate when viewed from the substrate side,

The lower-layer light-shielding film and the second capacitor electrode are connected to each other through a contact hole formed in a region where the first capacitor electrode is not formed in plan view. The electro-optical device according to 1 or 2.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000122601A JP4599655B2 (en) | 2000-04-24 | 2000-04-24 | Electro-optical device and projector |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000122601A JP4599655B2 (en) | 2000-04-24 | 2000-04-24 | Electro-optical device and projector |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010117377A Division JP5158131B2 (en) | 2010-05-21 | 2010-05-21 | Electro-optical device and projector |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001305580A JP2001305580A (en) | 2001-10-31 |

| JP2001305580A5 JP2001305580A5 (en) | 2007-02-01 |

| JP4599655B2 true JP4599655B2 (en) | 2010-12-15 |

Family

ID=18633057

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000122601A Expired - Fee Related JP4599655B2 (en) | 2000-04-24 | 2000-04-24 | Electro-optical device and projector |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4599655B2 (en) |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100490061B1 (en) * | 2002-01-16 | 2005-05-17 | 일진디스플레이(주) | Liquid crystal display having improved aperture ratio |

| JP3788387B2 (en) * | 2002-05-10 | 2006-06-21 | セイコーエプソン株式会社 | Electro-optical device and method of manufacturing electro-optical device |

| JP4019868B2 (en) | 2002-09-11 | 2007-12-12 | セイコーエプソン株式会社 | Electro-optical device and electronic apparatus |

| JP3772888B2 (en) * | 2003-05-02 | 2006-05-10 | セイコーエプソン株式会社 | Electro-optical device and electronic apparatus |

| JP4016955B2 (en) * | 2003-05-02 | 2007-12-05 | セイコーエプソン株式会社 | ELECTRO-OPTICAL DEVICE, MANUFACTURING METHOD THEREOF, AND ELECTRONIC DEVICE |

| CN100480826C (en) * | 2003-05-02 | 2009-04-22 | 精工爱普生株式会社 | Electro-optic device and electronic equipment |

| JP3767607B2 (en) | 2003-05-02 | 2006-04-19 | セイコーエプソン株式会社 | Electro-optical device and electronic apparatus |

| JP2004347838A (en) * | 2003-05-22 | 2004-12-09 | Seiko Epson Corp | Electro-optical apparatus, electronic device, and projection display device |

| US7309922B2 (en) * | 2003-10-20 | 2007-12-18 | Samsun Electronics Co., Ltd. | Lower substrate, display apparatus having the same and method of manufacturing the same |

| JP4686122B2 (en) * | 2003-11-28 | 2011-05-18 | 東芝モバイルディスプレイ株式会社 | Active matrix display device and manufacturing method thereof |

| JP2005222019A (en) * | 2004-01-07 | 2005-08-18 | Seiko Epson Corp | Electrooptical device and electronic equipment, and method for manufacturing electrooptical device |

| KR101058457B1 (en) * | 2004-08-09 | 2011-08-24 | 엘지디스플레이 주식회사 | LCD and its manufacturing method |

| JP2006303449A (en) | 2005-04-21 | 2006-11-02 | Samsung Sdi Co Ltd | Active matrix circuit substrate, method for manufacturing the same, and active matrix display equipped with the same |

| DE602005005451T2 (en) * | 2005-04-21 | 2009-04-02 | Samsung Sdi Germany Gmbh | Active matrix circuit, active matrix display and their manufacturing process |

| JP4245008B2 (en) | 2006-05-10 | 2009-03-25 | セイコーエプソン株式会社 | Electro-optical device substrate, electro-optical device, and electronic apparatus |

| KR101304902B1 (en) * | 2006-11-24 | 2013-09-05 | 삼성디스플레이 주식회사 | Liquid crystal display |

| JP5258277B2 (en) | 2006-12-26 | 2013-08-07 | 株式会社半導体エネルギー研究所 | Liquid crystal display |

| JP6550912B2 (en) * | 2015-05-11 | 2019-07-31 | 凸版印刷株式会社 | Liquid crystal display device and head-up display device |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000010121A (en) * | 1998-06-23 | 2000-01-14 | Seiko Epson Corp | Liquid crystal device and projection type display device |

-

2000

- 2000-04-24 JP JP2000122601A patent/JP4599655B2/en not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000010121A (en) * | 1998-06-23 | 2000-01-14 | Seiko Epson Corp | Liquid crystal device and projection type display device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001305580A (en) | 2001-10-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3591513B2 (en) | Electro-optical device and projector | |

| JP4599655B2 (en) | Electro-optical device and projector | |

| JP3731447B2 (en) | Electro-optical device and manufacturing method thereof | |

| JP3821067B2 (en) | Electro-optical device and electronic apparatus | |

| JP3743291B2 (en) | Electro-optical device and projector | |

| JP3608531B2 (en) | Electro-optical device and projection display device | |

| JP3937721B2 (en) | Electro-optical device, manufacturing method thereof, and projector | |

| JP3931547B2 (en) | Electro-optical device and manufacturing method thereof | |

| JP4023522B2 (en) | Electro-optical device and projector | |

| JP4123245B2 (en) | Electro-optical device and electronic apparatus | |

| JP4496600B2 (en) | Electro-optical device and projector | |

| JP3849434B2 (en) | Electro-optical device and projection display device | |

| JP3979010B2 (en) | Electro-optical device and projector | |

| JP3969439B2 (en) | Electro-optic device | |

| JP5158131B2 (en) | Electro-optical device and projector | |

| JP3982183B2 (en) | Electro-optical device and projection display device | |

| JP4147747B2 (en) | Electro-optical device and projector | |

| JP3965935B2 (en) | Electro-optical device and projection display device | |

| JP3736330B2 (en) | Electro-optic device | |

| JP4023107B2 (en) | Electro-optical device and electronic apparatus including the same | |

| JP3731460B2 (en) | Electro-optical device and projector | |

| JP4509463B2 (en) | Electro-optical device and electronic apparatus | |

| JP2004109988A (en) | Electro-optic apparatus and electronic appliance | |

| JP4066607B2 (en) | Electro-optical device and projector | |

| JP4063260B2 (en) | Electro-optical device and projection display device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061204 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061204 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090818 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090825 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091023 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100323 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100521 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100831 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100913 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131008 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |