JP4522904B2 - Method for manufacturing semiconductor device - Google Patents

Method for manufacturing semiconductor device Download PDFInfo

- Publication number

- JP4522904B2 JP4522904B2 JP2005114330A JP2005114330A JP4522904B2 JP 4522904 B2 JP4522904 B2 JP 4522904B2 JP 2005114330 A JP2005114330 A JP 2005114330A JP 2005114330 A JP2005114330 A JP 2005114330A JP 4522904 B2 JP4522904 B2 JP 4522904B2

- Authority

- JP

- Japan

- Prior art keywords

- gate electrode

- electrode layer

- insulating film

- semiconductor layer

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 166

- 239000004065 semiconductor Substances 0.000 title claims description 152

- 238000004519 manufacturing process Methods 0.000 title claims description 49

- 239000010410 layer Substances 0.000 claims description 402

- 239000012535 impurity Substances 0.000 claims description 186

- 238000010438 heat treatment Methods 0.000 claims description 34

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 32

- 239000011229 interlayer Substances 0.000 claims description 32

- 229910052760 oxygen Inorganic materials 0.000 claims description 32

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 31

- 239000001301 oxygen Substances 0.000 claims description 31

- 230000002829 reductive effect Effects 0.000 claims description 28

- 239000012212 insulator Substances 0.000 claims description 27

- 239000012298 atmosphere Substances 0.000 claims description 23

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 20

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 20

- 230000015572 biosynthetic process Effects 0.000 claims description 19

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 17

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 16

- 229910052757 nitrogen Inorganic materials 0.000 claims description 16

- 238000005530 etching Methods 0.000 claims description 12

- 239000011810 insulating material Substances 0.000 claims description 6

- 239000010408 film Substances 0.000 description 195

- 239000000758 substrate Substances 0.000 description 83

- 239000000203 mixture Substances 0.000 description 72

- 239000000463 material Substances 0.000 description 50

- 239000004973 liquid crystal related substance Substances 0.000 description 45

- 239000004020 conductor Substances 0.000 description 41

- 239000010409 thin film Substances 0.000 description 32

- 238000005401 electroluminescence Methods 0.000 description 30

- 230000008569 process Effects 0.000 description 29

- 238000002347 injection Methods 0.000 description 24

- 239000007924 injection Substances 0.000 description 24

- 239000007789 gas Substances 0.000 description 23

- 229910052710 silicon Inorganic materials 0.000 description 19

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 17

- 239000010703 silicon Substances 0.000 description 17

- 239000010936 titanium Substances 0.000 description 16

- 239000007788 liquid Substances 0.000 description 15

- 239000011159 matrix material Substances 0.000 description 15

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 14

- 238000007599 discharging Methods 0.000 description 14

- 229910052782 aluminium Inorganic materials 0.000 description 13

- 238000010586 diagram Methods 0.000 description 13

- 238000012545 processing Methods 0.000 description 13

- 239000003990 capacitor Substances 0.000 description 12

- 229910052739 hydrogen Inorganic materials 0.000 description 12

- 239000001257 hydrogen Substances 0.000 description 12

- 230000005236 sound signal Effects 0.000 description 12

- 238000001035 drying Methods 0.000 description 11

- 239000003550 marker Substances 0.000 description 11

- 239000012044 organic layer Substances 0.000 description 11

- 239000002356 single layer Substances 0.000 description 11

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 10

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 10

- 229910052796 boron Inorganic materials 0.000 description 10

- 229910052799 carbon Inorganic materials 0.000 description 10

- 239000010949 copper Substances 0.000 description 10

- 239000011521 glass Substances 0.000 description 10

- 239000002245 particle Substances 0.000 description 10

- 230000002940 repellent Effects 0.000 description 10

- 239000005871 repellent Substances 0.000 description 10

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 9

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 9

- 230000006870 function Effects 0.000 description 9

- 229910052751 metal Inorganic materials 0.000 description 9

- 239000002184 metal Substances 0.000 description 9

- 150000002894 organic compounds Chemical class 0.000 description 9

- 229910052698 phosphorus Inorganic materials 0.000 description 9

- 239000011574 phosphorus Substances 0.000 description 9

- 229920001721 polyimide Polymers 0.000 description 9

- 239000002904 solvent Substances 0.000 description 9

- 239000004642 Polyimide Substances 0.000 description 8

- 229910052785 arsenic Inorganic materials 0.000 description 8

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 8

- 238000002161 passivation Methods 0.000 description 8

- 238000000059 patterning Methods 0.000 description 8

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 8

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 7

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 7

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 7

- 230000009977 dual effect Effects 0.000 description 7

- -1 for example Inorganic materials 0.000 description 7

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 7

- 238000003384 imaging method Methods 0.000 description 7

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- 230000003321 amplification Effects 0.000 description 6

- 238000004380 ashing Methods 0.000 description 6

- 125000004429 atom Chemical group 0.000 description 6

- 229910052802 copper Inorganic materials 0.000 description 6

- 238000005468 ion implantation Methods 0.000 description 6

- XEEYBQQBJWHFJM-UHFFFAOYSA-N iron Substances [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 6

- 229910052759 nickel Inorganic materials 0.000 description 6

- 238000003199 nucleic acid amplification method Methods 0.000 description 6

- 238000005192 partition Methods 0.000 description 6

- 229920005989 resin Polymers 0.000 description 6

- 239000011347 resin Substances 0.000 description 6

- 229910021332 silicide Inorganic materials 0.000 description 6

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 6

- 125000006850 spacer group Chemical group 0.000 description 6

- 229910052718 tin Inorganic materials 0.000 description 6

- 239000011787 zinc oxide Substances 0.000 description 6

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 5

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 5

- 229910003087 TiOx Inorganic materials 0.000 description 5

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 5

- 229910052787 antimony Inorganic materials 0.000 description 5

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 5

- 230000004888 barrier function Effects 0.000 description 5

- 239000011248 coating agent Substances 0.000 description 5

- 238000010304 firing Methods 0.000 description 5

- 230000005525 hole transport Effects 0.000 description 5

- 229910010272 inorganic material Inorganic materials 0.000 description 5

- 229910052749 magnesium Inorganic materials 0.000 description 5

- 239000011777 magnesium Substances 0.000 description 5

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 5

- 229910052709 silver Inorganic materials 0.000 description 5

- HLLICFJUWSZHRJ-UHFFFAOYSA-N tioxidazole Chemical compound CCCOC1=CC=C2N=C(NC(=O)OC)SC2=C1 HLLICFJUWSZHRJ-UHFFFAOYSA-N 0.000 description 5

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 4

- 238000001994 activation Methods 0.000 description 4

- 239000000460 chlorine Substances 0.000 description 4

- 239000002270 dispersing agent Substances 0.000 description 4

- 229910052738 indium Inorganic materials 0.000 description 4

- 239000005001 laminate film Substances 0.000 description 4

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 4

- 239000012299 nitrogen atmosphere Substances 0.000 description 4

- 125000000962 organic group Chemical group 0.000 description 4

- 238000009832 plasma treatment Methods 0.000 description 4

- 239000000565 sealant Substances 0.000 description 4

- 239000004332 silver Substances 0.000 description 4

- 238000004528 spin coating Methods 0.000 description 4

- 239000011701 zinc Substances 0.000 description 4

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 3

- XEKOWRVHYACXOJ-UHFFFAOYSA-N Ethyl acetate Chemical compound CCOC(C)=O XEKOWRVHYACXOJ-UHFFFAOYSA-N 0.000 description 3

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 3

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 3

- 239000004952 Polyamide Substances 0.000 description 3

- 229910003902 SiCl 4 Inorganic materials 0.000 description 3

- 230000004913 activation Effects 0.000 description 3

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 3

- 239000011230 binding agent Substances 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 238000000354 decomposition reaction Methods 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- 239000010419 fine particle Substances 0.000 description 3

- 239000011737 fluorine Substances 0.000 description 3

- 229910052731 fluorine Inorganic materials 0.000 description 3

- 229910052732 germanium Inorganic materials 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- 229920006015 heat resistant resin Polymers 0.000 description 3

- 239000002784 hot electron Substances 0.000 description 3

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 3

- 239000011147 inorganic material Substances 0.000 description 3

- 229910052741 iridium Inorganic materials 0.000 description 3

- 229910052742 iron Inorganic materials 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 150000002739 metals Chemical class 0.000 description 3

- 239000002105 nanoparticle Substances 0.000 description 3

- 239000010955 niobium Substances 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- 239000011368 organic material Substances 0.000 description 3

- 239000003960 organic solvent Substances 0.000 description 3

- JMANVNJQNLATNU-UHFFFAOYSA-N oxalonitrile Chemical compound N#CC#N JMANVNJQNLATNU-UHFFFAOYSA-N 0.000 description 3

- 229910052763 palladium Inorganic materials 0.000 description 3

- 239000011295 pitch Substances 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 229920002647 polyamide Polymers 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- 230000002441 reversible effect Effects 0.000 description 3

- 239000010948 rhodium Substances 0.000 description 3

- 239000003566 sealing material Substances 0.000 description 3

- 239000000243 solution Substances 0.000 description 3

- 229920003002 synthetic resin Polymers 0.000 description 3

- 239000000057 synthetic resin Substances 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 229910052725 zinc Inorganic materials 0.000 description 3

- 229910052726 zirconium Inorganic materials 0.000 description 3

- WUPHOULIZUERAE-UHFFFAOYSA-N 3-(oxolan-2-yl)propanoic acid Chemical compound OC(=O)CCC1CCCO1 WUPHOULIZUERAE-UHFFFAOYSA-N 0.000 description 2

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 2

- 229910017073 AlLi Inorganic materials 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- UQSXHKLRYXJYBZ-UHFFFAOYSA-N Iron oxide Chemical compound [Fe]=O UQSXHKLRYXJYBZ-UHFFFAOYSA-N 0.000 description 2

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 2

- ZLMJMSJWJFRBEC-UHFFFAOYSA-N Potassium Chemical compound [K] ZLMJMSJWJFRBEC-UHFFFAOYSA-N 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- 229910002808 Si–O–Si Inorganic materials 0.000 description 2

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- 125000000217 alkyl group Chemical group 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 229910052980 cadmium sulfide Inorganic materials 0.000 description 2

- 229910052791 calcium Inorganic materials 0.000 description 2

- 239000011575 calcium Substances 0.000 description 2

- 239000006229 carbon black Substances 0.000 description 2

- 239000012159 carrier gas Substances 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 230000006854 communication Effects 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 235000019441 ethanol Nutrition 0.000 description 2

- 238000001704 evaporation Methods 0.000 description 2

- 125000001153 fluoro group Chemical group F* 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 229910001385 heavy metal Inorganic materials 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- 238000005984 hydrogenation reaction Methods 0.000 description 2

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 2

- 150000002484 inorganic compounds Chemical class 0.000 description 2

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 2

- 238000010030 laminating Methods 0.000 description 2

- 229910052744 lithium Inorganic materials 0.000 description 2

- 239000011572 manganese Substances 0.000 description 2

- 125000002496 methyl group Chemical group [H]C([H])([H])* 0.000 description 2

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 2

- 238000007645 offset printing Methods 0.000 description 2

- AHLBNYSZXLDEJQ-FWEHEUNISA-N orlistat Chemical compound CCCCCCCCCCC[C@H](OC(=O)[C@H](CC(C)C)NC=O)C[C@@H]1OC(=O)[C@H]1CCCCCC AHLBNYSZXLDEJQ-FWEHEUNISA-N 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 2

- 125000001997 phenyl group Chemical group [H]C1=C([H])C([H])=C(*)C([H])=C1[H] 0.000 description 2

- 230000001699 photocatalysis Effects 0.000 description 2

- 229910052700 potassium Inorganic materials 0.000 description 2

- 239000011591 potassium Substances 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 238000004151 rapid thermal annealing Methods 0.000 description 2

- 229910052703 rhodium Inorganic materials 0.000 description 2

- 229910052706 scandium Inorganic materials 0.000 description 2

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 2

- 238000007650 screen-printing Methods 0.000 description 2

- 238000007789 sealing Methods 0.000 description 2

- 229910052708 sodium Inorganic materials 0.000 description 2

- 239000011734 sodium Substances 0.000 description 2

- 239000007921 spray Substances 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- 239000002699 waste material Substances 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- 229910001928 zirconium oxide Inorganic materials 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 229910021364 Al-Si alloy Inorganic materials 0.000 description 1

- DKPFZGUDAPQIHT-UHFFFAOYSA-N Butyl acetate Natural products CCCCOC(C)=O DKPFZGUDAPQIHT-UHFFFAOYSA-N 0.000 description 1

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 1

- KZBUYRJDOAKODT-UHFFFAOYSA-N Chlorine Chemical compound ClCl KZBUYRJDOAKODT-UHFFFAOYSA-N 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- 229910000799 K alloy Inorganic materials 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- 241001676573 Minium Species 0.000 description 1

- 229910000990 Ni alloy Inorganic materials 0.000 description 1

- 229920002292 Nylon 6 Polymers 0.000 description 1

- 229920002302 Nylon 6,6 Polymers 0.000 description 1

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 239000006087 Silane Coupling Agent Substances 0.000 description 1

- 229910020776 SixNy Inorganic materials 0.000 description 1

- 229910020781 SixOy Inorganic materials 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- GDFCWFBWQUEQIJ-UHFFFAOYSA-N [B].[P] Chemical compound [B].[P] GDFCWFBWQUEQIJ-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- UQDKMJGHCDDRBE-UHFFFAOYSA-N [Sn]=O.[In].[Si]=O Chemical compound [Sn]=O.[In].[Si]=O UQDKMJGHCDDRBE-UHFFFAOYSA-N 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 150000001298 alcohols Chemical class 0.000 description 1

- 150000004645 aluminates Chemical class 0.000 description 1

- QQHJESKHUUVSIC-UHFFFAOYSA-N antimony lead Chemical compound [Sb].[Pb] QQHJESKHUUVSIC-UHFFFAOYSA-N 0.000 description 1

- 229910000410 antimony oxide Inorganic materials 0.000 description 1

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 1

- 230000007175 bidirectional communication Effects 0.000 description 1

- QDWJUBJKEHXSMT-UHFFFAOYSA-N boranylidynenickel Chemical compound [Ni]#B QDWJUBJKEHXSMT-UHFFFAOYSA-N 0.000 description 1

- 239000005380 borophosphosilicate glass Substances 0.000 description 1

- 229910052793 cadmium Inorganic materials 0.000 description 1

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 description 1

- AQCDIIAORKRFCD-UHFFFAOYSA-N cadmium selenide Chemical compound [Cd]=[Se] AQCDIIAORKRFCD-UHFFFAOYSA-N 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000003054 catalyst Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 230000008602 contraction Effects 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 150000002148 esters Chemical class 0.000 description 1

- 238000011156 evaluation Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 229910021397 glassy carbon Inorganic materials 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 1

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(iv) oxide Chemical compound O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- FUZZWVXGSFPDMH-UHFFFAOYSA-M hexanoate Chemical compound CCCCCC([O-])=O FUZZWVXGSFPDMH-UHFFFAOYSA-M 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 239000012948 isocyanate Substances 0.000 description 1

- 150000002513 isocyanates Chemical class 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- URLJKFSTXLNXLG-UHFFFAOYSA-N niobium(5+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Nb+5].[Nb+5] URLJKFSTXLNXLG-UHFFFAOYSA-N 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 238000010943 off-gassing Methods 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- VTRUBDSFZJNXHI-UHFFFAOYSA-N oxoantimony Chemical compound [Sb]=O VTRUBDSFZJNXHI-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 239000011941 photocatalyst Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 238000002294 plasma sputter deposition Methods 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229920006122 polyamide resin Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920000098 polyolefin Polymers 0.000 description 1

- 239000011148 porous material Substances 0.000 description 1

- BITYAPCSNKJESK-UHFFFAOYSA-N potassiosodium Chemical compound [Na].[K] BITYAPCSNKJESK-UHFFFAOYSA-N 0.000 description 1

- 238000007781 pre-processing Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 229910052702 rhenium Inorganic materials 0.000 description 1

- WUAPFZMCVAUBPE-UHFFFAOYSA-N rhenium atom Chemical compound [Re] WUAPFZMCVAUBPE-UHFFFAOYSA-N 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 1

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical class [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 1

- 239000010944 silver (metal) Substances 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 description 1

- 125000001424 substituent group Chemical group 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- 229910052714 tellurium Inorganic materials 0.000 description 1

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 1

- PPMWWXLUCOODDK-UHFFFAOYSA-N tetrafluorogermane Chemical compound F[Ge](F)(F)F PPMWWXLUCOODDK-UHFFFAOYSA-N 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 239000004408 titanium dioxide Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- ZNOKGRXACCSDPY-UHFFFAOYSA-N tungsten trioxide Chemical compound O=[W](=O)=O ZNOKGRXACCSDPY-UHFFFAOYSA-N 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

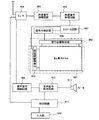

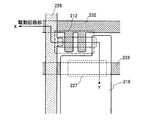

Images

Landscapes

- Liquid Crystal (AREA)

- Electroluminescent Light Sources (AREA)

- Electrodes Of Semiconductors (AREA)

- Thin Film Transistor (AREA)

Description

本発明は、大面積ガラス基板上に形成したトランジスタ等の能動素子、及び該能動素子を含む液晶表示装置(以下「LCD」ともいう。)及びEL表示装置並びにそれらの製造方法に関する。特に、インクジェット法に代表される液滴吐出法を用いた薄膜トランジスタ、液晶表示装置、EL表示装置及びその作製方法に関するものである。 The present invention relates to an active element such as a transistor formed over a large-area glass substrate, a liquid crystal display device (hereinafter also referred to as “LCD”) and an EL display device including the active element, and a method for manufacturing the same. In particular, the present invention relates to a thin film transistor, a liquid crystal display device, an EL display device, and a manufacturing method thereof using a droplet discharge method typified by an inkjet method.

従来、ガラス基板上の薄膜トランジスタ(以下「TFT」ともいう。)によって構成される、所謂アクティブマトリクス駆動方式の液晶表示パネルは、半導体集積回路の製造技術と同様に、フォトマスクを使った光露光工程により、各種薄膜をパターニングすることにより製造されてきた。 Conventionally, a so-called active matrix liquid crystal display panel composed of thin film transistors (hereinafter also referred to as “TFTs”) on a glass substrate is a light exposure process using a photomask, as in the manufacturing technology of a semiconductor integrated circuit. Thus, it has been manufactured by patterning various thin films.

これまで、一枚のマザーガラス基板から複数の液晶表示パネルを切り出して、大量生産を効率良く行う生産技術が採用されてきた。マザーガラス基板のサイズは、1990年初頭における第1世代の300×400mmから、2000年には第4世代となり680×880mm若しくは730×920mmへと大型化して、一枚の基板から多数の表示パネルが取れるように生産技術が進歩してきた。 Until now, a production technique has been adopted in which a plurality of liquid crystal display panels are cut out from a single mother glass substrate and mass production is efficiently performed. The size of the mother glass substrate was increased from 300 x 400 mm of the first generation in early 1990 to the fourth generation in 2000 and increased to 680 x 880 mm or 730 x 920 mm. Production technology has progressed so that

ガラス基板若しくは表示パネルのサイズが小さい場合には、露光装置により比較的簡便にパターニング処理を行うことが可能であったが、基板サイズが大型化するにつれ、1回の露光処理で表示パネルの全面を同時に処理することが不可能となっていた。その結果、フォトレジストが塗布された領域を複数の領域に分割して、所定のブロック領域毎に露光処理を行い、順次それを繰り返して基板全面の露光を行う方法などが開発されてきた(例えば、特許文献1参照。)。 When the size of the glass substrate or the display panel is small, the patterning process can be performed relatively easily by the exposure apparatus. However, as the substrate size increases, the entire surface of the display panel can be obtained by a single exposure process. Cannot be processed simultaneously. As a result, a method has been developed in which a region coated with a photoresist is divided into a plurality of regions, an exposure process is performed for each predetermined block region, and the entire substrate is exposed by sequentially repeating the exposure process (for example, , See Patent Document 1).

また、アクティブマトリクス型のLCDやEL表示装置に用いられる、複数のTFTからなるアクティブマトリクス基板を形成するにあたり、TFTのドレイン領域の端部に集中する電界を緩和し、所謂ホットキャリア(ホットエレクトロン又はホットホール)効果を抑制するために、ソース、ドレイン領域の端部に形成された比較的低濃度の不純物領域(LDD領域;Lightly Doped Drain Regions)を設ける技術が用いられている(例えば、特許文献2参照。)。

しかしながら、ガラス基板のサイズは、第5世代で1000×1200mm若しくは1100×1300mmへとさらに大型化し、第6世代では1500×1800mm、第7世代では2000×2200mm、第8世代では2500×3000mm級、若しくはそれ以上のサイズが想定されるにつけ、従来のパターニング方法のみによるプロセスでは、生産性良く、低コストで表示パネルを製造することが困難となってきた。すなわち、つなぎ露光により多数回の露光処理を行えば処理時間は増大し、基板の大型化に対応することが困難となってきた。 However, the size of the glass substrate is further increased to 1000 × 1200 mm or 1100 × 1300 mm in the fifth generation, 1500 × 1800 mm in the sixth generation, 2000 × 2200 mm in the seventh generation, 2500 × 3000 mm class in the eighth generation, In addition, when a larger size is assumed, it is difficult to manufacture a display panel with high productivity and low cost by a process using only a conventional patterning method. That is, if exposure processing is performed many times by continuous exposure, the processing time increases, and it has become difficult to cope with an increase in the size of the substrate.

また、TFTにLDD領域を設ける場合には、半導体膜に注入される不純物に濃度差を設けるために、マスクとなる絶縁膜を別途形成したり、ゲート電極層の形状を工夫したりする必要があり、パターニング工程が自ずと増加してしまい、工程が複雑なものとなっていた。また、工程が増加するにつれて、当然乍ら、装置稼働コストや材料コストが嵩み、また、重金属や絶縁物等を含む多量の廃液を処理することが要求されるという問題点が内在していた。 Further, in the case where an LDD region is provided in a TFT, it is necessary to separately form an insulating film serving as a mask or to devise the shape of the gate electrode layer in order to provide a concentration difference in impurities implanted into the semiconductor film. In addition, the patterning process naturally increases, and the process becomes complicated. In addition, as the number of processes increases, there are naturally problems that the operating cost of the apparatus and the material cost increase, and that it is required to process a large amount of waste liquid containing heavy metals and insulators. .

本発明は、このような状況に鑑みてなされたものであり、簡略化された工程で作製可能なTFTに代表される半導体装置、及び該半導体装置を含む液晶表示装置及びEL表示装置、並びにそれらの作製方法を提供することを目的としている。特に、LDD領域を有するTFTを用いた半導体装置、及び該半導体装置を含む液晶表示装置及びEL表示装置を簡略化された工程で提供することを目的としている。 The present invention has been made in view of such a situation, and a semiconductor device typified by a TFT that can be manufactured by a simplified process, a liquid crystal display device and an EL display device including the semiconductor device, and those It is an object to provide a manufacturing method. In particular, it is an object to provide a semiconductor device using a TFT having an LDD region, a liquid crystal display device including the semiconductor device, and an EL display device in a simplified process.

上記課題を解決するため、本発明に係る半導体装置は、チャネル領域、一対の不純物領域及び一対の低濃度不純物領域からなる半導体層と、ゲート絶縁膜を介して、前記半導体層に接して形成された、膜厚差を有する単層構造又は積層構造のゲート電極層を含むことを特徴としている。 In order to solve the above problems, a semiconductor device according to the present invention is formed in contact with a semiconductor layer including a channel region, a pair of impurity regions, and a pair of low-concentration impurity regions, and a gate insulating film. In addition, a gate electrode layer having a single layer structure or a stacked structure having a difference in film thickness is included.

そして、前記一対の低濃度不純物領域は、膜厚差を有するゲート電極層のうち、膜厚の薄い方の領域に重なって形成されていることを特徴としている。 The pair of low-concentration impurity regions are formed so as to overlap a region having a smaller thickness in the gate electrode layer having a thickness difference.

また、上記課題を解決するため、本発明に係る半導体装置の作製方法は、半導体層上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に、膜厚差を有する単層構造又は積層構造のゲート電極層を形成し、前記ゲート電極層をマスクとして、前記半導体層に不純物を導入することにより、一対の不純物領域及び一対の低濃度不純物領域を形成することを特徴としている。 In order to solve the above problems, a method for manufacturing a semiconductor device according to the present invention includes a gate insulating film formed over a semiconductor layer, and a single-layer structure or a stacked structure having a film thickness difference over the gate insulating film. A gate electrode layer is formed, and a pair of impurity regions and a pair of low-concentration impurity regions are formed by introducing impurities into the semiconductor layer using the gate electrode layer as a mask.

そして、前記一対の低濃度不純物領域は、膜厚差を有するゲート電極層のうち、膜厚の薄い方の領域に重なるように形成されることを特徴としている。 The pair of low-concentration impurity regions are formed so as to overlap with a region having a smaller thickness in the gate electrode layer having a thickness difference.

また、上記課題を解決するため、本発明に係る半導体装置の作製方法は、半導体層上にゲート絶縁膜を形成し、前記ゲート絶縁膜上にゲート電極層を形成し、前記ゲート電極層の焼成前後における幅の変化を利用して、前記半導体層中に濃度の異なる不純物元素を導入し、一対の不純物領域及び一対の低濃度不純物領域を形成することを特徴としている。 In order to solve the above problems, a method for manufacturing a semiconductor device according to the present invention includes forming a gate insulating film over a semiconductor layer, forming a gate electrode layer over the gate insulating film, and firing the gate electrode layer. A feature is that impurity elements having different concentrations are introduced into the semiconductor layer by utilizing a change in width before and after, thereby forming a pair of impurity regions and a pair of low-concentration impurity regions.

本発明は、膜厚差を有する単層構造又は積層構造のゲート電極層を含むことを特徴としているため、該ゲート電極層の膜厚差を利用して、低濃度不純物領域を容易に形成することができる。しかも、一度の不純物元素のドーピングによって、不純物領域と低濃度不純物領域を同時に作製することも可能である。これによって、ゲート電極層に低濃度不純物領域がオーバーラップした構造(Lov構造)を有するTFTのごとき半導体装置を容易に作成することができる。 Since the present invention includes a gate electrode layer having a single layer structure or a stacked structure having a film thickness difference, a low-concentration impurity region is easily formed using the film thickness difference of the gate electrode layer. be able to. In addition, the impurity region and the low-concentration impurity region can be formed simultaneously by doping the impurity element once. As a result, a semiconductor device such as a TFT having a structure in which a low concentration impurity region overlaps the gate electrode layer (Lov structure) can be easily formed.

また、本発明は、膜厚差を有する単層構造又は積層構造のゲート電極層を含むことを特徴としているが、このようなゲート電極層は、特に液滴吐出法を採用することによって、簡単に形成することができ、液滴吐出法の持つ利便性を最大限に活かすことができる。 Further, the present invention is characterized in that it includes a gate electrode layer having a single layer structure or a stacked structure having a film thickness difference. Such a gate electrode layer can be simplified by adopting a droplet discharge method in particular. The convenience of the droplet discharge method can be utilized to the maximum.

また、本発明において、液滴吐出法を積極的に採用することにより、工程を簡略化し、材料コストの削減を図ることができ、かつ、スループット、歩留まりの高い半導体装置、及びそれを含んだ発光装置(代表的には、EL表示装置)、液晶表示装置を提供することができる。特に、ガラス基板のサイズが、第6世代(1500×1800mm)、第7世代(2000×2200mm)、第8世代(2500×3000mm級)、若しくはそれ以上のサイズと拡大して行っても、生産性良く、低コストで表示パネルを製造することができる。また、導電材料としての重金属等を含む多量の廃液を処理する必要がなく、環境への配慮という観点からも、本発明は有意なものである。 In addition, in the present invention, by adopting the droplet discharge method positively, the process can be simplified, the material cost can be reduced, and a semiconductor device with high throughput and high yield, and light emission including the same A device (typically, an EL display device) or a liquid crystal display device can be provided. In particular, even if the size of the glass substrate is increased to the sixth generation (1500 × 1800 mm), the seventh generation (2000 × 2200 mm), the eighth generation (2500 × 3000 mm class), or larger, the production A display panel can be manufactured with good performance at low cost. Further, it is not necessary to treat a large amount of waste liquid containing heavy metal as a conductive material, and the present invention is significant from the viewpoint of environmental considerations.

以下、本発明の実施形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更することができる。例えば、本実施形態及び本実施例の各々を適宜組み合わせて本発明を実施することができる。 Hereinafter, embodiments of the present invention will be described with reference to the drawings. However, the present invention can be implemented in many different modes, and various changes can be made in form and details without departing from the spirit and scope of the present invention. For example, the present invention can be implemented by appropriately combining each of the present embodiment and this example.

また本発明は、積極的に液滴吐出法等のマスクレスプロセスを用いて、あらゆる半導体装置の作製方法、液晶表示装置の作製方法及びEL表示装置の作製方法を提供するものであるが、すべての工程をマスクレスプロセスによって行う必要はなく、少なくとも一部の工程にマスクレスプロセスが含まれていればよい。したがって、以下、液滴吐出法のみの工程を示した場合であっても、従来のパターニング工程をはじめとする他の作製方法に代替できるものとする。 In addition, the present invention provides a method for manufacturing any semiconductor device, a method for manufacturing a liquid crystal display device, and a method for manufacturing an EL display device by positively using a maskless process such as a droplet discharge method. It is not necessary to perform this process by a maskless process, and it is sufficient that the maskless process is included in at least a part of the processes. Therefore, hereinafter, even when only a droplet discharge method is shown, it can be replaced with another manufacturing method including a conventional patterning step.

(実施形態1)

本実施形態は、図1、2を参照して、本発明に係る半導体装置の構成及びその作製方法の一実施形態について説明する。ここでは、トップゲート型TFTを例に挙げて説明する。

(Embodiment 1)

In the present embodiment, an embodiment of a configuration of a semiconductor device and a manufacturing method thereof according to the present invention will be described with reference to FIGS. Here, a top gate TFT will be described as an example.

まず、基板100上に、半導体層101を形成する(図1(A))。半導体層101としては、アモルファス半導体、結晶性半導体、又はセミアモルファス半導体で形成する。いずれも、シリコン、シリコンゲルマニウム(SiGe)等を主成分とする半導体膜を用いることができる。また、特に、シリコンを主成分とするセミアモルファス半導体を、SAS(セミアモルファスシリコン)、又は、微結晶シリコン、マイクロクリスタルシリコンという。また、半導体層101は、CVD法やスパッタ法等によって形成することができる。なお、半導体層101の膜厚は、10〜100nmとするのが望ましい。また、シリコンウエハ、SOI基板(SIMOX基板等)のような基板を用いて、半導体層101を形成しても良い。

First, the

結晶性半導体膜を用いる場合、アモルファス半導体膜をニッケル等の触媒を含む溶液で処理した後、500〜750℃の熱結晶化工程によって結晶質シリコン半導体膜を得、さらにレーザー結晶化を行って結晶性の改善を施すことによって得ることができる。また、ジシラン(Si2H6)とフッ化ゲルマニウム(GeF4)の原料ガスとして、LPCVD(減圧CVD)法によって、多結晶半導体膜を直接形成することによっても、結晶性半導体膜を得ることができる。ガス流量比は、Si2H6/GeF4=20/0.9、成膜温度は400〜500℃、キャリアガスとしてHe又はArを用いたが、ガス流量比、成膜温度、及びキャリアガスはこれらの条件に限定されるものではない。 When a crystalline semiconductor film is used, after processing the amorphous semiconductor film with a solution containing a catalyst such as nickel, a crystalline silicon semiconductor film is obtained by a thermal crystallization process at 500 to 750 ° C., and further crystallized by laser crystallization. It can be obtained by improving the sex. A crystalline semiconductor film can also be obtained by directly forming a polycrystalline semiconductor film by LPCVD (low pressure CVD) as a source gas of disilane (Si 2 H 6 ) and germanium fluoride (GeF 4 ). it can. The gas flow rate ratio is Si 2 H 6 / GeF 4 = 20 / 0.9, the film formation temperature is 400 to 500 ° C., and He or Ar is used as the carrier gas, but the gas flow ratio, film formation temperature, and carrier gas are used. Is not limited to these conditions.

なお、基板100としては、ガラス基板、石英基板、アルミナなど絶縁物質で形成される基板、後工程の処理温度に耐え得る耐熱性を有するプラスチック基板等を用いることができる。この場合、酸化シリコン(SiOx)、窒化シリコン(SiNx)、酸化窒化シリコン(SiOxNy)(x>y)、窒化酸化シリコン(SiNxOy)(x>y)など(x、y=1、2・・・)、基板側から不純物などの拡散を防止するための下地絶縁膜を形成しておいてもよい。また、ステンレスなどの金属または半導体基板などの表面に酸化シリコンや窒化シリコンなどの絶縁膜を形成した基板なども用いることができる。

Note that as the

次に、半導体層101上にレジスト102を形成する(図1(A))。レジスト102は、ノズル120からレジスト材料を含む組成物を吐出することによって形成するのがよい。ただし、従来のように、レジスト102をパターニング形成しても良い。そして、レジスト102をマスクとして、半導体層101をエッチングすることにより、島状半導体層103を形成する(図1(B))。エッチング用ガスとしては、Cl2、BCl3、SiCl4もしくはCCl4などを代表とする塩素系ガス、CF4、SF6、NF3、CHF3などを代表とするフッ素系ガス、あるいはO2を用いたが、これらに限定されるものではない。なお、該エッチングは、大気圧プラズマを利用してもよい。

Next, a resist 102 is formed over the semiconductor layer 101 (FIG. 1A). The resist 102 is preferably formed by discharging a composition containing a resist material from the

次に、島状半導体層103上に、ゲート絶縁膜104を形成する(図1(B))。ゲート絶縁膜としては、酸化珪素(SixOy、例えばSiO2)、窒化珪素(SixNy、例えばSi3N4)、酸化窒化珪素(SiOxNy又はSiNxOy)、アルミナ(Al2O3)、酸化タンタル(Ta2O5)、酸化ランタン(La2O3)、酸化ハフニウム(HfO2)、酸化ジルコニウム(ZrO2)、シリケイト(ZrAlxOy)、アルミネート(HfAlxOy)等のあらゆる絶縁膜を利用することができる。また、これらの材料を2層以上に積層させた構造としてもよい。

Next, the

次に、ゲート絶縁膜104上に、第1の導電材料を含む組成物を、ノズル121を用いて液滴吐出法によって吐出することにより、第1のゲート電極層105を形成する(図1(C))。

Next, a first

次に、第1のゲート電極層105上に、第2の導電材料を含む組成物を、ノズル122を用いて液滴吐出法によって吐出することにより、第2のゲート電極層106を形成する(図1(D))。ここでは、図1(D)に示すように、第2のゲート電極層106は、第1のゲート電極層105よりも、幅が狭くなるようにする。また、第2のゲート電極層106は、第1のゲート電極層105よりも、幅が広くなるようし、第2のゲート電極層106が、第1のゲート電極層105を完全に覆うように形成してもよい。

Next, the second

いずれにせよ、後に説明する不純物元素のドーピング工程において、第1のゲート電極層105をスルーして、低濃度不純物領域が形成される。

In any case, a low concentration impurity region is formed through the first

なお、ここでは、第1及び第2のゲート電極層を形成するにあたり、異なるノズル121、122を用いたが、同じノズルを用いて、吐出条件を変えて第1及び第2のゲート電極層を形成しても良い。

Here,

第1及び第2のゲート電極層の膜厚については、特に制限はない。しかし、第2のゲート電極層106の幅を、第1のゲート電極層105の幅よりも狭くする場合においては、第1のゲート電極層105は、不純物を半導体層に注入しやすいようにできるだけ薄膜とし、第2のゲート電極層106は、チャネル領域に不純物が注入されないようにできるだけ厚膜としておくのが望ましい。一方、第2のゲート電極層106の幅を、第1のゲート電極層105の幅よりも広くする場合においては、その逆とすればよい。なお、チャネル領域に不純物が注入されないように、第1又は第2のゲート電極層は積層構造としても良い。

There are no particular restrictions on the thickness of the first and second gate electrode layers. However, in the case where the width of the second

なお、液滴吐出法とは、所定の導電材料を含む組成物を細孔から吐出して所定のパターンを形成する方法を意味し、代表的には、インクジェット法が挙げられるが、これに限定されるものではなく、ディスペンス法、スクリーン印刷やオフセット印刷等も含まれる。なお、以下、組成物としては、導電材料の他、半導体材料、有機半導体材料、絶縁材料(有機、無機共に含む。)、有機材料、無機材料等、液滴吐出法で吐出形成可能なあらゆる材料を含まれるものとする。ここで、有機材料、無機材料の代表的なものとして、LCDの配向膜や、カラーフィルタ、スペーサ、EL発光素子における発光層、電子輸送層、電子注入層、正孔輸送層、正孔注入層、カラーフィルタ等が挙げられる。以下、これらの材料を含む組成物を、インク、液滴、ペースト(特に、ナノ(nm)オーダーのサイズの材料を含む場合は、ナノペースト)と呼ぶことがある。 Note that the droplet discharge method means a method of forming a predetermined pattern by discharging a composition containing a predetermined conductive material from the pores, and typically includes an inkjet method, but is not limited thereto. In addition, dispensing methods, screen printing, offset printing, and the like are also included. Hereinafter, as the composition, any material that can be discharged and formed by a droplet discharge method, such as a conductive material, a semiconductor material, an organic semiconductor material, an insulating material (including both organic and inorganic), an organic material, and an inorganic material. Is included. Here, as typical organic materials and inorganic materials, LCD alignment films, color filters, spacers, light emitting layers in EL light emitting elements, electron transport layers, electron injection layers, hole transport layers, hole injection layers And color filters. Hereinafter, a composition containing these materials may be referred to as an ink, a droplet, or a paste (in particular, a nano paste when a material having a nano (nm) order size is included).

また、第1又は第2の導電材料としては、導電膜の機能に応じて種々の材料を選択することができる。代表的なものとしては、AgCu、Au、Ni、Pt、Cr、Al、W、Ta、Mo、Zn、Fe、In、Ti、Si、Ge、スズ(Sn)、パラジウム(Pd)、イリジウム(Ir)、ロジウム(Rh)、ルテニウム(Ru)、レニウム(Re)、テルル(Te)、カドミウム(Cd)、ジルコニウム(Zr)、バリウム(Ba)、アンチモン鉛、酸化スズ・アンチモン、フッ素ドープ酸化亜鉛、炭素、グラファイト、グラッシーカーボン、リチウム、ベリリウム、ナトリウム、マグネシウム、カリウム、カルシウム、スカンジウム、マンガン、ジルコニウム、ガリウム、ニオブ、ナトリウム−カリウム合金、マグネシウム/銅混合物、マグネシウム/銀混合物、マグネシウム/アルミニウム混合物、マグネシウム/インジウム混合物、アルミニウム/酸化アルミニウム混合物、リチウム/アルミニウム混合物等、ハロゲン化銀の微粒子等、又は分散性ナノ粒子、あるいは、透明導電膜として用いられる酸化インジウムスズ(ITO:Indium Tin Oxide)、ITOに珪素又は酸化珪素を含有させた導電材料(ITSO:Indium Tin Silicon Oxide)、酸化亜鉛(ZnO:Zinc Oxide)、ガリウムを添加した酸化亜鉛(GZO)、酸化インジウムに2〜20%の酸化亜鉛を混合した酸化インジウム亜鉛(IZO:Indium Zinc Oxide)、有機インジウム、有機スズ、窒化チタン、またはAl、C、Niの合金等を用いることができる。 Various materials can be selected as the first or second conductive material depending on the function of the conductive film. Typical examples include AgCu, Au, Ni, Pt, Cr, Al, W, Ta, Mo, Zn, Fe, In, Ti, Si, Ge, tin (Sn), palladium (Pd), iridium (Ir ), Rhodium (Rh), ruthenium (Ru), rhenium (Re), tellurium (Te), cadmium (Cd), zirconium (Zr), barium (Ba), antimony lead, tin / antimony oxide, fluorine-doped zinc oxide, Carbon, graphite, glassy carbon, lithium, beryllium, sodium, magnesium, potassium, calcium, scandium, manganese, zirconium, gallium, niobium, sodium-potassium alloy, magnesium / copper mixture, magnesium / silver mixture, magnesium / aluminum mixture, magnesium / Indium mixture, a Minium / aluminum oxide mixture, lithium / aluminum mixture, etc., silver halide fine particles or the like, or dispersible nanoparticles, or indium tin oxide (ITO) used as a transparent conductive film, ITO or silicon oxide Indium Tin Oxide (ITSO: Indium Tin Oxide), Zinc Oxide (ZnO), Zinc Oxide with Addition of Gallium (GZO), Indium Zinc Oxide Mixed with 2-20% Zinc Oxide (IZO: Indium Zinc Oxide), organic indium, organic tin, titanium nitride, an alloy of Al, C, Ni, or the like can be used.

なお、銅を用いる場合には、不純物対策のため、合わせてバリア膜を設けるとよい。溶媒は、酢酸ブチル、酢酸エチル等のエステル類、イソプロピルアルコール、エチルアルコール等のアルコール類、メチルエチルケトン、アセトン等の有機溶剤等を用いればよい。ここで、銅を配線として用いる場合のバリア膜としては、窒化シリコン、酸化窒化シリコン、窒化アルミニウム、窒化チタン、窒化タンタル(TaN:Tantalum Nitride)など窒素を含む絶縁性又は導電性の物質を用いると良く、これらを液滴吐出法で形成しても良い。 Note that when copper is used, a barrier film may be provided as a countermeasure against impurities. As the solvent, esters such as butyl acetate and ethyl acetate, alcohols such as isopropyl alcohol and ethyl alcohol, organic solvents such as methyl ethyl ketone and acetone may be used. Here, as a barrier film in the case of using copper as a wiring, an insulating or conductive material containing nitrogen such as silicon nitride, silicon oxynitride, aluminum nitride, titanium nitride, or tantalum nitride (TaN) is used. These may be formed by a droplet discharge method.

なお、ここでは、第1及び第2のゲート電極層を異なる材料で(例えば、第1のゲート電極層をTaN、第2のゲート電極層をW)形成したが、同材料で形成してもよい。また、これらの線幅や長さに応じて適宜材料を異ならせても良い。例えば、図1(C)、(D)における第1のゲート電極層のような比較的面積の大きな領域は、CuやAlのような安価な材料を用い、第2のゲート電極層は低抵抗のAgを用いることができる。 Here, the first and second gate electrode layers are formed of different materials (for example, the first gate electrode layer is TaN and the second gate electrode layer is W). Good. Further, the materials may be appropriately changed according to the line width and length. For example, a relatively large area such as the first gate electrode layer in FIGS. 1C and 1D uses an inexpensive material such as Cu or Al, and the second gate electrode layer has a low resistance. Ag can be used.

以上述べた液滴吐出手段に用いる組成物を吐出するためのノズルの径は、0.1〜50μm(好適には0.6〜26μm、)に設定し、ノズルから吐出される組成物の吐出量は0.00001pl〜50pl(好適には0.0001〜40pl)に設定するのがよい。この吐出量は、ノズルの径の大きさに比例して増加する。また、被処理物とノズル吐出口との距離は、所望の箇所に液滴を滴下するために、できる限り近づけておくことが好ましく、好適には0.1〜2mm程度に設定する。なお、ノズル径を変えずとも、圧電素子に印可されるパルス電圧を変えることによって吐出量を制御することもできる。これらの吐出条件は、ゲート電極層の線幅が約10μm以下となるように設定しておくのが望ましい。 The diameter of the nozzle for discharging the composition used for the droplet discharge means described above is set to 0.1 to 50 μm (preferably 0.6 to 26 μm), and the composition discharged from the nozzle is discharged. The amount is preferably set to 0.00001 pl to 50 pl (preferably 0.0001 to 40 pl). This discharge amount increases in proportion to the size of the nozzle diameter. In addition, the distance between the object to be processed and the nozzle outlet is preferably as close as possible in order to drop the liquid droplets at a desired location, and is preferably set to about 0.1 to 2 mm. In addition, the ejection amount can be controlled by changing the pulse voltage applied to the piezoelectric element without changing the nozzle diameter. These discharge conditions are preferably set so that the line width of the gate electrode layer is about 10 μm or less.

なお、液滴吐出法に用いる組成物の粘度は300mPa・s以下が好適であり、これは、乾燥を防止し、吐出口から組成物を円滑に吐出できるようにするためである。なお、用いる溶媒や用途に合わせて、組成物の粘度、表面張力等は適宜調整するとよい。一例として、ITO、ITSO、有機インジウム、有機スズを溶媒に溶解又は分散させた組成物の粘度は5〜50mPa・s、銀を溶媒に溶解又は分散させた組成物の粘度は5〜20mPa・s、金を溶媒に溶解又は分散させた組成物の粘度は10〜20mPa・sである。 Note that the viscosity of the composition used for the droplet discharge method is preferably 300 mPa · s or less, in order to prevent drying and to smoothly discharge the composition from the discharge port. Note that the viscosity, surface tension, and the like of the composition may be appropriately adjusted according to the solvent to be used and the application. For example, the viscosity of a composition in which ITO, ITSO, organic indium, or organic tin is dissolved or dispersed in a solvent is 5 to 50 mPa · s, and the viscosity of a composition in which silver is dissolved or dispersed in a solvent is 5 to 20 mPa · s. The viscosity of a composition in which gold is dissolved or dispersed in a solvent is 10 to 20 mPa · s.

各ノズルの径や所望のパターン形状などに依存するが、ノズルの目詰まり防止や高精細なパターンの作製のため、導電材料の粒子の径はなるべく小さい方が好ましく、好適には粒径0.1μm以下が好ましい。組成物は、電解法、アトマイズ法又は湿式還元法等の公知の方法で形成されるものであり、その粒子サイズは、一般的に約0.5〜10μmである。ただし、ガス中蒸発法で形成すると、分散剤で保護されたナノ分子は約7nmと微細であり、またこのナノ粒子は、被覆剤を用いて各粒子の表面を覆うと、溶剤中に凝集がなく、室温で安定に分散し、液体とほぼ同じ挙動を示す。したがって、被覆剤を用いることが好ましい。 Although depending on the diameter of each nozzle and the desired pattern shape, the diameter of the conductive material particles is preferably as small as possible for preventing nozzle clogging and producing a high-definition pattern. 1 μm or less is preferable. The composition is formed by a known method such as an electrolytic method, an atomizing method, or a wet reduction method, and its particle size is generally about 0.5 to 10 μm. However, when formed in a gas evaporation method, the nanomolecules protected by the dispersant are as fine as about 7 nm, and the nanoparticles are aggregated in the solvent when the surface of each particle is covered with a coating agent. And stably disperse at room temperature and shows almost the same behavior as liquid. Therefore, it is preferable to use a coating agent.

また、一導電材料の周囲を他の導電材料で覆った粒子を含む組成物を吐出形成して、ゲート電極層を形成してもよい。この際、両導電材料の間にバッファ層を設けておくのが望ましい。例えば、図19に示すように、Cu310の周りをAg311で覆った粒子(図19(A))において、Cu310とAg311の間にNi又はNiB(ニッケルボロン)からなるバッファ層312を設けた粒子構造が挙げられる(図19(B))。

Alternatively, the gate electrode layer may be formed by discharging a composition containing particles in which one conductive material is covered with another conductive material. At this time, it is desirable to provide a buffer layer between the two conductive materials. For example, as shown in FIG. 19, a particle structure in which a buffer layer 312 made of Ni or NiB (nickel boron) is provided between

なお、第1及び第2のゲート電極層は、上記組成物を吐出した後、一般的には加熱処理を行って形成される。例えば、100℃、3分間の乾燥を行い、さらに窒素及び/又は酸素を含む雰囲気下において、200〜350℃で15分間〜30分間の焼成を行うことにより形成する。この加熱処理は、第1の導電材料、第2の導電材料を吐出する毎に行っても良いし、第1の導電材料、第2の導電材料を吐出した後に一度に行っても良い。 Note that the first and second gate electrode layers are generally formed by performing heat treatment after discharging the composition. For example, the film is formed by drying at 100 ° C. for 3 minutes and further baking at 200 to 350 ° C. for 15 to 30 minutes in an atmosphere containing nitrogen and / or oxygen. This heat treatment may be performed every time the first conductive material and the second conductive material are discharged, or may be performed at a time after the first conductive material and the second conductive material are discharged.

ここで、ゲート電極層を液滴吐出法によって形成する場合、その後の加熱処理によって、ゲート電極層の膜厚が、減少するメカニズムについて説明する。 Here, in the case where the gate electrode layer is formed by a droplet discharge method, a mechanism by which the film thickness of the gate electrode layer is reduced by the subsequent heat treatment will be described.

ゲート電極層を液滴吐出法によって形成する場合、ノズルから吐出される組成物(液滴)は、一般的に、ゲート電極層を構成する導電材料を有機溶剤に分散又は溶解させたものであり、この他に組成物中には、分散剤や、バインダーと呼ばれる熱硬化性樹脂が含まれている。ここで、分散剤は、導電粒子を溶剤中に均一に分布させる働きを持ち、バインダーは、焼成時にクラックや不均一な焼きムラが発生するのを防止する働きを持つ。そして、乾燥又は焼成工程により、有機溶剤の蒸発、分散剤の分解除去及びバインダーによる硬化収縮が同時に進行することにより、導電粒子同士が融合し、組成物が硬化する。この際、導電粒子は、ナノレベルから数十〜百数十nmまで成長し、近接する成長粒子同士で融着、及び互いに連鎖することにより、金属連鎖体を形成する。一方、残った有機成分の殆ど(約80〜90%)は、金属連鎖体の外部に押し出され、結果として、金属連鎖体を含む導電層(ゲート電極層)と、その表面を覆う有機成分からなる層(以下、単に「有機層」という。)が形成される。 When the gate electrode layer is formed by a droplet discharge method, the composition (droplet) discharged from the nozzle is generally obtained by dispersing or dissolving a conductive material constituting the gate electrode layer in an organic solvent. In addition, the composition contains a dispersant and a thermosetting resin called a binder. Here, the dispersant has a function of uniformly distributing the conductive particles in the solvent, and the binder has a function of preventing generation of cracks and uneven baking during firing. Then, by the drying or baking step, evaporation of the organic solvent, decomposition and removal of the dispersant, and curing shrinkage by the binder proceed simultaneously, so that the conductive particles are fused and the composition is cured. At this time, the conductive particles grow from the nano level to several tens to hundreds of tens of nanometers, and are fused together and chained together to form a metal chain. On the other hand, most of the remaining organic components (about 80 to 90%) are pushed out of the metal chain, and as a result, from the conductive layer (gate electrode layer) containing the metal chain and the organic component covering the surface. A layer (hereinafter simply referred to as “organic layer”) is formed.

そして、導電ペーストを窒素及び酸素を含む雰囲気下で焼成すると、気体中に含まれる酸素(加熱雰囲気中に大気成分として含まれる酸素も含む。)と有機層中に含まれる炭素や水素などとが反応することにより、有機層を除去することができる。また、焼成雰囲気下に酸素が含まれていない場合には、別途、酸素プラズマ処理等によって有機層を除去することができる。 When the conductive paste is fired in an atmosphere containing nitrogen and oxygen, oxygen contained in the gas (including oxygen contained as an atmospheric component in the heating atmosphere) and carbon, hydrogen, etc. contained in the organic layer. By reacting, the organic layer can be removed. Further, when oxygen is not contained in the firing atmosphere, the organic layer can be removed separately by oxygen plasma treatment or the like.

このように、導電ペーストを窒素及び/又は酸素を含む雰囲気下で焼成、又は乾燥後、酸素プラズマで処理することによって、有機層は除去されるため、ゲート電極層の膜厚及び幅を減少させ、かつ、残存したゲート電極層の平滑化、薄膜化、低抵抗化を図ることができる。 In this way, the conductive layer is baked or dried in an atmosphere containing nitrogen and / or oxygen, and then treated with oxygen plasma to remove the organic layer, thereby reducing the thickness and width of the gate electrode layer. In addition, the remaining gate electrode layer can be smoothed, thinned, and reduced in resistance.

なお、導電材料を含む組成物を減圧下で吐出することにより組成物中の溶媒が揮発するため、後の加熱処理(乾燥又は焼成)時間を短縮することもできる。なお、前記雰囲気中における酸素の組成比を10〜25%とすると、効率良くゲート電極層の膜厚及び幅を減少させることができる。また、よりゲート電極層の平滑化、薄膜化、低抵抗化を図ることができる。 Note that since the solvent in the composition is volatilized by discharging the composition containing the conductive material under reduced pressure, the time for subsequent heat treatment (drying or baking) can be shortened. Note that when the oxygen composition ratio in the atmosphere is 10 to 25%, the thickness and width of the gate electrode layer can be efficiently reduced. In addition, the gate electrode layer can be made smoother, thinner, and lower in resistance.

次に、第1のゲート電極層105及び第2のゲート電極層106をマスクとして、島状半導体層103中に不純物元素109を、イオン注入法等によって導入する(図2(A))。不純物元素109は、n型の不純物元素でも、p型の不純物元素でもよい。n型の不純物元素としては、例えば、リン(P)、砒素(As)、アンチモン(Sb)を用いることができる。また、p型の不純物元素としては、例えば、硼素(B)を用いることができる。

Next, the

不純物元素109の導入により、島状半導体層103のうち、第1のゲート電極層105及び第2のゲート電極層106と重ならない部分には、一対の不純物領域110が形成される。一方、島状半導体層103のうち、第1のゲート電極層105のみと重なる部分には、不純物元素109が第1のゲート電極層105をスルーして導入されることによって、一対の低濃度不純物領域111が形成される。一対の不純物領域110は、ソース領域又はドレイン領域を構成する。また、一対の低濃度不純物領域111の間は、チャネル領域112となる(図2(A))。

By introduction of the

ここで、低濃度不純物領域は、トランジスタにおけるソース又はドレイン領域の端部に集中する電界を緩和し、所謂ホットキャリア(ホットエレクトロン又はホットホール)効果を抑制するために、ソース又はドレイン領域の端部に形成された比較的低濃度の不純物領域である。なお、ソース又はドレイン領域(高濃度不純物領域)と、低濃度不純物領域とに注入される不純物は、同じでも異なっていても良い。低濃度不純物領域の代表的なものとして、LDD領域(Lightly Doped Drain)がある。また、ドレイン近傍の電界を緩和するために、比較的浅い高濃度領域と、それを取り巻く低濃度領域からなる、所謂二重ドレイン構造(Double Diffused Drain : DDD)を有するトランジスタがあるが、DDDにおける低濃度領域も、上記低濃度不純物領域に含まれるものとする。 Here, the low-concentration impurity region relaxes the electric field concentrated on the end portion of the source or drain region in the transistor, and suppresses the so-called hot carrier (hot electron or hot hole) effect so as to suppress the end portion of the source or drain region. Is a relatively low-concentration impurity region. Note that the impurity implanted into the source or drain region (high concentration impurity region) and the low concentration impurity region may be the same or different. As a typical low-concentration impurity region, there is an LDD region (Lightly Doped Drain). In addition, in order to alleviate the electric field in the vicinity of the drain, there is a transistor having a so-called double drain structure (DDD) composed of a relatively shallow high-concentration region and a low-concentration region surrounding the high-concentration region. The low concentration region is also included in the low concentration impurity region.

次に、第2のゲート電極層106上にTFTを保護するためのキャップ絶縁膜113を形成する(図2(B))。材質は、ゲート絶縁膜104と同様のものを用いることができるが、O、C、Na等の不純物の混入を防止するためには、窒化珪素膜又は酸化窒化珪素膜を用いるのが望ましい。キャップ絶縁膜113は、必須ではないが、TFTを不純物の混入から保護するために、できるだけ形成しておくのが望ましい。

Next, a

次に、第2のゲート電極層106上に(キャップ絶縁膜113を形成した場合にはその上に)層間絶縁膜114を基板全面に形成する(図2(B))。層間絶縁膜114としては、ポリイミド、アクリル、ポリアミド、レジスト又はベンゾシクロブテン等の感光性又は非感光性の有機材料や、シロキサン(シリコンと酸素との結合で骨格構造が構成され、置換基に少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)、フルオロ基、または少なくとも水素を含む有機基とフルオロ基を用いたもの)等の耐熱性有機樹脂、を用いることができる。また、これらの材料に、カーボンブラック(CB)を混入させても良い。

Next, an

形成方法としては、その材料に応じて、スピンコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、ディスペンス法、スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーター、カーテンコーター、ナイフコーター等を採用することができる。あるいは、塗布法により得られるSOG膜(例えば、アルキル基を含むSiOx膜)を用いることもできる。また、無機材料を用いてもよく、その際には、酸化珪素、窒化珪素、酸化窒化珪素、DLC(ダイヤモンドライクカーボン)或いは窒化炭素(CN)等の炭素を有する膜、PSG(リンガラス)、BPSG(リンボロンガラス)、アルミナ膜等を用いることができる。形成方法としては、プラズマCVD法、減圧CVD(LPCVD)法、大気圧プラズマCVD等を用いることができる。なお、これらの絶縁膜を積層させてもよい。 As a forming method, depending on the material, spin coating, dipping, spray coating, droplet discharge method (inkjet method, dispensing method, screen printing, offset printing, etc.), doctor knife, roll coater, curtain coater, knife coater, etc. Can be adopted. Alternatively, an SOG film obtained by a coating method (for example, an SiOx film containing an alkyl group) can also be used. In addition, an inorganic material may be used, in which case silicon oxide, silicon nitride, silicon oxynitride, a film containing carbon such as DLC (diamond-like carbon) or carbon nitride (CN), PSG (phosphorus glass), BPSG (phosphorus boron glass), an alumina film, or the like can be used. As a formation method, a plasma CVD method, a low pressure CVD (LPCVD) method, an atmospheric pressure plasma CVD, or the like can be used. Note that these insulating films may be stacked.

次に、パターニング形成されたレジストをマスクとして、層間絶縁膜114、キャップ絶縁膜113及びゲート絶縁膜104をエッチングし、コンタクトホール115を開孔する(図2(C))。ここでは、プラズマエッチングを採用し、エッチング用ガスとしては、Cl2、BCl3、SiCl4もしくはCCl4などを代表とする塩素系ガス、CF4、SF6、NF3、CHF3などを代表とするフッ素系ガス、あるいはO2を用いたが、これらに限定されるものではない。なお、該エッチングは、大気圧プラズマを利用してもよい。

Next, using the patterned resist as a mask, the

なお、層間絶縁膜114を基板全面に形成せずに、コンタクトホールを形成したい領域を残して、液滴吐出法によって選択的に形成しても良い。そのために、コンタクトホールを形成したい領域に、予めFAS(フルオロアルキルシラン)等の撥液性の有機膜を形成しておくことは有効である。

Note that the

次に、コンタクトホール115に、第3の導電材料をノズル123から液滴吐出法によって吐出することにより、ソース電極116及びドレイン電極117を形成する(図2(D))。第3の導電材料は、第1又は第2の導電材料として用いられるものと同様のものを選択することができる。

Next, the third conductive material is discharged from the

以上の工程を経て、低濃度不純物領域を有する、いわゆるLDD構造のトップゲート型TFTが完成する。 Through the above steps, a so-called LDD structure top gate type TFT having a low concentration impurity region is completed.

以上説明したように、本発明に係る半導体装置は、チャネル領域、一対の不純物領域及び一対の低濃度不純物領域からなる半導体層と、ゲート絶縁膜を介して、前記半導体層に接して形成された幅の異なる複数のゲート電極層と、を含み、前記一対の低濃度不純物領域は、前記複数のゲート電極層のうち、膜厚の薄い部分に重なって形成されていることを特徴としている。 As described above, the semiconductor device according to the present invention is formed in contact with the semiconductor layer through the gate insulating film and the semiconductor layer including the channel region, the pair of impurity regions, and the pair of low-concentration impurity regions. A plurality of gate electrode layers having different widths, wherein the pair of low-concentration impurity regions are formed so as to overlap a thin portion of the plurality of gate electrode layers.

また、本発明に係る半導体装置の作製方法は、半導体層上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に、幅の異なる複数のゲート電極層を形成し、前記複数のゲート電極層をマスクとして、前記半導体層に不純物を導入することにより、一対の不純物領域及び一対の低濃度不純物領域を形成し、前記一対の低濃度不純物領域は、前記複数のゲート電極層のうち、膜厚の薄い部分に重なって形成されることを特徴としている。 Further, in the method for manufacturing a semiconductor device according to the present invention, a gate insulating film is formed over a semiconductor layer, a plurality of gate electrode layers having different widths are formed over the gate insulating film, and the plurality of gate electrode layers are formed. As a mask, a pair of impurity regions and a pair of low-concentration impurity regions are formed by introducing impurities into the semiconductor layer, and the pair of low-concentration impurity regions has a thickness of the plurality of gate electrode layers. It is characterized by being formed overlying a thin part.

本発明は、幅の異なる少なくとも2層からなるゲート電極層(ここでは、第1及び第2のゲート電極層)を含み、少なくとも2層からなるゲート電極層のうち幅の広い層に重なって、一対の低濃度不純物領域が形成されていることを特徴としている。これにより、少なくとも2層からなるゲート電極層は、特に液滴吐出法を採用することによって、簡単に形成することができ、液滴吐出法の持つ利便性を最大限に活かすことができる。また、少なくとも2層からなるゲート電極層をマスクとして、不純物元素を導入することにより、一対の不純物領域及び一対の低濃度不純物領域を簡単に形成することができる。 The present invention includes a gate electrode layer composed of at least two layers having different widths (here, the first and second gate electrode layers), and overlaps a wide layer among the gate electrode layers composed of at least two layers. A pair of low-concentration impurity regions is formed. As a result, at least two gate electrode layers can be easily formed by employing the droplet discharge method, and the convenience of the droplet discharge method can be utilized to the maximum. In addition, by introducing an impurity element using at least two gate electrode layers as a mask, a pair of impurity regions and a pair of low-concentration impurity regions can be easily formed.

なお、本実施形態では、半導体装置として、トップゲート型TFTを例に挙げて説明したが、本発明の適用はこれに限定されるものではない。例えば、半導体層の下部にゲート絶縁膜を介して他のゲート電極層を設けた構造を有するデュアルゲート型TFTについても本発明を適用することができる。 In the present embodiment, the top gate type TFT has been described as an example of the semiconductor device, but application of the present invention is not limited to this. For example, the present invention can be applied to a dual gate type TFT having a structure in which another gate electrode layer is provided under a semiconductor layer with a gate insulating film interposed therebetween.

(実施形態2)

本実施形態では、図3を参照して、本発明に係る半導体装置の構成及びその作製方法の一実施形態について説明する。ここでは、トップゲート型TFTを例に挙げて説明する。ゲート絶縁膜104を形成する工程までは、実施形態1と同様に行うことができる(図3(A))。

(Embodiment 2)

In the present embodiment, an embodiment of a structure of a semiconductor device and a manufacturing method thereof according to the present invention will be described with reference to FIG. Here, a top gate TFT will be described as an example. Up to the step of forming the

ゲート絶縁膜104を形成した後に、導電材料を含む組成物をノズル121から吐出することにより、ゲート電極層301を形成する(図3(A))。導電材料としては、実施形態1に示したものから選択することができる。また、ゲート電極層301は、上記組成物を吐出した後、一般的には加熱処理を行って形成される。例えば、100℃、3分間の乾燥を行い、さらに窒素及び/又は酸素を含む雰囲気下において、200〜350℃で15〜30分間の焼成を行うことによりゲート電極層301を形成する。

After the

次に、ゲート電極層301上に、レジスト302をゲート電極層301の略中央部に選択的に形成する(図3(B))。レジスト302は、液滴吐出法によって形成するのが望ましい。レジスト302を形成する箇所は、低濃度不純物領域の幅に応じて、設定すればよい。そして、レジスト302をマスクとして、ゲート電極層301をエッチングし、テーパー状の側面を有するゲート電極層303(本実施形態において、以下、単に「ゲート電極層303」という。)を形成する(図3(B))。

Next, a resist 302 is selectively formed over the

次に、ゲート電極層303及びレジスト302をマスクとして、島状半導体層103中に不純物元素109を、イオン注入法等によって導入(ドーピング)する(図3(C))。不純物元素109は、n型の不純物元素の場合、例えば、リン(P)、砒素(As)、アンチモン(Sb)、p型の不純物元素の場合、例えば、硼素(B)を用いることができる。

Next, using the

不純物元素109の導入により、島状半導体層103のうち、ゲート電極層303と重ならない部分には、一対の不純物領域110が形成される。一方、島状半導体層103のうち、ゲート電極層303のテーパー状の側面と重なる部分には、不純物元素109が該側面をスルーして導入されることによって、一対の低濃度不純物領域111が形成される。一対の不純物領域110は、ソース領域又はドレイン領域を構成する。また、一対の低濃度不純物領域111の間は、チャネル領域112となる(図3(C))。

With the introduction of the

なお、レジスト302を除去した後に、ドーピングを行うこともできるが、チャネル領域112へ不純物元素が導入されないように、レジスト302を残したまま、ドーピングを行うのが望ましい。

Note that doping can be performed after the resist 302 is removed; however, it is preferable to perform doping while leaving the resist 302 so that an impurity element is not introduced into the

次に、レジスト302を除去した後、又は残した状態で、ゲート電極層303上にTFTを保護するためのキャップ絶縁膜113及び層間絶縁膜114を実施形態1と同様の要領で形成する(図3(D))。そして、層間絶縁膜114、キャップ絶縁膜113及びゲート絶縁膜104をエッチングし、コンタクトホールを開孔した後、該コンタクトホールに、導電材料をノズル123から液滴吐出法によって吐出することにより、ソース電極116及びドレイン電極117を形成する(図3(D))。導電材料は、ゲート電極層として用いられるものと同様のものを選択することができる。

Next, after the resist 302 is removed or left, a

以上の工程を経て、低濃度不純物領域を有する、いわゆるLDD構造のトップゲート型TFTが完成する。 Through the above steps, a so-called LDD structure top gate type TFT having a low concentration impurity region is completed.

以上説明したように、本発明に係る半導体装置は、チャネル領域、一対の不純物領域及び一対の低濃度不純物領域からなる半導体層と、ゲート絶縁膜を介して、前記半導体層に接して形成されたテーパー状のゲート電極層と、を含み、前記一対の低濃度不純物領域は、前記ゲート電極層のうち、テーパー状の部分に重なって形成されていることを特徴としている。 As described above, the semiconductor device according to the present invention is formed in contact with the semiconductor layer through the gate insulating film and the semiconductor layer including the channel region, the pair of impurity regions, and the pair of low-concentration impurity regions. And the pair of low-concentration impurity regions are formed so as to overlap a tapered portion of the gate electrode layer.

また、本発明に係る半導体装置の作製方法は、半導体層上にゲート絶縁膜を形成し、前記ゲート絶縁膜上にゲート電極層を形成し、前記ゲート電極層上に形成された絶縁物をマスクとしてエッチングを行い、前記ゲート電極層をテーパー状とし、前記テーパー状のゲート電極層をマスクとして、前記半導体層に不純物を導入することにより、一対の不純物領域及び一対の低濃度不純物領域を形成し、前記一対の低濃度不純物領域は、前記ゲート電極層のうち、テーパー状の領域に重なって形成されることを特徴としている。 The method for manufacturing a semiconductor device according to the present invention includes forming a gate insulating film on a semiconductor layer, forming a gate electrode layer on the gate insulating film, and masking the insulator formed on the gate electrode layer. Etching is performed to form a pair of impurity regions and a pair of low-concentration impurity regions by forming the gate electrode layer into a tapered shape and introducing impurities into the semiconductor layer using the tapered gate electrode layer as a mask. The pair of low-concentration impurity regions are formed to overlap a tapered region of the gate electrode layer.

本発明は、テーパー状の側面を有するゲート電極層を含み、ゲート電極層のテーパー状の側面に重なって、一対の低濃度不純物領域が形成されていることを特徴としている。これにより、テーパー状のゲート電極層は、特に液滴吐出法を採用することによって、簡単に形成することができ、液滴吐出法の持つ利便性を最大限に活かすことができる。また、テーパー状のゲート電極層をマスクとして、不純物元素を導入することにより、一対の不純物領域及び一対の低濃度不純物領域を簡単に形成することができる。 The present invention is characterized in that it includes a gate electrode layer having a tapered side surface, and a pair of low-concentration impurity regions are formed so as to overlap the tapered side surface of the gate electrode layer. Thereby, the tapered gate electrode layer can be easily formed by adopting the droplet discharge method in particular, and the convenience of the droplet discharge method can be fully utilized. In addition, a pair of impurity regions and a pair of low-concentration impurity regions can be easily formed by introducing an impurity element using the tapered gate electrode layer as a mask.

なお、本実施形態では、半導体装置として、トップゲート型TFTを例に挙げて説明したが、本発明の適用はこれに限定されるものではない。例えば、デュアルゲート型TFTについても本発明を適用することができる。また、テーパー状とするためには、上述したように液滴吐出法で選択的にゲート電極層を形成した後、レジスト等の絶縁物で覆って、両端をテーパー状にエッチングしても良いし、異なる吐出量のノズルから、ゲート電極層を構成する導電材料を含む組成物を複数回吐出することにより段階的に形成してもよい。 In the present embodiment, the top gate type TFT has been described as an example of the semiconductor device, but application of the present invention is not limited to this. For example, the present invention can be applied to a dual gate TFT. In order to obtain a tapered shape, the gate electrode layer may be selectively formed by a droplet discharge method as described above, and then covered with an insulator such as a resist, and both ends may be etched into a tapered shape. Alternatively, it may be formed stepwise by discharging a composition containing a conductive material constituting the gate electrode layer a plurality of times from nozzles having different discharge amounts.

(実施形態3)

本実施形態では、図4を参照して、本発明に係る半導体装置の構成及びその作製方法の一実施形態について説明する。ここでは、トップゲート型TFTを例に挙げて説明する。ゲート電極層を構成する導電材料を含む組成物を液滴吐出法によって形成する工程までは、実施形態1、2と同様に行うことができる。

(Embodiment 3)

In the present embodiment, an embodiment of a structure of a semiconductor device and a manufacturing method thereof according to the present invention will be described with reference to FIG. Here, a top gate TFT will be described as an example. The steps up to the step of forming the composition containing the conductive material forming the gate electrode layer by a droplet discharge method can be performed in the same manner as in Embodiments 1 and 2.

導電材料を含む組成物を形成したら、乾燥処理を行い、組成物を固体化させ、ゲート電極層400とする(図4(A))。乾燥処理は、例えば、100℃、3分間の条件下で行う。

When a composition including a conductive material is formed, a drying process is performed to solidify the composition, whereby the

次に、耐熱性を有する絶縁物401(本実施形態において、以下、単に「絶縁物401」という。)を、ゲート電極層400の略中央部に選択的に形成する(図4(B))。絶縁物401は、液滴吐出法によって選択的に形成するのが望ましい。絶縁物401を形成する箇所は、低濃度不純物領域の幅に応じて、設定すればよい。

Next, an

耐熱性を有する絶縁物401の材料としては、代表的には、シロキサン等の耐熱性樹脂を用いることができる。ただし、耐熱性を有する、又は熱吸収性を有する材料であれば、絶縁物401の材料はこれに限定されるものではない。

As a material for the

次に、ゲート電極層400を絶縁物401で部分的に覆った状態で、加熱処理を行う。例えば、窒素及び/又は酸素を含む雰囲気下において、200〜350℃で15分間〜30分間の焼成を行う。

Next, heat treatment is performed with the

上記加熱処理によって、ゲート電極層400のうち、絶縁物401が形成されていない領域の膜厚は、減少する。そのメカニズムについては、実施形態1で説明したとおりである。なお、加熱雰囲気下に酸素が含まれていない場合、又は、有機成分からなる層(有機層)が残存している場合には、酸素プラズマ処理等によって有機層を除去することができる。

Through the heat treatment, the thickness of the

一方、ゲート電極層400のうち、絶縁物401で覆われた領域は、加熱処理中、絶縁物401によって保護されるため、その領域の膜厚は減少しない。

On the other hand, a region of the

かくして、部分的に絶縁物401で覆われたゲート電極層400を加熱処理することで、ゲート電極層400の絶縁物401で覆われた領域と覆われていない領域とで、膜厚が異なるゲート電極層402(本実施形態において、以下、単に「ゲート電極層402」という。)が形成される(図4(C))。なお、ゲート電極層402は、基本的には、単層からなるが、ゲート電極層400が多層の場合には、この限りでない。

Thus, by subjecting the

なお、ゲート電極層402全体の幅も、上記加熱処理によって減少するため、それを考慮に入れて、加熱処理前のゲート電極層400の吐出条件を制御するのが望ましい。

Note that the width of the entire

このように、ゲート電極層400を、絶縁物401で覆い、窒素及び/又は酸素を含む雰囲気下で焼成し、又は乾燥後、酸素プラズマで処理することによって、その表面部分の有機層は除去されるため、ゲート電極層の所望の領域の膜厚及び幅を減少させ、かつ、残存したゲート電極層の平滑化、薄膜化、低抵抗化を図ることができる。特に、前記雰囲気中における酸素の組成比を10〜25%とすると、効率良くゲート電極層の膜厚及び幅を減少させることができ、よりゲート電極層の平滑化、薄膜化、低抵抗化を図ることができる。

In this way, the