JP4399890B2 - Game machine - Google Patents

Game machine Download PDFInfo

- Publication number

- JP4399890B2 JP4399890B2 JP07766599A JP7766599A JP4399890B2 JP 4399890 B2 JP4399890 B2 JP 4399890B2 JP 07766599 A JP07766599 A JP 07766599A JP 7766599 A JP7766599 A JP 7766599A JP 4399890 B2 JP4399890 B2 JP 4399890B2

- Authority

- JP

- Japan

- Prior art keywords

- value

- output

- update

- storage means

- terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Pinball Game Machines (AREA)

- Display Devices Of Pinball Game Machines (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、パチンコ遊技機などに代表される遊技機に関するものである。

【0002】

【従来の技術】

例えばパチンコ遊技機は、複数種類の図柄を変動表示可能な表示装置を備えており、遊技領域に打ち込まれた打球が図柄作動ゲートを通過すると、変動表示を開始するように構成されている。この変動表示が予め定められた図柄の組み合わせと一致して停止すると、大当たりとなって、遊技者に所定の遊技価値が付与される。

【0003】

かかる大当たりの発生の有無は、打球が図柄作動ゲートを通過するタイミングで決定される。即ち、1カウントずつ定期的に一定の範囲で(例えば、1カウントずつ、2ms毎に、0から630の範囲で)更新される乱数カウンタを備え、打球が図柄作動ゲートを通過したときに、その乱数カウンタの値を読み出して、読み出された乱数カウンタの値が、例えば「7」などの所定値と一致する場合に、大当たりを発生するようにしている。

【0004】

ところが、最近、「ぶら下げ基板」と呼ばれる不正な基板を使用した不正行為が報告されている。この不正行為は、不正な基板をぶら下げて(不正な「ぶら下げ基板」を取り付けて)、不当に大当たりを発生させるというものである。具体的には、前記したパチンコ遊技機に設けられる大当たりを決定するための乱数カウンタと同様の働きをするカウンタ(1カウントずつ定期的に一定の範囲で更新されるカウンタ)を「ぶら下げ基板」内に設け、そのカウンタの値をパチンコ遊技機の電源投入等に合わせてリセット(0クリア)することにより、「ぶら下げ基板」内で大当たりの発生タイミングを把握するのである。そして、その把握した大当たりの発生タイミングに合わせて、「ぶら下げ基板」内で打球の図柄作動ゲート通過信号を不正に生成し、これをパチンコ遊技機の制御基板へ出力して、不当に大当たりを発生させるというものである。遊技場などでは、この「ぶら下げ基板」を用いた不正行為により、多大な被害を被っている。

【0005】

【0006】

【0007】

【発明が解決しようとする課題】

【0008】

【0009】

【0010】

本発明は上記例示した問題点等を解決するためになされたものであり、「ぶら下げ基板」等による不正行為を防止することができる遊技機を提供することを目的としている。

【0011】

【課題を解決するための手段】

この目的を達成するために請求項1記載の遊技機は、乱数値記憶手段と、その乱数値記憶手段の値を所定の範囲内で更新する第1更新手段と、所定の契機に基づいて前記乱数値記憶手段の値を読み出す読出手段とを有し、その読出手段により読み出された前記乱数値記憶手段の値が予め定められた値と一致する場合に遊技者に所定の遊技価値を付与する制御手段を備えており、前記乱数値記憶手段の値は、前記第1更新手段により所定回更新されることで一周するものであり、前記第1更新手段は、前記乱数値記憶手段の値が一周すると、前記所定の範囲内のいずれかの値を更新の初期値として次の周の更新を行うものであり、前記制御手段は、前記所定の範囲と同じ範囲で更新され、前記乱数値記憶手段の更新の初期値の変更に使用される初期値記憶手段と、その初期値記憶手段の値を読み出して、その値を更新し、更新された値を前記初期値記憶手段へ書き込む第2更新手段と、定期的な信号である定期信号を出力する出力手段とを有し、その出力手段が出力する定期信号に基づいて定期処理を行うとともに、その定期処理の終了の後、次の定期信号に基づく定期処理が行われるまでの期間に繰り返し所定の処理を行うものであり、その所定の処理において、前記第2更新手段による、読み出し、更新、および書き込み処理が行われ、前記第1更新手段による前記乱数値記憶手段の更新は、前記定期処理において行われ、前記制御手段は、電源投入後に前記乱数値記憶手段と前記初期値記憶手段とを含む記憶手段のデータが有効か否かを判別する判別手段と、その判別手段により有効と判別された場合に、前記記憶手段のデータを使用して遊技を実行する遊技実行手段と、その判別手段により有効でないと判別された場合に、前記記憶手段のデータを初期化する初期化手段と、前記第2更新手段による書き込み処理の実行時に、前記出力手段から定期信号が出力される場合に、その定期信号に基づく定期処理の実行を遅延させ、かつ、その書き込み処理の実行が終了した後に、実行が遅延された定期処理を実行する定期処理実行遅延手段とを有しており、その定期処理実行遅延手段により所定の定期処理の実行が遅延された場合であっても、次の定期処理を実行するために前記出力手段から出力される定期信号の出力は遅延されないものである。

【0012】

請求項2記載の遊技機は、請求項1記載の遊技機において、前記遊技機は、パチンコ遊技機である。

【0013】

【発明の実施の形態】

以下、本発明の好ましい実施例について、添付図面を参照して説明する。本実施例では、遊技機の一例としてパチンコ遊技機、特に、第1種パチンコ遊技機を用いて説明する。なお、本発明を第3種パチンコ遊技機やスロットマシン等の他の遊技機に用いることは、当然に可能である。

【0014】

図1は、第1実施例におけるパチンコ遊技機Pの遊技盤の正面図である。遊技盤1の周囲には、打球が入賞することにより5個から15個の遊技球が払い出される複数の入賞口2が設けられている。また、遊技盤1の中央には、複数種類の識別情報としての図柄などを表示する液晶(LCD)ディスプレイ3が設けられている。このLCDディスプレイ3の表示画面は横方向に3分割されており、3分割された各表示領域において、それぞれ図柄の変動表示が行われる。

【0015】

LCDディスプレイ3の下方には、図柄作動ゲート(第1種始動口)4が設けられ、打球がこの図柄作動ゲート4を通過することにより、前記したLCDディスプレイ3の変動表示が開始される。図柄作動ゲート4の下方には、特定入賞口(大入賞口)5が設けられている。この特定入賞口5は、LCDディスプレイ3の変動後の表示結果が予め定められた図柄の組み合わせの1つと一致する場合に、大当たりとなって、打球が入賞しやすいように所定時間(例えば、30秒経過するまで、あるいは、打球が10個入賞するまで)開放される入賞口である。この特定入賞口5内には、Vゾーン5aが設けられており、特定入賞口5の開放中に、打球がVゾーン5a内を通過すると、継続権が成立して、特定入賞口5の閉鎖後、再度、その特定入賞口5が所定時間(又は、特定入賞口5に打球が所定個数入賞するまで)開放される。この特定入賞口5の開閉動作は、最高で16回(16ラウンド)繰り返し可能にされており、開閉動作の行われ得る状態が、いわゆる所定の遊技価値の付与された状態(特別遊技状態)である。

【0016】

図2は、かかるパチンコ遊技機Pの電気的構成を示したブロック図である。パチンコ遊技機Pの制御部Cは、演算装置であるCPU11と、そのCPU11により実行される各種の制御プログラムや固定値データを記憶したROM12と、各種のデータ等を一時的に記憶するためのメモリであるRAM13とを備えている。図5から図7に示すフローチャートのプログラムは、制御プログラムの一部としてROM12内に記憶されている。

【0017】

CPU11は、演算を行うALUのほか、アキュームレータ(以下「Acc」と称す)11aや複数の内部レジスタ11b、フラグレジスタ11cを備えている。RAM13内に設けられるカウンタ等の値は、一旦、CPU11の内部レジスタ11bへロードされ(読み込まれ)、その内部レジスタ11b内で更新された後に、RAM13の元のカウンタ内へセイブされて(書き込まれて)、更新される。

【0018】

なお、68系の8ビットCPU11では、ペアになっている2バイト(16ビット)の内部レジスタ11bの値を、連続したアドレスの2バイトのメモリ(RAM13内)へ1命令でセイブする(書き込む)ことができる。バスライン14のデータバスは8ビットで構成されるので、この場合の書き込みは、上位バイト、下位バイトの順に行われる。また、80系の8ビットCPUでは、68系のCPU11とは逆に、ペアになっている2バイト(16ビット)の内部レジスタの値を、連続したアドレスの2バイトのメモリへ、下位バイト上位バイトの順に1命令でセイブすることができる。

【0019】

RAM13は、乱数カウンタ13aと、初期値カウンタ13bと、初期値メモリ13cとを備えている。乱数カウンタ13aは、大当たりの発生を決定するためのカウンタであり、図6の乱数更新処理(S6)によって、「0〜630(0〜276h)」の範囲で、2ms毎に1カウントずつ更新される。このため乱数カウンタ13aは2バイトで構成されている。打球が図柄作動ゲート4を通過したときに取得した乱数カウンタ13aの値が例えば「7」であると、大当たりが発生する。大当たりが発生すると、大当たりコマンドが制御部Cから後述する表示装置Dへ送られる。表示装置Dは、この大当たりコマンドに基づいて、LCDディスプレイ3の変動表示を大当たりの状態に制御する。

【0020】

初期値カウンタ13bは、乱数カウンタ13aの更新の初期値をカウントするためのカウンタであり、乱数カウンタ13aと同様に2バイトで構成されている。この初期値カウンタ13bの値は、図7の初期値カウンタ更新処理(S21)によって、乱数カウンタ13aの更新範囲と同じ「0〜630(276h)」の範囲で、1カウントずつ更新される。

【0021】

図7の初期値カウンタ更新処理は、図5のリセット割込処理における残余時間の間、即ち、効果音処理(S19)の終了後、次のリセット割込処理が発生するまでの間に、繰り返し実行される(S21)。リセット割込処理は2ms毎に実行されるが、1回のリセット割込処理において実行されるS1からS19までの各処理の処理時間は遊技の状況に応じて変化するので、リセット割込処理の残余時間は、一定な時間ではなく、遊技の状況に応じて変化する不定な時間となる。「ぶら下げ基板」ではこの不定な時間を把握することはできないので、かかる不定な時間内に繰り返し更新される初期値カウンタ13bの値を乱数カウンタ13aの更新の初期値として使用することにより、「ぶら下げ基板」による大当たり発生のタイミングの把握を不可能にしている。

【0022】

初期値メモリ13cは、乱数カウンタ13aの更新の初期値を記憶するためのメモリであり、乱数カウンタ13aと同様に2バイトで構成されている。本実施例では、乱数カウンタ13aの更新の初期値は、乱数カウンタの一回りの更新毎に変更される。よって、更新された乱数カウンタ13aの値が初期値メモリ13cの値と一致すると、乱数カウンタ13aの一回りの更新が終了したことになるので、両値13a,13cの一致を契機として、そのときの初期値カウンタ13bの値が乱数カウンタ13aおよび初期値メモリ13cに書き込まれて、乱数カウンタ13aの更新の初期値が変更される。従って、乱数カウンタ13aの更新の初期値を変更しても、乱数の一様性(連続で取得した場合に同じ値を取ることがなく、しかも、すべての値が同じ確率で取り出せること)のある乱数値を得ることができるのである。

【0023】

これらのCPU11、ROM12、RAM13は、バスライン14を介して互いに接続されており、バスライン14は、また、入出力ポート15にも接続されている。この入出力ポート15は表示装置Dや他の入出力装置16と接続されている。制御部Cは、入出力ポート15を介して、表示装置Dや他の入出力装置16へ動作コマンドを送り、それら各装置を制御する。LCDディスプレイ3の変動表示や特定入賞口5の開閉動作も、この動作コマンドに基づいて制御される。

【0024】

表示装置Dは、CPU21と、プログラムROM22と、ワークRAM23と、ビデオRAM24と、キャラクタROM25と、画像コントローラ26と、入出力ポート27と、LCDディスプレイ3とを備えている。表示装置DのCPU21は、制御部Cから出力される動作コマンドに応じて、LCDディスプレイ3の表示制御(変動表示)を行うものであり、プログラムROM22には、このCPU21により実行されるプログラムが記憶されている。ワークRAM23は、CPU21によるプログラムの実行時に使用されるワークデータが記憶されるメモリである。

【0025】

ビデオRAM24は、LCDディスプレイ3に表示されるデータが記憶されるメモリであり、このビデオRAM24の内容を書き換えることにより、LCDディスプレイ3の表示内容が変更される。即ち、各表示領域における図柄の変動表示は、ビデオRAM24の内容が書き換えられることにより行われる。キャラクタROM25は、LCDディスプレイ3に表示される図柄などのキャラクタデータを記憶するメモリである。画像コントローラ26は、CPU21、ビデオRAM24、入出力ポート27のそれぞれのタイミングを調整して、データの読み書きを介在するとともに、ビデオRAM24に記憶される表示データをキャラクタROM25を参照して所定のタイミングでLCDディスプレイ3に表示させるものである。

【0026】

次に、図3および図4を参照して、図5のリセット割込処理の実行契機となるユーザーリセット割込の発生タイミングについて説明する。このユーザーリセット割込は、2ms毎であって、且つ、CPU11によりオペコードフェッチ信号が出力されるタイミング、即ち、CPU11のLIR端子の出力がHiからLowになるタイミングで発生するように構成されている。

【0027】

オペコードフェッチ信号が出力されている間は、CPU11によりROM12からオペコードのリードが行われているため、RAM13への書き込みが行われることはない。よって、かかるオペコードフェッチ信号に同期してユーザーリセット割込を発生させることにより、リセット割込処理の残余時間の間において初期値カウンタ13bの値を繰り返し更新しても、次のリセット割込処理が発生する時には、その初期値カウンタ13bの値を書き換えることがなく本来の更新範囲外の値としてしまうことはない。

【0028】

CPU11のリセット端子RESには、リセットIC31が接続されている。リセットIC31の出力(A)は、パチンコ遊技機Pの電源投入後所定時間が経過するとLowからHiへ立ち上がり、以降は、パチンコ遊技機Pの電源がオフされるまでHiを維持する。CPU11は、リセット端子RESへの入力がLowからHiへ立ち上がりHiを維持している間、動作を継続する。

【0029】

また、CPU11には、8.1920MHzの発振子(クロック)32が接続されている。クロック32の出力はCPU11内で4分周され、Eクロック端子から488.3ns周期の矩形状の発振波が出力される(B)。更に、ICLK端子からは、そのEクロックを4096分周した2ms周期の矩形波が出力される(C)。

【0030】

リセットIC31の出力端は、HC74で構成されるDフリップフロップ33のCLR端子にも接続されている。Dフリップフロップ33のCK端子は、CPU11のICLK端子と接続されており、PR端子およびD端子はVcc(+5V)に接続されているので、CPU11のICLK端子の出力が立ち上がるまでは、Dフリップフロップ33のQ出力はLow(G)、Qバー出力はHi(D)を維持している。CPU11のICLK端子の出力が一旦LowからHiへ立ち上がると(C)、Dフリップフロップ33のQ出力はHi(G)、Qバー出力はLow(D)となり、Dフリップフロップ33は、パチンコ遊技機Pの電源がオフされるまで、この出力を維持する。

【0031】

Dフリップフロップ33のQバー出力端は、2入力オア回路34の一方の入力端に接続されている。また、オア回路34のもう一つの入力端はCPU11のICLK端子に接続されている。よって、オア回路34の出力端からは、Dフリップフロップ33のQバー出力がLow(D)となってから以降、ICLK端子の出力(C)と同じ2ms周期の矩形波が出力される(E)。

【0032】

一方、CPU11のEクロック端子はインバータ35の入力端と接続され、そのインバータ35の出力端は、HC74で構成されるDフリップフロップ36のCK端子および2入力オア回路37の一方の入力端に接続されている。Dフリップフロップ36のPR端子はVccに、CLR端子は前記したDフリップフロップ33のQ出力端に、D端子はHC4020で構成されるバイナリカウンタ38のQ7出力端に、Q出力端はオア回路37の入力端に、それぞれ接続されている。更に、オア回路37の出力端は、カウンタ38のCK端子に接続されている。

【0033】

Dフリップフロップ36のCLR端子に入力されるDフリップフロップ33のQ出力は、CPU11のICLK端子の出力がLowからHiへ一旦立ち上がると(C)、以降はHiを維持する(G)。Dフリップフロップ36のPR端子にはVccが入力されているので、その後は、CPU11のEクッロク端子の出力(B)が反転されたインバータ35の出力(F)の立ち上がり毎に、D端子へ入力されるカウンタ38のQ7出力(I)の状態がDフリップフロップ36のQ端子から出力される(J)。よって、オア回路37は、Dフリップフロップ36のQ端子の出力がLowの間は(J)、Eクロックの反転出力(F)を出力し(H)、Dフリップフロップ36のQ端子の出力がHiの間は(J)、Hiを出力する(H)。

【0034】

カウンタ38のQ7端子は、Dフリップフロップ36のD端子と接続される他、2入力オア回路39の一つの入力端に接続されている。このオア回路39の他方の入力端にはオア回路34の出力端が接続されている。カウンタ38のQ7出力は、CLR端子への出力がHiになっている間(E)、Lowを維持する(I)。そして、CLR端子への出力がLowになった状態で(E)、CK端子へ64回立ち下がりクロックが入力されると(H)、Hiとなり(I)、そのQ7端子のHi出力は、CLR端子へHiが入力されるまで維持される(E,I)。

【0035】

オア回路39からは、オア回路34の出力およびカウンタ38のQ7出力が共にLowである場合に(E,I)、Lowが出力される(K)。よって、オア回路39の出力は、オア回路34の出力がLowとなった後(E)、カウンタ38のCK端子へ64回立ち下がりクロックが入力されるまで(H)、Low出力を維持する(K)。即ち、オア回路39からは、2ms毎に(C,E)、カウンタ38のCK端子へ64回立ち下がりクロックが入力されるまでの間(H)、Lowが出力される。

【0036】

なお、従来技術においては、このオア回路39の出力端がCPU11のURES端子に接続されており、オア回路39からLow出力されるタイミングでユーザーリセット割込が発生するように構成されていた。よって、このオア回路39の出力がLowを維持する期間が(K)、ユーザーリセット割込の発生を確定させるための期間になっていた。

【0037】

オア回路39の出力端は、タイミング回路40のインバータ41の入力端と、HC74で構成されるDフリップフロップ42のD端子に接続されている。タイミング回路40は、ユーザーリセット割込をオペコードフェッチに同期するタイミングで発生させるための回路である。オア回路39からは2ms毎にLowが出力されるので(K)、タイミング回路40では、そのLow出力を入力した後の最初のオペコードフェッチのタイミングで、CPU11のURES端子へLowを出力し(N)、ユーザーリセット割込を発生させるのである。

【0038】

タイミング回路40のインバータ41の入力端は、前記した通り、オア回路39の出力端に接続されており、そのインバータ41の出力端は、Dフリップフロップ42のPR端子に接続されている。Dフリップフロップ42のCLR端子はVccに接続されているので、CPU11のURES端子に接続されるDフリップフロップ42のQ端子からは、オア回路39からHi出力されている間(K)、Hiが出力され(N)、ユーザーリセット割込は発生しない。

【0039】

CPU11のLIR端子はインバータ43の入力端に接続され、そのインバータ43の出力端はDフリップフロップ42のCK端子に接続されている。オペコードフェッチがあるとLIR端子の出力はHiからLowへ立ち下がるので、オペコードフェッチの度に、インバータ43からDフリップフロップ42のCK端子へはLowからHiへの立ち上がり信号が出力される(M)。

【0040】

ここで、オア回路39からLowが出力されると(K)、Dフリップフロップ42のPR端子へHiが入力される(L)。CLR端子にはVccが入力されているので、CPU11からオペコードフェッチ信号が出力されLIR端子の出力がHiからLowへ立ち下がると、Dフリップフロップ42のCK端子への入力がLowからHiへ立ち上がり(M)、その時のD端子へ入力されているLow出力が(K)、Dフリップフロップ42のQ端子から出力されて(N)、CPU11のURES端子へ入力される。これにより、ユーザーリセット割込がオペコードフェッチのタイミングで発生するのである。

【0041】

なお、このようにユーザーリセット割込の発生タイミングを最初のオペコードフェッチのタイミングまで遅延させるように構成しても、オア回路39は確実に2ms毎にLow信号を出力するので(K)、その遅延分が累積してしまうことはない。従って、ユーザーリセット割込を2ms毎に実行することができるのである。

【0042】

次に、上記のように構成されたパチンコ遊技機Pで実行される各処理を、図5から図7のフローチャートを参照して説明する。図5は、パチンコ遊技機Pの制御部Cにおいて、2ms毎に実行されるリセット割込処理のフローチャートである。パチンコ遊技機Pの主な制御は、このリセット割込処理によって実行される。なお、このリセット割込処理は、電源投入時におけるリセット割込の発生時、および、前記したユーザーリセット割込の発生時に実行される。

【0043】

リセット割込処理では、まず、スタックポインタを設定し(S1)、RAM13の所定エリアに書き込まれているパターンのチェックを行う(S2)。チェックの結果、所定エリアに所定のパターンが書き込まれていれば、RAM13に異常はなく正常であるので(S2:正常)、処理をS3へ移行する。一方、S2のチェックの結果、所定エリアに所定のパターンが書き込まれていなければ、電源投入後のリセット割込により最初に実行されたリセット割込処理であるか、或いは、RAM13に異常があるので(S2:異常)、この場合には処理をS22へ移行して、一旦、RAM13の内容をクリアした後、RAM13内へ初期値を書き込んで(S22)、次のリセット割込処理の発生を待機する。

【0044】

S3の処理ではタイマ割込の設定を行う(S3)。ここで設定されるタイマ割込としては、LCDディスプレイ3の表示を制御するコマンドを表示装置Dへ送信するためのストローブ信号を発生させるタイマ割込などがある。タイマ割込の設定後は、各割込を許可状態とする(S4)。割込の許可後は、特別図柄変動処理(S15)や、表示データ作成処理(S17)、ランプ・情報処理(S18)などにより、前回のリセット割込処理において更新された出力データを一度に各ポートへ出力するポート出力処理を実行する(S5)。ポート出力処理の実行後は、後述する乱数更新処理(S6)を実行して、乱数カウンタ13aの値を「+1」更新し、更に、記憶タイマ減算処理を実行する(S7)。記憶タイマ減算処理は、大当たり判定の保留球が所定数以上あり、且つ、LCDディスプレイ3において図柄の変動表示中である場合に、図柄の変動表示時間の短縮を行うものである。

【0045】

スイッチ読込処理(S8)は、各スイッチの値を読み込むことにより、遊技領域1へ打ち込まれた打球の入賞口2や大入賞口5(Vゾーン5aを含む)への入賞、図柄作動ゲート4の通過、更には賞球や貸球を検出するための処理である。カウント異常監視処理(S9)は、S8のスイッチ読込処理によって読み込まれたスイッチデータに異常があるか否かを監視するための処理である。例えば、大入賞口5が開放され、打球のVゾーン5aの通過を検出するVカウントスイッチで打球が検出されたにも拘わらず、Vゾーン5a以外の大入賞口5への入賞を検出する10カウントスイッチで1球の打球も検出できない場合には、10カウントスイッチが抜き取られるか故障するなどして、10カウントスイッチに何らかの異常が発生している。また、賞球を払い出すモータを駆動したにも拘わらず、1球の賞球も払い出されない場合には、賞球の払出装置に何らかの異常が発生している。このようにカウント異常監視処理(S9)では、スイッチ読込処理(S8)によって読み込まれたスイッチデータに基づいて、上記のような異常の有無を監視している。

【0046】

図柄カウンタ更新処理(S10)では、LCDディスプレイ3で行われる変動表示の結果、停止表示される図柄を決定するためのカウンタの更新処理が行われる。また、図柄チェック処理(S11)では、図柄カウンタ更新処理(S10)で更新されたカウンタの値に基づいて、特別図柄変動処理(S15)で使用される大当たり図柄や、はずれ図柄、更にはリーチ図柄などが決定される。

【0047】

S3からS11までの処理において、エラーが発生していなければ(S12:正常)、普通図柄変動処理(S13)によって、7セグメントLEDの変動表示を行うと共に、その変動表示の結果、当たりが発生した場合には普通電動役物(図示せず)を所定時間開放する当たり処理を実行する。その後、状態フラグをチェックし(S14)、LCDディスプレイ3の図柄の変動表示中であれば(S14:図柄変動中)、特別図柄変動処理(S15)によって、打球が図柄作動ゲート4を通過するタイミングで読みとられた乱数カウンタ13aの値に基づいて、大当たりか否かの判定が行われると共に、LCDディスプレイ3の表示図柄の変動処理を実行する。一方、状態フラグをチェックした結果、大当たり中であれば(S14:大当り中)、大入賞口5を開放するなどの大当たり処理(S16)を実行する。更に、状態フラグをチェックした結果、図柄の変動中でも大当たり中でもなければ(S14:その他)、S15及びS16の処理をスキップして、S17の表示データ作成処理へ移行する。なお、S12の処理において、エラーが確認された場合には(S12:エラー)、S13〜S16の各処理をスキップして、S17の表示データ作成処理へ移行する。

【0048】

表示データ作成処理(S17)では、図柄の変動表示以外にLCDディスプレイ3に表示されるデモデータや、7セグメントLEDの表示データなどが作成され、ランプ・情報処理(S18)では、保留球のランプデータをはじめ、各種のランプデータが作成される。効果音処理(S19)では、遊技の状況に応じた効果音データが作成される。なお、これらの表示データおよび効果音データは、前記したポート出力処理(S5)やタイマ割込処理によって各装置へ出力される。

【0049】

効果音処理(S19)の終了後は、次のリセット割込処理が発生するまでの残余時間の間、S10と同一の処理である図柄カウンタ更新処理(S20)と、初期値カウンタ更新処理(S21)とを繰り返し実行する。S1〜S19の各処理の実行時間は遊技の状態に応じて変化するので、次のリセット割込処理(次のユーザーリセット割込)が発生するまでの残余時間は、一定の時間ではなく、遊技の状態に応じて変化する。よって、かかる残余時間を使用して図柄カウンタ更新処理(S20)を繰り返し実行することにより、停止図柄をランダムに変更することができる。また、かかる残余時間を使用して初期値カウンタ更新処理(S21)を繰り返し実行することにより、乱数カウンタ13aの更新の初期値となる初期値カウンタ13bの値を「ぶら下げ基板」で把握不可能にすることができる。

【0050】

図6は、乱数更新処理のフローチャートである。乱数更新処理(S6)では、CPU11の内部レジスタ11bを介して、乱数カウンタ13aの値を「0〜630(0〜276h)」の範囲内で「+1」ずつ更新すると共に、制御部Cで使用される他の乱数の更新を行っている。

【0051】

まず、2バイトで構成される乱数カウンタ13aの値を2バイトの内部レジスタ11bへ書き込む(S31)。内部レジスタ11bの値を1加算し(S32)、加算後の内部レジスタ11bの値が「631」以上であるか否か、即ち、乱数カウンタ13aの更新範囲の値を超えている否かを調べる(S33)。加算後の内部レジスタ11bの値が「631」以上であれば(S33:Yes)、更新範囲の値を超えているので、内部レジスタ11bの値を「0」クリアする(S34)。一方、加算後の内部レジスタ11bの値が「630」以下であれば(S33:No)、更新範囲内の値であるので、S34の処理をスキップして、S35の処理へ移行する。

【0052】

S35の処理では、更新後の内部レジスタ11bの値と初期値メモリ13cの値とが比較される。初期値メモリ13cには乱数カウンタ13aの更新の初期値が記憶されているので、両値が等しい場合には(S35:Yes)、乱数カウンタ13aの更新は一回り終了したということである。よって、かかる場合には、2バイトの初期値カウンタ13bの値を内部レジスタ11bへ書き込み(S36)、その内部レジスタ11bの値を初期値メモリ13c及び乱数カウンタ13aへ書き込んで(S37,S38)、乱数カウンタ13aの更新の初期値を変更する。

【0053】

一方、更新後の内部レジスタ11bの値と初期値メモリ13cの値とが等しくない場合には(S35:No)、乱数カウンタ13aの更新は未だ一回り終了していないので、S36及びS37の処理をスキップして、S32からS34の処理で更新された内部レジスタ11bの値を乱数カウンタ13aへ書き込み(S38)、乱数カウンタ13aの更新を行う。その後は、制御部Cで使用される他の乱数の更新処理を行って(S39)、この乱数更新処理を終了する。

【0054】

図7は、リセット割込処理の残余時間の間に繰り返し実行される初期値カウンタ更新処理のフローチャートである。初期値カウンタ更新処理(S21)では、CPU11の内部レジスタ11bを介して、乱数カウンタ13aの更新の初期値をカウントする初期値カウンタ13bの値を、乱数カウンタ13aの更新範囲の「0〜630(0〜276h)」の範囲内で「+1」ずつ更新する。

【0055】

まず、2バイトで構成される初期値カウンタ13bの値を2バイトの内部レジスタ11bへ書き込む(S41)。内部レジスタ11bの値を1加算し(S42)、加算後の内部レジスタ11bの値が「631」以上であるか否か、即ち、乱数カウンタ13aの更新範囲の値を超えている否かを調べる(S43)。加算後の内部レジスタ11bの値が「631」以上であれば(S43:Yes)、乱数カウンタ13aの更新範囲の値を超えているので、内部レジスタ11bの値を「0」クリアする(S44)。一方、加算後の内部レジスタ11bの値が「630」以下であれば(S43:No)、乱数カウンタ13aの更新範囲内の値であるので、S44の処理をスキップして、S45の処理へ移行する。S45の処理では、更新された内部レジスタ11bの値を、68系CPU11の2バイト書き込み命令によって上位バイト下位バイトの順に初期値カウンタ13bへ書き込むのである。

【0056】

前記した通り、初期値カウンタ更新処理は、リセット割込処理において、次のリセット割込が発生するまでの残余時間の間に繰り返し実行される(S21)。このため、S45の処理によって内部レジスタ11bの上位バイトが初期値カウンタ13bへ書き込まれた後であって下位バイトの書き込み前に2msが経過して、次のユーザーリセット割込が発生するタイミングが到来する場合がある。ユーザーリセット割込は、割込の優先順位が最も高く、割込処理の開始を禁止できないノンマスカブルな割込である。しかし、前記した通り、ユーザーリセット割込の発生は、タイミング回路40によって、2msの経過後の最初のオペコードフェッチのタイミングまでに遅延されるので、CPU11による書き込み命令の実行中に、ユーザーリセット割込が発生してリセット割込処理が実行されることはない。よって、リセット割込処理の残余時間の間に、初期値カウンタ13bの値を繰り返し更新しても、初期値カウンタ13bの値を本来の更新範囲内の値である「0〜630(0〜276h)」の範囲内に維持することができるのである。

【0057】

次に、図8および図9を参照して、第2実施例のタイミング回路50について説明する。第1実施例のタイミング回路40はオペコードフェッチ信号(LIR端子の出力)を利用してユーザーリセット割込を発生させるように構成したが、第2実施例のタイミング回路50は、リード信号(R/Wバー端子のHi出力)を利用してユーザーリセット割込を発生させている。

【0058】

ここで、リード信号は、CPU11によってROM12,RAM13などのメモリに記憶されるデータが読み出されている場合に出力される信号であり、R/Wバー端子からHiの信号として出力される。一方、ライト信号は、CPU11によってRAM13などのメモリへデータの書き込みが行われている場合に出力される信号であり、R/Wバー端子からLowの信号として出力される。詳細には、Eクロック端子の出力がHiレベルである場合に、リード信号およびライト信号は有効となる。このため本実施例では、アンド回路53によってEクロック端子とR/Wバー端子との出力のアンド論理をとって、Dフリップフロップ54のCK端子へ入力するように構成している(図8参照)。

【0059】

よって、リード信号が出力されている間は(アンド回路53からHi信号が出力されている間は)、CPU11によりROM12やRAM13等のデータが読み込まれており、RAM13への書き込みは行われていない。従って、かかるリード信号に同期してユーザーリセット割込を発生させることにより、リセット割込処理の残余時間の間において、初期値カウンタ13bの値を繰り返し更新しても(図5のS21)、次のリセット割込処理が発生する時には、その初期値カウンタ13bの値を書き換えることがなく本来の更新範囲外の値としてしまうことはない。なお、前記した第1実施例と同一の部分には同一の符号を付し、その説明は省略し、異なる部分のみ説明する。

【0060】

オア回路39の出力端は、タイミング回路50のインバータ51の入力端と、HC74で構成されるDフリップフロップ52のD端子に接続されている。タイミング回路50は、リード信号が出力されている間に、ユーザーリセット割込を発生させるための回路である。言い換えれば、タイミング回路50は、ライト信号が出力されている間に、ユーザーリセット割込の発生を禁止するための回路でもある。

【0061】

タイミング回路50のインバータ51の入力端は、前記した通り、オア回路39の出力端に接続されており、そのインバータ51の出力端は、Dフリップフロップ52のPR端子に接続されている。Dフリップフロップ52のCLR端子はVccに接続されているので、CPU11のURES端子に接続されるDフリップフロップ52のQ端子からは、オア回路39からHi出力されている間(K)、Hiが出力され(Q)、ユーザーリセット割込は発生しない。

【0062】

CPU11のR/Wバー端子は、2入力アンド回路53の一つの入力端に接続され、そのアンド回路53の他の入力端はCPU11のEクロック端子に接続されている。更に、アンド回路53の出力端はDフリップフロップ52のCK端子に接続されている。CPU11からリード信号が出力されR/Wバー端子の出力がHiとなった状態で、Eクロックの出力がLowからHiへ立ち上がると(B)、アンド回路53からDフリップフロップ52のCK端子へLowからHiへの立ち上がり信号が出力される(P)。

【0063】

ここで、オア回路39からLowが出力されていると(K)、Dフリップフロップ52のPR端子へHiが入力される(L)。CLR端子にはVccが入力されているので、R/Wバー端子からHiが出力された状態でEクロックの出力がLowからHiへ立ち上がると(B)、Dフリップフロップ52のCK端子への入力がLowからHiへ立ち上がり(P)、その時のD端子へ入力されているLow出力が(K)、Dフリップフロップ52のQ端子からCPU11のURES端子へ出力される(Q)。これにより、リード信号が出力されているタイミングでユーザーリセット割込が発生する。従って、初期値カウンタ13bへの書き込み中に、次のリセット割込処理の実行が開始されることはない。

【0064】

なお、このようにユーザーリセット割込の発生タイミングを、オア回路39の出力がLowとなった後であって、最初のリード信号が出力され、且つ、Eクロック端子の出力が立ち上がるタイミングまで遅延させるように構成しても、オア回路39は確実に2ms毎にLow信号を出力するので(K)、その遅延分が累積してしまうことはない。従って、第2実施例においても、ユーザーリセット割込を2ms毎に発生させ、リセット割込処理を2ms毎に実行することができる。

【0065】

上記各実施例において、請求項1記載の第1更新手段としてはリセット割込処理(図5)のS6の処理が該当し、第2更新手段としてはリセット割込処理(図5)のS21の処理が該当し、定期処理としてはリセット割込処理(図5)のS1〜S19の処理が該当し、所定の処理としてはリセット割込処理(図5)のS20及びS21の処理が該当し、判別手段としてはリセット割込処理(図5)のS2の処理が該当し、初期化手段としてはリセット割込処理(図5)のS22の処理が該当する。

【0066】

以上、実施例に基づき本発明を説明したが、本発明は上記実施例に何ら限定されるものではなく、本発明の趣旨を逸脱しない範囲内で種々の改良変形が可能であることは容易に推察できるものである。

【0067】

以下に本発明の変形例を示す。請求項1記載の遊技機の制御装置において、遊技の制御主体となるCPUを備え、そのCPUからライト信号が出力されている間、前記禁止手段は前記割込処理の新たな発生を禁止することを特徴とする遊技機の制御装置1。

【0068】

請求項1記載の遊技機の制御装置において、遊技の制御主体となるCPUを備え、そのCPUからリード信号が出力されている間に、前記禁止手段は前記割込処理の新たな発生を許容することを特徴とする遊技機の制御装置2。リード信号が出力されている間は、CPUによりメモリのリードが行われメモリへのライトは行われていない。よって、割込処理におけるライト処理の実行時に、その割込処理の新たな発生を禁止することができる。

【0069】

請求項1記載の遊技機の制御装置において、遊技の制御主体となるCPUを備え、そのCPUからオペコードフェッチ信号が出力されている間に、前記禁止手段は前記割込処理の新たな発生を許容することを特徴とする遊技機の制御装置3。オペコードフェッチ信号が出力されている間は、CPUによりオペコードのリードが行われメモリへのライトは行われていない。よって、割込処理におけるライト処理の実行時に、その割込処理の新たな発生を禁止することができる。

【0070】

請求項1記載の遊技機の制御装置、または、遊技機の制御装置1乃至3において、前記割込処理はノンマスカブルなリセット割込処理またはノンマスカブルなユーザーリセット割込処理で構成されていることを特徴とする遊技機の制御装置4。

【0071】

請求項1記載の遊技機の制御装置、または、遊技機の制御装置1乃至4において、乱数カウンタと、その乱数カウンタの値を前記割込処理によって更新する第1更新手段と、所定の契機により前記乱数カウンタの値を読み出す読出手段とを備え、その読出手段により読み出された前記乱数カウンタの値が予め定められた値の1つと一致する場合に、遊技者に所定条件下で所定の遊技価値を付与するものであり、更新中の前記乱数カウンタの初期値を記憶する初期値メモリと、その初期値メモリおよび乱数カウンタに書き込まれる値であって前記乱数カウンタの次回の更新の初期値をカウントする少なくとも2バイトで構成された初期値カウンタと、その初期値カウンタの値を読み出して前記乱数カウンタの更新の範囲内で更新し、更新後の値をその初期値カウンタへ書き込む第2更新手段と、その第2更新手段を前記割込処理によって次回のその割込処理が発生するまでの残余時間の間に繰り返し実行する繰返手段とを備えていることを特徴とする遊技機の制御装置5。

【0072】

遊技機の制御装置5において、前記初期値カウンタの値は、前記乱数カウンタの値が前記初期値メモリの値と一致する場合に、前記乱数カウンタおよび初期値メモリに書き込まれることを特徴とする遊技機の制御装置6。

【0073】

【発明の効果】

本発明の遊技機によれば、「ぶら下げ基板」等による不正行為を防止することができる。

【図面の簡単な説明】

【図1】 本発明の第1実施例におけるパチンコ遊技機の遊技盤の正面図である。

【図2】 パチンコ遊技機の電気的構成を示したブロック図である。

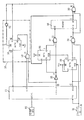

【図3】 ユーザーリセット割込を2msの間隔で発生させる回路のブロック図である。

【図4】 図3の回路のタイミングチャートである。

【図5】 リセット割込処理を示したフローチャートである。

【図6】 乱数更新処理を示したフローチャートである。

【図7】 初期値カウンタ更新処理を示したフローチャートである。

【図8】 第2実施例におけるユーザーリセット割込を2msの間隔で発生させる回路のブロック図である。

【図9】 図8の回路のタイミングチャートである。

【符号の説明】

11 制御部のCPU(制御手段の一部、出力手段、遊技実行手段)

13a 乱数カウンタ(乱数値記憶手段)

13b 初期値カウンタ(初期値記憶手段)

40,50 タイミング回路(定期処理実行遅延手段)

C 制御部(制御手段)

P パチンコ遊技機(遊技機)[0001]

BACKGROUND OF THE INVENTION

The present invention is a gaming machine represented by a pachinko gaming machine or the like.InIt is related.

[0002]

[Prior art]

For exampleThe pachinko gaming machine is provided with a display device capable of variably displaying a plurality of types of symbols, and is configured to start variably displaying when a hit ball that has been driven into the game area passes through the symbol operating gate. When this variable display stops in accordance with a predetermined combination of symbols, it becomes a big hit and a predetermined game value is given to the player.Ru.

[0003]

Whether or not the jackpot is generated is determined at the timing when the hit ball passes the symbol operating gate. That is, it is provided with a random number counter that is periodically updated by 1 count in a certain range (for example, 1 count every 2 ms, in the range of 0 to 630), and when the hit ball passes the symbol operation gate, When the value of the random number counter is read and the read value of the random number counter matches a predetermined value such as “7”, a big hit is generated..

[0004]

However, recently, fraudulent activity using an illegal substrate called “hanging substrate” has been reported. This fraud isBadThe right board is hung (attached with an illegal “hanging board”) to unreasonably generate a big hit. Specifically, a counter (counter that is regularly updated within a certain range in increments of 1 count) within the “hanging board” functioning similarly to the random number counter for determining the jackpot provided in the pachinko gaming machine described above. Set the counter value to power on the pachinko machineetcBy resetting (clearing to 0) at the same time, the occurrence timing of the jackpot in the “hanging board” is grasped. And, in accordance with the grasping timing of the big jackpot, illegally generate the symbol action gate passing signal of the hitting ball in the “hanging board” and output it to the control board of the pachinko machine to generate an unfair jackpot It is to let you. In game halls and the like, a great deal of damage has been caused by fraudulent acts using this "hanging board".

[0005]

[0006]

[0007]

[Problems to be solved by the invention]

[0008]

[0009]

[0010]

The present inventionExample aboveProblemsetcIt was made to solveTo prevent fraud by "hanging board" etc.It aims to provide a game machine that can be used.

[0011]

[Means for Solving the Problems]

In order to achieve this object, the gaming machine according to claim 1,Random number storage means, first update means for updating the value of the random value storage means within a predetermined range, and reading means for reading the value of the random value storage means based on a predetermined trigger, Control means for giving a predetermined game value to the player when the value of the random value storage means read by the reading means matches a predetermined value;,The value of the random value storage means makes a round by being updated a predetermined number of times by the first update means, and the first update means makes the predetermined range when the value of the random value storage means makes a round. One of the values is updated as an initial value for updating, and the control means is updated in the same range as the predetermined range, and the initial value of the random number value storage means is updated. An initial value storage means used for the change, a second update means for reading the value of the initial value storage means, updating the value, and writing the updated value to the initial value storage means, and a periodic signal Output means for outputting a periodic signal, and performing periodic processing based on the periodic signal output by the output means, and after completion of the periodic processing, periodic processing based on the next periodic signal is performed. Predetermined processing repeatedly until In the predetermined process, read, update, and write processes are performed by the second update unit, and the random value storage unit is updated by the first update unit in the regular process. The control means determines whether or not the data in the storage means including the random value storage means and the initial value storage means is valid after power-on, and if the determination means determines that the data is valid A game executing means for executing a game using the data in the storage means, an initialization means for initializing the data in the storage means if determined by the determining means, and the second update When a periodic signal is output from the output means during execution of the writing process by the means, the execution of the periodic process based on the periodic signal is delayed, and the writing process Even when the execution of the predetermined periodic process is delayed by the periodic process execution delay means, the execution unit has a periodic process execution delay means for executing the periodic process whose execution is delayed after the execution is completed. The output of the periodic signal output from the output means for executing the next periodic processing is not delayed..

[0012]

Claim2Listed gaming machinesIn the gaming machine according to claim 1,,The gaming machine is a pachinko gaming machine.

[0013]

DETAILED DESCRIPTION OF THE INVENTION

Hereinafter, preferred embodiments of the present invention will be described with reference to the accompanying drawings. In the present embodiment, description will be made using a pachinko gaming machine as an example of a gaming machine, in particular, a first type pachinko gaming machine. Note that it is naturally possible to use the present invention for other gaming machines such as a third type pachinko gaming machine and a slot machine.

[0014]

FIG. 1 is a front view of a game board of a pachinko gaming machine P in the first embodiment. Around the game board 1, there are provided a plurality of winning holes 2 through which 5 to 15 game balls are paid out by winning a hit ball. In the center of the game board 1, a liquid crystal (LCD) display 3 for displaying symbols as a plurality of types of identification information is provided. The display screen of the

[0015]

Below the

[0016]

FIG. 2 is a block diagram showing an electrical configuration of the pachinko gaming machine P. As shown in FIG. The control unit C of the pachinko gaming machine P includes a

[0017]

The

[0018]

The 68-system 8-

[0019]

The

[0020]

The initial value counter 13b is a counter for counting the initial value of the update of the random number counter 13a, and is composed of 2 bytes like the random number counter 13a. The value of the initial value counter 13b is updated by one count in the range of “0 to 630 (276h)” that is the same as the update range of the random number counter 13a by the initial value counter update process (S21) of FIG.

[0021]

The initial value counter update process of FIG. 7 is repeated during the remaining time in the reset interrupt process of FIG. 5, that is, after the end of the sound effect process (S19) until the next reset interrupt process occurs. It is executed (S21). The reset interrupt process is executed every 2 ms, but the processing time of each process from S1 to S19 executed in one reset interrupt process changes depending on the game situation. The remaining time is not a fixed time but an indefinite time that changes according to the game situation. Since the “hanging board” cannot grasp the indefinite time, the value of the initial value counter 13b that is repeatedly updated within the indefinite time is used as the initial value for updating the random number counter 13a. It is impossible to grasp the timing of jackpot occurrence by “substrate”.

[0022]

The initial value memory 13c is a memory for storing an initial value of update of the random number counter 13a, and is composed of 2 bytes like the random number counter 13a. In this embodiment, the initial value of the update of the random number counter 13a is changed every time the random number counter is updated once. Therefore, when the updated value of the random number counter 13a matches the value of the initial value memory 13c, one round of updating of the random number counter 13a is completed, so that when the two values 13a and 13c match, The initial value counter 13b is written into the random number counter 13a and the initial value memory 13c, and the initial value of the update of the random number counter 13a is changed. Therefore, even if the initial value of the update of the random number counter 13a is changed, the randomness is uniform (the same value is not obtained when continuously acquired, and all values can be extracted with the same probability). A random value can be obtained.

[0023]

The

[0024]

The display device D includes a

[0025]

The

[0026]

Next, with reference to FIG. 3 and FIG. 4, the occurrence timing of the user reset interrupt that triggers the execution of the reset interrupt process of FIG. 5 will be described. This user reset interrupt is generated every 2 ms and at the timing when the opcode fetch signal is output by the

[0027]

While the operation code fetch signal is being output, the operation code is read from the

[0028]

A

[0029]

In addition, a 8.1920 MHz oscillator (clock) 32 is connected to the

[0030]

The output terminal of the

[0031]

The Q bar output terminal of the D flip-

[0032]

On the other hand, the E clock terminal of the

[0033]

The Q output of the D flip-

[0034]

In addition to being connected to the D terminal of the D flip-

[0035]

The OR

[0036]

In the prior art, the output terminal of the

[0037]

The output terminal of the

[0038]

As described above, the input terminal of the

[0039]

The LIR terminal of the

[0040]

Here, when Low is output from the OR circuit 39 (K), Hi is input to the PR terminal of the D flip-flop 42 (L). Since Vcc is input to the CLR terminal, when the operation code fetch signal is output from the

[0041]

Even if the user reset interrupt generation timing is delayed until the first opcode fetch timing in this way, the

[0042]

Next, each process executed by the pachinko gaming machine P configured as described above will be described with reference to the flowcharts of FIGS. FIG. 5 is a flowchart of reset interrupt processing executed every 2 ms in the control unit C of the pachinko gaming machine P. The main control of the pachinko gaming machine P is executed by this reset interrupt process. This reset interrupt process is executed when a reset interrupt occurs when the power is turned on and when the above-described user reset interrupt occurs.

[0043]

In the reset interrupt process, first, a stack pointer is set (S1), and a pattern written in a predetermined area of the

[0044]

In the process of S3, a timer interrupt is set (S3). The timer interrupt set here includes a timer interrupt that generates a strobe signal for transmitting a command for controlling the display of the

[0045]

In the switch reading process (S8), the value of each switch is read to win the winning ball 2 and the big winning hole 5 (including the V zone 5a) of the ball that has been driven into the game area 1, This is a process for detecting passing, and also winning balls and rental balls. The count abnormality monitoring process (S9) is a process for monitoring whether there is an abnormality in the switch data read by the switch reading process of S8. For example, even though the big winning opening 5 is opened and a hit ball is detected by the V count switch that detects the passing of the hit ball through the V zone 5a, the winning in the big winning openings 5 other than the V zone 5a is detected 10 When a single shot cannot be detected by the count switch, some abnormality has occurred in the 10 count switch, such as the 10 count switch being pulled out or broken. Further, when a single prize ball is not paid out even though the motor for paying out a prize ball is driven, some abnormality has occurred in the prize ball payout device. As described above, in the count abnormality monitoring process (S9), the presence / absence of the abnormality as described above is monitored based on the switch data read by the switch reading process (S8).

[0046]

In the symbol counter update process (S10), a counter update process for determining a symbol to be stopped and displayed as a result of the variable display performed on the

[0047]

If no error has occurred in the processing from S3 to S11 (S12: normal), the normal symbol variation processing (S13) displays the variation of the 7-segment LED, and the variation display results in a win. In this case, a hit process for releasing a normal electric accessory (not shown) for a predetermined time is executed. Thereafter, the state flag is checked (S14), and if the change of the symbol on the

[0048]

In the display data creation process (S17), demo data displayed on the

[0049]

After the sound effect process (S19) ends, during the remaining time until the next reset interrupt process occurs, the symbol counter update process (S20), which is the same process as S10, and the initial value counter update process (S21) ) And repeatedly. Since the execution time of each process of S1-S19 changes according to the state of the game, the remaining time until the next reset interrupt process (next user reset interrupt) occurs is not a fixed time, but a game It changes according to the state. Therefore, by repeatedly executing the symbol counter update process (S20) using the remaining time, the stop symbol can be changed at random. Further, by repeatedly executing the initial value counter update process (S21) using the remaining time, the value of the initial value counter 13b that is the initial value of the update of the random number counter 13a cannot be grasped by the “hanging board”. can do.

[0050]

FIG. 6 is a flowchart of random number update processing. In the random number updating process (S6), the value of the random number counter 13a is updated by “+1” within the range of “0 to 630 (0 to 276h)” via the

[0051]

First, the value of the random number counter 13a composed of 2 bytes is written to the 2-byte

[0052]

In the process of S35, the updated value of the

[0053]

On the other hand, when the updated value of the

[0054]

FIG. 7 is a flowchart of the initial value counter update process that is repeatedly executed during the remaining time of the reset interrupt process. In the initial value counter update process (S21), the value of the initial value counter 13b that counts the initial value of the update of the random number counter 13a is set via the

[0055]

First, the value of the initial value counter 13b composed of 2 bytes is written to the 2-byte

[0056]

As described above, the initial value counter update process is repeatedly executed during the remaining time until the next reset interrupt occurs in the reset interrupt process (S21). For this reason, after the upper byte of the

[0057]

Next, the

[0058]

Here, the read signal is a signal output when data stored in a memory such as the

[0059]

Therefore, while the read signal is output (while the Hi signal is output from the AND circuit 53), the data in the

[0060]

The output terminal of the

[0061]

As described above, the input terminal of the

[0062]

The R / W bar terminal of the

[0063]

Here, when Low is output from the OR circuit 39 (K), Hi is input to the PR terminal of the D flip-flop 52 (L). Since Vcc is input to the CLR terminal, when the output of the E clock rises from Low to Hi while Hi is output from the R / W bar terminal (B), the input to the CK terminal of the D flip-

[0064]

In this way, the occurrence timing of the user reset interrupt is delayed until the first read signal is output and the output of the E clock terminal rises after the output of the

[0065]

In each of the embodiments described above,The first update means corresponds to the process of S6 of the reset interrupt process (FIG. 5), the second update means corresponds to the process of S21 of the reset interrupt process (FIG. 5), and the periodic process includes the reset interrupt process. 5 corresponds to the processes of S1 to S19 of the interrupt process (FIG. 5), the processes of S20 and S21 of the reset interrupt process (FIG. 5) correspond to the predetermined process, and the reset interrupt process (FIG. 5). ) Of S2 corresponds to the initialization process, and the process of S22 of the reset interrupt process (FIG. 5) is used as initialization means.Is applicable.

[0066]

The present invention has been described above based on the embodiments. However, the present invention is not limited to the above embodiments, and various modifications can be easily made without departing from the spirit of the present invention. It can be guessed.

[0067]

The modification of this invention is shown below. 2. The gaming machine control device according to claim 1, further comprising: a CPU that is a game controlling entity, and the prohibiting means prohibits new generation of the interrupt process while a write signal is output from the CPU. A control device 1 of a gaming machine characterized by the above.

[0068]

2. The gaming machine control device according to claim 1, further comprising: a CPU that is a game controlling entity, and the prohibiting means permits a new generation of the interrupt process while a read signal is output from the CPU. A control device 2 of a gaming machine characterized by the above. While the read signal is output, the CPU reads the memory and does not write to the memory. Therefore, when the write process is executed in the interrupt process, new generation of the interrupt process can be prohibited.

[0069]

2. The gaming machine control device according to claim 1, further comprising a CPU which is a game controlling entity, and the prohibiting means allows a new generation of the interrupt process while an opcode fetch signal is output from the CPU. A game

[0070]

2. The gaming machine control device according to claim 1, or the gaming machine control devices 1 to 3, wherein the interrupt process is configured by a non-maskable reset interrupt process or a non-maskable user reset interrupt process. A control device 4 for the gaming machine.

[0071]

2. The gaming machine control device according to claim 1, or the gaming machine control devices 1 to 4, wherein a random number counter, first update means for updating the value of the random number counter by the interrupt processing, and a predetermined trigger Reading means for reading the value of the random number counter, and when the value of the random number counter read by the reading means matches one of the predetermined values, the player is given a predetermined game under predetermined conditions. An initial value memory for storing an initial value of the random number counter being updated, and a value written to the initial value memory and the random number counter, and an initial value for the next update of the random number counter. An initial value counter composed of at least 2 bytes to be counted, and the value of the initial value counter is read and updated within the update range of the random number counter. A second updating means for writing to the initial value counter; and a repeating means for repeatedly executing the second updating means during the remaining time until the next interruption processing is generated by the interruption processing. A control device 5 of a gaming machine characterized by the above.

[0072]

In the gaming machine control device 5, the value of the initial value counter is written in the random number counter and the initial value memory when the value of the random number counter matches the value of the initial value memory. Control device 6 of the machine.

[0073]

【The invention's effect】

According to the gaming machine of the present invention,Can prevent fraudulent acts such as "hanging board".

[Brief description of the drawings]

FIG. 1 is a front view of a game board of a pachinko gaming machine according to a first embodiment of the present invention.

FIG. 2 is a block diagram showing an electrical configuration of a pachinko gaming machine.

FIG. 3 is a block diagram of a circuit for generating a user reset interrupt at intervals of 2 ms.

4 is a timing chart of the circuit of FIG.

FIG. 5 is a flowchart showing reset interrupt processing;

FIG. 6 is a flowchart showing random number update processing.

FIG. 7 is a flowchart showing an initial value counter update process.

FIG. 8 is a block diagram of a circuit for generating a user reset interrupt at an interval of 2 ms in the second embodiment.

FIG. 9 is a timing chart of the circuit of FIG.

[Explanation of symbols]

11 CPU of control unit(Part of control means, output means, game execution means)

13a random number counter(Random value storage means)

13b Initial value counter(Initial value storage means)

40, 50 Timing circuit (Periodic processing execution delaymeans)

C control unit(Control means)

P Pachinko machine (game machine)

Claims (2)

前記乱数値記憶手段の値は、前記第1更新手段により所定回更新されることで一周するものであり、

前記第1更新手段は、前記乱数値記憶手段の値が一周すると、前記所定の範囲内のいずれかの値を更新の初期値として次の周の更新を行うものであり、

前記制御手段は、

前記所定の範囲と同じ範囲で更新され、前記乱数値記憶手段の更新の初期値の変更に使用される初期値記憶手段と、

その初期値記憶手段の値を読み出して、その値を更新し、更新された値を前記初期値記憶手段へ書き込む第2更新手段と、

定期的な信号である定期信号を出力する出力手段とを有し、

その出力手段が出力する定期信号に基づいて定期処理を行うとともに、その定期処理の終了の後、次の定期信号に基づく定期処理が行われるまでの期間に繰り返し所定の処理を行うものであり、

その所定の処理において、前記第2更新手段による、読み出し、更新、および書き込み処理が行われ、

前記第1更新手段による前記乱数値記憶手段の更新は、前記定期処理において行われ、

前記制御手段は、

電源投入後に前記乱数値記憶手段と前記初期値記憶手段とを含む記憶手段のデータが有効か否かを判別する判別手段と、

その判別手段により有効と判別された場合に、前記記憶手段のデータを使用して遊技を実行する遊技実行手段と、

その判別手段により有効でないと判別された場合に、前記記憶手段のデータを初期化する初期化手段と、

前記第2更新手段による書き込み処理の実行時に、前記出力手段から定期信号が出力される場合に、その定期信号に基づく定期処理の実行を遅延させ、かつ、その書き込み処理の実行が終了した後に、実行が遅延された定期処理を実行する定期処理実行遅延手段とを有しており、

その定期処理実行遅延手段により所定の定期処理の実行が遅延された場合であっても、次の定期処理を実行するために前記出力手段から出力される定期信号の出力は遅延されないものであることを特徴とする遊技機。 Random number storage means, first update means for updating the value of the random value storage means within a predetermined range, and reading means for reading the value of the random value storage means based on a predetermined trigger, In a gaming machine comprising control means for giving a predetermined game value to a player when the value of the random number storage means read by the reading means matches a predetermined value ,

The value of the random value storage means is rotated once by being updated a predetermined number of times by the first update means,

When the value of the random number storage means goes around once, the first update means updates the next round using any value within the predetermined range as an initial value of the update,

The control means includes

An initial value storage means that is updated in the same range as the predetermined range and is used to change the initial value of the update of the random value storage means;

A second updating means for reading the value of the initial value storage means, updating the value, and writing the updated value to the initial value storage means;

Output means for outputting a periodic signal that is a periodic signal;

The periodic processing is performed based on the periodic signal output by the output means, and the predetermined processing is repeatedly performed during the period until the periodic processing based on the next periodic signal is performed after the termination of the periodic processing,

In the predetermined process, read, update, and write processes are performed by the second update unit,

The update of the random value storage means by the first update means is performed in the regular processing,

The control means includes

Determining means for determining whether or not the data in the storage means including the random value storage means and the initial value storage means is valid after power-on;

A game execution means for executing a game using the data of the storage means when determined to be valid by the determination means;

An initialization means for initializing data in the storage means when it is determined that the determination means is not valid;

When a periodic signal is output from the output means during execution of the writing process by the second update means, the execution of the periodic process based on the periodic signal is delayed, and after the execution of the writing process is completed, Periodic processing execution delay means for executing periodic processing whose execution is delayed,

Even when the execution of a predetermined periodic process is delayed by the periodic process execution delay means, the output of the periodic signal output from the output means for executing the next periodic process is not delayed. A gaming machine characterized by

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP07766599A JP4399890B2 (en) | 1999-03-23 | 1999-03-23 | Game machine |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP07766599A JP4399890B2 (en) | 1999-03-23 | 1999-03-23 | Game machine |

Related Child Applications (5)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003306825A Division JP4124062B2 (en) | 2003-08-29 | 2003-08-29 | Game machine |

| JP2008111136A Division JP4450255B2 (en) | 2008-04-22 | 2008-04-22 | Game machine |

| JP2008195789A Division JP4725615B2 (en) | 2008-07-30 | 2008-07-30 | Game machine |

| JP2008195790A Division JP4683086B2 (en) | 2008-07-30 | 2008-07-30 | Game machine |

| JP2008195791A Division JP4683087B2 (en) | 2008-07-30 | 2008-07-30 | Game machine |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000271326A JP2000271326A (en) | 2000-10-03 |

| JP2000271326A5 JP2000271326A5 (en) | 2006-05-11 |

| JP4399890B2 true JP4399890B2 (en) | 2010-01-20 |

Family

ID=13640186

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP07766599A Expired - Lifetime JP4399890B2 (en) | 1999-03-23 | 1999-03-23 | Game machine |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4399890B2 (en) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3907926B2 (en) * | 2000-08-09 | 2007-04-18 | 株式会社三共 | Game machine |

| JP3907928B2 (en) * | 2000-08-22 | 2007-04-18 | 株式会社三共 | Game machine |

| JP3907929B2 (en) * | 2000-08-24 | 2007-04-18 | 株式会社三共 | Game machine |

| JP3907931B2 (en) * | 2000-09-11 | 2007-04-18 | 株式会社三共 | Game machine |

| JP4540840B2 (en) * | 2000-12-28 | 2010-09-08 | 株式会社三共 | Game machine |

| JP4911545B2 (en) * | 2001-08-01 | 2012-04-04 | サミー株式会社 | Control device for gaming machine |

| JP4754127B2 (en) * | 2001-09-25 | 2011-08-24 | 株式会社三共 | Game machine |

| JP4510859B2 (en) * | 2007-08-23 | 2010-07-28 | 株式会社藤商事 | Game machine |

| JP4916558B2 (en) * | 2010-03-01 | 2012-04-11 | 株式会社三共 | Game machine |

| JP5307062B2 (en) * | 2010-03-18 | 2013-10-02 | 株式会社三共 | Game machine |

| JP5164191B2 (en) * | 2011-05-18 | 2013-03-13 | サミー株式会社 | Control device for gaming machine |

-

1999

- 1999-03-23 JP JP07766599A patent/JP4399890B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000271326A (en) | 2000-10-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4399890B2 (en) | Game machine | |

| JP3885367B2 (en) | Random number generation circuit and gaming machine including the random number generation circuit | |

| JP2000271326A5 (en) | ||

| JP3888221B2 (en) | CONTROL DEVICE AND GAME MACHINE HAVING THE CONTROL DEVICE | |

| JP4124062B2 (en) | Game machine | |

| JP4450255B2 (en) | Game machine | |

| JP5278501B2 (en) | Bullet ball machine | |

| JP4683086B2 (en) | Game machine | |

| JP4725615B2 (en) | Game machine | |

| JP4683087B2 (en) | Game machine | |

| JP2004008807A5 (en) | ||

| JP4033083B2 (en) | Game machine | |

| JP5360022B2 (en) | Game machine | |

| JP4379936B2 (en) | Bullet ball machine | |

| JP4407209B2 (en) | Bullet ball machine | |

| JP2008178745A5 (en) | ||

| JP2004000755A5 (en) | ||

| JP3951482B2 (en) | Game machine | |

| JP4868059B2 (en) | Bullet ball machine | |

| JP4450259B2 (en) | Bullet ball machine | |

| JP4293218B2 (en) | Game machine | |

| JP5382039B2 (en) | Bullet ball machine | |

| JP4626641B2 (en) | Bullet ball machine | |

| JP4375475B2 (en) | Bullet ball machine | |

| JP4626640B2 (en) | Bullet ball machine |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060315 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060315 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20070302 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090428 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090629 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091006 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091019 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121106 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121106 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151106 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |