JP4390728B2 - ネットリスト生成装置 - Google Patents

ネットリスト生成装置 Download PDFInfo

- Publication number

- JP4390728B2 JP4390728B2 JP2005048775A JP2005048775A JP4390728B2 JP 4390728 B2 JP4390728 B2 JP 4390728B2 JP 2005048775 A JP2005048775 A JP 2005048775A JP 2005048775 A JP2005048775 A JP 2005048775A JP 4390728 B2 JP4390728 B2 JP 4390728B2

- Authority

- JP

- Japan

- Prior art keywords

- memory cell

- circuit

- net list

- information

- cell array

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/20—Design optimisation, verification or simulation

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Computer Hardware Design (AREA)

- Evolutionary Computation (AREA)

- Geometry (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Description

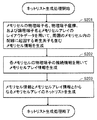

本発明の実施形態では、図1に示すように複数個のメモリセルが繰返し配列されることによってメモリセルアレイが構成されていることを利用して、階層的な処理によってメモリセルアレイの配線寄生素子付きネットリストを生成する。すなわち、メモリセル単体について配線寄生素子を特定して、それを組み合わせることによってメモリセルアレイのネットリストを生成する。

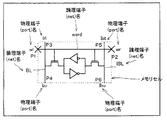

図3は、第1の実施形態に係るネットリスト生成装置の構成を示す機能ブロック図である。

次に、第1の実施形態に係るネットリスト生成装置の動作を説明する。

第2の実施形態は、周囲のメモリセル内の配線に起因するものも含めて、メモリセルの配線寄生素子を特定するネットリスト生成装置に関する。

図12は、第2の実施形態に係るネットリスト生成装置の構成を示す機能ブロック図である。

次に、第2の実施形態に係るネットリスト生成装置の動作を説明する。

本変形例は、第2の実施形態の寄生素子についての情報の生成の変形例である。

第3の実施形態は、周辺回路ブロックとメモリセルアレイと有するメモリ装置のネットリストを生成するネットリスト生成装置に関する。

図17は、第3の実施形態に係るネットリスト生成装置の構成を示す機能ブロック図である。

次に、第3の実施形態に係るネットリスト生成装置の動作を説明する。

本発明は、上記の実施形態に限定されるものではなく、たとえば以下のような変形例も含む。

図21は、第2の実施形態の変形例をさらに変形させたメモリセルの配線寄生素子の特定方法を説明するための図である。

本発明の実施形態では、図1に示すように複数個のメモリセルが繰返し配列されることによってメモリセルアレイが構成されていることを利用して、階層的な処理によってメモリセルアレイの配線寄生素子付きネットリストを生成することとしたが、これに限定するものではない。第1の回路の繰返しで第2の回路が構成されるような場合には、本発明の実施形態のネットリスト生成装置によって、第2の回路の配線寄生素子付きネットリストを生成することができる。

本発明の実施の形態では、ネットリスト生成装置1,11,31と、回路配置装置およびレイアウト装置とは別物としたが、これに限定するものではない。ネットリスト生成装置1,11,31が回路配置装置の機能を実行する回路配置部と、レイアウト装置の機能を実行するレイアウト部を含むものとしてもよい。

本発明の実施形態のネットリスト生成装置1,11,31は、専用のハードウエアで構成された装置に限定するものではない。コンピュータがプログラムを実行することによって、ネットリスト生成装置1,11,31の各構成要素の機能を実行するものとしてもよい。

メモリセル情報の生成と同様の方法で、周辺回路ブロックのネットリストを生成してもよい。すなわち、周辺回路ブロックネットリスト生成部32は、レイアウト装置からレイアウトデータを取得し、回路配置装置から周辺回路ブロックの物理端子座標、物理端子名および論理端子名を取得して、取得したこれらのデータに基づいて、周辺回路ブロックの配線に寄生する容量成分(C)および抵抗成分(R)からなる寄生素子を特定する。すなわち、周辺回路ブロックネットリスト生成部32は、取得した物理端子座標に対応するレイアウトデータの位置に物理端子名を割当てるとともに、論理端子名で表わされる配線についてレイアウトデータに基づいて配線寄生素子を特定する。このように、物理端子名を割当てることによって、配線寄生素子抽出前の周辺回路ブロックの位置を特定することが可能となる。

Claims (5)

- 第1の回路の繰返しで構成される第2の回路の配線寄生素子付きネットリストを生成するネットリスト生成装置であって、

前記第1の回路の物理端子座標、物理端子名および論理端子名とレイアウトデータを取得して、前記取得した物理端子座標、物理端子名、論理端子名およびレイアウトデータに基づいて、前記第1の回路の配線に寄生する寄生素子の特定、および前記物理端子名を含み前記第1の回路の内部の素子および前記寄生素子についての物性および接続関係を表わした第1回路情報の生成を行なう第1回路情報生成部と、

前記第2の回路に含まれるすべての前記第1の回路の物理端子の接続関係を定めた接続情報を取得して、前記接続情報に基づいて、前記第2の回路に含まれるすべての前記第1の回路の物理端子にノード名を割当てて、前記第2の回路の含まれるすべての第1の回路のノード名を表わした第2回路情報を生成する第2回路情報生成部と、

前記第1回路情報と前記第2回路情報とからなる前記第2の回路のネットリストを生成する第2回路ネットリスト生成部とを備えるネットリスト生成装置。 - 前記第1の回路はメモリセルであり、前記第2の回路は前記メモリセルの繰返しで構成されるメモリセルアレイである、請求項1記載のネットリスト生成装置。

- 前記第1回路情報生成部は、前記メモリセルの配線と前記メモリセルの周囲にある周囲メモリセルの配線との間で発生する寄生素子も含めて、前記メモリセルの配線の寄生素子を特定する、請求項2記載のネットリスト生成装置。

- 前記第1回路情報生成部は、前記周囲メモリセルの配線をグランドに接続されるものとみなして、前記メモリセルの配線の寄生素子を特定する、請求項3記載のネットリスト生成装置。

- 前記ネットリスト生成装置は、さらに、

前記メモリセルアレイの周辺回路ブロックのネットリストを生成する周辺回路ブロックネットリスト生成部と、

前記メモリセルアレイと前記周辺回路ブロックの物理端子の接続関係を定めた接続情報を取得して、前記取得した接続情報に基づいて、前記メモリセルアレイおよび前記周辺回路ブロックの物理端子にノード名を割当てて、前記メモリセルアレイおよび前記周辺回路ブロックのノード名を表わしたメモリセルアレイ/周辺回路ブロック情報を生成するメモリセルアレイ/周辺回路ブロック情報生成部と、

前記メモリセルアレイのネットリストと、前記周辺回路ブロックのネットリストと、前記メモリセルアレイ/周辺回路ブロック情報とからなるメモリ装置のネットリストを生成するメモリ装置ネットリスト生成部とを備える、請求項2記載のネットリスト生成装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005048775A JP4390728B2 (ja) | 2005-02-24 | 2005-02-24 | ネットリスト生成装置 |

| TW095104992A TW200643753A (en) | 2005-02-24 | 2006-02-15 | Net list producing device |

| US11/358,101 US7398506B2 (en) | 2005-02-24 | 2006-02-22 | Net list producing device producing a net list with an interconnection parasitic element by hierarchical processing |

| US12/213,623 US7979817B2 (en) | 2005-02-24 | 2008-06-23 | Net list producing device producing a net list with an interconnection parasitic element by hierarchical processing |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005048775A JP4390728B2 (ja) | 2005-02-24 | 2005-02-24 | ネットリスト生成装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006235920A JP2006235920A (ja) | 2006-09-07 |

| JP2006235920A5 JP2006235920A5 (ja) | 2008-01-10 |

| JP4390728B2 true JP4390728B2 (ja) | 2009-12-24 |

Family

ID=36914335

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005048775A Expired - Fee Related JP4390728B2 (ja) | 2005-02-24 | 2005-02-24 | ネットリスト生成装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US7398506B2 (ja) |

| JP (1) | JP4390728B2 (ja) |

| TW (1) | TW200643753A (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7890892B2 (en) * | 2007-11-15 | 2011-02-15 | International Business Machines Corporation | Balanced and bi-directional bit line paths for memory arrays with programmable memory cells |

| US7913216B2 (en) | 2008-02-16 | 2011-03-22 | International Business Machines Corporation | Accurate parasitics estimation for hierarchical customized VLSI design |

| US7962877B2 (en) * | 2008-08-05 | 2011-06-14 | International Business Machines Corporation | Port assignment in hierarchical designs by abstracting macro logic |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11186398A (ja) | 1997-12-19 | 1999-07-09 | Sharp Corp | 半導体集積回路の回路シミュレーションを行うためのデータ作成方法及びデータ作成システム |

| JP2002009260A (ja) | 2000-06-26 | 2002-01-11 | Hitachi Ltd | 半導体装置の設計方法 |

| US6405351B1 (en) * | 2000-06-27 | 2002-06-11 | Texas Instruments Incorporated | System for verifying leaf-cell circuit properties |

| US6865726B1 (en) * | 2001-10-22 | 2005-03-08 | Cadence Design Systems, Inc. | IC layout system employing a hierarchical database by updating cell library |

| JP2004094402A (ja) | 2002-08-29 | 2004-03-25 | Matsushita Electric Ind Co Ltd | 遅延シミュレーション用ネットリスト生成システムおよび遅延シミュレーション用ネットリスト生成方法 |

-

2005

- 2005-02-24 JP JP2005048775A patent/JP4390728B2/ja not_active Expired - Fee Related

-

2006

- 2006-02-15 TW TW095104992A patent/TW200643753A/zh unknown

- 2006-02-22 US US11/358,101 patent/US7398506B2/en not_active Expired - Fee Related

-

2008

- 2008-06-23 US US12/213,623 patent/US7979817B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7979817B2 (en) | 2011-07-12 |

| TW200643753A (en) | 2006-12-16 |

| JP2006235920A (ja) | 2006-09-07 |

| US7398506B2 (en) | 2008-07-08 |

| US20060190898A1 (en) | 2006-08-24 |

| US20080270967A1 (en) | 2008-10-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10140396B1 (en) | Partitioning electronic circuits for simulation on multiple processors | |

| US9361415B1 (en) | Method, system, and computer program product for implementing a multi-fabric electronic design spanning across multiple design fabrics | |

| US9501593B2 (en) | Semiconductor device design method, system and computer program product | |

| TWI627547B (zh) | 用於ic設計協定的自動化功能覆蓋生成和管理的系統和方法 | |

| CN100456308C (zh) | 断言产生系统、电路验证系统以及断言产生方法 | |

| TWI770081B (zh) | 用於設計積體電路的計算系統與電腦實施方法 | |

| US10713410B2 (en) | Method for legalizing mixed-cell height standard cells of IC | |

| US8234612B2 (en) | Cone-aware spare cell placement using hypergraph connectivity analysis | |

| US10558772B1 (en) | Partitioning a system graph for circuit simulation to obtain an exact solution | |

| US20150234978A1 (en) | Cell Internal Defect Diagnosis | |

| JP5699768B2 (ja) | 回路シミュレーション方法および回路シミュレーション装置 | |

| JP4390728B2 (ja) | ネットリスト生成装置 | |

| JP2015166981A (ja) | レイアウト検証方法、検証装置、及び検証プログラム | |

| US9129079B1 (en) | Solving a circuit network in hierarchical, multicore, and distributed computing environment | |

| US20100095262A1 (en) | Schematic Generation From Analog Netlists | |

| Huang et al. | A robust ECO engine by resource-constraint-aware technology mapping and incremental routing optimization | |

| US9293450B2 (en) | Synthesis of complex cells | |

| US8726218B2 (en) | Transistor-level layout synthesis | |

| WO2014205114A1 (en) | Automated circuit triplication method and system | |

| US20060136851A1 (en) | Method for the generation of static noise check data | |

| US8819086B2 (en) | Naming methodologies for a hierarchical system | |

| JP6146224B2 (ja) | 判定方法、判定プログラム、および判定装置 | |

| CN117807948B (zh) | 顶层网表文件的生成方法、装置、计算机设备及存储介质 | |

| JP2011028644A (ja) | 電源ノイズ解析方法及び電源ノイズ解析プログラム | |

| CN113779923A (zh) | 具有最佳化胞元布置的装置布局 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071116 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071116 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090929 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091006 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121016 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4390728 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121016 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121016 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121016 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131016 Year of fee payment: 4 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |