JP4355443B2 - 2重デジタル低if複合受信機 - Google Patents

2重デジタル低if複合受信機 Download PDFInfo

- Publication number

- JP4355443B2 JP4355443B2 JP2000389165A JP2000389165A JP4355443B2 JP 4355443 B2 JP4355443 B2 JP 4355443B2 JP 2000389165 A JP2000389165 A JP 2000389165A JP 2000389165 A JP2000389165 A JP 2000389165A JP 4355443 B2 JP4355443 B2 JP 4355443B2

- Authority

- JP

- Japan

- Prior art keywords

- components

- signal

- bandwidth

- communication receiver

- digital

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/69—Spread spectrum techniques

- H04B1/707—Spread spectrum techniques using direct sequence modulation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/06—Receivers

- H04B1/16—Circuits

- H04B1/30—Circuits for homodyne or synchrodyne receivers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

- H03D7/16—Multiple-frequency-changing

- H03D7/165—Multiple-frequency-changing at least two frequency changers being located in different paths, e.g. in two paths with carriers in quadrature

- H03D7/166—Multiple-frequency-changing at least two frequency changers being located in different paths, e.g. in two paths with carriers in quadrature using two or more quadrature frequency translation stages

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/38—Transceivers, i.e. devices in which transmitter and receiver form a structural unit and in which at least one part is used for functions of transmitting and receiving

- H04B1/40—Circuits

- H04B1/403—Circuits using the same oscillator for generating both the transmitter frequency and the receiver local oscillator frequency

- H04B1/406—Circuits using the same oscillator for generating both the transmitter frequency and the receiver local oscillator frequency with more than one transmission mode, e.g. analog and digital modes

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Power Engineering (AREA)

- Digital Transmission Methods That Use Modulated Carrier Waves (AREA)

- Compression, Expansion, Code Conversion, And Decoders (AREA)

Description

【発明の属する技術分野】

この発明は通信受信機に関し、かつより特定的には広帯域符号分割多元接続(Wide Band Code Division Multiple Access:WBCDMA)のようなあるモードにおける広帯域信号を、かつまた、欧州セルラ電話システムGSM(グローバル・システム・モービル:Global System Mobile)が1つの例である、時分割多元接続(TDMA)のような他のモードに対する中帯域または狭帯域信号を受信することができる受信機に関する。

【0002】

【従来の技術】

今日の通信システム、例えばセルラ電話通信システム、は狭帯域または中帯域技術で動作する。前記GSMセルラ電話システム、時分割多元接続(TDMA)システム、はそのような中帯域システムの1つである。例えば、データまたはビデオ伝送に対するより高速の送信の要求が増大するに応じて、より広い帯域の技術がより望ましいものになってくる。セルラ通信のための1つのそのような広帯域技術は広帯域符号分割多元接続(WBCDMA)である。新しい技術が発展するに応じて、1つより多くの通信システムで動作して1つのシステムから他のものへと推移できるようにしあるいはユーザが両方のシステムの組み合わされた能力および特徴(フィーチャ:features)へとアクセスできるようにする通信機器を提供することが一般的になっている。したがって、通信受信機が狭帯域または中帯域のシステムからかつまた広帯域通信システムの双方から信号を受信できることが必要とされる。

【0003】

単一の広帯域および中帯域受信機を提供するための今日の努力は各々のモードに対して異なる受信機データ経路を提供することによって各々のモードに対する受信機回路を単に2重化した受信機設計を生じる結果となっている。一例として、ヨーロッパにおいて現在開発されている前記広帯域CDMAシステム、万能移動電話システム(Universal Mobile Telephone System:UMTS)、においては、チャネル帯域幅は3.84MHzであり、一方現在の欧州セルラシステム、GSM、は200KHzの帯域幅を有している。これらのシステムの双方はIQ変調モードで動作し、その場合送信されるべき情報は、適切に符号化された後、キャリヤ信号に重畳された同相および直角位相変調成分において提供され複素信号または複合信号を生成し、これはその後受信機によってデコードされて元の符号化された情報を出現させることになる。

【0004】

【発明が解決しようとする課題】

現在これら2つのモードは異なるダウンコンバージョン・ミキサ、ブロッキング・フィルタ、増幅器、アンチエイリアシング・フィルタ(antialiasing filters)、およびアナログ−デジタル変換器を備えた2つの異なる受信機回路を設けることによって1つの通信受信機ユニット内へと組み合わされている。前記受信機回路の各々は従って送信された信号のIおよびQ成分を受信しかつデコードすることができる別個の受信機である。

【0005】

したがって、いくつかのモードで動作可能でありかつ回路の多くの要素が各モードで使用可能であり、従って受信機において必要な回路の数を低減することにより受信機の複雑さを低減する単一の通信受信機を提供することが有利であろう。

【0006】

前記WBCDMA UMTSシステムの帯域幅は3.84MHzであるから、前記WBCDMA信号の各々のIおよびQ成分は3.84MHz/2の範囲にあることになる。これらの広い帯域幅は、送信信号の要求されるダイナミックレンジが与えられれば、フラッシュ(Flash)またはパイプライン化(Pipelined)データコンバータのような複雑なデータコンバータまたはデータ変換器を使用することを必要とし、該データコンバータは、非常に高速であるためスペクトル拡散システムにおける送信された符号を再生するために符号のトラッキングを可能とするよう高いサンプリングレートを許容するが、GSMモードにとって特に適したものではなく、それはこれらのデータコンバータは高い電力消費および限られたダイナミックレンジ(10ビット)を有するのに対しGSMモードは高いダイナミックレンジ(14ビット)を必要とするが低いサンプリングレートを許容するためである。より低い電力消費は、もちろん、セルラ電話のような携帯用または移動通信機器においては常に望ましいものである。前記GSMモードは異なる帯域幅に対して容易にプログラム可能であり、より広いダイナミックレンジを有し、かつ電力消費が少ないシグマ−デルタ(Sigma−Delta)デジタル−アナログ変換器または他の変換器を使用できるようにする。

【0007】

【課題を解決するための手段】

上述のおよび他の利点はある広帯域チャネルのサブバンド(sub−bands)をデュアル低中間周波(IF)デジタル手法を使用してII,IQ,QI,QQと称されるより狭い帯域幅成分へと重ね合わせる(superimpose)ことによって得ることができ、この場合各々の成分は中帯域幅または狭帯域幅モードが選択された場合に再使用できる共通のデータコンバータを使用することができる。

【0008】

これは送信のために広帯域または狭帯域のキャリアへと符号化されかつ変調された情報を伝達する無線信号を検出しかつ復調するためのデュアルモード通信受信機を提供することによって達成でき、該通信受信機は検出された帯域をサブバンドへと再分割しかつ該サブバンドを該サブバンドの帯域幅と同様の帯域幅を備えた複数の成分へと重ね合わせるための手段、各々の成分に別個に含まれる情報の部分を処理するための手段、および前記成分からの処理された情報を組み合わせて送信された元の情報を再現するための手段を具備する。

【0009】

これはまた送信のために広いまたは狭い帯域幅のキャリアへと符号化されかつ変調された情報を伝達する無線信号を検出しかつ復調するためのデュアルモード通信受信機を動作させる方法を提供することによって達成でき、該方法は、検出された信号を検出されたサブバンドへと再分割する段階、前記検出されたサブバンドを前記サブバンドの帯域幅と同じまたは同様の帯域幅を備えた複数の成分へと重ね合わせる段階、各々の成分に別個に含まれる情報の部分を処理する段階、および前記成分からの処理された情報を組み合わせて元の送信された情報を再現する段階を具備する。

【0010】

【発明の実施の形態】

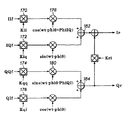

図1は、本発明に係わる通信受信機の全体のブロック図である。入力信号Vinは前に述べたように無線周波または中間周波チャネルへと変換されるベースバンド・スペクトルを表わす複素または複合信号であり、同相(In−phase)および直角位相(Quadrature−phase)成分を有する入力信号を生成するために送信機における変調器によって加えられる情報を有し、該入力信号Vinは増幅器100に印加され、該増幅器100の出力は2つの直交ミキサまたはダウンコンバータ102,104に供給される。入力信号VinはBWの帯域幅を有する。入力信号Vinは4つのサブバンドへと再分割される。

【0011】

IQダウンコンバータ102,104は無線周波信号(RF)または中間周波(IF)チャネルを、例えば、ギルバート型ミキサ(Gilbert Typeof Mixer)またはチョッパ型ミキサ(Chopper Type of Mixer)を使用してDCスペクトルへとダウンコンバートする。

【0012】

局部発振器(Local Oscillator)105は2つのアナログ−デジタル変換器106および107をドライブして直交アナログ出力(sin(wt)およびcos(wt)、この場合w=2*Pi*BW/4)を生成し、これらは次に直交ネットワーク108をドライブし、該直交ネットワーク108は2つのRFまたはIF発振器信号を伝達するためにPi/2で分割または除算し、これらの信号は直交ミキサ102,104の2つの局部発振器ポートに供給するために直交している。

【0013】

ミキサ102および104の出力はベースバンドまたは低中間周波数における(以後、ベースバンドへの言及は代わりに、受信機の設計に応じて、低中間周波を含むことがある)入力信号Vinの直交表現である。

【0014】

ミキサ102および104の出力は第1のローパス・ブロッキングフィルタ(容量)によってろ波されかつ次にそれぞれさらに他のミキサ(乗算器)110,112,114および116に供給され、これらのミキサにおいて帯域幅BW/2のIおよびQサブバンド成分はさらに帯域幅BW/4の4つの成分II,IQ,QIおよびQQへと分割される。これら4つの成分は増幅されかつ、各々BW/4に等しいかまたはそれより大きな帯域幅を有する、ローパスフィルタ118,120,122および124によってさらなるブロッキングろ波(blocking filtering)を行なうためにろ波される。

【0015】

前記ミキサはIおよびQ IFまたはRFからベースバンドへのミキサ102および104を除き低周波ミキサ/乗算器である。該ミキサ/乗算器110,112,114および116は利得を有する乗算器DACとして実施することができ、この場合デジタル入力ポートは供給されるcos(wt)およびsin(wt)のデジタル表現を有しかつ前記アナログ入力ポートはミキサ102および104のろ波された出力である。乗算器DACのクロック周波数はこのクロックの高調波におけるスプリアス応答を避けるために前に設けられるブロッキングの量に依存する。また、この乗算器DACは受信機における自動利得制御(AGC)信号を設定するために使用できる。

【0016】

前記ローパスフィルタは一般に広帯域または中帯域または狭帯域がろ波できるようにプログラム可能なカットオフ周波数を備えたアクティブまたは能動RC型のフィルタに基づいている。これらのフィルタはBW/4に等しい帯域幅を有し、これは同様のブロッキング排除要求を備えたBW/2に等しい帯域幅のフィルタに対してそれらの設計を簡略化する。これは前記フィルタがフィルタごとに要求されるポールの数を低減できるようにし、それは次により少ないグループまたは群および振幅リップルを導入することになる。また、プログラミングのカットオフ周波数範囲が低減される。

【0017】

ローパスフィルタ118,120,122および124の出力は、シグマ−デルタA/D変換器とすることができる、アナログ−デジタル変換器126,128,130および132、ならびにデシメイション・フィルタ134,136,138および140へと供給され後に詳細に説明する成分信号IIf,IQf,QIfおよびQQfを生成する。該信号はコンバイナ142において利得および位相修正されかつ再結合されて出力信号Vout++およびVout−+を生成する。これらの出力信号はその後復調されかつデコードされて送信機の変調器によって前記複素または複合入力信号へと前に符号化された情報を表わすデジタルビットストリームを生成する。

【0018】

アナログ−デジタル変換器126,128,130および132は好ましくは種々の広帯域または中帯域または狭帯域信号成分に対してオーバサンプリング比をプログラム可能なシグマ−デルタ型のA/D変調器である。前記成分II,IQ,QI,QQはそれらの帯域幅が各々BW/4に低減されているから、これは同じダイナミックレンジに対してシグマ−デルタに対するオーバサンプリングの要求されるオーバサンプリング・クロック周波数を低減する。例えば、BW=3.84MHzを有するWBCDMAモードにおいては、前記オーバサンプリングクロックは26MHzの範囲において選択されそれによって10ビットの分解能に対して26MHz/(3.84MHz/4)=27.08の範囲になるようにされ、一方、GMSモードにおいては、前記オーバサンプリングクロックは14ビットの分解能に対してオーバサンプリング比13MHz/0.2KHz=65に対し13MHzとなる。

【0019】

前記シグマ−デルタ変調器126,128,130および132はオーバサンブリングの特定周波数でオーバサンプルされたデジタルストリームを発生する。これらのデジタル出力はこの種の変調器にとって典型的であるようにシグマ−デルタ変調器の次数(order)および形式に応じて成形されたノイズスペクトルを含む。前記デジタル出力は次にデジタル的にろ波されてシグマ−デルタ変調器の前記成形されたノイズを除去し、かつ次に選択ろ波(selectivity filtering)を行なうためにより低いクロックレートで動作するデシメイション・デジタルフィルタ134,136,138および140によってさらに処理するためにより低いクロック周波数へとデシメイトされる。デジタル出力IIf,IQf,QIfおよびQQfは次にコンバイナ142におけるデジタル乗算器および加算器によって処理されて利得および位相の不平衡の修正を行ないかつベクトルVout++およびVout−+で表わされる4つのデジタル出力成分を発生する。

【0020】

アナログフィルタ118,120,122および124、シグマ−デルタ変換器126,128,130および132、およびデジタル・デシメイションフィルタ134,136,138および140の帯域幅はまたいくつかの帯域幅設定を取り扱うためにプログラム可能にすることができる。

【0021】

図1に示される好ましい実施形態においては、受信機が示されており、該受信機においては、入力信号は4つの成分に分割される。しかしながら、入力信号の帯域幅および前記成分の所望の帯域幅に応じて異なる数の成分を使用できることが理解されるであろう。

【0022】

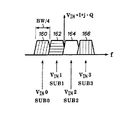

図1の受信機の動作は図2〜図5に示される受信機における種々のポイントでの信号のスペクトル表現を参照することにより最もよく理解することができる。増幅器100に印加される入力チャネルは図2においてそれぞれ、以後sub0,sub1,sub2およびsub3と称されかつ参照数字160,162,164および166によって参照される4つのサブバンドへと再分割または細分される。図2は4つのサブバンドへと分割された後のVinのスペクトル表現である。前記サブバンドの各々はBW/4の帯域幅を有する。

【0023】

これら4つのサブバンドの基礎を成すRFチャネルはRFまたはIF周波数から、ミキサ102および104の出力として、2つの成分、IおよびQ、においてベースバンドへとダウンコンバートされ、これらの出力は直交位相関係にありかつ各々の成分はBW/2(0からBW/2)のスペクトル帯域幅を有する。

【0024】

もしベクトルVin=I+j・Qがベースバンドにおける入力チャネルの表現であるとすれば、Vinは前記4つのサブバンドに対応する4つのベクトルの合計として表現することができ、例えば、Vin=Vin0+Vin1+Vin2+Vin3となる。図2はまたこの表現を示し、そこではVin0はsub0に対応し、Vin1はsub1に対応し、Vin2はsub2に対応し、そしてVin3はsub3に対応する。

【0025】

図3(a)および図3(b)は、その構成要素IおよびQ成分(ラインf上)で表現されたVinのスペクトルを示す。したがって、Vinの実数部、例えば、I=I0+I1+I2+I3はそれぞれ図3(b)において160I,162I,164Iおよび166Iとして示され、かつ虚数部はj・Q=j・Q0+j・Q1+j・Q2+j・Q3はそれぞれ図3(a)において160Q,162Q,164Qおよび166Qとして示されている。

【0026】

それから、前に述べたように、sub3,166はsub0,160と混合され、sub2,164はsub1,162と混合され、再び前記fラインの下にIおよびj・Qスペクトルが別個に見られる。

【0027】

各々の成分IおよびQは次にミキサ110,112,114および116において低IF直交信号cos(wt)およびsin(wt)と混合され(この場合、w=2・pi・BW/4または最も近い値である)、すなわち前記低IFクロックはIまたはQ帯域幅の半分である。該動作は次のようになる。

【数1】

IIf=II**HII, II=Icos(wt)

IQf=IQ**HIQ, IQ=Isin(wt)

QIf=QI**HQI, QI=Qcos(wt)

QQf=QQ**HQQ, QQ=Qsin(wt)

【0028】

この場合、HII,HIQ,HQIおよびHQQは、それぞれ、前記II,IQ,QIおよびQQ経路における、それぞれ、アナログおよびデジタルフィルタ118,120,122および124、および134,136,138および140の伝達関数である。

前記**は時間領域のたたみ込み(convolution)を意味する。

【0029】

【数2】

II=I・(e+j(wt)+e−j(wt))/2

IQ=I・(e+j(wt)−e−j(wt))/2j

QI=Q・(e+j(wt)+e−j(wt))/2

QQ=Q・(e+j(wt)−e−j(wt))/2j

【0030】

e+j(wt)による乗算はスペクトルを+wだけ、すなわち、+BW/4だけシフトすることと等価である。e−j(wt)による乗算は−wだけ、すなわち−BW/4だけスペクトルをシフトすることと等価である。

【0031】

結果として図4(a)、図4(b)、図4(c)および図4(d)に示されるスペクトルになり、これらの図はまたそれぞれ前記フィルタ118,120,122および124の出力を、各々図面に示される、II,IQ,QIおよびQQとして図式的に示す。帯域幅BW/2のフィルタとしてかつ、それぞれ、IIf,IQf,QIfおよびQQfとしてフィルタ134,136,138および140の出力も帯域幅W/2のフィルタとして示されている。上で述べたスペクトルのシフトもまた図4に図式的に示されている。前記II,IQ,QIおよびQQ経路におけるフィルタの出力の各々は前記4つのサブバンドの各々を含み、これが成分II,IQ,QIおよびQQが図4(a)〜図4(d)に示されるように、重ね合わされた4つのサブバンドを有する理由であり、かつ従って入力信号Vin内に元々含まれる全ての情報が元の信号を再現するために利用または入手可能であるが、信号の処理は元の信号Vinよりも狭い帯域幅において行なわれ従って広い帯域幅をサポートするためこの動作を行なうために通常使用されるフラッシュまたはパイプライン化データコンバータではなくシグマ−デルタA/D変換器によって達成できる。

【0032】

送信された元の(しかしながら、今や処理された)情報の再現の形式で出力を生成するため、前記4つのサブバンドの各々の情報はコンバイナ142において再結合されて2つのベクトル成分Vout++およびVout−+を形成しなければならない。

【数3】

Vout++=(IIf−QQf)

+j・(IQf+QIf)

Vout−+=(IIf+QQf)

+j・(−IQf+QIf)

【0033】

したがって、それぞれ図5(a)および図5(b)に図式的に示されるように、前記Vout++ベクトルはサブバンド0およびサブバンド1、160および162、の再現に対応し、かつ前記Vout−+ベクトルはサブバンド2およびサブバンド3、164および166、の再現に対応する。コンバイナ142による再結合はいくつかの方法で行なわれ、例えば次のように行なうことができる。

Vout++に対してIIf−QQf=I++を達成するため加算器/減算器を使用する。

Vout++に対してIQf+QIf=Q++を達成するため加算器/減算器を使用する。

Vout−+に対してIIf+QQf=I−+を達成するため加算器/減算器を使用する。

Vout−+に対して−IQf+QIf=Q−+を達成するため加算器/減算器を使用する。

【0034】

前記演算操作Vout++e−j(wt)は複素乗算器を使用して形成され、加算器および乗算器を使用して次のデジタル演算操作を行なう。すなわち、(I++ +j・Q++)・(cos(wt)−j・sin(wt))=I++・cos(wt)+Q++・sin(wt)+j・(−I++・sin(wt)+Q++・cos(wt))

【0035】

演算操作Vout−+ej(wt)は複素乗算器を使用して形成され、加算器および乗算器を使用して次のデジタル演算操作を行なう。すなわち、(I−+ +j・Q−+)・(cos(wt)+j・sin(wt))=I−+・cos(wt)−Q−+・sin(wt)+j・(I−+sin(wt)+Q−+・cos(wt))

【0036】

前記成分IIf,IQf,QIfおよびQQfの4つ全ては各々のサブバンドを再現するために必要とされることに注意を要する。サブバンドを別個に復元するために4つ全ての成分が利用できることが要求される。各々の成分(II,IQ,QIおよびQQ)は前記BW/4の中にそれらのそれぞれのスペクトルで示されるように4つのサブバンド全てに関連する情報を含んでいる。これが受信機が4つのサブバンド全てを並列に処理することができるようにしかつより好ましいA/D変換技術を使用できるようにする。このため、前記受信機は2重デカルト(ダブル・カーテシアン:Double Cartesian)受信機と称することができ、それは各々のサブバンドを再現するために前記4つの成分が必要とされるからである。

【0037】

また、これら4つの実数成分はBW/4のスペクトル幅を有しかつこれら4つの成分をデジタル化するために同じローパスA/D変換器を備えた同じローパスフィルタが必要とされることに注意を要する。

【0038】

本発明を採用した受信機はBW/4の帯域幅要求を有するIIf,QQf,QIfおよびIQfと称される4つのベースバンド出力成分(2重デカルト)を備えた帯域幅BWのRFまたはIF入力チャネルを有する受信機とみることができる。元のスペクトルを再現し戻すため、2つの再現ベクトルVout++およびVout−+がそれぞれ−wだけかつ+wだけシフトされることが必要であり、かつそれぞれe−j(wt−phi0)およびe+j(wt−phi0)で乗算されることが必要である。

【0039】

【数4】

Vout r

=Vout++・e−j(wt−phi0)

+Vout−+・e+j(wt−phi0)

この場合、phi0は位相の不連続を除去するよう選択される。sin(wt)およびcos(wt)が発生される必要があるから、sin(wt)およびcos(wt)を発生した位相発生器は単に−phi0のオフセットでスタートする。

【0040】

Vout++およびVout−+をそれらの表現で置き換えることにより次の式を得る。

【数5】

Vout r=2(IIf・cos(wt−phi0)

+IQf・sin(wt−phi0))

+2・j・(QIf・cos(wt−phi0)

+QQf・sin(wt−phi0))

【0041】

すなわち、再現された同相および直角位相成分は次のようになる。

【数6】

Ir=(IIf・cos(wt−phi0)

+IQf・sin(wt−phi0))

Qr=(QIf・cos(wt−phi0)

+QQf・sin(wt−phi0))

【0042】

上で述べた数式に従って再現されたベクトルVout rの実数および虚数出力を発生するためかつまた前記4つの経路によって導入される不整合に対する利得および位相修正を提供するためにコンバイナ142の再現構成が図6に示されている。図6において実施される再結合方程式Ir=(IIf・cos(wt−phi0)+IQf・sin(wt−phi0))およびQr=(QIf・cos(wt−phi0)+QQf・sin(wt−phi0))はまたそれらがそれらの間で整合しない場合に前記成分の間の利得および位相修正を使用する。

【0043】

IIfは利得修正項Kiiによって乗算され、IQfは利得修正項Kiqによって乗算され、QQfは利得修正項Kqqによって乗算され、かつQIfは利得修正項Kqiによって乗算され、これらの乗算はそれぞれ乗算器170,172,174および176によって行なわれる。前記利得修正項は修正された各項が等しい振幅になるよう選択される。

【0044】

さらに、IIf,IQf,QIfおよびQQfの間で位相を修正することが必要とされる。例えば、IIfをcos(wt−phi0)により、乗算するよりはむしろ、それは乗算器178においてcos(wt−phi0+PhiIQ)によって乗算され、この場合PhiIQはIIfおよびIQfの間の位相の不整合を補償するためにIQfに対してIIfの位相をシフトするために使用される位相値である。同様に、前記項PhiQIは乗算器180において適用されるQIfおよびQQfの間の位相不整合を補償するための位相修正である。

【0045】

いったんIIfおよびIQfが利得および位相整合されると、かつQIfおよびQQfが利得および位相整合されると、(IIf,IQf)、加算器182の出力、および(QQf,QIf)、加算器184の出力、は位相が整合されなければならない。これは加算器182の出力に加算器184の出力である項Kriを加算することによって行なわれる。これは単に次の式で説明できる。

【数7】

cos(wt+PhiIR)

=cos(wt)cos(PhiIR)

+sin(wt)・sin(PhiIR)

【0046】

これは、位相値PhiRによって修正するために、虚数部sin(wt)(加算器184の出力)がとられかつKri=sin(PhiIR)によって乗算され、そして加算器182の出力cos(wt)・cos(PhiIR)に加えられることを意味する。cos(PhiIR)による乗算の演算は加算器182の前にKii′=Kii・cos(PhrIR)およびKiq′=Kiq・cos(PhiIR)の変更によって達成でき乗算器を節約する。

【0047】

したがって次のようになる。

【数8】

Ir=Kii・cos(PhIR)

・Iff・cos(wt−phi0+PhiIQ)

+Kiq・cos(PhiIR)

・IQf・sin(wt−phi0)

+Qr・Kri、および

Qr=Kqq・QQf

・sin(wt−phi0−PhiQI)

+Kqi・QIf・cos(wt−phi0)

【0048】

前記受信信号が狭帯域幅または中帯域幅(これらの双方は本説明の目的で狭帯域と称することができ、その理由はそれらが前に述べた広帯域に対して狭いからである)を有する場合、すなわちBWよりはむしろBW/2のような場合(例えば、GSMセルラ電話信号)、前記受信機の成分の枝路の内の2つはオフに切り替えることができ、一方他の2つの枝路はオンに留めることができ、デジタル局部発振器が0に設定されまたは利得制御(AGC)を設定するために使用される。(すなわち、cos(wt)=1またはcos(wt)=AGCおよびsin(wt)=0である。)これは次に単一デカルト受信機として機能する。

【0049】

図1の受信機は図7においてそのようなモードで示されている。図6に示されるように、図7の受信機への入力は図1のものと同様に操作され、すなわち、局部発振器105、および局部発振器直交発生器108は前に述べたのと同じ信号を生成し、これは入力チャネルをベースバンドへと低減しかつスペクトルをそのIおよびQ直交成分へと分割するよう作用するミキサ102および104と同様である。しかしながら、図6の受信機においては、IQおよびQQ経路はそこへの入力信号を0によって乗算することによりディスエーブルされる。これは2つの経路のみがアクティブに留まることができるようにし、前記複合の、しかしながら、狭い、またはより狭い、帯域の入力信号のIおよびQ成分の各々に対して1つの経路を許容する。

【0050】

前記アクティブな経路IIおよびQIはそれぞれアナログのローパスフィルタ118および122において入力チャネルをろ波し、A/D変換器126および130(これはシグマ−デルタ変換器とすることができる)においてアナログ−デジタル変換を行ない、かつフィルタ134および138においてデジタルろ波を提供し、出力信号IoutおよびQoutを生成し、これらは次に送信機によって符号化された元の符号化情報を引き出すために使用される。

【0051】

理解できるように、このようにして広帯域および狭帯域の信号の双方が同じ受信機構成要素によって処理できかつ構成要素およびデータ経路の重複が避けられる。

【0052】

前に述べたように、上記好ましい実施形態においては、受信機は入力信号が4つの場合(または、中帯域または狭帯域信号の場合2つの成分)へと分割されるものとして説明されているが、入力信号の帯域幅および構成成分の所望の帯域幅に応じて異なる数の構成成分を使用できることが理解されるであろう。

【図面の簡単な説明】

【図1】本発明に係わる通信受信機全体の構成を示すブロック図である。

【図2】入力信号Vinのスペクトル表現を示す説明図である。

【図3】入力信号Vinのスペクトル表現を虚数部(a)および実数部(b)に分離して示す説明図である。

【図4】信号Vinである成分II,IQ,QIおよびQQの、サブバンドの各々をsin(wt)またはcos(wt)と混合しかつ前記成分の各々をろ波した後の、スペクトル表現を示す説明図である。

【図5】サブバンド0およびサブバンド1の再現に対応するVout++ベクトル、およびサブバンド2およびサブバンド3の再現に対応するVout−+ベクトルを図式的に示す説明図である。

【図6】本発明に係わるコンバイナ回路の構成を示す概略的ブロック回路図である。

【図7】狭帯域幅または中帯域幅信号の受信のための受信機の構成を示す本発明に係わる通信受信機の全体的なブロック図である。

【符号の説明】

100 増幅器

102,104 直交ミキサまたはダウンコンバータ

105局部発振器

106,107 A/D変換器

108 直交ネットワーク

110,112,114,116 ミキサ

118,120,122,124 ローパスフィルタ

126,128,130,132 A/D変換器

134,136,138,140 デシメイション・フィルタ

142 コンバイナ

Claims (11)

- キャリヤの同相−直角位相(IQ)変調を有する広帯域キャリヤ信号または狭帯域キャリヤ信号として送信される送信情報を受信しかつ処理するよう構成された通信受信機であって、

広帯域信号の帯域幅(BW)を包含するのに十分広いスペクトルの一部を検出し、かつ該検出した信号をIおよびQ成分におけるベースバンドへと変換するための検出および変換手段(100〜108)であって、各々の成分はBW/2の帯域幅を有するもの、

を具備し、さらに、

前記IおよびQ成分を少なくとも広帯域信号からさらに他のIおよびQ成分に変換してサブ成分(II,IQ,QIおよびQQ)を形成するためのさらに他の変換手段(110〜116)であって、前記サブ成分の各々はBW/4の帯域幅を有し、かつ元の送信情報の部分を含むことができるもの、

広帯域モードにおいて、前記サブ成分(II,IQ,QIおよびQQ)の各々を別個に処理して元の送信情報の部分を抽出するよう動作し、かつ狭帯域モードにおいて、狭帯域送信信号内の情報(IIおよびQI)を含む前記サブ成分の各々を別個に処理して元の送信情報の部分を抽出するよう動作可能な処理手段(118〜140)、および

前記抽出された情報を再結合して元の送信情報を再現するための再結合手段(142)、

を具備することを特徴とする通信受信機。 - 前記検出および変換手段(100〜108)は、受信された無線信号を単一の局部発振器出力(105)によって混合して前記受信された無線信号を前記処理が行なわれる周波数へとダウンコンバートし、かつその後該ダウンコンバートされた信号を独立したかつ同時的な処理のためにBW/2の帯域幅を有する成分へと分割することを特徴とする請求項1に記載の通信受信機。

- 前記検出および変換手段(100〜108)は、受信された無線信号を単一の局部発振器出力(105)により混合して前記受信された無線信号を中間周波数へとダウンコンバートし、かつその後該ダウンコンバートされた信号を独立したかつ同時的な処理のためにBW/2の帯域幅を有する成分へと分割することを特徴とする請求項1に記載の通信受信機。

- 前記さらに他の変換手段(110〜116)は、前記ダウンコンバートされたIおよびQ成分を局部的に発生された信号と混合して前記サブ成分(II,IQ,QIおよびQQ)を生成するための成分混合手段を具備することを特徴とする請求項2または3に記載の通信受信機。

- 前記成分混合手段は、そのデジタル入力が局部発振器からの低周波デジタル局部発振器信号によって駆動される乗算器DACを具備することを特徴とする請求項4に記載の通信受信機。

- 前記乗算器DACは自動利得調整のための利得制御を提供することを特徴とする請求項5に記載の通信受信機。

- 前記処理手段(118〜140)は、アナログ−デジタル変換器(126〜132)を具備することを特徴とする請求項6に記載の通信受信機。

- 前記アナログ−デジタル変換器(126〜132)は、広帯域または狭帯域変換のためのプログラム可能なオーバサンプリング比を備えたシグマ−デルタA/D変換器からなることを特徴とする請求項7に記載の通信受信機。

- 前記さらに他の変換手段(110〜116)は、前記サブ成分(II,IQ,QIおよびQQ)のためのそれぞれの経路を有し、前記サブ成分の内の2つの経路は狭帯域モードにおいてディスエーブルされることを特徴とする請求項1〜8の内のいずれか1項に記載の通信受信機。

- 前記再結合手段(142)は、前記再結合プロセスの間にデジタル局部発振器(105)からの信号との複素混合と組み合わせて前記サブ成分のためのデジタル利得および位相修正を行なうよう構成されていることを特徴とする請求項1〜9の内のいずれか1項に記載の通信受信機。

- 前記再結合手段(142)は前記再結合プロセスの間に前記デジタル局部発振器を位相シフトすることにより位相の不連続性を除去するよう構成されていることを特徴とする請求項10に記載の通信受信機。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP19990403266 EP1111803B1 (en) | 1999-12-23 | 1999-12-23 | Dual mode with a single receiver circuit |

| EP99403266.2 | 1999-12-23 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001217800A JP2001217800A (ja) | 2001-08-10 |

| JP2001217800A5 JP2001217800A5 (ja) | 2008-02-07 |

| JP4355443B2 true JP4355443B2 (ja) | 2009-11-04 |

Family

ID=8242232

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000389165A Expired - Fee Related JP4355443B2 (ja) | 1999-12-23 | 2000-12-21 | 2重デジタル低if複合受信機 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6931241B2 (ja) |

| EP (1) | EP1111803B1 (ja) |

| JP (1) | JP4355443B2 (ja) |

| KR (1) | KR100736057B1 (ja) |

| DE (1) | DE69921495T2 (ja) |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7099688B2 (en) * | 2001-12-07 | 2006-08-29 | Matsushita Electric Industrial Co., Ltd. | Combined Low-IF/direct down conversion baseband architecture for 3G GSM/WCDMA receivers |

| US6819910B2 (en) * | 2002-03-08 | 2004-11-16 | Broadcom Corp. | Radio employing a self calibrating transmitter with reuse of receiver circuitry |

| US7310386B2 (en) * | 2002-04-25 | 2007-12-18 | Broadcom Corporation | Radio receiver utilizing a single analog to digital converter |

| FR2843249A1 (fr) * | 2002-07-31 | 2004-02-06 | Koninkl Philips Electronics Nv | Recepteur comportant des moyens de reception multiples en parallele. |

| TW566011B (en) * | 2002-09-23 | 2003-12-11 | Ind Tech Res Inst | Dual mode receiving method and device |

| US7003263B2 (en) * | 2003-05-12 | 2006-02-21 | Lucent Technologies Inc. | Telecommunications receiver and a transmitter |

| US7233778B2 (en) * | 2003-05-27 | 2007-06-19 | Broadcom Corporation | Apparatus and method for converting a signal from a first analog format to a second analog format |

| DE10360470B4 (de) * | 2003-12-22 | 2010-11-18 | Infineon Technologies Ag | Verfahren und Vorrichtung zum Demodulieren eines Empfangssignals |

| KR100622646B1 (ko) * | 2004-05-12 | 2006-09-14 | 전자부품연구원 | 2.3 - 2.4 GHz 무선 통신을 위한 다중표준 송수신기구조 |

| US20060160518A1 (en) * | 2004-12-10 | 2006-07-20 | Maxlinear, Inc. | Harmonic reject receiver architecture and mixer |

| KR100618347B1 (ko) | 2005-02-01 | 2006-08-31 | 삼성전자주식회사 | 생성하는 4개의 쿼드러쳐신호 모두에 대해 위상조정이가능한 쿼드러쳐신호 생성장치 |

| US7142144B1 (en) * | 2005-05-19 | 2006-11-28 | Ami Semiconductor, Inc. | Low power sigma delta modulator |

| CN101248580B (zh) * | 2005-07-20 | 2012-05-02 | 新加坡国立大学 | 谐振器中抗谐振的抵消 |

| US8059758B2 (en) * | 2006-02-10 | 2011-11-15 | Qualcomm, Incorporated | Conversion of multiple analog signals in an analog to digital converter |

| FR2900006B1 (fr) * | 2006-04-13 | 2013-09-20 | St Microelectronics Sa | Recepteur de signal radio, du type a frequence intermediaire |

| US8099072B2 (en) * | 2006-11-21 | 2012-01-17 | Qualcomm Incorporated | Frequency changer circuits |

| KR100897158B1 (ko) * | 2007-12-03 | 2009-05-14 | 한국전자통신연구원 | 다중 채널 튜닝 수신 장치 및 그 다중 채널 튜닝 방법 |

| DE102008003669B4 (de) * | 2008-01-09 | 2010-10-21 | Eads Deutschland Gmbh | Verfahren zum Empfang eines breitbandigen elektromagnetischen Signals |

| US8085088B2 (en) * | 2009-03-04 | 2011-12-27 | National Semiconductor Corporation | Quadrature signal demodulator circuitry suitable for doppler ultrasound |

| US8514919B2 (en) | 2009-08-26 | 2013-08-20 | Bae Systems National Security Solutions Inc. | Synthetic instrument unit |

| EP2434641B1 (en) | 2010-09-24 | 2012-12-05 | Telefonaktiebolaget L M Ericsson (PUBL) | Complex intermediate frequency mixer stage and calibration thereof |

| EP2434640B1 (en) * | 2010-09-24 | 2012-12-05 | Telefonaktiebolaget L M Ericsson (PUBL) | Correction of imbalances in a complex intermediate frequency mixer |

| US11108468B2 (en) * | 2017-08-08 | 2021-08-31 | Nippon Telegraph And Telephone Corporation | Optical transmitter, optical receiver and communication system |

| CN108897019A (zh) * | 2018-04-27 | 2018-11-27 | 武汉大学 | 一种双模双通道的gps/北斗二代导航射频接收系统 |

| US11456898B2 (en) * | 2020-01-21 | 2022-09-27 | Maxim Integrated Products, Inc. | Low-power complex analog LMS adaptation systems and methods |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5053983A (en) * | 1971-04-19 | 1991-10-01 | Hyatt Gilbert P | Filter system having an adaptive control for updating filter samples |

| US5815525A (en) * | 1991-05-13 | 1998-09-29 | Omnipoint Corporation | Multi-band, multi-mode spread-spectrum communication system |

| US5668837A (en) * | 1993-10-14 | 1997-09-16 | Ericsson Inc. | Dual-mode radio receiver for receiving narrowband and wideband signals |

| US5642358A (en) * | 1994-04-08 | 1997-06-24 | Ericsson Inc. | Multiple beamwidth phased array |

| US5745846A (en) * | 1995-08-07 | 1998-04-28 | Lucent Technologies, Inc. | Channelized apparatus for equalizing carrier powers of multicarrier signal |

| FR2742946B1 (fr) * | 1995-12-22 | 1998-01-16 | Alcatel Mobile Comm France | Terminal de radiocommunication multimode |

| FI108486B (fi) * | 1997-01-31 | 2002-01-31 | Nokia Corp | Menetelmõ ja piirijõrjestely vastaanotettujen signaalien kõsittelemiseksi tiedonsiirtojõrjestelmõssõ |

| US5974305A (en) * | 1997-05-15 | 1999-10-26 | Nokia Mobile Phones Limited | Dual band architectures for mobile stations |

| US6157329A (en) * | 1997-09-15 | 2000-12-05 | Massachusetts Institute Of Technology | Bandpass sigma-delta modulator employing high-Q resonator for narrowband noise suppression |

| JPH11234150A (ja) * | 1998-02-09 | 1999-08-27 | Toshiba Corp | デジタル復調装置 |

| US6337885B1 (en) * | 1998-02-13 | 2002-01-08 | Telefonaktiebolaget Lm Ericsson (Publ) | Radio receiver that digitizes a received signal at a plurality of digitization frequencies |

| US6028850A (en) * | 1998-07-10 | 2000-02-22 | Hyundai Electronics America, Inc. | Wireless transceiver and frequency plan |

| US6330290B1 (en) * | 1998-09-25 | 2001-12-11 | Lucent Technologies, Inc. | Digital I/Q imbalance compensation |

| US6160859A (en) * | 1998-10-19 | 2000-12-12 | Motorola, Inc. | Integrated multi-mode bandpass sigma-delta receiver subsystem with interference mitigation and method of using the same |

| US6675024B1 (en) * | 1999-09-30 | 2004-01-06 | Skyworks Solutions, Inc. | System and method for receiving analog and digital signals |

-

1999

- 1999-12-23 EP EP19990403266 patent/EP1111803B1/en not_active Expired - Lifetime

- 1999-12-23 DE DE69921495T patent/DE69921495T2/de not_active Expired - Fee Related

-

2000

- 2000-12-21 US US09/746,692 patent/US6931241B2/en not_active Expired - Lifetime

- 2000-12-21 JP JP2000389165A patent/JP4355443B2/ja not_active Expired - Fee Related

- 2000-12-22 KR KR1020000080523A patent/KR100736057B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| EP1111803A1 (en) | 2001-06-27 |

| KR100736057B1 (ko) | 2007-07-06 |

| DE69921495T2 (de) | 2005-02-24 |

| US6931241B2 (en) | 2005-08-16 |

| JP2001217800A (ja) | 2001-08-10 |

| US20010014594A1 (en) | 2001-08-16 |

| EP1111803B1 (en) | 2004-10-27 |

| KR20010062641A (ko) | 2001-07-07 |

| DE69921495D1 (de) | 2004-12-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4355443B2 (ja) | 2重デジタル低if複合受信機 | |

| KR100954705B1 (ko) | 직접 컨버젼 수신기 | |

| JP4152944B2 (ja) | ダイレクトコンバージョンマルチキャリアプロセッサのためのシステムおよび方法 | |

| US4736390A (en) | Zero IF radio receiver apparatus | |

| US6782038B1 (en) | Method and apparatus for radio communications | |

| US7769359B2 (en) | Adaptive wireless receiver | |

| US7593491B1 (en) | Quadrature single-mixer multi-mode radio frequency receiver | |

| JP2003509909A (ja) | 角度変調rf信号に対する位相補間受信機 | |

| WO2000074252A1 (en) | Method and apparatus for receiving a signal | |

| US20070140382A1 (en) | Bandpass sampling receiver and the sampling method | |

| WO2004039028A2 (en) | Quadrature mismatch compensation | |

| KR20020072565A (ko) | 무선 수신기 | |

| JP3432156B2 (ja) | 変調された単側波帯信号を生成する方法および装置 | |

| JPH05129984A (ja) | 無線通信装置 | |

| JP2007513562A (ja) | バンドパスサンプリング受信器及びサンプリング方法 | |

| RU2337494C2 (ru) | Мультистандартная передающая система и способ для беспроводной системы связи | |

| JP4589331B2 (ja) | マルチモード・マルチバンド送受信機 | |

| US20110230153A1 (en) | Providing Channel Filtering In An Automatic Frequency Control Path | |

| US7190939B2 (en) | Time division IQ channel direct conversion receiver and method therefor | |

| JP2001103104A (ja) | ディジタル無線装置 | |

| JPH0774790A (ja) | 非線形歪補償送受信回路 | |

| JPH06188751A (ja) | デュアルモード無線送信機 | |

| JP2006180004A (ja) | 無線通信装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20041217 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071217 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071217 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20071217 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20081114 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090714 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090803 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120807 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130807 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |