JP4159570B2 - オシレータ回路、該オシレータ回路を備えた半導体装置、及び該オシレータ回路を備えた半導体記憶装置 - Google Patents

オシレータ回路、該オシレータ回路を備えた半導体装置、及び該オシレータ回路を備えた半導体記憶装置 Download PDFInfo

- Publication number

- JP4159570B2 JP4159570B2 JP2005258629A JP2005258629A JP4159570B2 JP 4159570 B2 JP4159570 B2 JP 4159570B2 JP 2005258629 A JP2005258629 A JP 2005258629A JP 2005258629 A JP2005258629 A JP 2005258629A JP 4159570 B2 JP4159570 B2 JP 4159570B2

- Authority

- JP

- Japan

- Prior art keywords

- oscillation

- signal

- unit

- state

- oscillator circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Dram (AREA)

Description

IC=K×((VDD−VR)−Vthp)2

=K×((VDD−Vthp)−VR)2

の関係を有する。ここで、KはPMOSトランジスタP101が有する物理定数である。また、Vthpは正の値を示している。従って、閾値電圧としては、−Vthpとなる。この式が成立するのは、ゲート・ソース間電圧が閾値電圧を下回らないことが条件であるので、VR<VDD−Vthpでの関係式である。

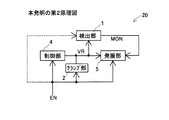

図4は、第1実施形態を示す回路図である(オシレータ回路)。図5は、第1実施形態の動作を示す動作波形図である。図6は、第2実施形態を示す回路図である(オシレータ回路)。図7は、第2実施形態の動作を示す動作波形図である。図8は、第3実施形態を示す回路図である(クランプ部)。図9は、第4実施形態を示す回路図である(クランプ部)。図10は、第5実施形態を示す回路図である(検出部)。図11は、第6実施形態を示す回路図である(オシレータ回路)。図12は、第6実施形態の動作を示す動作波形図である。図13は、オシレータ回路を備える半導体装置を示す回路ブロック図である。図14は、オシレータ回路を備える半導体記憶装置を示す回路ブロック図である。

例えば、本実施形態では、電流駆動型のオシレータ回路について例示したが、本発明はこれに限定されるものではなく、図21に例示した電圧駆動型のオシレータ回路においても同様に適用することができる。

また、電流駆動型、電圧駆動型の何れの方式においても、制御すべき駆動電流や駆動電圧は、高電源電圧側に備える構成とすることも、低電源電圧側に備える構成とすることもできる。更に、高電源電圧側及び低電源電圧側の双方に備える構成とすることもできる。この場合、駆動電流や駆動電圧の挿入位置により制御部の回路構成を適宜変更することは言うまでもない。

また、発振部における発振動作の作動・停止については、第1実施形態において、リングオシレータの動作制御をイネーブル信号ENにより行い、発振信号OSCの出力制御を検出信号MONにより行なう構成を示し、第2及び第6実施形態については、リングオシレータの動作制御を、イネーブル信号ENと、検出信号MONあるいは遅延信号Dとの論理合成により生成された発振開始信号ONにより行なう場合について例示した。しかしながら、本発明はこれに限定されるものではなく、制御信号と発振動作の作動・停止手段との組み合わせについては例示された組み合わせ以外にも任意に設定することができる。

また、発振周波数制御信号VRにより設定される発振周波数は固定として説明したが、制御部における抵抗素子を可変とする構成とすれば、抵抗値に応じて発振周波数制御信号VRの電圧レベルを可変とすることができ、発振周波数を可変することができる。このとき、可変抵抗としては、抵抗素子を切り替えることのほか、ゲート端子へのバイアスを可変とすることによりMOSトランジスタのオン抵抗を利用することもできる。

また、発振部については、リングオシレータで構成する場合について説明したが、本発明はこれに限定されるものではなく、双安定マルチバイブレータや容量成分への充放電を繰り返す方式等、発振動作を行なう回路構成であれば回路方式にかかわらず適用することができる。

前記発振許可信号に応じて発振周波数を制御する発振周波数制御信号を前記発振部に向けて出力する制御部と、

前記発振周波数制御信号を検出し、検出結果に応じて前記発振部を制御する検出信号を出力する検出部とを備えることを特徴とするオシレータ回路。

(付記2) 前記検出部は、

入力される前記発振周波数制御信号の信号値と、所定発振周波数に対応する信号値とを比較する比較部を備えることを特徴とする付記1に記載のオシレータ回路。

(付記3) 前記信号値は、アナログ電圧値であり、

前記比較部は、前記所定発振周波数に対応する信号値を閾値電圧とする論理ゲート素子を含むことを特徴とする付記2に記載のオシレータ回路。

(付記4) 前記検出部は、前記発振許可信号により制御され、発振不可状態において非活性化されることを特徴とする付記1に記載のオシレータ回路。

(付記5) 前記発振許可信号により制御され、発振不可状態において前記発振周波数制御信号を所定クランプ値にクランプするクランプ部を備えることを特徴とする付記1に記載のオシレータ回路。

(付記6) 前記所定クランプ値は、前記発振部を、発振停止状態又は発振信号の出力停止状態に制御する信号値であることを特徴とする付記5に記載のオシレータ回路。

(付記7) 発振許可信号に応じて発振動作が可能となる発振部と、

前記発振許可信号に応じて発振周波数を制御する発振周波数制御信号を前記発振部に向けて出力する制御部と、

前記発振許可信号に対して所定遅延時間を付加した遅延信号を、前記発振部に出力する遅延部とを備えることを特徴とするオシレータ回路。

(付記8) 前記所定遅延時間は、前記発振許可信号に応じて、前記発振周波数制御信号の信号値が所定発振周波数に対応する信号値に達するまでの時間以上の時間であることを特徴とする付記7に記載のオシレータ回路。

(付記9) 前記遅延部は、

前記発振周波数制御信号を生成する回路構成と同等の回路構成を有することを特徴とする付記7に記載のオシレータ回路。

(付記10) 前記発振部は、

前記発振動作の作動制御手段又は発振信号の出力制御手段のうち少なくとも何れか一方を備え、

前記検出信号又は前記遅延信号による制御は、前記発振許可信号による発振可能状態において前記発振周波数制御信号が所定発振周波数を指示する場合に、前記作動制御手段の活性化による発振動作の開始、又は前記出力制御手段の活性化による前記発振信号の出力のうち少なくとも何れか一方を行なうことを特徴とする付記1又は7に記載のオシレータ回路。

(付記11) 前記発振部は、

前記発振許可信号と、前記検出信号又は前記遅延信号との信号の合成を行なう信号合成部を備え、

前記信号合成部からの出力信号に応じて、前記作動制御手段又は前記出力制御手段のうち少なくとも何れか一方の活性化を行なうことを特徴とする付記10に記載のオシレータ回路。

(付記12) 前記発振部は、

前記発振許可信号により前記作動制御手段が活性化され、

前記検出信号又は前記遅延信号により前記出力制御手段が活性化されることを特徴とする付記10に記載のオシレータ回路。

(付記13) 前記発振部は、駆動電源電流により発振周波数が制御され、

前記発振周波数制御信号は、前記駆動電源電流であるか、又は、

前記駆動電源電流を供給するための定電流源を制御する電流信号又は電圧信号であることを特徴とする付記1又は7に記載のオシレータ回路。

(付記14) 前記発振部は、駆動電源電圧により発振周波数が制御され、

前記発振周波数制御信号は、前記駆動電源電圧であるか、又は、

前記駆動電源電圧を供給するための定電圧源を制御する電流信号又は電圧信号であることを特徴とする付記1又は7に記載のオシレータ回路。

(付記15) 付記1又は7に記載のオシレータ回路と、

前記オシレータ回路から出力される発振信号に応じた電圧を発生する電圧発生回路とを備えることを特徴とする半導体装置。

(付記16) 前記電圧発生回路は、昇圧回路であり、前記発振信号に応じた昇圧電圧を発生することを特徴とする付記15に記載の半導体装置。

(付記17) 前記電圧発生回路は、負電圧発生回路であり、前記発振信号に応じた負電圧を発生することを特徴とする付記15に記載の半導体装置。

(付記18) 付記1又は7に記載のオシレータ回路と、

前記オシレータ回路から出力される発振信号に応じた電圧を発生する電圧発生回路とを備えることを特徴とする半導体記憶装置。

(付記19) 前記電圧発生回路は、昇圧回路であり、前記発振信号に応じた昇圧電圧を発生することを特徴とする付記18に記載の半導体記憶装置。

(付記20) 前記電圧発生回路は、負電圧発生回路であり、前記発振信号に応じた負電圧を発生することを特徴とする付記18に記載の半導体記憶装置。

(付記21) 付記1又は7に記載のオシレータ回路と、

前記オシレータ回路から出力される発振信号に応じてリフレッシュ周期を制御するリフレッシュ制御回路とを備えることを特徴とする半導体記憶装置。

(付記22) 発振許可信号に応じて発振動作が可能となる発振部と、前記発振許可信号に応じて発振周波数を制御する発振周波数制御信号を前記発振部に向けて出力する制御部とを有するオシレータ回路の制御方法であって、

前記発振許可信号による発振可能状態において、前記発振周波数制御信号が所定発振周波数を指示する状態に達した時点以後の所定タイミングで、前記発振部の発振動作の開始、又は前記発振部からの発振信号の出力のうち少なくとも何れか一方を行なうことを特徴とするオシレータ回路の制御方法。

(付記23) 前記所定タイミングは、前記発振周波数制御信号の信号値と所定発振周波数に対応する信号値との比較により検出されることを特徴とする付記22に記載のオシレータ回路の制御方法。

(付記24) 前記発振許可信号による発振不可状態において、前記発振周波数制御信号の信号値と前記所定発振周波数に対応する信号値との比較動作は、非活性化されることを特徴とする付記23に記載のオシレータ回路の制御方法。

(付記25) 前記発振許可信号による発振不可状態において、前記発振周波数制御信号は、前記所定発振周波数を指示する状態に達せず非活性な信号値に維持されることを特徴とする付記23に記載のオシレータ回路の制御方法。

(付記26) 前記所定タイミングは、前記発振許可信号からの所定遅延時間の経過以後のタイミングとして設定されることを特徴とする付記22に記載のオシレータ回路の制御方法。

(付記27) 前記所定遅延時間は、前記発振許可信号に応じて、前記発振周波数制御信号の信号値が所定発振周波数に対応する信号値に達するまでの時間以上の時間であることを特徴とする付記26に記載のオシレータ回路の制御方法。

(付記28) 前記発振許可信号による発振可能状態において前記発振部の発振動作を開始し、

前記所定タイミングで前記発振部からの発振信号の出力を行なうことを特徴とする付記22に記載のオシレータ回路の制御方法。

また、付記4によれば、発振許可信号により検出部の活性・非活性を制御することができるので、発振不可状態において検出部を非活性として、不要な電流消費を低減することができる。

また、付記9によれば、制御部において発振許可信号に応じて発振周波数制御信号を生成する回路構成と同等の回路構成で所定遅延時間を計時する回路を構成しておけば、最適なタイミングで所定遅延時間を構成することができる。

また、付記11によれば、発振許可信号と、検出信号又は遅延信号とが信号合成部により合成されて出力信号として出力されるので、両信号が所定の状態にあることを検出した上で、作動制御手段又は出力制御手段を制御することができる。

2、21、22 クランプ部

3、31 遅延部

4、41、42、43、44、45 制御部

5、51、52、53、54、55 発振部

10 オシレータ回路(第1原理)

20 オシレータ回路(第2原理)

30 オシレータ回路(第3原理)

100 オシレータ回路(従来技術)

200 昇圧/負電源回路

300 リフレッシュ制御回路

400、410 内部回路

500 メモリセル

1000 半導体装置

2000 半導体記憶装置

D1 第1遅延部

D2 第2遅延部

D 遅延信号

EN イネーブル信号

MON 検出信号

OSC 発振信号

ON 発振開始信号

VR 発振周波数制御信号

Claims (11)

- 発振許可信号に応じて発振動作が制御される発振部と、

前記発振許可信号に応じて起動し、発振周波数を制御する発振周波数制御信号を前記発振部に向けて出力する制御部と、

前記発振許可信号に対して前記発振周波数制御信号が安定する遅延時間を付加した遅延信号を前記発振部に出力して、前記遅延信号に応じて前記発振部の前記発振動作を開始させる遅延部とを備えることを特徴とするオシレータ回路。 - 前記遅延時間は、前記発振許可信号に応じて、前記発振周波数制御信号の信号値が所定発振周波数に対応する信号値に達するまでの時間以上の時間であることを特徴とする請求項1に記載のオシレータ回路。

- 前記発振部は、

前記発振動作の作動制御手段又は発振信号の出力制御手段のうち少なくとも何れか一方を備え、

前記遅延信号による制御は、前記発振許可信号による発振可能状態において前記発振周波数制御信号が所定発振周波数を指示する場合に、前記作動制御手段の活性化による発振動作の開始、又は前記出力制御手段の活性化による前記発振信号の出力のうち少なくとも何れか一方を行なうことを特徴とする請求項1に記載のオシレータ回路。 - 前記発振部は、

前記発振許可信号により前記作動制御手段が活性化され、

前記遅延信号により前記出力制御手段が活性化されることを特徴とする請求項3に記載のオシレータ回路。 - 請求項1に記載のオシレータ回路と、

前記オシレータ回路から出力される発振信号に応じた電圧を発生する電圧発生回路とを備えることを特徴とする半導体装置。 - 請求項1に記載のオシレータ回路と、

前記オシレータ回路から出力される発振信号に応じた電圧を発生する電圧発生回路とを備えることを特徴とする半導体記憶装置。 - 請求項1に記載のオシレータ回路と、

前記オシレータ回路から出力される発振信号に応じてリフレッシュ周期を制御するリフレッシュ制御回路とを備えることを特徴とする半導体記憶装置。 - 発振許可信号に応じて発振状態が制御される発振部と、

前記発振許可信号に応じて起動し、前記発振部の発振周波数を指定する第1信号の第1状態と第2状態との遷移を、前記発振許可信号に応じて制御する制御部と、

前記発振許可信号を遅延させて、前記発振状態を制御する第2信号を生成する第1遅延部とを有し、

前記第1遅延部は、前記発振許可信号に対する前記第2信号の遅延量を、前記第1信号が前記第1状態から前記第2状態へ遷移する期間以上とし、

前記発振器は、前記第2状態において、予め定められた発振周波数となることを特徴とする半導体装置。 - 発振許可信号に応じて発振状態が制御される発振部と、

前記発振許可信号に応じて起動し、前記発振部の発振周波数を指定する第1信号の第1状態と第2状態との遷移を、前記発振許可信号に応じて制御する制御部と、

前記発振許可信号を遅延させて、前記発振状態を制御する第2信号を生成する第1遅延部とを有し、

前記第1遅延部は、前記第1信号が前記第1状態から前記第2状態に遷移している期間において前記第2信号が前記発振器を前記発振状態にしないようにし、前記第1信号が前記第2状態において前記第2信号が前記発振器を前記発振状態にするように、前記発振許可信号を遅延させて前記第2信号を生成し、

前記発振器は、前記第2状態において、予め定められた発振周波数となることを特徴とする半導体装置。 - 前記発振許可信号を遅延させて、前記発振状態を制御する第3信号を生成する第2遅延部を有し、

前記第2遅延部は、前記第3信号における前記発振状態を指定する期間が、前記第2信号における前記発振状態を指定する期間と重なるように、前記発振許可信号に対して前記第3信号を遅延させることを特徴とする請求項8または9に記載の半導体装置。 - 前記発振部は、前記発振許可信号、前記第2信号、および前記第3信号が共に前記発振状態を指定する場合に発信することを特徴とする請求項10に記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005258629A JP4159570B2 (ja) | 2005-09-07 | 2005-09-07 | オシレータ回路、該オシレータ回路を備えた半導体装置、及び該オシレータ回路を備えた半導体記憶装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005258629A JP4159570B2 (ja) | 2005-09-07 | 2005-09-07 | オシレータ回路、該オシレータ回路を備えた半導体装置、及び該オシレータ回路を備えた半導体記憶装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002003750A Division JP3742345B2 (ja) | 2002-01-10 | 2002-01-10 | オシレータ回路、該オシレータ回路を備えた半導体装置、及び該オシレータ回路を備えた半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006054913A JP2006054913A (ja) | 2006-02-23 |

| JP4159570B2 true JP4159570B2 (ja) | 2008-10-01 |

Family

ID=36032011

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005258629A Expired - Fee Related JP4159570B2 (ja) | 2005-09-07 | 2005-09-07 | オシレータ回路、該オシレータ回路を備えた半導体装置、及び該オシレータ回路を備えた半導体記憶装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4159570B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7286377B1 (en) | 2006-04-28 | 2007-10-23 | Mosaid Technologies Incorporated | Dynamic random access memory device and method for self-refreshing memory cells with temperature compensated self-refresh |

| JP2008052516A (ja) * | 2006-08-24 | 2008-03-06 | Seiko Instruments Inc | 定電圧回路 |

| CN113746427B (zh) * | 2021-11-05 | 2022-02-11 | 深圳飞骧科技股份有限公司 | 一种rc振荡电路 |

-

2005

- 2005-09-07 JP JP2005258629A patent/JP4159570B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006054913A (ja) | 2006-02-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7492232B2 (en) | Oscillator circuit, semiconductor device and semiconductor memory device provided with the oscillator circuit, and control method of the oscillator circuit | |

| US7667529B2 (en) | Charge pump warm-up current reduction | |

| KR20100094787A (ko) | 래치-업 현상을 방지할 수 있는 cmos 차지 펌프 | |

| KR100913957B1 (ko) | 반도체 소자 | |

| US8212609B2 (en) | Internal voltage generation circuit | |

| US6977828B2 (en) | DC-DC converter applied to semiconductor device | |

| US6831500B2 (en) | Noise-reduced voltage boosting circuit | |

| JP3742345B2 (ja) | オシレータ回路、該オシレータ回路を備えた半導体装置、及び該オシレータ回路を備えた半導体記憶装置 | |

| JP4159570B2 (ja) | オシレータ回路、該オシレータ回路を備えた半導体装置、及び該オシレータ回路を備えた半導体記憶装置 | |

| JP3925788B2 (ja) | オシレータ回路、該オシレータ回路を備えた半導体装置および半導体記憶装置、および該オシレータ回路の制御方法 | |

| US9025401B2 (en) | Semiconductor memory device including bulk voltage generation circuit | |

| JP2006146868A (ja) | 半導体装置用の内部電圧発生器 | |

| KR100904480B1 (ko) | 반도체 메모리 소자 | |

| JP2016206818A (ja) | 電圧レギュレータ、半導体装置、及び電圧レギュレータの電圧生成方法 | |

| KR101005139B1 (ko) | 반도체 소자의 파워 업 회로 | |

| KR101040001B1 (ko) | 전압 공급 회로 | |

| JP2007181347A (ja) | 昇圧回路 | |

| KR20040092739A (ko) | 전압 방전 회로 | |

| KR19990084907A (ko) | 전류소모가 적은 엑티브용 내부 승압전압 디텍터를 구비하는 반도체 메모리장치의 내부 승압전압 발생기 및 내부 승압전압 디텍터 제어방법 | |

| KR20040016069A (ko) | 승압전압 발생회로 | |

| KR20040043000A (ko) | 2 스테이지 구동 장치 | |

| KR20090011183A (ko) | 오실레이터와 그를 이용한 내부전압 생성회로 | |

| KR20050055212A (ko) | 반도체 장치의 딜레이 회로 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20070517 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20070521 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070801 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070911 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071108 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080408 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080521 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20080618 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080715 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080715 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4159570 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110725 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110725 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110725 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110725 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110725 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120725 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120725 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130725 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |