以下、本発明の一実施形態を図面を参照して説明する。

まず、遊技機の一例であるパチンコ遊技機の全体の構成について説明する。図1はパチンコ遊技機1を正面からみた正面図、図2はパチンコ遊技機1の裏面に配置されている各基板を示す背面図、図3はパチンコ遊技機1の機構板を背面からみた背面図である。なお、以下の実施の形態では、パチンコ遊技機を例に説明を行うが、本発明による遊技機はパチンコ遊技機に限られず、画像式の遊技機やスロット機に適用することもできる。

図1に示すように、パチンコ遊技機1は、額縁状に形成されたガラス扉枠2を有する。ガラス扉枠2の下部表面には打球供給皿3がある。打球供給皿3の下部には、打球供給皿3からあふれた貯留球を貯留する余剰球受皿4と打球を発射する打球操作ハンドル(操作ノブ)5が設けられている。ガラス扉枠2の後方には、遊技盤6が着脱可能に取り付けられている。また、遊技盤6の前面には遊技領域7が設けられている。

遊技領域7の中央付近には、複数種類の図柄を可変表示するための可変表示部9と7セグメントLEDによる可変表示器10とを含む可変表示装置8が設けられている。また、可変表示器10の下部には、4個のLEDからなる通過記憶表示器(普通図柄用記憶表示器)41が設けられている。この実施の形態では、可変表示部9には、「左」、「中」、「右」の3つの図柄表示エリアがある。可変表示装置8の側部には、打球を導く通過ゲート11が設けられている。通過ゲート11を通過した打球は、球出口13を経て始動入賞口14の方に導かれる。通過ゲート11と球出口13との間の通路には、通過ゲート11を通過した打球を検出するゲートスイッチ12がある。また、始動入賞口14に入った入賞球は、遊技盤6の背面に導かれ、始動口スイッチ17によって検出される。また、始動入賞口14の下部には開閉動作を行う可変入賞球装置15が設けられている。可変入賞球装置15は、ソレノイド16によって開状態とされる。

可変入賞球装置15の下部には、特定遊技状態(大当り状態)においてソレノイド21によって開状態とされる開閉板20が設けられている。この実施の形態では、開閉板20が大入賞口を開閉する手段となる。開閉板20から遊技盤6の背面に導かれた入賞球のうち一方(Vゾーン)に入った入賞球はVカウントスイッチ22で検出される。また、開閉板20からの入賞球はカウントスイッチ23で検出される。可変表示装置8の下部には、始動入賞口14に入った入賞球数を表示する4個の表示部を有する始動入賞記憶表示器18が設けられている。この例では、4個を上限として、始動入賞がある毎に、始動入賞記憶表示器18は点灯している表示部を1つずつ増やす。そして、可変表示部9の可変表示が開始される毎に、点灯している表示部を1つ減らす。

遊技盤6には、複数の入賞口19,24が設けられ、遊技球のそれぞれの入賞口19,24への入賞は、対応して設けられている入賞口スイッチ19a,24aによって検出される。遊技領域7の左右周辺には、遊技中に点滅表示される装飾ランプ25が設けられ、下部には、入賞しなかった打球を吸収するアウト口26がある。また、遊技領域7の外側の左右上部には、効果音を発する2つのスピーカ27が設けられている。遊技領域7の外周には、遊技効果LED28aおよび遊技効果ランプ28b,28cが設けられている。

そして、この例では、一方のスピーカ27の近傍に、景品球払出時に点灯する賞球ランプ51が設けられ、他方のスピーカ27の近傍に、補給球が切れたときに点灯する球切れランプ52が設けられている。さらに、図1には、パチンコ遊技台1に隣接して設置され、プリペイドカードが挿入されることによって球貸しを可能にするカードユニット50も示されている。

カードユニット50には、使用可能状態であるか否かを示す使用可表示ランプ151、カード内に記録された残額情報に端数(100円未満の数)が存在する場合にその端数を打球供給皿3の近傍に設けられる度数表示LEDに表示させるための端数表示スイッチ152、カードユニット50がいずれの側のパチンコ遊技機1に対応しているのかを示す連結台方向表示器153、カードユニット50内にカードが投入されていることを示すカード投入表示ランプ154、記録媒体としてのカードが挿入されるカード挿入口155、およびカード挿入口155の裏面に設けられているカードリーダライタの機構を点検する場合にカードユニット50を解放するためのカードユニット錠156が設けられている。

打球発射装置から発射された打球は、打球レールを通って遊技領域7に入り、その後、遊技領域7を下りてくる。打球が通過ゲート11を通ってゲートスイッチ12で検出されると、可変表示器10の表示数字が連続的に変化する状態になる。また、打球が始動入賞口14に入り始動口スイッチ17で検出されると、図柄の変動を開始できる状態であれば、可変表示部9内の図柄が回転を始める。図柄の変動を開始できる状態でなければ、始動入賞記憶を1増やす。

可変表示部9内の画像の回転は、一定時間が経過したときに停止する。停止時の画像の組み合わせが大当り図柄の組み合わせであると、大当り遊技状態に移行する。すなわち、開閉板20が、一定時間経過するまで、または、所定個数(例えば10個)の打球が入賞するまで開放する。そして、開閉板20の開放中に打球が特定入賞領域に入賞しVカウントスイッチ22で検出されると、継続権が発生し開閉板20の開放が再度行われる。継続権の発生は、所定回数(例えば15ラウンド)許容される。

停止時の可変表示部9内の画像の組み合わせが確率変動を伴う大当り図柄の組み合わせである場合には、次に大当りとなる確率が高くなる。すなわち、高確率状態という遊技者にとってさらに有利な状態となる。また、可変表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定時間だけ開状態になる。さらに、高確率状態では、可変表示器10における停止図柄が当り図柄になる確率が高められるとともに、可変入賞球装置15の開放時間と開放回数が高められる。

次に、パチンコ遊技機1の裏面に配置されている各基板について説明する。

図2に示すように、パチンコ遊技機1の裏面では、枠体2A内の機構板の上部に球貯留タンク38が設けられ、パチンコ遊技機1が遊技機設置島に設置された状態でその上方から遊技球が球貯留タンク38に供給される。球貯留タンク38内の遊技球は、誘導樋39を通って球払出機構(図示せず)に至る。

遊技機裏面側では、可変表示部9を制御する可変表示制御ユニット29、遊技制御用マイクロコンピュータ等が搭載された遊技制御基板(主基板)31が設置されている。また、球払出制御を行う払出制御用マイクロコンピュータ等が搭載された払出制御基板37、およびモータの回転力を利用して打球を遊技領域7に発射する打球発射装置が設置されている。さらに、装飾ランプ25、遊技効果LED28a、遊技効果ランプ28b,28c、賞球ランプ51および球切れランプ52に信号を送るためのランプ制御基板35、スピーカ27からの音声発生を制御するための音声制御基板70および打球発射装置を制御するための発射制御基板91も設けられている。なお、払出制御基板37には、エラー表示用LED374も搭載されている。

さらに、DC30V、DC21V、DC12VおよびDC5Vを作成する電源回路が搭載された電源基板910が設けられ、上方には、各種情報を遊技機外部に出力するための各端子を備えたターミナル基板160が設置されている。ターミナル基板160には、少なくとも、後述する球切れ検出スイッチ167の出力を導入して外部出力するための球切れ用端子、賞球個数信号を外部出力するための賞球用端子および球貸し個数信号を外部出力するための球貸し用端子が設けられている。また、中央付近には、主基板31からの各種情報を遊技機外部に出力するための各端子を備えた情報端子盤(外部情報出力装置)34が設置されている。

なお、図2には、ランプ制御基板35および音声制御基板70からの信号を、枠側に設けられている遊技効果LED28a、遊技効果ランプ28b,28c、賞球ランプ51および球切れランプ52に供給するための電飾中継基板A77および度数表示LED等を搭載した残高表示基板74が示されているが、信号中継の必要に応じて他の中継基板も設けられる。

また、図3はパチンコ遊技機1の機構板を背面からみた背面図である。球貯留タンク38に貯留された玉は誘導樋39を通り、図3に示すように、球切れ検出器(球切れスイッチ)187a,187bを通過して球供給樋186a,186bを経て球払出装置97に至る。球切れスイッチ187a,187bは遊技球通路内の遊技球の有無を検出するスイッチであるが、球タンク38内の補給球の不足を検出する球切れ検出スイッチ167も設けられている。球払出装置97から払い出された遊技球は、連絡口45を通ってパチンコ遊技機1の前面に設けられている打球供給皿3に供給される。

なお、図3には示されていないが、球払出装置97の下方には、球振分部材が設けられている。球振分部材は、振分用ソレノイドによって駆動される。例えば、ソレノイドのオン時には、球振分部材は右側に倒れ、オフ時には左側に倒れる。振分用ソレノイドの下方には、近接スイッチによる賞球カウントスイッチおよび球貸しカウントスイッチが設けられている。すなわち、この実施の形態では、賞球払出も球貸しも同一の球払出装置97によってなされる。ただし、賞球払出を行う機構と球貸しを行う機構とが独立している構成であってもよい。

連絡口45の側方には、パチンコ遊技機1の前面に設けられている余剰玉受皿4に連通する余剰玉通路46が形成されている。入賞にもとづく景品球が多数払い出されて打球供給皿3が満杯になり、ついには遊技球が連絡口45に到達した後さらに遊技球が払い出されると遊技球は、余剰玉通路46を経て余剰玉受皿4に導かれる。さらに遊技球が払い出されると、感知レバー47が満タンスイッチ48を押圧して満タンスイッチ48がオンする。その状態では、球払出装置97内のステッピングモータの回転が停止して球払出装置97の動作が停止するとともに打球発射装置34の駆動も停止する。

図4は、主基板31における回路構成の一例を示すブロック図である。なお、図4には、払出制御基板37、ランプ制御基板35、音制御基板70、発射制御基板91および表示制御基板80も示されている。主基板31には、プログラムに従ってパチンコ遊技機1を制御する基本回路53と、ゲートスイッチ12、始動口スイッチ17、Vカウントスイッチ22、カウントスイッチ23、入賞口スイッチ19a,24aおよび賞球カウントスイッチ301Aからの信号を基本回路53に与えるスイッチ回路58と、可変入賞球装置15を開閉するソレノイド16および開閉板20を開閉するソレノイド21等を基本回路53からの指令に従って駆動するソレノイド回路59とが搭載されている。

また、基本回路53から与えられるデータに従って、大当りの発生を示す大当り情報、可変表示部9の画像表示開始に利用された始動入賞球の個数を示す有効始動情報、確率変動が生じたことを示す確変情報等をホール管理コンピュータ等のホストコンピュータに対して出力する情報出力回路64を含む。

基本回路53は、ゲーム制御用のプログラム等を記憶するROM54、ワークメモリとして使用される記憶手段の一例であるRAM55、プログラムに従って制御動作を行うCPU56およびI/Oポート部57を含む。この実施の形態では、ROM54,RAM55はCPU56に内蔵されている。すなわち、CPU56は、1チップマイクロコンピュータである。なお、1チップマイクロコンピュータは、少なくともRAM55が内蔵されていればよく、ROM54およびI/Oポート部57は外付けであっても内蔵されていてもよい。また、RAM55の一部または全部はバックアップ電源でバックアップされているバックアップRAMである。

さらに、主基板31には、基本回路53から与えられるアドレス信号をデコードしてI/Oポート部57のうちのいずれかのI/Oポートを選択するための信号を出力するアドレスデコード回路67が設けられている。なお、球払出装置97から主基板31に入力されるスイッチ情報もあるが、図4ではそれらは省略されている。

また、CPU56には、電源基板910からリセット信号および電源断信号が供給されている。リセット信号がローレベルであるとCPU56はリセット状態となり、リセット信号がハイレベルになるとCPU56は動作可能状態になる。すなわち、リセット信号は、立ち上がりの時点ではリセット解除信号に相当する。また、電源断信号が、電源電圧が所定値以下になったことを示す状態になると、CPU56は、後述する電源断時処理を実行する。

そして、遊技球を打撃して発射する打球発射装置は発射制御基板91上の回路によって制御される駆動モータ94で駆動される。そして、駆動モータ94の駆動力は、操作ノブ5の操作量に従って調整される。すなわち、発射制御基板91上の回路によって、操作ノブ5の操作量に応じた速度で打球が発射されるように制御される。

なお、この実施の形態では、ランプ制御基板35に搭載されているランプ制御手段が、遊技盤に設けられている始動記憶表示器18、ゲート通過記憶表示器41および装飾ランプ25の表示制御を行うとともに、枠側に設けられている遊技効果ランプ・LED28a,28b,28c、賞球ランプ51および球切れランプ52の表示制御を行う。ここで、ランプ制御手段は発光体制御手段の一例である。また、特別図柄を可変表示する可変表示部9および普通図柄を可変表示する可変表示器10の表示制御は、表示制御基板80に搭載されている表示制御手段によって行われる。

図5は、払出制御基板37および球払出装置97の構成要素などの払出に関連する構成要素を示すブロック図である。図5に示すように、満タンスイッチ48からの検出信号は、中継基板71を介して主基板31のI/Oポート57に入力される。満タンスイッチ48は、余剰球受皿4の満タンを検出するスイッチである。また、球切れスイッチ187a,187bからの検出信号も、中継基板72および中継基板71を介して主基板31のI/Oポート57に入力される。

主基板31のCPU56は、球切れスイッチ187a,187bからの検出信号が球切れ状態を示しているか、または、満タンスイッチ48からの検出信号が満タン状態を示していると、払出禁止を指示する払出制御コマンドを送出する。払出禁止を指示する払出制御コマンドを受信すると、払出制御基板37の払出制御用CPU371は球払出処理を停止する。

さらに、賞球カウントスイッチ301Aからの検出信号も、中継基板72および中継基板71を介して主基板31のI/Oポート57に入力される。賞球カウントスイッチ301Aは、球払出装置97の下部に設けられ、実際に払い出された賞球払出球を検出する。

入賞があると、払出制御基板37には、主基板31の出力ポート(ポート0,1)570,571から賞球個数を示す払出制御コマンドが入力される。出力ポート(出力ポート1)571は8ビットのデータを出力し、出力ポート570は1ビットのストローブ信号(INT信号)を出力する。賞球個数を示す払出制御コマンドは、入力バッファ回路373Aを介してI/Oポート372aに入力される。INT信号は、入力バッファ回路373Bを介して払出制御用CPU371の割込端子に入力されている。払出制御用CPU371は、I/Oポート372aを介して払出制御コマンドを入力し、払出制御コマンドに応じて球払出装置97を駆動して賞球払出を行う。

なお、この実施の形態では、払出制御用CPU371は、1チップマイクロコンピュータであり、少なくともRAMが内蔵されている。また、RAMの一部または全部がバックアップ電源でバックアップされているバックアップRAMである。

また、主基板31において、出力ポート570,571の外側にバッファ回路620,68Aが設けられている。バッファ回路620,68Aとして、例えば、汎用のCMOS−ICである74HC250,74HC14が用いられる。このような構成によれば、外部から主基板31の内部に入力される信号が阻止されるので、払出制御基板37から主基板31に信号が与えられる可能性がある信号ラインをさらに確実になくすことができる。なお、バッファ回路620,68Aの出力側にノイズフィルタを設けてもよい。

払出制御用CPU371は、出力ポート372gおよび情報出力回路377を介して、貸し球数を示す球貸し個数信号をターミナル基板160に出力し、ブザー駆動信号をブザー基板75に出力する。ブザー基板75にはブザーが搭載されている。さらに、出力ポート372eを介して、エラー表示用LED374にエラー信号を出力する。

さらに、払出制御基板37の入力ポート372bには、中継基板72を介して、球貸しカウントスイッチ301Bからの検出信号が入力される。球貸しカウントスイッチ301Bは、球払出装置97の下部に設けられ、実際に払い出された貸し球を検出する。払出制御基板37からの払出モータ289への駆動信号は、出力ポート372cおよび中継基板72を介して払出モータ289に伝えられる。払出モータ289の回転に応じて遊技球の払い出しがなされる。

球払出装置97の下方には、球振分部材が設けられている。球振分部材は、振分用ソレノイド310によって駆動される。例えば、ソレノイド310のオン時には、球振分部材は右側に倒れ、オフ時には左側に倒れる。振分用ソレノイド310の下方には、近接スイッチによる賞球カウントスイッチ301Aおよび球貸しカウントスイッチ301Bが設けられている。入賞にもとづく賞球時には、球振分部材は右側に倒れ、払い出された遊技球は賞球カウントスイッチ301Aを通過する。また、球貸し時には、球振分部材は左側に倒れ、払い出された遊技球は球貸しカウントスイッチ301Bを通過する。従って、球払出装置97は、賞球時と球貸し時とで払出流下路を切り替えて、所定数の遊技媒体の払出を行うことができる。

また、払出制御用CPU371には、電源基板910からリセット信号および電源断信号が供給されている。リセット信号がローレベルであると払出制御用CPU371はリセット状態となり、リセット信号がハイレベルになると払出制御用CPU371は動作可能状態になる。電源断信号が、電源電圧が所定値以下になったことを示す状態になると、払出制御用CPU371は、後述する電源断時処理を実行する。

カードユニット50には、カードユニット制御用マイクロコンピュータが搭載されている。また、カードユニット50には、端数表示スイッチ152、連結台方向表示器153、カード投入表示ランプ154およびカード挿入口155が設けられている(図1参照)。残高表示基板74には、打球供給皿3の近傍に設けられている度数表示LED、球貸しスイッチおよび返却スイッチが接続される。

残高表示基板74からカードユニット50には、遊技者の操作に応じて、球貸しスイッチ信号および返却スイッチ信号が払出制御基板37を介して与えられる。また、カードユニット50から残高表示基板74には、プリペイドカードの残高を示すカード残高表示信号および球貸し可表示信号が払出制御基板37を介して与えられる。カードユニット50と払出制御基板37の間では、接続信号(VL信号)、ユニット操作信号(BRDY信号)、球貸し要求信号(BRQ信号)、球貸し完了信号(EXS信号)およびパチンコ機動作信号(PRDY信号)がI/Oポート372fを介してやりとりされる。

パチンコ遊技機1の電源が投入されると、払出制御基板37の払出制御用CPU371は、カードユニット50にPRDY信号を出力する。また、カードユニット制御用マイクロコンピュータは、VL信号を出力する。払出制御用CPU371は、VL信号の入力状態により接続状態/未接続状態を判定する。カードユニット50においてカードが受け付けられ、球貸しスイッチが操作され球貸しスイッチ信号が入力されると、カードユニット制御用マイクロコンピュータは、払出制御基板37にBRDY信号を出力する。

この時点から所定の遅延時間が経過すると、カードユニット制御用マイクロコンピュータは、払出制御基板37にBRQ信号を出力する。そして、払出制御基板37の払出制御用CPU371は、カードユニット50に対するEXS信号を立ち上げ、カードユニット50からのBRQ信号の立ち下がりを検出すると、払出モータ289を駆動し、所定個の貸し球を遊技者に払い出す。このとき、振分用ソレノイド310は駆動状態とされている。すなわち、球振分部材を球貸し側に向ける。そして、払出が完了したら、払出制御用CPU371は、カードユニット50に対するEXS信号を立ち下げる。その後、カードユニット50からのBRDY信号がオン状態でなければ、賞球払出制御を実行する。

以上のように、カードユニット50からの信号は、カードユニット50に直接接続されている払出制御基板37に入力される構成になっている。従って、球貸し制御に関して、カードユニット50から主基板31に信号が入力されることはなく、主基板31の基本回路53にカードユニット50の側から不正に信号が入力される余地はない。

また、プリペイドカードの残高を示すカード残高表示信号および球貸し可表示信号は、払出制御用CPU371を介さずに残高表示基板74に伝達される。残高表示基板74から送出される球貸しスイッチ信号および返却スイッチ信号も、払出制御用CPU371を介さずにカードユニット50に伝達される。

なお、この実施の形態ではカードユニット50が設けられている場合を例にするが、コイン投入に応じてその金額に応じた遊技球を貸し出す場合にも本発明を適用できる。また、この実施の形態では遊技球を貸し出す場合を例にしているが、得点が加算されるものであっても本発明を適用できる。

この実施の形態では、少なくとも主基板31および払出制御基板37におけるRAMの一部または全部が、バックアップ電源でバックアップされている。すなわち、遊技機に対する電力供給が停止しても、所定期間はRAMの内容が保存される。そして、各CPUは、電源電圧の低下を検出すると、所定の処理を行った後に電源復旧待ちの状態になる。また、電源投入時に、各CPUは、RAMにデータが保存されている場合には、保存データにもとづいて電源断前の状態を復元する。

また、払出制御基板37、表示制御基板80、ランプ制御基板35および音声制御基板70にコマンドを送出するために、主基板31の出力ポート(出力ポート0)570からINT信号が各電気部品制御基板に出力される。この場合、例えば、出力ポート570は8ビット構成であって、ビット0が払出制御基板37へのINT信号、ビット1が表示制御基板80へのINT信号、ビット2がランプ制御基板35へのINT信号、ビット3が音声制御基板70へのINT信号の出力用に用いられる。

図6は、表示制御基板80内の回路構成を、可変表示部9の一実現例であるLCD(液晶表示装置)82、可変表示器10、主基板31の出力ポート(ポート0,2)570,572および出力バッファ回路620,62Aとともに示すブロック図である。出力ポート(出力ポート2)572からは8ビットのデータが出力され、出力ポート570からは1ビットのストローブ信号(INT信号)が出力される。

表示制御用CPU101には、電源基板910からリセット信号が供給されている。リセット信号がローレベルであると表示制御用CPU101はリセット状態となり、リセット信号がハイレベルになると表示制御用CPU101は動作可能状態になる。

表示制御用CPU101は、制御データROM102に格納されたプログラムに従って動作し、主基板31からノイズフィルタ107および入力バッファ回路105Bを介してINT信号が入力されると、入力バッファ回路105Aを介して表示制御コマンドを受信する。入力バッファ回路105A,105Bとして、例えば汎用ICである74HC540,74HC14を使用することができる。なお、表示制御用CPU101がI/Oポートを内蔵していない場合には、入力バッファ回路105A,105Bと表示制御用CPU101との間に、I/Oポートが設けられる。

そして、表示制御用CPU101は、受信した表示制御コマンドに従って、LCD82に表示される画面の表示制御を行う。具体的には、表示制御コマンドに応じた指令をVDP103に与える。VDP103は、キャラクタROM86から必要なデータを読み出す。VDP103は、入力したデータに従ってLCD82に表示するための画像データを生成し、R,G,B信号および同期信号をLCD82に出力する。

なお、図6には、VDP103をリセットするためのリセット回路83、VDP103に動作クロックを与えるための発振回路85、および使用頻度の高い画像データを格納するキャラクタROM86も示されている。キャラクタROM86に格納される使用頻度の高い画像データとは、例えば、LCD82に表示される人物、動物、または、文字、図形もしくは記号等からなる画像などである。

入力バッファ回路105A,105Bは、主基板31から表示制御基板80へ向かう方向にのみ信号を通過させることができる。従って、表示制御基板80側から主基板31側に信号が伝わる余地はない。すなわち、入力バッファ回路105A,105Bは、入力ポートともに不可逆性情報入力手段を構成する。表示制御基板80内の回路に不正改造が加えられても、不正改造によって出力される信号が主基板31側に伝わることはない。

なお、出力ポート570,572の出力をそのまま表示制御基板80に出力してもよいが、単方向にのみ信号伝達可能な出力バッファ回路620,62Aを設けることによって、主基板31から表示制御基板80への一方向性の信号伝達をより確実にすることができる。すなわち、出力バッファ回路620,62Aは、出力ポートともに不可逆性情報出力手段を構成する。

また、高周波信号を遮断するノイズフィルタ107として、例えば3端子コンデンサやフェライトビーズが使用されるが、ノイズフィルタ107の存在によって、表示制御コマンドに基板間でノイズが乗ったとしても、その影響は除去される。なお、主基板31のバッファ回路620,62Aの出力側にもノイズフィルタを設けてもよい。

図7は、主基板31およびランプ制御基板35における信号送受信部分を示すブロック図である。この実施の形態では、遊技領域7の外側に設けられている遊技効果LED28a、遊技効果ランプ28b,28cと遊技盤に設けられている装飾ランプ25の点灯/消灯と、賞球ランプ51および球切れランプ52の点灯/消灯とを示すランプ制御コマンドが主基板31からランプ制御基板35に出力される。また、始動記憶表示器18およびゲート通過記憶表示器41の点灯個数を示すランプ制御コマンドも主基板31からランプ制御基板35に出力される。

ランプ制御用CPU351には、電源基板910からリセット信号が供給されている。リセット信号がローレベルであるとランプ制御用CPU351はリセット状態となり、リセット信号がハイレベルになるとランプ制御用CPU351は動作可能状態になる。

図7に示すように、ランプ制御に関するランプ制御コマンドは、基本回路53におけるI/Oポート部57の出力ポート(出力ポート0,3)570,573から出力される。出力ポート(出力ポート3)573は8ビットのデータを出力し、出力ポート570は1ビットのINT信号を出力する。ランプ制御基板35において、主基板31からの制御コマンドは、入力バッファ回路355A,355Bを介してランプ制御用CPU351に入力する。なお、ランプ制御用CPU351がI/Oポートを内蔵していない場合には、入力バッファ回路355A,355Bとランプ制御用CPU351との間に、I/Oポートが設けられる。

ランプ制御基板35において、ランプ制御用CPU351は、各制御コマンドに応じて定義されている遊技効果LED28a、遊技効果ランプ28b,28c、装飾ランプ25の点灯/消灯パターンに従って、遊技効果LED28a、遊技効果ランプ28b,28c、装飾ランプ25に対して点灯/消灯信号を出力する。点灯/消灯信号は、遊技効果LED28a、遊技効果ランプ28b,28c、装飾ランプ25に出力される。なお、点灯/消灯パターンは、ランプ制御用CPU351の内蔵ROMまたは外付けROMに記憶されている。

主基板31において、CPU56は、RAM55の記憶内容に未払出の賞球残数があるときに賞球ランプ51の点灯を指示する制御コマンドを出力し、前述した遊技盤裏面の払出球通路186a,186bの上流に設置されている球切れスイッチ187a,187b(図3参照)が遊技球を検出しなくなると球切れランプ52の点灯を指示する制御コマンドを出力する。ランプ制御基板35において、各制御コマンドは、入力バッファ回路355A,355Bを介してランプ制御用CPU351に入力する。ランプ制御用CPU351は、それらの制御コマンドに応じて、賞球ランプ51および球切れランプ52を点灯/消灯する。なお、点灯/消灯パターンは、ランプ制御用CPU351の内蔵ROMまたは外付けROMに記憶されている。

さらに、ランプ制御用CPU351は、制御コマンドに応じて始動記憶表示器18およびゲート通過記憶表示器41に対して点灯/消灯信号を出力する。

入力バッファ回路355A,355Bとして、例えば、汎用のCMOS−ICである74HC540,74HC14が用いられる。入力バッファ回路355A,355Bは、主基板31からランプ制御基板35へ向かう方向にのみ信号を通過させることができる。従って、ランプ制御基板35側から主基板31側に信号が伝わる余地はない。たとえ、ランプ制御基板35内の回路に不正改造が加えられても、不正改造によって出力される信号がメイン基板31側に伝わることはない。なお、入力バッファ回路355A,355Bの入力側にノイズフィルタを設けてもよい。

また、主基板31において、出力ポート570,573の外側にバッファ回路620,63Aが設けられている。バッファ回路620,63Aとして、例えば、汎用のCMOS−ICである74HC250,74HC14が用いられる。このような構成によれば、外部から主基板31の内部に入力される信号が阻止されるので、ランプ制御基板70から主基板31に信号が与えられる可能性がある信号ラインをさらに確実になくすことができる。なお、バッファ回路620,63Aの出力側にノイズフィルタを設けてもよい。

図8は、主基板31における音声制御コマンドの信号送信部分および音声制御基板70の構成例を示すブロック図である。この実施の形態では、遊技進行に応じて、遊技領域7の外側に設けられているスピーカ27の音声出力を指示するための音声制御コマンドが、主基板31から音声制御基板70に出力される。

音声制御用CPU701には、電源基板910からリセット信号が供給されている。リセット信号がローレベルであると音声制御用CPU701はリセット状態となり、リセット信号がハイレベルになると音声制御用CPU701は動作可能状態になる。

図8に示すように、音声制御コマンドは、基本回路53におけるI/Oポート部57の出力ポート(出力ポート0,4)570,574から出力される。出力ポート(出力ポート4)574からは8ビットのデータが出力され、出力ポート570からは1ビットのINT信号が出力される。音声制御基板70において、主基板31からの各信号は、入力バッファ回路705A,705Bを介して音声制御用CPU701に入力する。なお、音声制御用CPU701がI/Oポートを内蔵していない場合には、入力バッファ回路705A,705Bと音声制御用CPU701との間に、I/Oポートが設けられる。

そして、例えばディジタルシグナルプロセッサによる音声合成回路702は、音声制御用CPU701の指示に応じた音声や効果音を発生し音量切替回路703に出力する。音量切替回路703は、音声制御用CPU701の出力レベルを、設定されている音量に応じたレベルにして音量増幅回路704に出力する。音量増幅回路704は、増幅した音声信号をスピーカ27に出力する。

入力バッファ回路705A,705Bとして、例えば、汎用のCMOS−ICである74HC540,74HC14が用いられる。入力バッファ回路705A,705Bは、主基板31から音声制御基板70へ向かう方向にのみ信号を通過させることができる。よって、音声制御基板70側から主基板31側に信号が伝わる余地はない。従って、音声制御基板70内の回路に不正改造が加えられても、不正改造によって出力される信号が主基板31側に伝わることはない。なお、入力バッファ回路705A,705Bの入力側にノイズフィルタを設けてもよい。

また、主基板31において、出力ポート570,574の外側にバッファ回路620,67Aが設けられている。バッファ回路620,67Aとして、例えば、汎用のCMOS−ICである74HC250,74HC14が用いられる。このような構成によれば、外部から主基板31の内部に入力される信号が阻止されるので、音声制御基板70から主基板31に信号が与えられる可能性がある信号ラインをさらに確実になくすことができる。なお、バッファ回路620,67Aの出力側にノイズフィルタを設けてもよい。

図9は、払出制御基板37および打球発射を制御する制御手段が搭載されている発射制御基板91を示すブロック図である。図9に示すように、発射制御信号が、払出制御基板37における出力ポート372dから発射制御基板91に出力される。発射制御基板91において、払出制御基板37からの発射制御信号は、バッファ回路815を介してモータ駆動回路813に入力する。

モータ駆動回路813は、例えば、遊技球を発射する球打ち動作および次の遊技球を発射する準備である復旧・球補給動作の各期間における駆動モータ94の回転速度を制御する電圧を発生する。球打ち動作期間では、操作ノブ5に対する回転操作角に対応して徐々に増加する電圧を発生し、復旧・球補給動作期間では、あらかじめ定められた所定の電圧を発生する。

タッチセンサ回路93は、操作ノブ5に取り付けられた人体検出用の電極に人体が接触している間、発射許可信号をモータ駆動回路813に出力する。また、モータ駆動回路813には、払出制御基板37からの発射制御信号が与えられる。モータ駆動回路813は、発射制御信号および発射許可信号がオンすると、球打ち動作期間および復旧・球補給動作期間のシーケンス動作の切り替えを制御するとともに、駆動モータ94の駆動に必要な駆動パターン信号および駆動電圧切替信号を発生する。

図10は、電源基板910から各基板に供給される直流電圧等を示すブロック図である。図10に示すように、電源基板910には各種直流電圧を生成する電源回路が搭載される。また、必要に応じて、AC24Vも各基板に供給される。

この実施の形態では、主基板31には、DC30V、DC12V、DC5Vおよびバックアップ電源電圧(VBB)が供給される。ランプ制御基板35には、DC30V、DC21V、DC12VおよびDC5Vが供給される。払出制御基板37には、AC24V、DC30V、DC12V、DC5Vおよびバックアップ電源電圧(VBB)が供給される。そして、発射制御基板91には、DC30V、DC12VおよびDC5Vが供給される。また、音声制御基板70には、DC12およびDC5Vが供給される。表示制御基板80には、DC12VおよびDC5Vが供給される。さらに、各基板には、電源基板910からリセット信号が供給される。

図10に示すように、各基板に供給される電圧のグラウンド側は電源基板910において共通にとられている。従って、各基板におけるグラウンドレベルは共通である。すると、ある基板から他の基板に伝達される信号として、電圧レベルをそのまま使用することができる。グラウンドレベルが共通化されていない基板があると、そのような基板に対する信号伝達を行う場合には、フォトカプラ等の非接触式の情報伝達手段を用いる必要がありコストアップの要因となる。しかし、この実施の形態のように、全ての基板のグラウンドレベルが共通化されている場合には、フォトカプラ等を用いる必要はない。

図11は、遊技機の電源基板910の一構成例を示すブロック図である。電源基板910は、主基板31、表示制御基板80、音声制御基板70、ランプ制御基板35および払出制御基板37等の電気部品制御基板と独立して設置され、遊技機内の各電気部品制御基板および機構部品が使用する電圧を生成する。この例では、AC24V、VSL(DC+30V)、DC+21V、DC+12VおよびDC+5Vを生成する。また、バックアップ電源となるコンデンサ916は、DC+5Vすなわち各基板上のIC等を駆動する電源のラインから充電される。

トランス911は、交流電源からの交流電圧を24Vに変換する。AC24V電圧は、コネクタ915に出力される。また、整流回路912は、AC24Vから+30Vの直流電圧を生成し、DC−DCコンバータ913およびコネクタ915に出力する。DC−DCコンバータ913は、+21V、+12Vおよび+5Vを生成してコネクタ915に出力する。コネクタ915は例えば中継基板に接続され、中継基板から各電気部品制御基板および機構部品に必要な電圧の電力が供給される。

ただし、電源基板910に各電気部品制御基板に至る各コネクタを設け、電源基板910から、中継基板を介さずにそれぞれの基板に至る各電圧を供給するようにしてもよい。

DC−DCコンバータ913からの+5Vラインは分岐してバックアップ+5Vラインを形成する。バックアップ+5Vラインとグラウンドレベルとの間には大容量のコンデンサ916が接続されている。コンデンサ916は、遊技機に対する電力供給が遮断されたときの電気部品制御基板のバックアップRAM(電源バックアップされているRAMすなわち記憶内容保持状態となりうる記憶手段)に対して記憶状態を保持できるように電力を供給するバックアップ電源となる。また、+5Vラインとバックアップ+5Vラインとの間に、逆流防止用のダイオード917が挿入される。

なお、バックアップ電源として、+5V電源から充電可能な電池を用いてもよい。電池を用いる場合には、+5V電源から電力供給されない状態が所定時間継続すると容量がなくなるような充電池が用いられる。

また、電源基板910には、電源監視用IC902が搭載されている。電源監視用IC902は、VSL電源電圧を導入し、VSL電源電圧を監視することによって電源断の発生を検出する。具体的には、VSL電源電圧が所定値(この例では+22V)以下になったら、電源断が生ずるとして電圧低下信号を出力する。なお、監視対象の電源電圧は、各電気部品制御基板に搭載されている回路素子の電源電圧(この例では+5V)よりも高い電圧であることが好ましい。この例では、交流から直流に変換された直後の電圧であるVSLが用いられている。電源監視用IC902からの電圧低下信号は、主基板31や払出制御基板37等に供給される。

電源監視用IC902が電源断を検知するための所定値は、通常時の電圧より低いが、各電気部品制御基板上のCPUが暫くの間動作しうる程度の電圧である。また、電源監視用IC902が、CPU等の回路素子を駆動するための電圧(この例では+5V)よりも高く、また、交流から直流に変換された直後の電圧を監視するように構成されているので、CPUが必要とする電圧に対して監視範囲を広げることができる。従って、より精密な監視を行うことができる。

さらに、監視電圧としてVSL(+30V)を用いる場合には、遊技機の各種スイッチに供給される電圧が+12Vであることから、電源瞬断時のスイッチオン誤検出の防止も期待できる。すなわち、+30V電源の電圧を監視すると、+30V作成の以降に作られる+12Vが落ち始める以前の段階でそれの低下を検出できる。よって、+12V電源の電圧が低下するとスイッチ出力がオン状態を呈するようになるが、+12Vより早く低下する+30V電源電圧を監視して電源断を認識すれば、スイッチ出力がオン状態を呈する前に電源復旧待ちの状態に入ってスイッチ出力を検出しない状態となることができる。

また、電源監視用IC902は、電気部品制御基板とは別個の電源基板910に搭載されているので、電源監視回路から複数の電気部品制御基板に電圧低下信号を供給することができる。電圧低下信号を必要とする電気部品制御基板が幾つあっても第1の電源監視手段は1つ設けられていればよいので、各電気部品制御基板における各電気部品制御手段が後述する復帰制御を行っても、遊技機のコストはさほど上昇しない。

なお、図11に示された構成では、電源監視用IC902の検出出力(電圧低下信号)は、バッファ回路918,919を介してそれぞれの電気部品制御基板(例えば主基板31と払出制御基板37)に伝達されるが、例えば、1つの検出出力を中継基板に伝達し、中継基板から各電気部品制御基板に同じ信号を分配する構成でもよい。また、電圧低下信号を必要とする基板数に応じたバッファ回路を設けてもよい。

さらに、電源基板910には、各基板にリセット信号を供給するリセット管理回路940が搭載されている。

図12は、リセット管理回路940の構成例を示すブロック図である。リセット管理回路940において、リセットIC651は、電源投入時に、外付けのコンデンサの容量で決まる所定時間だけ出力をローレベルとし、所定時間が経過すると出力をハイレベルにする。リセットIC651の出力は、各回路941〜949を介して、バッファ回路961〜964および遅延回路960に供給される。遅延回路960の出力はバッファ回路965に入力する。そして、バッファ回路961〜965が各電気部品制御基板にリセット信号として供給される。従って、リセットIC651の出力がハイレベルになると、各電気部品制御基板におけるCPUが動作可能状態になる。

また、リセットIC651は、電源監視用IC902が監視する電源電圧と等しい電源電圧であるVSLの電源電圧を監視して電圧値が所定値(電源監視用IC902が電圧低下信号を出力する電源電圧値よりも低い値)以下になるとローレベルになる。従って、CPU56および払出制御用CPU371は、電源監視用IC902からの電圧低下信号(電源断信号)に応じて所定の電力供給停止準備処理を行った後、システムリセットされることになる。

図12に示すように、リセットIC651からのリセット信号は、NAND回路947に入力されるとともに、反転回路(NOT回路)944を介してカウンタIC941のクリア端子に入力される。カウンタIC941は、クリア端子への入力がローレベルになると、発振器943からのクロック信号をカウントする。そして、カウンタIC941のQ5出力がNOT回路945,946を介してNAND回路947に入力される。

また、カウンタIC941のQ6出力は、フリップフロップ(FF)942のクロック端子に入力される。フリップフロップ942のD入力はハイレベルに固定され、Q出力は論理和回路(OR回路)949に入力される。OR回路949の他方の入力には、NAND回路947の出力がNOT回路948を介して導入される。そして、OR回路949の出力が、バッファ回路961〜965を介して各CPUに供給されている。このような構成によれば、電源投入時に、各CPUのリセット端子に2回のリセット信号(ローレベル信号)が与えられるので、各CPUは、確実に動作を開始する。

そして、例えば、第1の電源監視回路である電源監視用IC902の検出電圧(電圧低下信号を出力することになる電圧)を+22Vとし、第2の電源監視回路に相当するリセットICの検出電圧を+9Vとする。そのように構成した場合には、第1の電源監視回路と第2の電源監視回路とは、同一の電源VSLの電圧を監視するので、第1の電圧監視回路が電圧低下信号を出力するタイミングと第2の電圧監視回路が電圧低下信号を出力するタイミングの差を所望の所定期間に確実に設定することができる。所望の所定期間とは、第1の電源監視回路からの電圧低下信号に応じて電力供給停止準備処理を開始してから電力供給停止準備処理が確実に完了するまでの期間である。

この例では、第1の電源監視手段が検出信号を出力することになる第1検出条件は+30V電源電圧が+22Vにまで低下したことであり、第2の電源監視手段が検出信号を出力することになる第2検出条件は+30V電源電圧が+9Vにまで低下したことになる。ただし、ここで用いられている電圧値は一例であって、他の値を用いてもよい。

ただし、監視範囲が狭まるが、第1の電圧監視回路および第2の電圧監視回路の監視電圧として+5V電源電圧を用いることも可能である。その場合にも、第1の電圧監視回路の検出電圧は、第2の電圧監視回路の検出電圧よりも高く設定される。

主基板31および払出制御基板37のCPU56および払出制御用CPU371の駆動電源である+5V電源から電力が供給されていない間、RAMの少なくとも一部は、電源基板910から供給されるバックアップ電源によってバックアップされ、遊技機に対する電源が断しても内容は保存される。そして、+5V電源が復旧すると、リセット管理回路940からのリセット信号がハイレベルになるので、CPU56および払出制御用CPU371は、通常の動作状態に復帰する。そのとき、必要なデータがバックアップRAMに保存されているので、停電等からの復旧時に停電発生時の遊技状態に復帰することができる。

なお、図12では、電源投入時に各電気部品制御基板のCPUのリセット端子に2回のリセット信号(ローレベル信号)が与えられる構成が示されたが、リセット信号の立ち上がりタイミングが1回しかなくても確実にリセット解除されるCPUを使用する場合には、符号941〜949で示された回路素子は不要である。その場合、リセットIC651の出力がそのままバッファ回路961〜964および遅延回路960に接続される。

この実施の形態では、電源基板910から各電気部品制御基板のCPUにリセット信号が供給される。また、遅延回路960は、主基板31のCPU56に対するリセット信号を遅延させる。従って、電源投入時に、主基板31のCPU56に対するリセット信号は、他の電気部品制御基板のCPUに対するリセット信号よりも遅く立ち上がる。

例えば、主基板31のCPU56が他の電気部品制御基板に対して制御コマンドを出力する際に、他の電気部品制御基板におけるCPUは既に立ち上がっているので、制御コマンドは確実に受信側の電気部品制御基板のCPUで受信される。

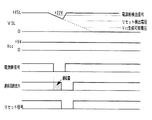

図13は、リセット管理回路940のリセットIC651とその周辺のICの出力信号の様子を示すタイミング図である。図13に示すように、リセットIC651の出力は、電源電圧のレベルが所定値(各CPUの正常な動作を担保することが可能なレベル、この例では各CPUは+5Vで動作可能なので例えば+9V)を越えるとハイレベルになる。リセットIC651の出力がハイレベルになると、カウンタIC941のクリア状態が解除されるので、カウンタIC941は発振器943の出力クロック信号のカウントを開始する。発振器943の発振周波数は例えば11.776MHzである。

カウンタIC941が16クロックをカウントするとQ5出力が立ち上がる。また、32クロックをカウントするとQ6出力がハイレベルに立ち上がる。カウンタIC941のQ6出力が立ち上がると、FF942の出力がハイレベルになる。IC947は、カウンタIC941のQ6出力とリセットIC651の出力との論理積を反転する。OR回路949は、IC947の出力を反転するIC948の出力とFF942の出力との論理和をとって、図13に示すような信号を出力する。

バッファ回路961〜964はIC949の出力をそのまま通過させて主基板31のCPU56以外のCPUの対してリセット信号として出力する。また、バッファ回路965は、IC949の出力が遅延された信号を主基板31のCPU56に対してリセット信号として出力する。

従って、遊技機の電源オン時には、図13にIC961〜964出力およびIC965出力として示すように、各CPUのリセット端子に対して一旦リセット解除状態(ハイレベル)になってから再度リセット状態(ローレベル)になるような信号が供給される。すなわち、電源オン時には、各CPUをリセット状態とするようなローレベル信号が2回発生することになる。また、リセット解除を示すハイレベルが2回発生しているということもできる。その結果、各CPUは、最初のリセット解除を示すローレベルからハイレベルへの変化によって起動しなかったとしても、2回目のローレベルからハイレベルへの変化によって確実に起動することができる。よって、遊技機の電源投入時に、確実に遊技制御が開始される。

図13に示すように、主基板31へのリセット信号がリセット解除状態となるタイミングは、他の基板へのリセット信号がリセット解除状態となるタイミングよりも遅い。従って、主基板31のCPU56が他の電気部品制御基板に対して制御コマンドを出力する際に、他の電気部品制御基板におけるCPUは既に立ち上がっているので、制御コマンドは確実に受信側の電気部品制御基板のCPUで受信される。

なお、ここでは、リセット管理回路940が、主基板31に与えられるリセット解除タイミングと他の複数の電気部品制御基板に送られるリセット解除タイミングとをずらせるように制御したが、他の複数の電気部品制御基板に与えられるリセット解除タイミングをそれぞれずらすことも容易である。例えば、図12に示した回路構成において、バッファ回路961〜964の前に遅延回路を置き、各遅延回路の遅延量に差を設ければ、主基板31および他の電気部品制御基板に与えられるリセット解除タイミングのそれぞれの間で差を付けることができる。すなわち、各電気部品制御手段を、あらかじめ定められた順序で立ち上げることができる。

各電気部品制御基板のそれぞれにおいて自身が使用するリセット信号を作成するように構成した場合には、それぞれのリセット信号のリセット解除タイミングを調整することが難しいが、この実施の形態では、電源基板910におけるリセット管理回路940が一括して各基板に対するリセット信号を作成するので、立ち上げの順序制御を容易に調整することができる。

なお、この実施の形態では、図12に例示したような立上管理手段が電源基板910に搭載されたが、立上管理手段を搭載した立上管理基板を別個に設けてもよい。ただし、一般にリセット信号は電源電圧の立ち上がりを利用して作成されるので、電源基板910を立上管理基板とした場合には、各リセット信号をより容易に作成できるメリットがある。

次に遊技制御動作について説明する。

図14は、主基板31におけるCPU56が実行するメイン処理を示すフローチャートである。遊技機に対する電源が投入されCPU56のリセットが解除されると、メイン処理において、CPU56は、まず、必要な初期設定を行う(ステップS1)。

そして、電源断時にバックアップRAM領域のデータ保護処理(例えばパリティデータの付加等の電力供給停止準備処理)が行われたか否か確認する(ステップS2)。この実施の形態では、不測の電源断が生じた場合には、バックアップRAM領域のデータを保護するための電力供給停止準備処理が行われている。そのような処理が行われていた場合をバックアップありとする。バックアップなしを確認したら、CPU56は初期化処理を実行する(ステップS2,S3)。

この実施の形態では、バックアップRAM領域にバックアップデータがあるか否かは、電源断時にバックアップRAM領域に設定されるバックアップフラグの状態によって確認される。例えば、バックアップフラグ領域に「55H」が設定されていればバックアップあり(オン状態)を意味し、「55H」以外の値が設定されていればバックアップなし(オフ状態)を意味する。バックアップフラグ領域に設定されている「55H」は、電力供給停止準備処理においてバックアップRAM領域のデータ保護処理が完了したときに設定されたデータであり、バックアップRAM領域のデータにもとづくパリティコードである。

バックアップRAM領域にバックアップデータがある場合には、CPU56は、バックアップRAM領域のデータチェック(例えばパリティチェック)を行う(ステップS4)。不測の電源断が生じた後に復旧した場合には、バックアップRAM領域のデータは保存されていたはずであるから、チェック結果は正常になる。チェック結果が正常でない場合には、内部状態を電源断時の状態に戻すことができないので、停電復旧時でない電源投入時に実行される初期化処理を実行する(ステップS5,S3)。

チェック結果が正常であれば、CPU56は、内部状態を電源断時の状態に戻すための遊技状態復旧処理を行う(ステップS6)。図15に示すように、バックアップフラグの値が「55H」に設定され、かつ、チェック結果が正常である場合に、ステップS6の遊技状態復旧処理が実行される。そして、バックアップRAM領域に保存されていたPC(プログラムカウンタ)の退避値がPCに設定され、そのアドレスに復帰する(ステップS7)。

通常の初期化処理の実行(ステップS3)が完了すると、メイン処理で、タイマ割込フラグの監視(ステップS9)の確認が行われるループ処理に移行する。なお、ループ内では、表示用乱数更新処理(ステップS8)も実行される。

なお、この実施の形態では、ステップS2でバックアップデータの有無が確認された後、バックアップデータが存在する場合にステップS4でバックアップ領域のチェックが行われたが、逆に、バックアップ領域のチェック結果が正常であったことが確認された後、バックアップデータの有無の確認を行うようにしてもよい。また、バックアップデータの有無の確認、またはバックアップ領域のチェックの何れか一方の確認を行うことによって、停電復旧処理を実行するか否かを判定してもよい。

また、例えば停電復旧処理を実行するか否か判断する場合のパリティチェック(ステップS4)の際に、すなわち、遊技状態を復旧するか否か判断する際に、保存されていたRAMデータにおける特別プロセスフラグ等や始動入賞記憶数データによって、遊技機が遊技待機状態(図柄変動中でなく、大当り遊技中でなく、確変中でなく、また、始動入賞記憶がない状態)であることが確認されたら、遊技状態復旧処理を行わずに初期化処理を実行するようにしてもよい。

図16は、ステップS1の初期設定処理を示すフローチャートである。初期設定処理において、CPU56は、まず、割込禁止に設定する(ステップS1a)。割込禁止に設定すると、CPU56は、割込モードを割込モード2に設定し(ステップS1b)、スタックポインタにスタックポインタ指定アドレスを設定する(ステップS1c)。そして、CPU56は、内蔵デバイスレジスタの初期化を行う(ステップS1d)。また、内蔵デバイス(内蔵周辺回路)であるCTC(カウンタ/タイマ)およびPIO(パラレル入出力ポート)の初期化(ステップS1e)を行った後、RAMをアクセス可能状態に設定する(ステップS1f)。

この実施の形態で用いられているCPU56には、マスク可能な割込(INT)のモードとして以下の3種類のモードが用意されている。そのうちの割込モード2に設定されると、各内蔵デバイスからの割込要求を容易に処理することが可能になり、また、プログラムにおける任意の位置に割込処理を設置することが可能になる。なお、マスク可能な割込が発生すると、CPU56は、自動的に割込禁止状態に設定するとともに、プログラムカウンタの内容をスタックにセーブする。

図17は、通常の初期化処理(ステップS3)の処理を示すフローチャートである。図17に示すように、初期化処理では、RAMのクリア処理が行われる(ステップS3a)。次いで、作業領域初期設定テーブルのアドレス値にもとづいて、所定の作業領域(例えば、普通図柄判定用乱数カウンタ、普通図柄判定用バッファ、特別図柄左中右図柄バッファ、払出コマンド格納ポインタなど)に初期値を設定する初期値設定処理(ステップS3b)が行われる。

そして、2ms毎に定期的にタイマ割込がかかるようにCPU56に設けられているCTCのレジスタの設定が行われる(ステップS3c)。すなわち、初期値として2msに相当する値が所定のレジスタ(時間定数レジスタ)に設定される。そして、初期設定処理(ステップS1)において割込禁止(図16参照)にされているので、初期化処理を終える前に割込が許可される(ステップS3d)。

従って、この実施の形態では、CPU56の内蔵CTCが繰り返しタイマ割込を発生するように設定される。この実施の形態では、繰り返し周期は2msに設定される。そして、図18に示すように、タイマ割込が発生すると、CPU56は、タイマ割込フラグをセットする(ステップS12)。

CPU56は、ステップS9において、タイマ割込フラグがセットされたことを検出すると、タイマ割込フラグをリセットするとともに(ステップS10)、遊技制御処理を実行する(ステップS11)。以上の制御によって、この実施の形態では、遊技制御処理は2ms毎に起動されることになる。なお、この実施の形態では、タイマ割込処理ではフラグセットのみがなされ、遊技制御処理はメイン処理において実行されるが、タイマ割込処理で遊技制御処理を実行してもよい。

図19は、ステップS11の遊技制御処理を示すフローチャートである。遊技制御処理において、CPU56は、まず、スイッチ回路58を介して、ゲートセンサ12、始動口センサ17、カウントセンサ23および入賞口スイッチ19a,24aの状態を入力し、各入賞口や入賞装置に対する入賞があったか否か判定する(スイッチ処理:ステップS21)。

次いで、パチンコ遊技機1の内部に備えられている自己診断機能によって種々の異常診断処理が行われ、その結果に応じて必要ならば警報が発せられる(エラー処理:ステップS22)。

次に、遊技制御に用いられる大当り判定用の乱数等の各判定用乱数を示す各カウンタを更新する処理を行う(ステップS23)。CPU56は、さらに、停止図柄の種類を決定する乱数等の表示用乱数を更新する処理を行う(ステップS24)。

さらに、CPU56は、特別図柄プロセス処理を行う(ステップS25)。特別図柄プロセス制御では、遊技状態に応じてパチンコ遊技機1を所定の順序で制御するための特別図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、特別図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。

また、普通図柄プロセス処理を行う(ステップS26)。普通図柄プロセス処理では、7セグメントLEDによる可変表示器10を所定の順序で制御するための普通図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、普通図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。

さらに、CPU56は、払出制御基板37等に送出される制御コマンドをRAM55の所定の領域に設定して各電気部品制御基板に対して制御コマンドを送出する処理を行う(コマンド制御処理:ステップS27)。

次いで、CPU56は、例えばホール管理用コンピュータに供給される大当り情報、始動情報、確率変動情報などのデータを出力するデータ出力処理を行う(ステップS29)。

また、CPU56は、所定の条件が成立したときにソレノイド回路59に駆動指令を行う(ステップS30)。ソレノイド回路59は、駆動指令に応じてソレノイド16,21を駆動し、可変入賞球装置15または開閉板20を開状態または閉状態とする。

そして、CPU56は、各入賞口への入賞を検出するためのスイッチ17,23,19a,24aの検出出力にもとづく賞球数の設定などを行う(ステップS31)。具体的には、入賞検出に応じて払出制御基板37に払出制御コマンドを出力する。払出制御基板37に搭載されている払出制御用CPU371は、払出制御コマンドに応じて賞球払出装置97Aを駆動する。

以上のように、メイン処理には遊技制御処理に移行すべきか否かを判定する処理が含まれ、CPU56の内部タイマが定期的に発生するタイマ割込にもとづくタイマ割込処理で遊技制御処理に移行すべきか否かを判定するためのフラグがセットされるので、遊技制御処理の全てが確実に実行される。つまり、遊技制御処理の全てが実行されるまでは、次回の遊技制御処理に移行すべきか否かの判定が行われないので、遊技制御処理中の全ての各処理が実行完了することは保証されている。

なお、ここでは、主基板31のCPU56が実行する遊技制御処理は、CPU56の内部タイマが定期的に発生するタイマ割込にもとづくタイマ割込処理でセットされるフラグに応じて実行されたが、定期的に(例えば2ms毎)信号を発生するハードウェア回路を設け、その回路からの信号をCPU56の外部割込端子に導入し、割込信号によって遊技制御処理に移行すべきか否かを判定するためのフラグをセットするようにしてもよい。

図20は、電源基板910からの電源断信号にもとづくNMIに応じて実行される停電発生NMI処理の一例を示すフローチャートである。停電発生NMI処理において、CPU56は、まず、停電時などの電源断時直前の割込許可/禁止状態をバックアップするために、割込禁止フラグの内容をパリティフラグに格納する(ステップS41)。

次いで、割込禁止に設定する(ステップS42)。停電発生NMI処理ではRAM内容の保存を確実にするためにチェックサムの生成処理を行う。その処理中に他の割込処理が行われたのではチェックサムの生成処理が完了しないうちにCPUが動作し得ない電圧にまで低下してしまうことが考えられるので、まず、他の割込が生じないような設定がなされる。なお、停電発生NMI処理におけるステップS44〜S50は、電力供給停止準備処理の一例である。また、割込処理中では他の割込がかからないような仕様のCPUを用いている場合には、ステップS42の処理は不要である。

次いで、CPU56は、バックアップフラグが既にセットされているか否か確認する(ステップS42)。バックアップフラグが既にセットされていれば、以後の処理を行わない。バックアップフラグがセットされていなければ、以下の電力供給停止準備処理を実行する。すなわち、ステップS44からステップS50の処理を実行する。

まず、各レジスタの内容をバックアップRAM領域に格納する(ステップS44)。その後、バックアップフラグをセットする(ステップS45)。そして、バックアップRAM領域のバックアップチェックデータ領域に適当な初期値を設定し(ステップS46)、初期値およびバックアップRAM領域のデータについて順次排他的論理和をとったあと反転し(ステップS47)、最終的な演算値をバックアップパリティデータ領域に設定する(ステップS48)。また、RAMアクセス禁止状態にする(ステップS49)。電源電圧が低下していくときには、各種信号線のレベルが不安定になってRAM内容が化ける可能性があるが、このようにRAMアクセス禁止状態にしておけば、バックアップRAM内のデータが化けることはない。

さらに、CPU56は、主基板31に搭載されている全ての出力ポートに対してクリア信号を出力する。すると、全ての出力ポートは、クリア信号によりクリアされオフ状態とされる(ステップS50)。

次いで、CPU56は、ループ処理にはいる。すなわち、何らの処理もしない状態になる。従って、リセット管理回路940からのリセット信号がローレベルになって動作禁止状態にされる前に、内部的に動作停止状態になる。よって、電源断時に確実にCPU56は動作停止する。その結果、上述したRAMアクセス禁止の制御および動作停止制御によって、電源電圧が低下していくことに伴って生ずる可能性がある異常動作に起因するRAMの内容破壊等を確実に防止することができる。

なお、この実施の形態では、停電発生NMI処理では最終部でプログラムをループ状態にしたが、ホールト(HALT)命令を発行するように構成してもよい。

また、レジスタの内容をRAM領域に格納した後にセットされるバックアップフラグは、上述したように、電源投入時において復旧すべきバックアップデータがあるか否か(停電からの復旧か否か)を判断する際に使用される。また、ステップS41からS50の処理は、CPU56がシステムリセット回路65からのシステムリセット信号を受ける前に完了する。換言すれば、システムリセット回路65からのシステムリセット信号を受ける前に完了するように、電圧監視回路の検出電圧の設定が行われている。

この実施の形態では、電力供給停止準備処理開始時に、バックアップフラグの確認が行われる。そして、バックアップフラグが既にセットされている場合には電力供給停止準備処理を実行しない。上述したように、バックアップフラグは、必要なデータのバックアップが完了し、その後電力供給停止準備処理が完了したことを示すフラグである。従って、例えば、リセット待ちのループ状態で何らかの原因で再度NMIが発生したとしても、電力供給停止準備処理が重複して実行されてしまうようなことはない。

ただし、割込処理中では他の割込がかからないような仕様のCPUを用いている場合には、ステップS43の判断は不要である。

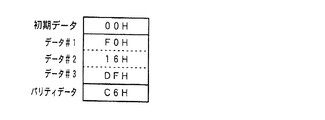

図21は、バックアップパリティデータ作成方法の一例を説明するための説明図である。ただし、図21に示す例では、簡単のために、バックアップデータRAM領域のデータのサイズを3バイトとする。電源電圧低下にもとづく停電発生処理において、図21に示すように、バックアップチェックデータ領域に、初期データ(この例では00H)が設定される。次に、「00H」と「F0H」の排他的論理和がとられ、その結果と「16H」の排他的論理和がとられる。さらに、その結果と「DFH」の排他的論理和がとられる。そして、その結果(この例では「39H」)を反転して得られた値(この例では「C6H」)がバックアップパリティデータ領域に設定される。

電源が再投入されたときには、停電復旧処理においてパリティ診断が行われる。バックアップ領域の全データがそのまま保存されていれば、電源再投入時に、図21に示すようなデータがバックアップ領域に設定されている。

ステップS4の処理において、CPU56は、電源発生MNI処理にて実行された処理と同様の処理を行う。すなわち、バックアップチェックデータ領域に、初期データ(この例では00H)が設定され、「00H」と「F0H」の排他的論理和がとられ、その結果と「16H」の排他的論理和がとられる。さらに、その結果と「DFH」の排他的論理和がとられる。そして、その結果(この例では「39H」)を反転した最終演算結果を得る。バックアップ領域の全データがそのまま保存されていれば、最終的な演算結果は、「C6H」、すなわちバックアップチェックデータ領域に設定されているデータと一致する。バックアップRAM領域内のデータにビット誤りが生じていた場合には、最終的な演算結果は「C6H」にならない。

よって、CPU56は、最終的な演算結果とバックアップチェックデータ領域に設定されているデータとを比較して、一致すればパリティ診断正常とする。一致しなければ、パリティ診断異常とする。

以上のように、この実施の形態では、遊技制御手段には、遊技機の電源が断しても、所定期間電源バックアップされる記憶手段(この例ではバックアップRAM)が設けられ、電源投入時に、CPU56(具体的にはCPU56が実行するプログラム)は、記憶手段がバックアップ状態にあればバックアップデータにもとづいて遊技状態を回復させる遊技状態復旧処理(ステップS6)を行うように構成される。

なお、この実施の形態では、電源基板910において、電源監視用IC902と、リセット管理回路940は、同一の電源電圧を監視しているが、異なる電源電圧を監視してもよい。例えば、電源監視用IC902が+30V電源電圧を監視し、リセット管理回路940が+5V電源電圧を監視してもよい。そして、リセット管理回路940がリセット信号をローレベルにするタイミングは電源監視用IC902がNMI割込信号(電源断信号)を発生するタイミングに対して遅くなるように、システムリセット回路65のしきい値レベル(システムリセット信号を発生する電圧レベル)が設定される。例えば、しきい値は4.25Vである。4.25Vは、通常時の電圧より低いが、CPU56が暫くの間動作しうる程度の電圧である。

また、上記の実施の形態では、CPU56は、マスク不能割込端子(NMI端子)を介して電源基板からのNMI割込信号(電源監視手段からのNMI割込信号)を検知したが、NMI割込信号をマスク可能割込割込端子(IRQ端子)に導入してもよい。その場合には、割込処理(IRQ処理)で電力供給停止準備処理が実行される。また、入力ポートを介して電源基板からのNMI割込信号を検知してもよい。その場合には、メイン処理において入力ポートの監視が行われる。

また、NMI割込信号に変えて、IRQ端子を介して電源基板からの割込信号を検知する場合に、メイン処理のステップS11における遊技制御処理の開始時にIRQ割込マスクをセットし、遊技制御処理の終了時にIRQ割込マスクを解除するようにしてもよい。そのようにすれば、遊技制御処理の開始前および終了後に割込がかかることになって、遊技制御処理が中途で中断されることはない。従って、払出制御コマンドを払出制御基板37に送出しているときなどにコマンド送出が中断されてしまうようなことはない。よって、停電が発生するようなときでも、払出制御コマンド等は確実に送出完了する。

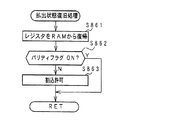

図22は、払出制御用CPU371のメイン処理を示すフローチャートである。メイン処理では、払出制御用CPU371は、まず、必要な初期設定を行う(ステップS701)。

そして、払出制御用CPU371は、払出制御用のバックアップRAM領域にバックアップデータが存在しているか否かの確認を行う(ステップS702)。すなわち、例えば、主基板31のCPU56の処理と同様に、電源断時にセットされるバックアップフラグがセット状態になっているか否かによって、バックアップデータが存在しているか否か確認する。バックアップフラグがセット状態になっている場合には、バックアップデータありと判断する。バックアップデータなしと判断された場合には、前回の電源オフ時に未払出の遊技球がなかったことになり、内部状態を電源断時の状態に戻す必要がない。従って、払出制御用CPU371は、停電復旧時でない電源投入時に実行される初期化処理を実行する(ステップS702,S703)。

バックアップRAM領域にバックアップデータが存在している場合には、払出制御用CPU371は、バックアップRAM領域のデータチェック(この例ではパリティチェック)を行う(ステップS704)。不測の電源断が生じた後に復旧した場合には、バックアップRAM領域のデータは保存されていたはずであるから、チェック結果は正常になる。チェック結果が正常でない場合には、内部状態を電源断時の状態に戻すことができないので、停電復旧時でない電源投入時に実行される初期化処理を実行する(ステップS705,S703)。

チェック結果が正常であれば、払出制御用CPU371は、内部状態を電源断時の状態に戻すための払出状態復旧処理を行う(ステップS706)。そして、バックアップRAM領域に保存されていたPC(プログラムカウンタ)の指すアドレスに復帰する(ステップS707)。

通常の初期化処理の実行(ステップS703)を終えると、払出制御用CPU371により実行されるメイン処理は、タイマ割込フラグの監視(ステップS708)の確認が行われるループ処理に移行する。

なお、この実施の形態では、ステップS702でバックアップデータの有無が確認された後、バックアップデータが存在する場合にステップS704でバックアップ領域のチェックが行われたが、逆に、バックアップ領域のチェック結果が正常であったことが確認された後に、バックアップデータの有無の確認が行われるようにしてもよい。また、バックアップデータの有無の確認、またはバックアップ領域のチェックの何れか一方を確認することによって、停電復旧処理を実行するか否かを判断するように構成してもよい。

また、例えば停電復旧処理を実行するか否か判断する場合のパリティチェック(ステップS704)の際などに、すなわち、遊技状態を復旧するか否か判断する際に、保存されていたRAMデータにおける払出遊技球数データ等によって、遊技機が払出待機状態(払出途中でない状態)であることが確認されたら、払出状態復旧処理を行わずに初期化処理を実行するようにしてもよい。

通常の初期化処理では、図23に示すように、レジスタおよびRAMのクリア処理(ステップS901)が行われ、所定の初期値の設定が行われる(ステップS902)。そして、初期化処理を終える前に割込が許可される(ステップS903)。

この実施の形態では、払出制御用CPU371の内蔵タイマ/カウンタが繰り返しタイマ割込を発生するように設定される。また、繰り返し周期は2msに設定される。そして、図24に示すように、タイマ割込が発生すると、払出制御用CPU371は、タイマ割込フラグをセットする(ステップS711)。なお、図24には割込を許可することも明示されているが(ステップS710)、2msタイマ割込処理では、最初に割込許可状態に設定される。すなわち、2msタイマ割込処理中には割込許可状態になっている。

払出制御用CPU371は、ステップS708において、タイマ割込フラグがセットされたことを検出すると、タイマ割込フラグをリセットするとともに(ステップS709)、払出制御処理を実行する(ステップS710)。以上の制御によって、この実施の形態では、払出制御処理は2ms毎に起動されることになる。なお、この実施の形態では、タイマ割込処理ではフラグセットのみがなされ、払出制御処理はメイン処理において実行されるが、タイマ割込処理で払出制御処理を実行してもよい。

払出制御用CPU371は、電源投入時に、バックアップRAM領域のデータを確認するだけで、通常の初期設定処理を行うのか払出中の状態を復元するのか決定できる。すなわち、簡単な判断によって、未払出の遊技球について払出処理再開を行うことができる。さらに、この実施の形態では、主基板31における遊技制御と同様に、パリティチェックコードによって記憶内容保存の確実化が図られている。

図25は、ステップS710の払出制御処理を示すフローチャートである。払出制御処理において、払出制御用CPU371は、まず、中継基板72を介して入力ポート372bに入力される賞球カウントスイッチ301A、球貸しカウントスイッチ301Bがオンしたか否かを判定する(スイッチ処理:ステップS751)。

次に、払出制御用CPU371は、センサ(例えば、払出モータ289の回転数を検出するモータ位置センサ)からの信号入力状態を確認してセンサの状態を判定する等の処理を行う(入力判定処理:ステップS752)。払出制御用CPU371は、さらに、受信した払出制御コマンドを解析し、解析結果に応じた処理を実行する(コマンド解析実行処理:ステップS753)。

次いで、払出制御用CPU371は、主基板31から払出停止指示コマンドを受信していたら払出停止状態に設定し、払出開始指示コマンドを受信していたら払出停止状態の解除を行う(ステップS754)。また、プリペイドカードユニット制御処理を行う(ステップS755)。

また、払出制御用CPU371は、球貸し要求に応じて貸し球を払い出す制御を行う(ステップS756)。さらに、払出制御用CPU371は、所定の賞球を払い出す賞球制御処理を行う(ステップS757)。そして、払出制御用CPU371は、出力ポート372cおよび中継基板72を介して球払出装置97の払出機構部分における払出モータ289に向けて駆動信号を出力し、ステップS756の球貸し制御処理またはステップS757の賞球制御処理で設定された回転数分払出モータ289を回転させる払出モータ制御処理を行う(ステップS758)。

なお、この実施の形態では、払出モータ289としてステッピングモータが用いられ、払出モータ289を制御するために1−2相励磁方式が用いられる。従って、具体的には、払出モータ制御処理において、8種類の励磁パターンデータが繰り返し払出モータ289に出力される。また、この実施の形態では、各励磁パターンデータが4msずつ出力される。

次いで、エラー検出処理が行われ、その結果に応じてエラー表示LED374に所定の表示を行う(エラー処理:ステップS759)。

さらに、ターミナル基板160に情報信号を出力する処理を行う(出力処理:ステップS760)。なお、情報信号は、貸し球の払出一単位(例えば25個)ごとに所定時間オンとなり、続いて所定時間オフを出力する信号である。

図26は、電源基板910の電源監視用IC902からの電源断信号にもとづくNMIに応じて実行される停電発生NMI処理の一例を示すフローチャートである。停電発生NMI処理において、払出制御用CPU371は、まず、割込禁止フラグの内容をパリティフラグに格納する(ステップS801)。次いで、割込禁止に設定する(ステップS802)。

停電発生NMI処理では、主基板31において実行された処理と同様に、RAM内容の保存を確実にするためのチェックサムの生成処理を行う。その処理中に他の割込処理が行われたのではチェックサムの生成処理が完了しないうちに払出制御用CPU371が動作し得ない電圧にまで低下してしまうことがことも考えられるので、まず、他の割込が生じないような設定がなされる。なお、停電発生NMI処理におけるステップS804〜S810は、電力供給停止準備処理の一例である。

なお、割込処理中では他の割込がかからないような仕様のCPUを用いている場合には、ステップS802の処理は不要である。

次いで、払出制御用CPU371は、バックアップフラグが既にセットされているか否か確認する(ステップS803)。バックアップフラグが既にセットされていれば、以後の処理を行わない。バックアップフラグがセットされていなければ、以下の電力供給停止準備処理を実行する。すなわち、ステップS804からステップS810の処理を実行する。

まず、各レジスタの内容をバックアップRAM領域に格納する(ステップS804)。その後、バックアップフラグをセットする(ステップS805)。そして、バックアップRAM領域のバックアップチェックデータ領域に適当な初期値を設定し(ステップS806)、初期値およびバックアップRAM領域のデータについて順次排他的論理和をとったあと反転し(ステップS807)、最終的な演算値をバックアップパリティデータ領域に設定する(ステップS808)。また、RAMアクセス禁止状態にする(ステップS809)。電源電圧が低下していくときには、各種信号線のレベルが不安定になってRAM内容が化ける可能性があるが、このようにRAMアクセス禁止状態にしておけば、バックアップRAM内のデータが化けることはない。

さらに、払出制御用CPU371は、全ての出力ポートに対してクリア信号を出力する。従って、全ての出力ポートは、クリア信号によりオフ状態とされる(ステップS810)。

次いで、払出制御用CPU371は、ループ処理にはいる。すなわち、何らの処理もしない状態になる。従って、リセット管理回路940からのリセット信号がローレベルになって動作禁止状態にされる前に、内部的に動作停止状態になる。よって、電源断時に確実に払出制御用CPU371は動作停止する。その結果、上述したRAMアクセス禁止の制御および動作停止制御によって、電源電圧が低下していくことに伴って生ずる可能性がある異常動作に起因するRAMの内容破壊等を確実に防止することができる。

なお、この実施の形態では、停電発生NMI処理では最終部でプログラムをループ状態にしたが、ホールト(HALT)命令を発行するように構成してもよい。

また、レジスタの内容をRAM領域に格納した後にセットされるバックアップフラグは、上述したように、電源投入時において復旧すべきバックアップデータがあるか否か(停電からの復旧か否か)を判断する際に使用される。また、ステップS801からS810の処理は、払出制御用CPU371が電源基板910からのリセット信号がローレベルになる前に完了する。換言すれば、電源基板910からのリセット信号がリセット状態を示すようになる前に完了するように、電源基板910の電圧監視用IC902において検出電圧の設定が行われている。

この実施の形態では、電力供給停止準備処理開始時に、バックアップフラグの確認が行われる。そして、バックアップフラグが既にセットされている場合には電力供給停止準備処理を実行しない。上述したように、バックアップフラグは、必要なデータのバックアップが完了し、その後電力供給停止準備処理が完了したことを示すフラグである。従って、例えば、リセット待ちのループ状態で何らかの原因で再度NMIが発生したとしても、電力供給停止準備処理が重複して実行されてしまうようなことはない。

ただし、割込処理中では他の割込がかからないような仕様のCPUを用いている場合には、ステップS803の判断は不要である。

また、この実施の形態では、払出制御用CPU371は、マスク不能外部割込端子(NMI端子)を介して電源基板からのNMI割込信号(電源監視手段からのNMI割込信号)を検知したが、NMI割込信号をマスク可能割込割込端子(IRQ端子)に導入してもよい。その場合には、IRQ処理によって図26に示された停電発生NMI処理が実行される。また、入力ポートを介してNMI割込信号を検知してもよい。その場合には、払出制御用CPU371が実行するメイン処理において、入力ポートの監視が行われる。

図27は、バックアップパリティデータ作成方法の一例を説明するための説明図である。ただし、図27に示す例では、簡単のために、バックアップデータRAM領域のデータのサイズを3バイトとする。電源電圧低下にもとづく停電発生処理において、図27に示すように、バックアップチェックデータ領域に、初期データ(この例では00H)が設定される。次に、「00H」と「F0H」の排他的論理和がとられ、その結果と「16H」の排他的論理和がとられる。さらに、その結果と「DFH」の排他的論理和がとられる。そして、その結果(この例では「39H」)を反転して得られた値(この例では「C6H」)がバックアップパリティデータ領域に設定される。

電源が再投入されたときには、停電復旧処理においてパリティ診断が行われる。バックアップ領域の全データがそのまま保存されていれば、電源再投入時に、図27に示すようなデータがバックアップ領域に設定されている。

ステップS704の処理において、払出制御用CPU371は、図26のステップS806およびステップS807にて実行された処理と同様の処理を行う。すなわち、バックアップチェックデータ領域に、初期データ(この例では00H)が設定され、「00H」と「F0H」の排他的論理和がとられ、その結果と「16H」の排他的論理和がとられる。さらに、その結果と「DFH」の排他的論理和がとられる。そして、その結果(この例では「39H」)を反転した最終演算結果を得る。バックアップ領域の全データがそのまま保存されていれば、最終的な演算結果は、「C6H」、すなわちバックアップチェックデータ領域に設定されているデータと一致する。バックアップRAM領域内のデータにビット誤りが生じていた場合には、最終的な演算結果は「C6H」にならない。

よって、払出制御用CPU371は、最終的な演算結果とバックアップチェックデータ領域に設定されているデータとを比較して、一致すればパリティ診断正常とする。一致しなければ、パリティ診断異常とする。

以下、払出状態復旧処理について説明する。図28は、図22のステップS706に示された払出状態復旧処理の一例を示すフローチャートである。この例では、払出制御用CPU371は、バックアップRAMに保存されていた値をレジスタに復元する(ステップS861)。そして、バックアップRAMに保存されていたデータにもとづいて停電時の払出状態を復旧するための処理を行う。例えば、賞球中処理中フラグのセット等を行う。

例えば、電源復旧時に、バックアップRAM領域に、未払出賞球数もしくは未払出貸し球数、またはそれらの両方が保存されていた場合には、それらの保存数にもとづいて払出処理を再開する。

以上のように、この実施の形態では、払出制御手段には、遊技機の電源が断しても、所定期間電源バックアップされる記憶手段(この例ではバックアップRAM)が設けられ、電源投入時に、払出制御用CPU371(具体的には払出制御用CPU371が実行するプログラム)は、記憶手段がバックアップ状態にあればバックアップデータにもとづいて払出状態を回復させる払出状態復旧処理(ステップS706)を行うように構成される。

図11に例示した電源基板910の構成において、電源監視用IC902が出力する信号は、バッファ回路918を介して主基板31に対して電源断信号として出力されるとともに、遅延回路920およびバッファ回路919を介して払出制御基板37に対して電源断信号として出力されていた。すると、図29に示すように、遊技機の電源が断する際に、主基板31のCPU56には、払出制御基板37の払出制御用CPU371に対するよりも早く電源断信号が供給される。

従って、図29に示すように、主基板31のCPU56には、払出制御基板37の払出制御用CPU371よりも早くNMIがかかる。NMIに応じて電力供給停止準備処理が開始されるので、その時点で、CPU56による遊技制御および払出制御用CPU371による払出制御は停止する。

すなわち、電源基板910に搭載されている立下管理手段が、遊技制御手段を立ち下げた後に払出制御手段(価値付与制御手段)を立ち下げるという順序制御を行っている。従って、主基板31のCPU56が他の電気部品制御基板に対して制御コマンドを出力する前に、払出制御手段におけるCPUが既に立ち下がっていることはなく、主基板31からの制御コマンドが受信側の電気部品制御基板のCPUで受信されないという事態は生じない。なお、この実施の形態では、立下管理手段は、電源監視用IC902、制御手段の作動を停止させるためのリセット信号を出力可能なリセット管理回路940および遅延回路920で実現されている。

ここでは、立下管理手段が、主基板31に与えられる電源断信号と払出制御手段に送られる電源断信号とのタイミングをずらせることによって、それらの間の立ち下げの順序制御を行ったが、他の複数の電気部品制御基板、例えば表示制御基板70、ランプ制御基板35および音声制御基板80等の遊技演出に関わる電気部品制御手段を搭載した電気部品制御基板の立ち下げタイミングを制御することもできる。例えば、図12に示した回路構成において、主基板31および払出制御基板371以外の電気部品制御基板に対してもバッファ回路を介して電源断信号を出力するようにすればよい。

そして、それぞれのバッファ回路の前に遅延回路を置き、各遅延回路の遅延量に差を設ければ、主基板31および他の電気部品制御基板に与えられる電源断信号出力タイミングのそれぞれの間で差を付けることができる。表示制御基板70、ランプ制御基板35および音声制御基板80等における各CPUも電源断信号に応じて演出制御を停止するようにすれば、各電気部品制御手段を、あらかじめ定められた順序で立ち下げることができるようになる。

さらに、この実施の形態のように、電源基板910における立下管理手段が一括して各基板における制御手段の立ち下げを管理することによって、立ち下げの順序制御を容易に調整することができる。例えば、それぞれの遅延回路の遅延量を調整することによって容易に立ち下げ順序を制御することができる。

なお、この実施の形態では、立下管理手段が電源基板910に搭載されたが、立下管理手段を搭載した立下管理手段を別個に設けてもよい。ただし、一般に立ち下げのための信号は電源電圧の立ち下がりを利用して作成されるので、電源基板910に立下管理手段を搭載した場合には、各電気部品制御手段の立ち下げ管理をより容易に行えるというメリットがある。

上記の実施の形態では、立上管理手段は、各電気部品制御手段へのリセット信号の遅延量を調整することによって立ち上げの順序管理を行ったが、リセット信号ではなく電源電圧の供給開始タイミングを調整することによって立ち上げの順序管理を行うこともできる。

図30は、電源電圧の供給開始タイミングを調整する立上管理手段が搭載された電源基板910の構成例を示すブロック図である。図30に示す実施の形態では、主基板31に対する+30V、+12V、+5Vおよびバックアップ電源電圧の供給開始が遅延される。すなわち、遅延回路971はバックアップ電源電圧の立ち上がりを遅延させ、遅延回路972は+5Vの立ち上がりを遅延させる。また、遅延回路973は+12Vの立ち上がりを遅延させ、遅延回路974は+30Vの立ち上がりを遅延させる。遅延回路971,972,973,974は例えばコンデンサで実現できる。

なお、図30では、1つのコネクタ915が示されているが、各電気部品制御基板対応にコネクタが設けられていてもよい。その場合には、例えば、主基板31への各種電圧を供給するためのコネクタ、ランプ制御基板35への各種電圧を供給するためのコネクタ、払出制御基板37への各種電圧を供給するためのコネクタ、表示制御基板70への各種電圧を供給するためのコネクタ、音声制御基板80への各種電圧を供給するためのコネクタ、および発射制御基板91への各種電圧を供給するためのコネクタが別個に設けられる。

また、図30に示す電源基板910では、主基板31に供給される各電圧の立ち上がりのみを遅延させているので、主基板31の遊技制御手段の立ち上がりのみが、他の電気部品制御手段の立ち上がりよりも遅れる。しかし、他のそれぞれの電気部品制御手段の立ち上がりに順序をつけることもできる。例えば、ランプ制御基板35、払出制御基板37、表示制御基板70および音声制御基板80のそれぞれに供給される各種電圧も遅延回路を介して供給し、それぞれの遅延回路の遅延量に差を設ければ、遊技制御手段、ランプ制御手段、払出制御手段、表示制御手段および音声制御手段の間で、立ち上がりタイミングに順序付けすることもできる。

さらに、電気部品制御基板で用いられる全ての種類の電圧を遅延対象とするのではなく、CPUが使用する電源電圧のみを遅延対象としてもよい。

図31は、図30に示す電源基板910を用いた場合の各基板に供給される直流電圧等を示すブロック図である。図30に示すように、主基板31に至る各種電圧が遅延回路で遅延された後に、主基板31に供給される。

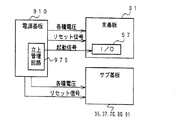

図32は、立上管理手段のさらに他の実施の形態を示すブロック図である。図32に示す構成では、起動信号を出力する立上管理回路975が電源基板910に搭載されている。主基板31とサブ基板(ランプ制御基板35、払出制御基板37、表示制御基板70および音声制御基板80)には、電源基板910から、遅延されることなく各種電圧およびリセット信号が供給される。

図33に例示するように、この実施の形態で用いられる主基板31のCPU56は、リセット信号がリセット解除状態を示すと、まず、セキュリティチェックプログラムを実行し、その後初期化処理を実行する。また、サブ基板35,37,70,80のCPUは、リセット信号がリセット解除状態を示すと、初期化処理を実行した後に遊技演出に関わる制御を行う状態である制御状態に入る。そして、立上管理回路975は、CPU56のセキュリティチェックプログラムの実行が確実に完了するタイミングで起動信号を出力する。起動信号は、主基板31の入出力ポート57に入力される。

主基板31のCPU56は、入出力ポート57を介して起動信号を受けたことを確認したら遊技制御状態に入る。従って、遊技制御手段が遊技制御状態に入ったときには、サブ基板35,37,70,80のCPUは既に制御状態になっている。よって、例えば、主基板31から送出された制御コマンドは、サブ基板35,37,70,80のCPUにおいて確実に受信される。

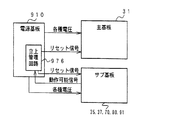

図34は、立上管理手段のさらに他の実施の形態を示すブロック図である。図34に示す構成では、主基板31に対するリセット信号の立ち上げタイミングを調整する立上管理回路976が電源基板910に搭載されている。主基板31とサブ基板(ランプ制御基板35、払出制御基板37、表示制御基板70および音声制御基板80)には、電源基板910から、遅延されることなく各種電圧およびリセット信号が供給される。

図35に示すように、サブ基板35,37,70,80のCPUは、リセット信号がリセット解除状態を示すと、初期化処理を実行した後に、動作可能信号を出力する。立上管理回路976は、動作可能信号を受信すると、主基板31に対するリセット信号を立ち上げる。リセット信号が立ち上がったことに応じて、主基板31CPU56は、初期化処理を行った後に遊技制御状態に入る。従って、遊技制御手段が遊技制御状態に入ったときには、サブ基板35,37,70,80のCPUは既に制御状態になっている。よって、例えば、主基板31から送出された制御コマンドは、サブ基板35,37,70,80のCPUにおいて確実に受信される。

なお、図34に示す構成において、立上管理回路976は、動作可能信号を受信すると、主基板31に対して起動信号を出力するようにしてもよい。そのように構成されている場合には、主基板31に対するリセット信号は、サブ基板35,37,70,80に対するリセット信号と同様のタイミングでリセット解除状態になる。そして、主基板31では、電源基板910からの起動信号が入出力ポート57に入力され、CPU56は、起動信号を受信したら遊技制御状態に入る。

また、上記の各実施の形態では、立下管理手段は、各電気部品制御手段への電源断信号の遅延量を調整することによって立ち下げの順序管理を行ったが、他の方法によっても各電気部品制御手段の立ち下げ管理を行うことができる。

図36は、立下管理手段の他の実施の形態を示すブロック図である。図36に示す構成では、立下管理手段は、サブ基板35,37,70,80に対するリセット信号を遅延する遅延回路960で実現される。なお、立上管理回路968は、サブ基板35,37,70,80からの動作可能信号に応じて、主基板31に対して起動信号を出力する。また、この実施の形態では、主基板31およびサブ基板35,37,70,80のCPUは、リセット信号がローレベルになったことによって制御動作を停止する。

図37に示すように、主基板31に対するリセット信号は、サブ基板35,37,70,80に対するリセット信号よりも早く立ち上がる。しかし、主基板31のCPU56は、起動信号を受けたことに応じて初めて遊技状態に入る。起動信号は、サブ基板35,37,70,80の各CPUが制御状態に入って動作可能信号を出力すると動作可能状態を示すので、主基板31のCPU56が遊技制御状態に入ったとき、すなわち立ち上がったときには、サブ基板35,37,70,80の各CPUは既に制御状態に入っている。すなわち、既に立ち上がっている。

そして、遊技機への電源供給が断してVSLが所定値以下になると、リセットIC651の出力がローレベルになる。リセットIC651の出力は、そのまま主基板31に供給されているが、サブ基板35,37,70,80には遅延回路960を介して供給されている。従って、図37に示すように、主基板31のCPU56は、サブ基板35,37,70,80の各CPUよりも早く立ち下がる。

よって、例えば、電源断直前に遊技制御手段が他の電気部品制御手段に対して制御コマンドを送出しているような場合でも、その制御コマンドは、受信側の電気部品制御手段において確実に受信される。

なお、図36に示す構成では、1つの遅延回路960の出力が各サブ基板35,37,70,80に供給されているので、各サブ基板35,37,70,80のCPUは同時に立ち下がることになるが、バッファ回路961〜964の前段にそれぞれ遅延回路を置き、各遅延回路の遅延量に差を設ければ、主基板31および各サブ基板35,37,70,80の立ち下げ順序を任意に設定することができる。

また、図36に示す構成では、リセットIC651の出力がそのまま遅延回路960およびバッファ回路965に出力されるので、電源投入時に1回のリセット解除動作(ローレベルからハイレベルへの変化)が行われることになるが、図12に示されたようなIC941〜949を設け、2回のリセット解除動作が行われるように構成してもよい。

図38は、立下管理手段の他の実施の形態を示すブロック図である。図38に示す構成では、立下管理回路977は、電源監視用IC902の出力がハイレベルからローレベルに変化すると、スイッチ回路978を介して、主基板31に供給される各種電圧を直ちに遮断する。各サブ基板35,37,70,80に至る各種電源については特に制御を行わない。よって、各サブ基板35,37,70,80に供給される電圧はしばらくの間、各サブ基板35,37,70,80が動作可能な電位を維持するが、主基板31に供給される電圧は直ちに遮断される。その結果、主基板31は、各サブ基板35,37,70,80よりも早く立ち下がることになる。

図39は、立上管理手段の他の実施の形態を示すブロック図である。図38に示す構成では、立上管理手段であるリセット管理回路940において、リセットIC931,932が設けられている。リセットIC931,932として、図11等に示された電源監視用ICと同じICを用いることができる。リセットIC931は、+30V電源電圧(VSL)が+9V以上になると出力をハイレベルにし、+9Vを下回ると出力をローレベルにする。リセットIC931の出力は、各サブ基板に搭載されたCPUに対してシステムリセット信号として供給される。

リセットIC932は、+30V電源電圧(VSL)が+7V以上になると出力をハイレベルにし、+7Vを下回ると出力をローレベルにする。リセットIC931の出力は、主基板31に搭載されたCPU56に対してシステムリセット信号として供給される。リセットIC931,932において、それぞれのVs 端子に、+30V電源電圧が抵抗で分圧された電圧が入力されている。そして、リセットIC931,932が、+30V電源電圧(VSL)と+7Vまたは+9Vとを比較できるように各抵抗の抵抗値が選定されている。

図39に示すように、異なる電圧を監視してリセット信号を出力する2つのリセットIC931,932を設けた構成によっても、主基板31のCPU56に対するリセット解除のタイミングを、サブ基板のCPUに対するリセット解除のタイミングよりも遅くすることができる。

なお、リセットIC931,932の出力がハイレベルに立ち上げるときには、立ち上がりタイミングが、コンデンサC1,C2の容量で定まる時間だけ遅延される。

従って、図40に示すように、遊技機に電源投入がなされ、VSLが+7Vにまで立ち上がると、その時点からコンデンサC1の容量で定まる時間だけ遅延してリセットIC931の出力がハイレベルに立ち上がる。また、VSLが+9Vにまで立ち上がると、その時点からコンデンサC2の容量で定まる時間だけ遅延してリセットIC932の出力がハイレベルに立ち上がる。各サブ基板におけるCPUは、リセットIC931の出力がハイレベルに立ち上がるとリセット解除されて動作を開始するのであるが、各CPUの初期化処理時間の相違等に起因して、本来の制御を開始するタイミングがばらつくことがある。

そこで、この実施の形態では、コンデンサC2の容量をコンデンサC1の容量よりも大きくして、リセットIC932の出力がハイレベルに立ち上がるタイミングをより遅くする。そのように構成すれば、各サブ基板におけるCPUの制御開始タイミングがばらついても、主基板31のCPU56が動作開始したときに全てのサブ基板におけるCPUが必ず制御を開始しているようにすることができる。また、電源断時には、主基板31へのリセット信号は+9Vレベルで立ち下がり、VSLの+7Vまでの低下を検出した時点で各サブ基板が立ち下がるので、主基板31を先に立ち下げることができる。

なお、図39に示された構成では、電源投入時に1回だけリセット信号が立ち上がるが、図12に示されたように、電源投入時にリセット信号において2回の立ち上がりが発生するように構成してもよい。

上記の各実施の形態では、複数の電気部品制御基板を備えた構成において、立上管理手段が各電気部品制御基板の立ち上げ順序を制御することが可能になっている。従って、払出制御基板37を主基板31よりも早く立ち上げたり、表示制御基板70,ランプ制御基板35および音声制御基板80等の遊技演出に関わる制御手段を搭載した電気部品制御基板(演出制御用基板)を主基板31よりも早く立ち上げるように制御することが容易である。

また、立下管理手段が各電気部品制御基板の立ち下げ順序を制御することが可能になっている。よって、払出制御基板37を主基板31よりも遅く立ち下げたり、表示制御基板70、ランプ制御基板35および音声制御基板80等の遊技演出に関わる制御手段を搭載した演出制御用基板を主基板31よりも遅く立ち下げるように制御することが容易である。

ところで、主基板31におけるCPU56および払出制御基板37における払出制御用CPU371は、電力供給停止時に、電源基板910からの電源断信号に応じて電力供給停止準備処理を行い、その後、ループする動作を行う(図20および図26参照)。電力供給停止時には、さらにその後にシステムリセット信号がローレベルになってCPUはリセット状態になる。

しかし、極めて短い電源の瞬断が発生した場合には、システムリセット信号がローレベルにならない可能性がある。上記の各実施の形態では、電源断信号は+30V電源電圧が+22Vを下回ると発生し、システムリセット信号は+30V電源電圧が+9Vを下回るとシステムリセット信号がローレベルになるので、+30V電源電圧が+22Vよりも低下するが+9Vにまで低下しないうちに復旧するような電源瞬断が発生した場合には、電源断信号が発生するので電力供給停止準備処理が実行開始されるが、システムリセット信号はローレベルにならない。そのような場合には、CPUは、電力供給停止準備処理におけるループ処理から抜けることができない。

図41は、極めて短い電源の瞬断が発生した場合でも電力供給停止準備処理におけるループ処理から抜け出せないような事態を回避しうる電源基板の一構成例を示すブロック図である。図41に示す構成では、電源監視用IC903が搭載されている。電源監視用IC903は、+30V電源電圧(VSL)が20Vを下回ると出力(RESET端子の出力)をローレベルにする。なお、図41では、電源監視用IC902,903において、それぞれのVs 端子に、+30V電源電圧が抵抗で分圧された電圧が入力されている。そして、電源監視用IC902,903が、+30V電源電圧(VSL)と+22Vまたは+20Vとを比較できるように各抵抗の抵抗値が選定されている。また、IC918の出力は、電源断信号として主基板31および払出制御基板37に供給される。

電源監視用IC902の出力はラッチ回路981でラッチされ、ラッチ回路981の出力は、双方の入力がともにローレベルになるとローレベルを出力する論理回路(等価的にOR回路であるから、以下、OR回路と呼ぶ。)982の一方の入力端子に入力される。また、電源監視用IC903の出力は、いずれかの入力がローレベルになるとローレベルを出力する論理回路(等価的にAND回路であるから、以下、AND回路と呼ぶ。)の他方の入力端子に入力される。そして、OR回路982の出力とリセット管理回路940の出力とがAND回路983に入力され、AND回路983の出力はリセット信号として各基板に供給される。

なお、図41には、説明を簡単にするために、主基板31および払出制御基板37に同一の電源断信号が供給される構成が示されているが、既に説明したように、主基板31と払出制御基板37とのそれぞれに対応した電源断信号を作成し、払出制御基板37への電源断信号を遅延させてもよい。また、リセット管理回路940は既に説明した実施の形態の場合と同様に、各基板へのリセット信号をそれぞれ作成し、主基板31へのリセット信号を遅延させてもよい。

図42(A)は、電源監視用IC903等が設けられていない場合の電源断信号とシステムリセット信号との関係の一例を示す説明図である。図42(A)に示された例では、+30V電源電圧(VSL)は、+22Vを下回ったものの、+9Vにまで低下する前に復旧している。従って、電源断信号(ローアクティブ)は出力されるが、リセット信号はハイレベルのままである。このような場合には、CPUは、電力供給停止準備処理におけるループ処理から抜け出せない。

しかし、図41に示された構成によれば、図42(B)に示すように、+30V電源電圧(VSL)が+22Vを下回ると、ラッチ回路981においてローレベルがラッチされ、+30V電源電圧(VSL)が+20Vを下回ると電源監視用IC903の出力がローレベルになるので、OR回路982の出力がローレベルになる。その結果、AND回路983の出力がローレベルになる。すなわち、システムリセット信号がローレベルになる。よって、CPUがシステムリセットされ、ループ処理から抜け出すことができる。

図43は、電源基板910の他の構成例を示すブロック図である。図43に示す構成では、電源監視用IC902の出力が遅延回路984を介してAND回路983の一方の入力端子に入力される。また、AND回路983の他方の入力端子には、リセット管理回路940の出力が入力される。

図43に示された構成によれば、図44に示すように、+30V電源電圧(VSL)が+22Vを下回ると、電源監視用IC902の出力(電源断信号)がローレベルになる。その信号は、遅延回路986で遅延されてAND回路983に入力されるので、主基板31や払出制御基板37に供給されるシステムリセット信号がローレベルになる。よって、CPUがシステムリセットされ、ループ処理から抜け出すことができる。なお、遅延回路984における遅延量は、主基板31のCPU56や払出制御基板37の払出制御用CPU371が電力供給停止準備処理を完了するのに十分な時間に設定される。

なお、図43には、説明を簡単にするために、主基板31および払出制御基板37に同一の電源断信号が供給される構成が示されているが、既に説明したように、主基板31と払出制御基板37とのそれぞれに対応した電源断信号を作成し、払出制御基板37への電源断信号を遅延させてもよい。また、リセット管理回路940は既に説明した実施の形態の場合と同様に、各基板へのリセット信号をそれぞれ作成し、主基板31へのリセット信号を遅延させてもよい。