JP3908764B2 - 位相比較利得検出回路、誤同期検出回路及びpll回路 - Google Patents

位相比較利得検出回路、誤同期検出回路及びpll回路 Download PDFInfo

- Publication number

- JP3908764B2 JP3908764B2 JP2004547995A JP2004547995A JP3908764B2 JP 3908764 B2 JP3908764 B2 JP 3908764B2 JP 2004547995 A JP2004547995 A JP 2004547995A JP 2004547995 A JP2004547995 A JP 2004547995A JP 3908764 B2 JP3908764 B2 JP 3908764B2

- Authority

- JP

- Japan

- Prior art keywords

- phase

- phase comparison

- data

- signal

- identification

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000001514 detection method Methods 0.000 title claims description 118

- 238000010586 diagram Methods 0.000 description 24

- 230000003111 delayed effect Effects 0.000 description 14

- 230000001360 synchronised effect Effects 0.000 description 9

- 238000003708 edge detection Methods 0.000 description 6

- 238000009499 grossing Methods 0.000 description 5

- 238000012546 transfer Methods 0.000 description 5

- 230000010355 oscillation Effects 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 3

- 230000000630 rising effect Effects 0.000 description 3

- 230000007423 decrease Effects 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- 238000000034 method Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012935 Averaging Methods 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/091—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector using a sampling device

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/093—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal using special filtering or amplification characteristics in the loop

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/02—Speed or phase control by the received code signals, the signals containing no special synchronisation information

- H04L7/033—Speed or phase control by the received code signals, the signals containing no special synchronisation information using the transitions of the received signal to control the phase of the synchronising-signal-generating means, e.g. using a phase-locked loop

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

- Manipulation Of Pulses (AREA)

Description

ここで位相比較器10における位相比較利得をKp、チャージポンプ20における電流振幅をIc、ループフィルタ30の伝達関数をF(s)、VCOの利得をKvとした場合、当該PLL回路のループ利得は周知の以下の式にて表される。

開ループ利得=[Kp・Ic・F(s)・Kv]/s

閉ループ利得=φin/φout

=[Kp・Ic・F(s)・Kv]/[s+Kp・Ic・F(s)・Kv]

又、ループフィルタとして、完全次形のものを使用した場合、

開ループ利得=[Kp・Ic・R・Kv/s]・[1+1/sCR]

閉ループ利得=[Kp・Ic・R・Kv・(1+sCR)]/[s^2・CR+Kp・Ic・R・Kv・(1+sCR)]

の各ループ利得が得られる。

上式から閉ループ利得のカットオフ周波数は開ループ利得が0dBになる周波数であり、位相比較器10、チャージポンプ20、VCO40の夫々の利得に比例することが分かる(図2A参照)。ここで、各部の利得が大きい場合このカットオフ周波数は高くなり、その結果出力ジッタが増加する傾向にある。他方これらの利得が小さい場合には(図2B参照)、カットオフ周波数が低くなり、その結果位相余裕が減少してピーキングが増加する傾向にある。又その場合、位相誤差応答が悪くなる傾向にある。

ここでPLLのジッタ特性としての閉ループ特性は所謂ジッタトランスファに相当するものであり、PLLがロックした状態における入力ジッタに対する出力ジッタの増幅率で表される。この値はPLLの応答速度が遅いほど良い。他方、PLLがロックした状態でどの位のジッタに耐えられるかの指標である所謂ジッタトレランスの見地から考えた場合、逆にPLLの応答速度が速いほど耐力が大きい。従って両者は互いにトレードオフの関係にある。

図3は、PLL方式を適用した識別タイミング信号抽出回路の一例を示すブロック図である。上記の如くのPLL回路機能によって抽出されたクロック信号CLによって、識別回路100にて入力データ信号DAのデータが抽出される。

このような光送受信回路等におけるPLL回路では、一般の周波数シンセサイザで使用されるPLL回路とは異なり、入力データ信号としてランダムなデータが入力される。従って、入力信号の周波数の変動が大きい場合、抽出すべき周波数成分値のレベルが相対的に低下し、結果的に上記PLLループ利得が低下してその動作が不安定になる。

図4は上記位相比較回路10として、周知のハーフレートクロックBang−Bang回路を適用した場合の回路例を示す。同図中、入力データ信号DAに対し、二つのD−FF(D−フリップフロップ)回路にて、夫々データ識別用クロック信号CLと、これをπ/2位相分遅らせたエッジ検出用クロック信号CL’とによってデータ識別動作を行う。そしてその結果得られる夫々の信号Da,Dbに対して排他的論理和回路ExORにて排他的論理和演算を行い、信号Dcを得る。

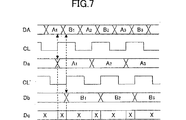

その結果、データ信号DAの位相が識別クロック信号CLの位相に対して遅れていた場合、確率的に、図6に示す如く、排他的論路和出力Dcは間欠的な信号となり、他方、データ信号DAの位相が識別クロック信号CLの位相に対して進んでいた場合、図7に示す如く、排他的論路和出力Dcは連続的な信号となる可能性が高い。

その結果、このような位相比較結果に対してチャージポンプ20とループフィルタ30とによる低域通過フィルタを通して得られた信号のレベルは、図6のように位相比較出力が間欠的な信号の場合低く、他方図7の場合のように連続的となる可能性が高い位相比較出力の場合、上記低域通過フィルタの出力レベルは高くなる。そしてこの低域通過フィルタの出力レベルに応じてVCO40の発振周波数が制御される。

即ち、データ信号の位相が遅れている場合にはVOC入力レベルが下がり、その結果VCO発振周波数が低下してデータ信号の位相に応じてクロック信号CLの位相を遅らせるよう作用する。逆にデータ信号の位相が進んでいる場合にはVCO発振周波数が上昇し、データ信号に対してクロック信号の位相を進ませるよう作用する。

ここで図6の場合において入力データ信号の内のA系統のデータの符号が変化すると位相比較出力においてクロック信号の1/4周期のH信号が出力される。他方A系統のデータの符号が連続した場合、その間、H信号が出力されないこととなる。この様子を図8乃至図10に示す。

又、図7の場合、即ちデータ信号の位相が進んでいる場合、図7に示す如く同じデータ間の排他的論理和が発生することが無いため、統計的には位相比較出力としてH信号とL信号とは半分ずつ発生することとなる。しかしながら、A系統とB系統共、同符号が連続するような場合にはL信号が出力され、他方異符号の繰り返しが続くとH信号が出力される事となる。この様子を図11乃至図13に示す。

このように、位相比較出力は必ずしもデータ信号とクロック信号との間の位相差のみでなく、データ信号の内容そのもの(この場合所謂エッジ率、デューティー等)によっても影響を受けることとなる。その結果、上記位相比較器10の利得Kpが変動し、もって上記PLL回路全体のループ利得が変動することとなる。

図14A,図14Bは、図4に示す如くの構成を有する位相比較器10の出力波形の例を示す。図14Aに示す如く、破線で示す理想的な出力特性に対し、入力ジッタ、位相比較回路中のD−FF回路のセットアップホールド動作特性による影響等により、実際には実線で示される如く波形になまりが生ずる。又、図14Bに示す如く、上記入力データのエッジ率によっても波形になまりが生ずる。その結果PLL回路のループ利得が変動し、もって上述の如くの回路動作不安定要因となる。

本発明では、入力データ信号の識別に関して位相条件が異ならせて複数の位相比較動作を行い、夫々の位相比較結果を比較することによって位相比較利得を検出する。従って入力データ信号のエッジ率、デューティー、更に識別器のセットアップ・ホールド特性等の位相比較利得の変動要因を加味したオンタイムの位相比較利得を検出出来る。その結果、当該位相比較検出結果に基づいてPLL回路のループ利得を制御することによってオンタイムで正確なループ利得補償制御が実現可能である。

図2A、2Bは、PLL回路のループ利得についての説明図である。

図3は従来のPLL回路の動作説明図である。

図4は、従来のハーフレートクロックBang−Bang位相比較器の回路例を示す図である。

図5はデータ識別位相について説明するための図である。

図6は図4の回路における各信号のタイムチャート(その1)である。

図7は図4の回路における各信号のタイムチャート(その2)である。

図8は図4の回路における各信号のタイムチャート(その3)である。

図9は図4の回路における各信号のタイムチャート(その4)である。

図10は図4の回路における各信号のタイムチャート(その5)である。

図11は図4の回路における各信号のタイムチャート(その6)である。

図12は図4の回路における各信号のタイムチャート(その7)である。

図13は図4の回路における各信号のタイムチャート(その8)である。

図14A,14Bは、位相比較特性の劣化状態を説明するための図(その1)である。

図15は、位相比較利得補償機能付きPLL回路の一例の回路ブロック図である。

図16は、位相比較利得検出回路の一例を示す回路図である。

図17は、位相比較特性の劣化状態を説明するための図(その2)である。

図18は、本発明の一実施例のブロック図である。

図19は、図18に示す構成による位相比較利得検出原理を説明するための図である。

図20は、本発明の一実施例の回路図である。

図21は、図20に示す回路における各信号のタイムチャートである。

図22は、図20に示す構成による位相比較利得検出原理を説明するための図である。

図23は、図20に示す構成を有する位相比較検出回路を用いた本発明の一実施例によるPLL回路のブロック図である。

図24は、本発明の他の実施例による位相比較利得検出回路の回路図である。

図25は、図24に示す構成による位相比較利得検出原理を説明するための図である。

図26は、本発明の更に他の実施例による誤同期検出回路の回路図である。

図27は、図26に示す構成による誤同期検出原理を説明するための図である。

好ましい実施例の説明

以下に本発明の実施例の構成について図面と共に説明する。

上述の如くのPLL回路(例えば図15に示す回路)の利得変化を、VCO40の利得を検出して補償するものとして、位相比較器10の利得をデータDAのエッジ率によって検出し、その検出結果に基づいてチャージポンプ20の出力電流を調整し、或いはフィルタ30の容量値又は抵抗値を調整して補償する等の方法が考えられる。図15の場合、位相比較利得回路210にて位相比較記10の利得を検出し、その検出結果に基づいて制御回路220にてチャージポンプの特性を制御する。

この場合、位相比較記10が例えば図16に示す如くの周知のHogge位相比較器のように鋸波位相比較特性(図17参照)を持つ位相比較器の場合、位相周期が決まった値であり、その出力振幅で利得が決まる。そして図15に示す如くの位相比較利得補償回路においては、データのエッジ率変動による振幅の変動を検出する。即ちこの場合、EXOR回路213の出力は、データにエッジが有る場合、即ちデータの変化時に”H”、無い場合には”L”となる。これをLPF(R,Cによる回路)で平均化することによりデータのエッジ率が検出出来る。そして制御回路220によって位相検出器の出力振幅の変動分をチャージポンプ20の電流を調整することで補償する方法である。

他方、識別器および分周器を位相比較器の一部として構成可能であるため構成部品が少なくてすむ周知のBnag−Bang位相比較器を適用する場合、この位相比較器では位相比較特性がステップ関数(Bang−Bang位相比較特性)で表され(例えば図14Aの破線の特性)、位相比較器出力の確率的変動に応じて位相比較利得値が決まる特性を有する。この場合の位相比較利得の変動要因としては、データのエッジ率の変動に加え、▲1▼入力データのジッタ、▲2▼入力データのデューティ、▲3▼位相比較器中の識別器(FF)のセットアップ・ホールド特性等のバラツキ及び変動等が挙げられる。従ってこの場合位相比較利得に対する設計は図16,17の場合に比較して複雑であり、該当するシステム中に位相比較回路を組み込んだ後に位相比較利得を含んだPLL全体のループ利得を調整する必要がある。

そこで、本発明では、上記のBang−Bang位相比較器等を備えたPLL回路において、これら入力データのジッタ、入力データのデューティ、位相比較器の識別器(FF)のセットアップ・ホールド特性のバラツキ及び変動等による位相比較利得の変動を正確に検出する回路を提供する。

図18は、本発明の一実施例の原理図である。同図は、上記Bang−Bang位相比較器を用いた位相比較利得検出器を示す。同図に示す通り、この位相比較検出器300は、データDAを識別するクロック信号CLを入力とする位相比較器311、データ識別用クロック信号CLを所定時間遅延させてクロック信号CL’として出力する遅延器313、この遅延クロック信号CL’を入力とする位相比較器312、出力を平滑化するLPF314,315、及び差電圧検出回路316とで構成される。

同図の回路では、データ信号DAとクロック信号CLとが同期している間、即ち入力データ識別用クロック同期時、異なる位相の二つのクロック信号CL,CL’によって夫々データ識別動作を行い、夫々の位相比較器出力D1,D2と、両クロック信号CL,CL’間の時間差、即ち上記所定の遅延時間から、所望の位相比較利得を検出する。これにより、位相比較器のセットアップ・ホールド時間、入力データのエッジ率およびジッタ並びにデューティ変動やバラツキ等があった場合であっても、これらを織り込み済みの位相比較利得が検出可能であるため、当該検出出力に基づいて制御することにより、PLL回路全体のループ利得を一定となるように補償し得る。従って、安定な応答特性が得られ、所望のジッタトランスファ特性を満足するPLL回路を提供可能である。

図19は上記本発明の一実施例の原理を説明するための各位相比較器311,312の出力レベルを示し、同図の位相比較特性は、図14A,14Bに示すものに相当する。同図に示す如く、位相比較出力は位相比較結果としての位相差に応じて変化し、その変化率即ち、ΔV/(Δt/T)が位相比較利得Kpに相当する。上式において、ΔVは、異なる位相条件による位相比較出力を平滑化した値D1とD2との間の差電圧であり、Δtは、当該位相条件の差異を提供する遅延器313による遅延量であり、Tはクロック信号の信号周期を示す。

図20は図18の構成を更に具体化した本発明の一実施例による位相比較検出回路の構成を示す。同回路はハーフレートクロックを用いたBang−Bang位相比較器を適用した位相比較利得検出回路である。図に示す如く、同回路は、識別器(FF)として、データ識別用識別器411、412、データエッジ検出用識別器413、更に位相比較利得検出用識別器414とを設け、更に、排他的論理和回路(EXOR)として、データ識別FF出力DOaとデータエッジ検出用FF出力DOcとの論理をとる回路431、同じくデータ識別FF出力DObとデータエッジ検出用FF出力DOcとの論理をとる回路432、データ識別FF出力DObと位相比較利得検出用FF出力DOdとの論理をとる回路433とが設けられている。そしてこれらの出力は夫々LPF441,442,443で平滑化されて位相比較出力Ph1,Ph2,Ph3として出力される。

この図20の回路では、図21の波形図で示す如く、データ信号DAとクロック信号CLとの同期がとれている状態で、識別器411の出力DOaとしてはA系統のデータが得られ、識別器412の出力DObとしてはB系統のデータが得られる。他方、エッジ検出用識別器413の出力DOcとしては、クロック信号の立ち上がりタイミングがデータ信号DAの変化点と一致するため、上記タイミングによってA系統のデータが得られる確率とB系統のデータが得られる確率とが等しくなる。他方、位相比較利得検出用識別器414の出力としては、クロック信号の立ち上がりタイミングがデータ信号DAの変化点より若干遅れているため、上記タイミングによってA系統のデータが得られる確率よりもB系統のデータが得れる確立の方が大きくなる。

その結果、これらのデータの間の排他的論理和の結果として、EXOR回路441の出力Ph1におけるHレベルの出現確率はEXOR442の出力Ph2におけるHレベルの出現確率と略等しくなる。他方、EXOR回路443の出力Ph3では、Hレベルの出現確率は前者の各々より高くなる。即ち、EXOR回路443の入力であるDOaとDOdとが一致する確率が、EXOR回路441の入力であるDOaとDOcとが一致する確率又はEXOR回路442の入力であるDObとDOcとが一致する確率より低いからである。これは、上記の如く、信号DOcにおけるA系統データの出現確率よりも信号DOdにおけるA系統データの出現確率のほうが小さく、同様に信号DOcにおけるB系統データの出現確率よりも信号DOdにおけるA系統データの出現確率のほうが小さいことによる。

このように、本実施例では、意図的に所定時間Δt遅延させたクロック信号CLbを発生させてデータ識別を行い、その識別結果のデータと、Δt遅延させていないクロックCLにて識別された識別結果のデータとの排他的論理和をとる。更にエッジ検出用クロック信号CLaにてデータ識別を行なった識別結果データと、同じくΔt遅延させていないクロックCLにて識別された識別結果データとの排他的論理和をとる。そしてこれら2種類の排他的論理和の結果をLPFにて平滑化してそのレベル差を、上記遅延量Δtを周期Tで基準化した位相で割ることによって位相比較利得Kpが得られる。

即ち、ここでは同期確立後に意図的に遅延量Δtを発生させて擬似的にデータ信号DAと同期がずれたクロック信号(図20,21の例では信号CLb)を生成し、その「疑似同期ズレ」クロック信号によって同じデータ信号DAの識別を行なう。そしてそこで得られる識別データと、π/2遅延させたクロック信号CLaで識別されたデータとの間の排他的論理和出力を平滑化して「疑似同期ズレ」位相比較検出値を得る。そしてこの疑似同期ズレ位相比較検出値に対し、同期状態のクロック信号CLにて識別された識別データと、同じくπ/2遅延させたクロック信号CLaで識別されたデータとの間の排他的論理和出力を平滑化して得られた値、即ち「同期時位相比較検出値」とを比較する。この比較結果の差異が大きい程、データ信号DAに対するクロック信号CLとの間の位相差に対する位相比較検出感度が高いと言え、もって位相比較利得が高いことと同義である。

このように当該実施例では、現時点でのデータのエッジ率、デューティー、各識別器(FF)のセットアップ・ホールド特性等を全て織り込み済みの位相比較利得を求めることとなるため、非常に正確にオンタイムの実効的な位相比較利得を求めることが可能である。

図23は、本発明の一実施例による位相比較利得補償機能を備えたPLL回路例を示し、図20の構成を有する位相比較器検出回路400の位相比較出力Ph1とPh3との間の差電圧をディジタル信号に変換するA/D変換器510と、当該ディジタル差電圧と所定の基準値とを比較し、その比較結果に基づいてチャージポンプの出力電流を調整し、もって当該PLL回路のループ利得を補償する構成を有する。

又、図23の構成では、図20に示す位相比較検出回路400のデータ出力DOa、DObは、そのまま入力データの再生データとして使用可能である。即ち、これらデータ出力DOa、DObは、図3における識別回路100の出力に相当する。

即ち、図23のPLL回路では、位相比較検出回路400で得られた「疑似同期ズレ」識別信号と「同期」識別信号との間の位相比較出力差電圧に基づいてPLL回路のループ利得を制御するため、現時点での入力信号の特性及び位相比較回路特性を加味した正確なループ利得補償機能を有するPLL回路を提供可能である。

尚、図23の回路構成に限らず、制御回路520はチャージポンプの出力電流振幅1c以外のPLL回路のループ利得の決定要因であるフィルタ30の伝達関数F(s)、VCO40の利得Kv等を制御してPLL回路のループ利得を補償する構成としても良いことは言うまでも無い。

上述の実施例では、位相比較検出回路400においてハーフレートクロックを用いたBang−Bang位相比較器を適用しているが、これ以外にもフルレートクロックを用いた、位相比較特性が鋸波状(図25参照)となる位相比較器に対して本発明を適用することも可能である。図24はその場合の位相比較検出回路の回路構成例を示す。同図の回路では、データ信号DAをクロック信号CLのタイミングで識別する識別器611とデータ信号DAを、クロック信号CLを遅延器622にて所定量遅延させた遅延クロック信号CL’のタイミングで識別する識別器612とが設けられている。そしてこれら識別器611,612による識別出力DO1,DO2の夫々とデータ信号DAとの排他的論理和をとるEXOR631,632を設け、これらEXOR631,632の出力を平滑化する低域通過フィルタ641,642を設けている。

図24の位相比較検出回路によれば、図20の場合同様、識別クロック信号CL,CL’の位相差による識別結果信号DO1,DO2間の差異を、これら識別結果信号DO1,DO2と元のデータ信号DAとの排他論理和演算を行ってそれらEXOR演算結果を夫々平滑化して差を得ることで検出する。図25は、その場合に得られる差電圧を説明するための図である。ここで検出されるLPF641,642の出力Ph1’とPh2’との間の差電圧ΔVを、遅延器622による遅延量であるΔtを周期Tで基準化した遅延位相量を表すΔt/Tで割ることで、位相比較利得であるKpが得られる(下式参照)。

Kp=ΔV/(Δt/T)

このようにして得られた位相比較検出値を基にして図23に示す制御回路520がチャージポンプ20の電流振幅値Ic等のループ利得決定要因パラメータを調整制御することでPLL回路のループ利得を補償する。

尚この場合では、図16の例に比較して、入力データのエッジ率以外の要因による利得変動があった場合にも位相比較利得を補償可能である。

又、位相比較器を他の構成としても良く、クロック信号CLの位相又は入力データ信号DAの位相を所定量遅延させ又は進ませる機能を有する、位相比較器同様の回路構成を有する位相検出回路と組み込んでPLL回路を構成しても良い。

以上説明したように、本発明によればPLL回路の位相比較器の変動・バラツキ及び入力データのジッタ等に応じて位相比較利得を補償するため、PLLのループ利得を精度良く一定に保つことが可能であると共にジッタ周波数特性を安定化することが出来、もってPLL回路の性能の向上が可能である。

図26、図27は本発明の他の実施例による誤同期検出装置を説明するための図である。図26は図18の回路構成と実質的に同様であり、対応構成部分には同一符号を付し、重複説明を省く。

この場合、PLL回路の位相比較器として図27の破線にて示す如くの鋸波特性を有するものを想定する。即ち、検出位相差に応じて出力される検出電圧が検出位相差に応じて鋸波状に変化する特性を有するものである。このようなPLL回路では、この鋸波の上昇ランプ部の中間部、即ち図中P点にて位相ロックを掛けることにより、入力データ信号DAの信号変化点間の中央部分、即ちアイパターンの中心部のタイミングでデータを識別し得るようにクロック信号CLの位相をロックし得る(図5参照)。

ところが、実際には入力データ信号DAのデューティーの変動等により、鋸波特性に図27の実線で示す如くの波形の歪が生ずることがある。その場合、PLL回路では、図27中のQ点にて誤って位相ロックを掛けてしまう場合がある。この場合誤同期となり、クロック信号はデータのアイパターンのクロスポイントのタイミングでデータ識別を行なうことになり、識別データが誤りとなる可能性が高い。

このような誤同期を防止するため、本発明の他の実施例による誤同期検出装置では、例えば図20乃至図25と共に述べたように、位相比較器の位相比較検出出力は、遅延器313,622によって与えられる遅延量Δtによって変化する。しかしながら、その変化量は、データ信号DAとクロック信号CLとの間の絶対位相に依存する特性を有する。即ち、データ信号DAとクロック信号CLとの間の位相差がゼロ近辺、即ちデータ信号DAのアイパターンの中心部のタイミング(図5参照)でデータを識別する状態では、正しくデータを識別できるため、その識別信号とデータ信号DAとの排他的論理和結果には、データ識別タイミングを遅延器313にて遅延させても、その遅延量Δtが周期Tよりある程度小さい限り、その遅延量に略比例した程度の差異しか生じない。

逆にアイパターンのクロスポイントのタイミング,即ちデータ信号DAの値が不定状態でデータ識別する場合正しいデータを識別できる可能性は50%程度である。他方、そのタイミングから上記所定量Δt遅延させ、その遅延量Δtが上記不定状態(不感帯)を超えて略正確にデータ識別が可能な識別タイミングとなる程度に大きい場合、正しいデータ識別の可能性は100%近くとなる。その結果、そのような識別タイミングによる識別結果は、遅延無しの場合(即ち不定状態で識別率50%程度の場合)の識別結果とは大きく異なることとなり、その差異は上記のアイパターンの中心付近での識別の場合に比してかなり大きくなる。

この点を図27と共に再度説明するに、アイパターンの中心付近でのデータ識別の場合、即ち同図のP点の場合の遅延有り無しの位相比較出力は夫々D1,D2であり、その差はΔVである。他方、アイパターンのクロスポイント付近での場合、即ちQ点の場合の遅延有り無しの位相比較出力は夫々D1’、D2’であり、その差はΔV’となる。図示の如く、明らかに

ΔV<ΔV’

である。従ってΔVが所定の基準値を超えて大きくなったことを検出することによって誤同期を検出可能である。

尚本発明は上記実施例に限られず、本発明の基本思想に従った様々な変形例が実施可能であり、それらの変形例も本発明の範囲に含まれることは言うまでも無い。

本発明は、以下の構成を含む。

(構成1)

入力データ信号に対する、そのデータを識別するための識別タイミング信号の位相関係を所定の位相関係にするためのPLL回路における、入力データ信号と識別タイミング信号との間の位相を比較する際の位相比較利得を検出する位相比較利得検出回路であって、

入力データ信号と識別タイミング信号との間の位相関係を検出する第1の位相比較手段と、

入力データ信号と識別タイミング信号との間の位相関係を所定量シフトさせる位相関係シフト手段と、

位相関係シフト手段によってシフトされた入力データ信号と識別タイミング信号との間の位相関係を検出する第2の位相比較手段と、

第1及び第2の位相比較手段の夫々の出力の差及び上記位相関係シフト手段が位相関係をシフトさせる所定量に基づいて位相比較利得を検出する位相比較利得検出手段とよりなる位相比較利得検出回路。

(構成2)

上記構成1の位相比較利得検出回路において、

第1の位相比較手段は入力データ信号と識別タイミング信号とが略同期した状態の両者間の位相関係を検出し、

第2の位相比較手段は入力データ信号と識別タイミング信号とが略同期した状態から所定量シフトした状態における両者間の位相関係を検出する構成の位相比較利得検出回路。

(構成3)

所定周期でデータが切り替わる入力データ信号に対する、そのデータを識別するための識別タイミング信号の位相関係を所定の位相関係にするためのPLL回路における、入力データ信号と識別タイミング信号との間の位相を比較する際の位相比較利得を検出する位相比較利得検出回路であって、

入力データ信号のデータを識別するデータ識別部のデータ識別出力と、データ識別タイミングを第1の所定量ずらすことのよって入力データ信号のデータの切り替え検出する切り替え検出部のデータ識別出力との間のデータ相関を検出することによって両者の位相を比較する第1の位相比較手段と、

上記データ識別部のデータ識別出力と、上記切り替え検出部におけるデータ識別タイミングを更に第2の所定量ずらせた際のデータ識別出力との間のデータ相関を検出することによって両者の位相を比較する第2の位相比較手段と、

第1及び第2の位相比較手段の夫々の出力の差及び上記識別タイミングをずらす第2の所定量に基づいて位相比較利得を検出する位相比較利得検出手段とよりなる位相比較利得検出回路。

(構成4)

入力データ信号に対する、そのデータを識別するための識別タイミング信号の位相関係を所定の位相関係にするためのPLL回路における、入力データ信号と識別タイミング信号との間の位相を比較する際の位相比較利得を検出する位相比較利得検出回路であって、

入力データ信号のデータと、入力データ信号を上記識別タイミング信号によって識別することによって得られた識別出力のデータとの間のデータ相関を検出することで位相を比較する第1の位相比較手段と、

入力データ信号のデータと、入力データ信号を上記識別タイミング信号の識別タイミングから所定量をずらせたタイミングにて識別することによって得られた識別出力のデータとの間のデータ相関を検出することで位相を比較する第2の位相比較手段と、

第1及び第2の位相比較手段の夫々の出力の差及び上記識別タイミング信号の識別タイミングをずらす所定量に基づいて位相比較利得を検出する位相比較利得検出手段とよりなる位相比較利得検出回路。

(構成5)

第1及び第2の位相比較手段におけるデータ間のデータ相関検出は、排他的論理和演算によって実現される構成を有してなる上記構成3又は4の位相比較利得検出回路。

(構成6)

排他論理和出力は平滑化されて位相比較利得検出手段に入力される構成よりなる上記構成5の位相比較利得検出回路。

(構成7)

各々のデータ識別はフリップフロップ回路によって実行される構成とされてなる上記構成3乃至6のうちのいずれかの位相比較利得検出回路。

(構成8)

入力データ信号に対し、そのデータを識別するための識別タイミング信号を同期させるPLL回路において入力データ信号と識別タイミング信号との間の誤同期を検出するための誤同期検出回路であって、

入力データ信号と識別タイミング信号との間の位相関係を検出する第1の位相比較手段と、

入力データ信号と識別タイミング信号との間の位相関係を所定量シフトさせる位相関係シフト手段と、

位相関係シフト手段によってシフトされた入力データ信号と識別タイミング信号との間の位相関係を検出する第2の位相比較手段と、

第1及び第2の位相比較手段の夫々の出力の差に基づいて誤同期状態を検出する構成の誤同期検出回路。

(構成9)

入力データ信号に対し、そのデータを識別するための識別タイミング信号を同期させるPLL回路において入力データ信号と識別タイミング信号との間の誤同期を検出するための誤同期検出回路であって、

入力データ信号のデータを識別するデータ識別部のデータ識別出力と、データ識別タイミングを第1の所定量ずらすことのよって入力データ信号のデータの切り替え検出する切り替え検出部のデータ識別出力との間のデータ相関を検出することによって両者の位相を比較する第1の位相比較手段と、

上記データ識別部のデータ識別出力と、上記切り替え検出部におけるデータ識別タイミングを更に第2の所定量ずらせた際のデータ識別出力との間のデータ相関を検出することによって両者の位相を比較する第2の位相比較手段と、

第1及び第2の位相比較手段の夫々の出力の差に基づいて誤同期状態を検出する誤同期検出手段とよりなる

誤同期検出回路。

(構成10)

入力データ信号に対し、そのデータを識別するための識別タイミング信号を同期させるPLL回路において入力データ信号と識別タイミング信号との間の誤同期を検出するための誤同期検出回路であって、

入力データ信号のデータと、入力データ信号を上記識別タイミング信号によって識別することによって得られた識別出力のデータとの間の相関を検出することで位相を比較する第1の位相比較手段と、

入力データ信号のデータと、入力データ信号を上記識別タイミング信号の識別タイミングから所定量をずらせたタイミングにて識別することによって得られた識別出力のデータとの間の相関を検出することで位相を比較する第2の位相比較手段と、

第1及び第2の位相比較手段の夫々の出力の差に基づいて誤同期状態を検出する誤同期検出手段よりなる誤同期検出回路。

(構成11)

上記構成1乃至7のうちのいずれかの位相比較利得検出回路及び上記構成8乃至11のうちのいずれかの誤同期検出回路のうちの少なくとも一方の回路を備えたPLL回路であって、

該位相比較利得検出回路の位相比較検出利得に基づいてPLL回路のループ利得を制御する制御回路、及び上記誤同期検出回路の誤同期検出結果に基づいて位相ロック動作を制御する制御回路のうちの少なくとも一方の制御回路を更に有するPLL回路。

(構成12)

前記制御回路は、当該PLL回路を構成するチャージポンプの電流振幅、ループフィルタの伝達関数、VCOの制御利得のうちの少なくともいずれかを変化させることによってPLL回路のループ利得を制御する構成よりなる上記構成11のPLL回路。

(構成13)

入力データ信号に対する、そのデータを識別するための識別タイミング信号の位相関係を所定の位相関係にするためのPLL回路における、入力データ信号と識別タイミング信号との間の位相を比較する際の位相比較利得を検出する位相比較利得検出方法であって、

入力データ信号と識別タイミング信号との間の位相関係を検出する第1の位相比較段階と、

入力データ信号と識別タイミング信号との間の位相関係を所定量シフトさせる位相関係シフト段階と、

位相関係シフト手段によってシフトされた入力データ信号と識別タイミング信号との間の位相関係を検出する第2の位相比較段階と、

第1及び第2の位相比較段階の夫々で得られる出力値の差及び上記位相関係シフト段階にて位相関係をシフトさせる所定量に基づいて位相比較利得を検出する位相比較利得検出段階とよりなる位相比較利得検出方法。

(構成14)

上記構成13の位相比較検出方法において、

第1の位相比較方法では入力データ信号と識別タイミング信号とが略同期した状態の両者間の位相関係を検出し、

第2の位相比較段階では入力データ信号と識別タイミング信号とが略同期した状態から所定量シフトした状態における両者間の位相関係を検出する構成の位相比較検出方法。

(構成15)

所定周期でデータが切り替わる入力データ信号に対する、そのデータを識別するための識別タイミング信号の位相関係を所定の位相関係にするためのPLL回路における、入力データ信号と識別タイミング信号との間の位相を比較する際の位相比較利得を検出する位相比較利得検出方法であって、

入力データ信号のデータを識別するデータ識別部のデータ識別出力と、データ識別タイミングを第1の所定量ずらすことのよって入力データ信号のデータの切り替え検出する切り替え検出部のデータ識別出力との間のデータ相関を検出することによって両者の位相を比較する第1の位相比較段階と、

上記データ識別部のデータ識別出力と、上記切り替え検出部におけるデータ識別タイミングを更に第2の所定量ずらせた際のデータ識別出力との間のデータ相関を検出することによって両者の位相を比較する第2の位相比較段階と、

第1及び第2の位相比較段階の夫々における比較出力値の差及び上記識別タイミングをずらす第2の所定量に基づいて位相比較利得を検出する位相比較利得検出段階とよりなる位相比較利得検出方法。

(構成16)

入力データ信号に対する、そのデータを識別するための識別タイミング信号の位相関係を所定の位相関係にするためのPLL回路における、入力データ信号と識別タイミング信号との間の位相を比較する際の位相比較利得を検出する位相比較利得検出方法であって、

入力データ信号のデータと、入力データ信号を上記識別タイミング信号によって識別することによって得られた識別出力のデータとの間のデータ相関を検出することで位相を比較する第1の位相比較段階と、

入力データ信号のデータと、入力データ信号を上記識別タイミング信号の識別タイミングから所定量をずらせたタイミングにて識別することによって得られた識別出力のデータとの間のデータ相関を検出することで位相を比較する第2の位相比較段階と、

第1及び第2の位相比較段階の夫々における比較出力の差及び上記識別タイミング信号の識別タイミングをずらす所定量に基づいて位相比較利得を検出する位相比較利得検出段階とよりなる位相比較利得検出方法。

(構成17)

入力データ信号に対し、そのデータを識別するための識別タイミング信号を同期させるPLL回路において入力データ信号と識別タイミング信号との間の誤同期を検出するための誤同期検出方法であって、

入力データ信号と識別タイミング信号との間の位相関係を検出する第1の位相比較段階と、

入力データ信号と識別タイミング信号との間の位相関係を所定量シフトさせる位相関係シフト段階と、

位相関係シフト手段によってシフトされた入力データ信号と識別タイミング信号との間の位相関係を検出する第2の位相比較段階と、

第1及び第2の位相比較段階における夫々の出力の差に基づいて誤同期状態を検出する構成の誤同期検出方法。

(構成18)

入力データ信号に対し、そのデータを識別するための識別タイミング信号を同期させるPLL回路において入力データ信号と識別タイミング信号との間の誤同期を検出するための誤同期検出方法であって、

入力データ信号のデータを識別するデータ識別部のデータ識別出力と、データ識別タイミングを第1の所定量ずらすことのよって入力データ信号のデータの切り替え検出する切り替え検出部のデータ識別出力との間のデータ相関を検出することによって両者の位相を比較する第1の位相比較段階と、

上記データ識別部のデータ識別出力と、上記切り替え検出部におけるデータ識別タイミングを更に第2の所定量ずらせた際のデータ識別出力との間のデータ相関を検出することによって両者の位相を比較する第2の位相比較段階と、

第1及び第2の位相比較段階の夫々における出力の差に基づいて誤同期状態を検出する誤同期検出段階とよりなる誤同期検出方法。

(構成19)

入力データ信号に対し、そのデータを識別するための識別タイミング信号を同期させるPLL回路において入力データ信号と識別タイミング信号との間の誤同期を検出するための誤同期検出回路であって、

入力データ信号のデータと、入力データ信号を上記識別タイミング信号によって識別することによって得られた識別出力のデータとの間の相関を検出することで位相を比較する第1の位相比較段階と、

入力データ信号のデータと、入力データ信号を上記識別タイミング信号の識別タイミングから所定量をずらせたタイミングにて識別することによって得られた識別出力のデータとの間の相関を検出することで位相を比較する第2の位相比較段階と、

第1及び第2の位相比較段階の夫々における出力の差に基づいて誤同期状態を検出する誤同期検出段階とよりなる誤同期検出方法。

Claims (5)

- 入力データ信号に対する、そのデータを識別するための識別タイミング信号の位相関係を所定の位相関係にするためのPLL回路における、入力データ信号と識別タイミング信号との間の位相を比較する際の位相比較利得を検出する位相比較利得検出回路であって、

入力データ信号と識別タイミング信号との間の位相関係を検出する第1の位相比較手段と、

入力データ信号と識別タイミング信号との間の位相関係を所定量シフトさせる位相関係シフト手段と、

位相関係シフト手段によってシフトされた入力データ信号と識別タイミング信号との間の位相関係を検出する第2の位相比較手段と、

第1及び第2の位相比較手段の夫々の出力の差及び上記位相関係シフト手段が位相関係をシフトさせる所定量に基づいて位相比較利得を検出する位相比較利得検出手段とよりなる位相比較利得検出回路。 - 所定周期でデータが切り替わる入力データ信号に対する、そのデータを識別するための識別タイミング信号の位相関係を所定の位相関係にするためのPLL回路における、入力データ信号と識別タイミング信号との間の位相を比較する際の位相比較利得を検出する位相比較利得検出回路であって、

入力データ信号のデータを識別するデータ識別部のデータ識別出力と、データ識別タイミングを第1の所定量ずらすことのよって入力データ信号のデータの切り替え検出する切り替え検出部のデータ識別出力との間のデータ相関を検出することによって両者の位相を比較する第1の位相比較手段と、

上記データ識別部のデータ識別出力と、上記切り替え検出部におけるデータ識別タイミングを更に第2の所定量ずらせた際のデータ識別出力との間のデータ相関を検出することによって両者の位相を比較する第2の位相比較手段と、

第1及び第2の位相比較手段の夫々の出力の差及び上記識別タイミングをずらす第2の所定量に基づいて位相比較利得を検出する位相比較利得検出手段とよりなる位相比較利得検出回路。 - 入力データ信号に対する、そのデータを識別するための識別タイミング信号の位相関係を所定の位相関係にするためのPLL回路における、入力データ信号と識別タイミング信号との間の位相を比較する際の位相比較利得を検出する位相比較利得検出回路であって、

入力データ信号のデータと、入力データ信号を上記識別タイミング信号によって識別することによって得られた識別出力のデータとの間のデータ相関を検出することで位相を比較する第1の位相比較手段と、

入力データ信号のデータと、入力データ信号を上記識別タイミング信号の識別タイミングから所定量をずらせたタイミングにて識別することによって得られた識別出力のデータとの間のデータ相関を検出することで位相を比較する第2の位相比較手段と、

第1及び第2の位相比較手段の夫々の出力値の差及び上記識別タイミング信号の識別タイミングをずらす所定量に基づいて位相比較利得を検出する位相比較利得検出手段とよりなる位相比較利得検出回路。 - 入力データ信号に対し、そのデータを識別するための識別タイミング信号を同期させるPLL回路において入力データ信号と識別タイミング信号との間の誤同期状態を検出するための誤同期検出回路であって、

入力データ信号と識別タイミング信号との間の位相関係を検出する第1の位相比較手段と、

入力データ信号と識別タイミング信号との間の位相関係を所定量シフトさせる位相関係シフト手段と、

位相関係シフト手段によってシフトされた入力データ信号と識別タイミング信号との間の位相関係を検出する第2の位相比較手段と、

第1及び第2の位相比較手段の夫々の出力値のに基づいて誤同期状態を検出する構成の誤同期検出回路。 - 上記請求の範囲1乃至3のうちのいずれか一項に記載の位相比較利得検出回路又は請求の範囲4に記載の誤同期検出回路のうちの少なくともいずれかの回路を備えたPLL回路であって、

該位相比較利得検出回路の位相比較検出利得に基づいてPLL回路のループ利得を制御する制御回路又は誤同期検出回路の誤同期検出出力に基づいて位相ロック動作を制御する制御回路を更に備えたPLL回路。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2002/011319 WO2004040768A1 (ja) | 2002-10-30 | 2002-10-30 | 位相比較利得検出回路、誤同期検出回路及びpll回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2004040768A1 JPWO2004040768A1 (ja) | 2006-03-02 |

| JP3908764B2 true JP3908764B2 (ja) | 2007-04-25 |

Family

ID=32260021

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004547995A Expired - Fee Related JP3908764B2 (ja) | 2002-10-30 | 2002-10-30 | 位相比較利得検出回路、誤同期検出回路及びpll回路 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP3908764B2 (ja) |

| WO (1) | WO2004040768A1 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7593497B2 (en) | 2005-10-31 | 2009-09-22 | Teradyne, Inc. | Method and apparatus for adjustment of synchronous clock signals |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01215122A (ja) * | 1988-02-24 | 1989-08-29 | Hitachi Ltd | 位相同期信号発生回路 |

| JPH0730415A (ja) * | 1993-07-12 | 1995-01-31 | Oki Electric Ind Co Ltd | Pll回路 |

| JP4094851B2 (ja) * | 2000-01-17 | 2008-06-04 | 富士通株式会社 | Pll回路 |

-

2002

- 2002-10-30 WO PCT/JP2002/011319 patent/WO2004040768A1/ja active Application Filing

- 2002-10-30 JP JP2004547995A patent/JP3908764B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPWO2004040768A1 (ja) | 2006-03-02 |

| WO2004040768A1 (ja) | 2004-05-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4163180B2 (ja) | クロックデータリカバリー回路 | |

| US6879195B2 (en) | PLL lock detection circuit using edge detection | |

| EP2291914B1 (en) | Fast-locking bang-bang pll with low output jitter | |

| US6915081B2 (en) | PLL circuit and optical communication reception apparatus | |

| JP3649194B2 (ja) | Pll回路および光通信受信装置 | |

| US8686768B2 (en) | Phase locked loop | |

| US6404363B1 (en) | Circuit for recovering digital clock signal and method thereof | |

| US7983370B2 (en) | Clock and data recovery circuit | |

| US7279992B2 (en) | Circuit for detecting phase errors and generating control signals and PLL using the same | |

| WO1995034127A1 (en) | A three-state phase-detector/charge pump circuit with no dead-band region | |

| KR100434501B1 (ko) | 듀티 정정을 기반으로 하는 주파수 체배기 | |

| JP3109587B2 (ja) | オーバーサンプリング型クロックリカバリ回路 | |

| US7598816B2 (en) | Phase lock loop circuit with delaying phase frequency comparson output signals | |

| EP1199806B1 (en) | PLL circuit and optical communication reception apparatus | |

| US7109806B2 (en) | Device and method for detecting phase difference and PLL using the same | |

| JP3908764B2 (ja) | 位相比較利得検出回路、誤同期検出回路及びpll回路 | |

| JP3926368B2 (ja) | 位相誤同期検出回路 | |

| US7078938B2 (en) | Method of detecting phase difference, phase detector for performing the same and clock-and-data recovering device including the phase detector | |

| JP2005086789A (ja) | クロックデータリカバリ回路 | |

| US20040088619A1 (en) | Method and apparatus for enabling fast clock phase locking in a phase-locked loop | |

| US20090243673A1 (en) | Phase locked loop system and phase-locking method for phase locked loop | |

| US6934869B1 (en) | Method and apparatus for eliminating dead zone in phase locked loops using binary quantized phase detectors | |

| US7440518B2 (en) | Phase-locked loop circuit | |

| WO1998039847A1 (en) | Emulating narrow band phase-locked loop behavior on a wide band phase-locked loop | |

| EP0968568A1 (en) | Emulating narrow band phase-locked loop behavior on a wide band phase-locked loop |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070116 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070118 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110126 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110126 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120126 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130126 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130126 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140126 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |