JP3668356B2 - 高速フーリエ変換演算回路 - Google Patents

高速フーリエ変換演算回路 Download PDFInfo

- Publication number

- JP3668356B2 JP3668356B2 JP08799997A JP8799997A JP3668356B2 JP 3668356 B2 JP3668356 B2 JP 3668356B2 JP 08799997 A JP08799997 A JP 08799997A JP 8799997 A JP8799997 A JP 8799997A JP 3668356 B2 JP3668356 B2 JP 3668356B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- fourier transform

- fast fourier

- radix

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Complex Calculations (AREA)

Description

【発明の属する技術分野】

本発明は、信号処理、データ解析、線形システム等に利用される高速フーリエ変換に係り、特に、入力データ点数Nに対して、入力データ点数が減少しても、高速フーリエ変換(以下、FFTと略称する)が行える高速フーリエ変換演算回路に関するものである。

【0002】

【従来の技術】

近年のディジタル技術の発展に伴い、地上波テレビ放送が現行のアナログ放送からディジタル放送へ移行しようと準備が行われている。この地上波ディジタルテレビ放送では変調方式としてマルチキャリア直交周波数分割多重変調方式(以下、OFDMと略称する)の採用が見込まれている。このOFDMでは搬送波の変復調に高速フーリエ変換が用いられている。この変調方式で用いられる高速フーリエ変換の高速フーリエ変換点数NはOFDMの搬送波数Kに依存する。

【0003】

この搬送波数Kは規格上では1705本、6817本、と様々であり、また、これらの規格はさらに増える可能性がある。これらの複数の搬送波の本数に対応させるためにはそれぞれ専用の高速フーリエ変換演算回路を用意する必要があった。また、従来存在している複数のデータ点数に対応可能な高速フーリエ変換演算回路は点数Nに対してN/R、N/R2、(Rは基数)…というようにRのべき乗で分割された点数しか計算できない。

【0004】

また、異なる基数のバタフライ演算回路を持たせることで、多くの点数に対応した高速フーリエ変換回路も存在するが、この場合に全ての並べ替え回路の構造を変更する必要があり、演算回路の制御が困難になる。したがってRに関係なく同一の回路で様々な点数に対応することができ、かつ、データ点列の変更に対しての制御が容易な回路は存在していない。

【0005】

【発明が解決しようとする課題】

前述のように、従来の高速フーリエ変換を行う回路では点数Nが決定されると、回路構成も一意に定まってしまう。したがって、入力データの点数が変更になり、減少しても同一の回路で演算を行うことができないという問題点があった。

【0006】

また、点数を可変にすることのできる高速フーリエ変換演算回路でも点数の変更は基数Rのべき乗分の1でしか変更することができない。即ち、点数の変更が基数Rに左右されるという問題点があった。

【0007】

本発明は、上記従来の欠点に鑑み、入力データ点数が減少しても、基数Rに左右されることなく変換点数を設定し、同一の回路で変換が行える回路を提供することを目的とするものである。

【0008】

【課題を解決するための手段】

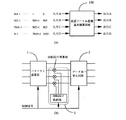

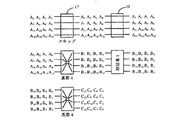

図1は本発明の原理を説明する図であり、図1(a)は基本回路へのデータ入力の概念を示し、図1(b)は本発明の基本回路の構成例を示している。図2は本発明におけるバタフライ演算回路の構成例を示し、図3はデータ並べ替え回路の構成例を示している。上記の問題点は下記の如く構成した高速フーリエ変換回路によって解決される。

【0009】

(1)処理する高速フーリエ変換(FFT)点数Nについて、高速フーリエ変換を行う回路であって、バタフライ演算部1、回転因子乗算部3、データ並べ替え回路2からなるR入力の基本演算回路100を1段として、これをM個(=logRN)(Rは基数)直列に並べて高速フーリエ変換が行えるように構成し、バタフライ演算部1では、上記R入力間で基数Rのたすき掛け演算を行い、回転因子乗算部3では、バタフライ演算部2の出力のうちR−1個の出力に対して回転因子の乗算を行い、データ並べ替え回路2では、上記入力データNに対し2段目以降の演算に必要となるデータの組を生成し、さらに、外部からの制御信号により、バタフライ演算部1の基数が変更可能であり、回転因子乗算部3および、データ並べ替え回路2を基数に応じて変更できる基本演算回路100を1個もしくは複数個備え、そのうち、1個もしくは複数個の基本演算回路100の基数を変更することで、上記高速フーリエ変換点数Nが基数Rに関わりなくN/2、N/4、…となっても同一の回路で高速フーリエ変換を行う。

【0010】

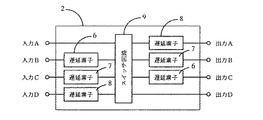

(2)(1)に示した高速フーリエ変換演算回路であり、バタフライ演算の途中経過を出力する信号線を備え、選択回路5により、前記信号線の信号とほかの計算結果が選択できるバタフライ演算部1を備え、外部からの信号により、基数の変更を可能にした。

【0011】

(3)(1)に示した高速フーリエ変換回路であり、基本演算回路100におけるデータ並べ替え回路で、入力段に複数の遅延量が可変な遅延素子6,7,8を備え、基数に応じて切り替え状態を変更できるスイッチ回路9を備え、出力段に複数の遅延量が可変の遅延素子6,7,8を備え、外部からの制御信号に基づいて基数が変更に対応することが可能なデータ並べ替え回路を持つ。

【0012】

(4)(1)に示した高速フーリエ変換演算回路であり、M段の基本演算回路100を直列に接続した回路において、前方からL段(L≦M)を基数が変更可能な基本演算回路とする。

【0013】

(5)(1)に示した高速フーリエ変換演算回路であり、全ての基本演算回路100を基数が変更可能な演算回路とし、すべての基本演算回路100で基数をRより小さく、同一の値に設定し、請求項3におけるデータ並べ替え回路2において、遅延量を変更できる遅延素子6,8の遅延量を等しくし、外部からの制御信号に基づいてそれぞれ独立した入力データをフーリエ変換し出力することが可能なもの。

【0015】

以上の構成において更に、処理する高速フーリエ変換(FFT)点数Nについて、高速フーリエ変換を行う回路であって、バタフライ演算部1、回転因子乗算部3、データ並べ替え回路 2からなる基本演算回路100を複数個並べることで構成する。このうち1個もしくは複数個の基本演算回路100のバタフライ演算部1を基数が変更可能な回路構成にする。この演算回路に入力データを適切に入力することでN点の高速フーリエ変換の結果が得られる。

【0016】

このとき、1個もしくは複数個のバタフライ演算部1の基数を変更することで、基数Rに関係することなくフレキシブルにN/2、N/4、…、2点の高速フーリエ変換が可能となる。さらに、この演算回路を用いることで、これまでに高速フーリエ変換点数ごとに必要となっていた演算回路がただ一つの演算回路でよくなるので、ハードウェアの削減ができる。また、地上波ディジタル放送の種々の伝送パラメータに対応でき、受信システムを瞬時に切り替えることができる。

【0017】

本発明によると、ハードウェアの大幅な増大なしに複数のデータ点列数に対応した高速フーリエ変換が可能である。また、本発明の構成によると、独立した2つのデータを高速にフーリエ変換できる。

【0018】

【発明の実施の形態】

以下、本発明の実施の形態について図面を用いて詳細に説明する。図1〜図3は本発明の原理を説明する図であり、図4〜図12は本発明の実施の形態を示した図である。図13は従来の高速フーリエ変換を説明する図であり、図14〜図16は本発明の他の実施の形態を示している。

【0019】

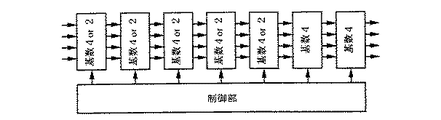

本発明において、高速フーリエ変換(FFT)点数Nの高速フーリエ変換演算回路は図4に示すように、基本演算回路100をM個(=logRN)並べて構成する。各基本演算回路100はバタフライ演算部1、回転因子演算部3、データ並べ替え回路2から構成される。バタフライ演算部1では、図13に示すたすき掛け演算を行い、回転因子演算部3では対応する回転因子とデータを乗算し、データ並べ替え回路2では、次段の入力に対応したデータを生成するためにデータの並べ替えを行う。

【0020】

このような高速フーリエ変換演算回路について入力データ数Nが減少した場合、バタフライ演算回路における基数Rを変更することで、入力データ数の変更に対応する。この場合における演算の例として基数Rが4、高速フーリエ変換点数N=64とする。

【0021】

64=43であるので、バタフライ演算部1、回転因子乗算部3、データ並べ替え部2からなる基本回路100を3個直列に並べる。この演算回路の全体の構成を図4に示す。

【0022】

データ点列数64の高速フーリエ変換を実行する場合を図5を用いて説明する。入力データA0…A63を図のように1段目の入力としてあたえる。1段目のバタフライ演算部10で基数4のバタフライ演算が行われデータB0…B63が出力される。これらのデータを2段目の入力に適するように、データの組を変更する必要がある。これを遅延量4のデータ並べ替え回路11で実行する。このデータ並べ替え回路11を経てデータは次段の入力に適したデータの組に変更される。

【0023】

並べ替えられたデータB0…B63は2段目のバタフライ演算部12に入力されて、基数4のバタフライ演算が実行され、データC0…C63が出力される。前段と同様に、これらのデータはデータ並べ替え回路13でデータの組が変更され、3段目のバタフライ演算部14に入力される。3段目のバタフライ演算回路で基数4のバタフライ演算が実行されて、データD0…D63が出力される。このデータD0…D63が高速フーリエ変換の結果となる。

【0024】

次に、この回路を用いてデータ点列数32の高速フーリエ変換を実行する場合を図6を用いて説明する。入力データA0…A31を図のように1段目の入力としてあたえ、1段目のバタフライ演算部15の基数を変更し、この演算部で基数2のバタフライ演算を行う。1段目のバタフライ演算部15の出力データB0…B31はデータ並べ替え回路16でデータの組の変更が行われ、次段に入力される。2段目以降は64点の変換と同様に基数4のバタフライ演算が実行され、得られた結果D0…D31が高速フーリエ変換の結果となる。

【0025】

同様にデータ点列数16の高速フーリエ変換を実行する場合は、図7に示すように入力データは1段目のバタフライ演算部17、データ並べ替え回路18をスキップする。これ以降の演算回路で基数4のバタフライ演算を行うことで得られるC0…C16が高速フーリエ変換の結果となっている。

【0026】

基数の変更や基本演算回路のスキップといった動作はデータ点列数Nをさらに増加させたときも同様の効果を示し、図8に示す回路では16〜16384点の高速フーリエ変換に対応することができる。

【0027】

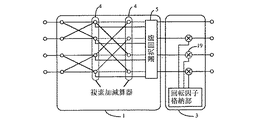

次に、基数の変更について図9、図10を用いて詳細に説明する。この場合、演算の切り替え方法は以下のとおりである。高速フーリエ変換の性質として、データ点列数の大きな高速フーリエ変換は、データ点列数のより小さな高速フーリエ変換を内部に含んでいる。この性質から、基数4のバタフライ演算には基数2のバタフライ演算が含まれていることがわかる。そこで、基数の切り替えが可能な演算回路では、基数4のバタフライ演算の途中で、基数2のバタフライ演算の結果を出力できるようにしておく。

【0028】

これは図9において、2段に接続された複素加減算器4の1段目の出力を取り出すことで実現される。この出力は2段目の複素加減算器4の入力と選択回路5の入力に接続される。2段目の複素加減算器4で演算された結果は基数4のバタフライ演算の結果となっているので、この基数4のバタフライ演算の結果と、基数2のバタフライ演算の結果を選択回路5で選択することで基数の変更を実現している。

【0029】

図9は基数が2のときのバタフライ演算部1、回転因子乗算部3の動作を示しており、実線で示した経路を通ってデータが流れていく。また、このときの回転因子は出力Bと出力Dにのみ乗算されるので、出力Cに乗算するための複素乗算器19は1を乗じるようにしておく。基数が4のときのバタフライ演算部1の動作は図10に示すようになり、図9と同様に実線部分をデータが流れていく。

【0030】

次に、基本演算回路のスキップについて説明する。この処理はある段の基本演算回路100の演算をまったく行わない。また、スキップされる基本演算回路100は常に前方の段であるので、基本演算回路100にスキップ用の特別な回路を付加することなく、スキップする段の次段に直接入力すればよいことになる。したがって、高速フーリエ変換演算回路の入力部で複数の段への入力を行えるようにしておき、この入力線を選択することでスキップ処理が容易に行えるようになる。

【0031】

これより、基本回路の内部には付加回路がないので、回路構成の縮小に役立てることができる。また、本発明においてはスキップする演算回路は常に前方のステージである。こうすることでスキップ処理を施した演算回路以降の演算において変更を加えることなく演算することができる。これは演算の流れ図を示した、図5〜7において最終の2段の演算の順番が同じであるということから容易に理解できる。この性質はデータ点列数が多くなっても同様である。

【0032】

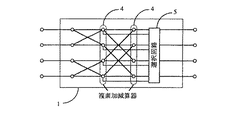

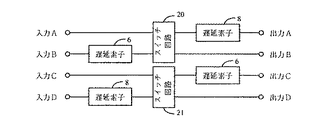

データ並べ替え回路2の変更方法について図11、図12を用いて詳細に説明する。データ並べ替え回路2はバタフライ演算部1の基数Rによって変更を加える必要がある。図3に示すのは基数4のときに用いられる構成である。データ並べ替え回路2では、まず、データ点列を入力A、入力B、入力C、入力Dからそれぞれシリアルに入力する。

【0033】

入力B、入力C、入力Dから入力されたそれぞれのデータは、高速フーリエ変換の各基本回路で必要とされるだけ遅延させる。このとき、入力Cに接続される遅延素子7の遅延量は入力Bに接続される遅延素子6の遅延量の2倍、入力Dに接続される遅延素子8の遅延量は遅延素子6の遅延量の3倍である。

【0034】

遅延させたデータは4個の入力を適切に配分するスイッチング回路9に入力する。スイッチング回路では図12に示すようにデータの交換を行う。データ交換を行った後、出力A、出力B、出力Cのデータを遅延させ、データ出力のタイミングをあわせ、出力する。このようにして各基本回路で必要となるデータの組になるように並べ替えを行う。また、基数2のバタフライ演算部1に対応する場合の回路のブロック図を図11に示す。

【0035】

基数2のバタフライ演算部1に対応したデータ並べ替え回路2の動作は以下のとおりである。データ点列は入力A、入力B、入力C、入力Dからそれぞれシリアルに入力され、入力B、入力Dから入力されたデータを高速フーリエ変換で必要な数だけ遅延させる。このとき、入力Bと入力Dに接続される遅延素子6,8の遅延量は等しくなる。

【0036】

この後、入力Aと入力B、入力Cと入力Dとでデータ交換をスイッチング回路20,21で、図12に示すように必要な部分で行う。データ交換を行った後、出力A、出力Cで入力で行った数の遅延を行い、出力のタイミングを調整し、出力する。

【0037】

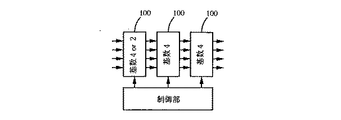

本発明ではすべての基本演算回路の基数を変更可能にすることで、2個の高速フーリエ変換を同時に実行することが可能になる。この場合の回路のブロック図を図14に、データの流れ図を図15に示す。この演算では、すべての基本演算回路100で基数を2として演算する。また、この場合のデータ並べ替え回路2は上記に示した基数2のときの動作と同じ動作を示すが、遅延素子6,8における遅延量は上記の場合の平方根をとった数となる。

【0038】

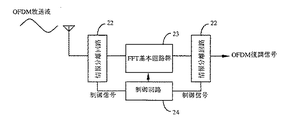

本発明の高速フーリエ変換回路をマルチキャリア直交周波数分割多重方式(OFDM)の受信機に用いた場合の構成を図16に示す。この場合、放送波の搬送波数Kは放送波からの信号により取り出すことができ、この情報は情報分離回路22で分離され、高速フーリエ変換回路の制御部24に送られる。この情報によりFFTの基本回路23に制御部24から制御信号が送られ、高速フーリエ変換回路の処理点数が変更される。このようにして、OFDMの搬送波数Kに対応した高速フーリエ変換点数N(N≧K)に瞬時に変更することが可能になる。

【0039】

上記実施形態においては、例として基数が4の場合の回路の構成方法について述べてきたが、これは基数Rを大きくしても同様の効果が得られ、ハードウェアの削減、高速化など新たな効果が期待できる。

【0040】

【発明の効果】

以上、説明したように、本発明の高速フーリエ変換演算回路は、処理するデータ点列数Nが基数Rに関係なくN/2、N/4、…と変更になっても同一の回路で高速フーリエ変換を行えるようにしたものである。この演算回路を用いることで、様々な点数の高速フーリエ変換にただ一つの回路で対応することができるようになったことが、本発明の最大の効果である。これにより、多様な入力数Nで高速フーリエ変換処理を必要とする場合に、単一のハードウェアで実現が可能となり、物量の削減等に効果を発揮できる。

【0041】

請求項1の発明では、様々な点数の高速フーリエ変換にただ1つの回路で対応することができる。請求項2の発明では、これまで複数個必要であったバタフライ演算回路を1個にすることができ、部品点数の削減に効果がある。請求項3の発明では、請求項2と同様にデータ並べ替え回路を1個にすることができ、部品点数の削減に効果がある。請求項4の発明では、後方の演算回路になんら影響を与えないので制御系統が簡略化される。請求項5の発明では、これまで同時に実行するには2個の演算回路が必要であったが、これを1個で行えることから、部品点数の削減、制御系統の簡略化の効果がある。

【図面の簡単な説明】

【図1】本発明の原理説明図である。

【図2】本発明の原理説明におけるバタフライ演算部のブロック図である。

【図3】本発明の原理説明におけるデータ並べ替え回路のブロック図である。

【図4】本発明の実施の形態の64点高速フーリエ変換回路のブロック図である。

【図5】本発明の実施の形態の64点高速フーリエ変換のデータの流れ図である。

【図6】本発明の実施の形態の32点高速フーリエ変換のデータの流れ図である。

【図7】本発明の実施の形態の16点高速フーリエ変換のデータの流れ図である。

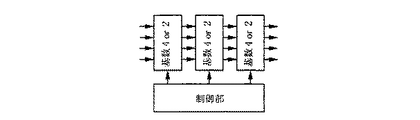

【図8】本発明の実施の形態の16〜16384点に対応した高速フーリエ変換演算回路である。

【図9】本発明の実施の形態の基数が2の時の動作である。

【図10】本発明の実施の形態の基数が4の時の動作である。

【図11】本発明の実施の形態の基数が2の時のデータ並べ替え回路の動作ブロック図である。

【図12】本発明の実施の形態の32点高速フーリエ変換におけるデータ並べ替え回路の動作説明図である。

【図13】従来の高速フーリエ変換を説明する図である。

【図14】本発明の他の実施の形態のすべての基本演算回路を変更可能にしたときの演算回路である。

【図15】本発明の他の実施の形態の2個の高速フーリエ変換を同時に実行したときのデータの流れ図である。

【図16】本発明の他の実施の形態のOFDM受信機における本発明の利用である。

【符号の説明】

100 高速フーリエ変換基本回路

1,10,12,14,15,17 バタフライ演算部

2,11,13,16,18 データ並べ替え回路

3 回転因子乗算部

4 複素加減算器

5 選択回路

6,7,8 遅延素子

9,20,21 スイッチ回路

19 複素乗算器

22 制御信号分離部

23 FFT基本回路群

24 高速フーリエ変換回路の制御部

Claims (5)

- 処理する高速フーリエ変換点数Nについて、高速フーリエ変換を行う回路であって、

バタフライ演算部1、回転因子乗算部3、データ並べ替え回路2からなるR入力の基本演算回路100を1段として、これをM個(=logRN)(Rは基数)直列に並べて高速フーリエ変換が行えるように構成し、

前記バタフライ演算部1では、上記R入力間で基数Rのたすき掛け演算を行い、

前記回転因子乗算部3では、バタフライ演算部2の出力のうちR−1個の出力に対して回転因子の乗算を行い、

前記データ並べ替え回路2では、上記入力データNに対し2段目以降の演算に必要となるデータの組を生成し、

さらに、外部からの制御信号により、前記バタフライ演算部1の基数が変更可能であり、

前記回転因子乗算部3、および前記データ並べ替え回路2を基数に応じて変更できる基本演算回路100を1個もしくは複数個備え、そのうち、1個もしくは複数個の基本演算回路100の基数を変更することで、上記高速フーリエ変換点数Nが基数Rに関わりなくN/2、N/4、…となっても同一の回路で高速フーリエ変換を行うことを特徴とする高速フーリエ変換演算回路。 - 前記請求項1に記載の高速フーリエ変換演算回路において、

バタフライ演算の途中経過を出力する信号線を備え、選択回路5により、前記信号線の信号とほかの計算結果が選択できるバタフライ演算部1を備え、外部からの信号により、基数の変更を可能にしたことを特徴とする高速フーリエ変換演算回路。 - 前記請求項1に記載の高速フーリエ変換演算回路において、

基本演算回路100におけるデータ並べ替え回路で、入力段に複数の遅延量が可変な遅延素子6,7,8を備え、基数に応じて切り替え状態を変更できるスイッチ回路9を備え、出力段に複数の遅延量が可変の遅延素子6,7,8を備え、外部からの制御信号に基づいて基数が変更に対応することが可能なデータ並べ替え回路を持つことを特徴とする高速フーリエ変換演算回路。 - 前記請求項1に記載の高速フーリエ変換演算回路において、

M段の基本演算回路100を直列に接続した回路は、前方からL段(L≦M)を基数が変更可能な基本演算回路であることを特徴とする高速フーリエ変換演算回路。 - 前記請求項1に記載の高速フーリエ変換演算回路において、

全ての基本演算回路100を基数が変更可能な演算回路とし、すべての基本演算回路100で基数をRより小さく、同一の値に設定し、前記データ並べ替え回路2は、遅延量を変更できる遅延素子6,8の遅延量を等しくし、外部からの制御信号に基づいてそれぞれ独立した入力データをフーリエ変換し出力することが可能であることを特徴とする高速フーリエ変換演算回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP08799997A JP3668356B2 (ja) | 1997-04-07 | 1997-04-07 | 高速フーリエ変換演算回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP08799997A JP3668356B2 (ja) | 1997-04-07 | 1997-04-07 | 高速フーリエ変換演算回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH10283341A JPH10283341A (ja) | 1998-10-23 |

| JP3668356B2 true JP3668356B2 (ja) | 2005-07-06 |

Family

ID=13930494

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP08799997A Expired - Lifetime JP3668356B2 (ja) | 1997-04-07 | 1997-04-07 | 高速フーリエ変換演算回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3668356B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100628303B1 (ko) * | 2004-09-03 | 2006-09-27 | 한국전자통신연구원 | 가변 포인트 ifft/fft 방법 및 장치 |

| US8229014B2 (en) | 2005-03-11 | 2012-07-24 | Qualcomm Incorporated | Fast fourier transform processing in an OFDM system |

| US8266196B2 (en) | 2005-03-11 | 2012-09-11 | Qualcomm Incorporated | Fast Fourier transform twiddle multiplication |

| JP4698394B2 (ja) | 2005-11-25 | 2011-06-08 | パナソニック株式会社 | 高速フーリエ変換回路 |

| KR101045713B1 (ko) * | 2006-04-28 | 2011-06-30 | 콸콤 인코포레이티드 | 멀티―포트 혼합―라딕스 fft |

| US9002919B2 (en) | 2009-09-24 | 2015-04-07 | Nec Corporation | Data rearranging circuit, variable delay circuit, fast fourier transform circuit, and data rearranging method |

| JP5556323B2 (ja) * | 2010-04-15 | 2014-07-23 | 日本電気株式会社 | データ並び替え回路に対する制御情報自動生成方法、データ並び替え回路、コンピュータ、及び制御情報自動生成プログラム |

| WO2014103235A1 (ja) * | 2012-12-25 | 2014-07-03 | 日本電気株式会社 | 演算装置及び演算方法 |

| WO2014104520A1 (ko) * | 2012-12-27 | 2014-07-03 | 전자부품연구원 | 변환 방법, 연산 방법 및 이를 적용한 hevc 시스템 |

| US20200372095A1 (en) | 2017-08-07 | 2020-11-26 | Nec Corporation | Fast fourier transform device, data sorting processing device, fast fourier transform processing method, and program recording medium |

| JP7086321B2 (ja) * | 2020-04-14 | 2022-06-17 | 三菱電機株式会社 | 周波数解析装置、周波数解析方法、制御回路および記憶媒体 |

-

1997

- 1997-04-07 JP JP08799997A patent/JP3668356B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JPH10283341A (ja) | 1998-10-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100551111B1 (ko) | 파이프라인 고속 푸리에 변환 프로세서 | |

| US5717620A (en) | Improved-accuracy fast-Fourier-transform butterfly circuit | |

| JP3668356B2 (ja) | 高速フーリエ変換演算回路 | |

| US20050047325A1 (en) | Combined inverse fast fourier transform and guard interval processing for efficient implementation of OFDM based systems | |

| WO2007115329A2 (en) | Pipeline fft architecture and method | |

| US4646256A (en) | Computer and method for the discrete bracewell transform | |

| US5270953A (en) | Fast convolution multiplier | |

| EP0944005A1 (en) | Arithmetic unit and method for fourier transform | |

| US3777131A (en) | High base multiple rail fourier transform serial stage | |

| KR20090127462A (ko) | Fft/ifft 연산코어 | |

| CA2269464A1 (en) | A device and method for calculating fft | |

| JPH06243161A (ja) | 離散余弦変換回路 | |

| US6157938A (en) | Fast fourier transform device with parallel lattice architecture | |

| US8010588B2 (en) | Optimized multi-mode DFT implementation | |

| US20020165683A1 (en) | Fast fourier transform apparatus | |

| KR100836624B1 (ko) | 가변 고속 푸리에 변환 장치 및 그 방법 | |

| JPH08320858A (ja) | フーリエ変換演算装置および方法 | |

| KR100602272B1 (ko) | 고속으로 데이터를 처리하는 고속 퓨리에 변환 장치 및 방법 | |

| JPH10307811A (ja) | 演算装置および演算方法 | |

| KR101334494B1 (ko) | 고속 저 복잡도의 Radix 2의 5승 고속 푸리에 변환 장치 및 방법 | |

| JP3727406B2 (ja) | 関数変換演算器 | |

| KR100576520B1 (ko) | 반복 연산 기법을 이용한 가변 고속 푸리에 변환프로세서 | |

| EP0484944B1 (en) | Vector calculation apparatus capable of rapidly carrying out vector calculation of two input vectors | |

| KR20120109214A (ko) | Ofdm 시스템에서의 고속 푸리에 변환 프로세서 및 그 고속 푸리에 변환방법 | |

| KR101711783B1 (ko) | 이중 경로 공유 기법을 이용한 고속 저 복잡도의 혼합 기수 고속 푸리에 변환 장치 및 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040210 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20050208 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050303 |

|

| A911 | Transfer of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20050308 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050329 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050408 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313114 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080415 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080415 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090415 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090415 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100415 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100415 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110415 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110415 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120415 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130415 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140415 Year of fee payment: 9 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |