JP3649828B2 - ヘテロ接合バイポーラトランジスタの等価回路モデルの作成方法および回路のシミュレータ - Google Patents

ヘテロ接合バイポーラトランジスタの等価回路モデルの作成方法および回路のシミュレータ Download PDFInfo

- Publication number

- JP3649828B2 JP3649828B2 JP31988796A JP31988796A JP3649828B2 JP 3649828 B2 JP3649828 B2 JP 3649828B2 JP 31988796 A JP31988796 A JP 31988796A JP 31988796 A JP31988796 A JP 31988796A JP 3649828 B2 JP3649828 B2 JP 3649828B2

- Authority

- JP

- Japan

- Prior art keywords

- equivalent circuit

- model

- current

- circuit model

- hbt

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Bipolar Transistors (AREA)

Description

【発明の属する技術分野】

本発明は半導体デバイスの等価回路モデルの作成方法に関し、特に自己発熱効果を取り入れたヘテロ接合バイポーラトランジスタ(以下「HBT」という。)の等価回路モデルの作成方法およびHBTを含む回路のシミュレータに関する。

【0002】

【従来の技術】

半導体デバイスの特性を表現する等価回路モデルを用いることにより、半導体回路の設計を開始させることができ、一方半導体デバイスの開発に軌道修正をかけることも可能になる。すなわち、等価回路モデルを使用したシミュレーションにより半導体回路設計に必要な物理的パラメータを得て設計を開始することができる。一方、既に設計製作したデバイスの特性の実測値とシミュレーションの計算値とからフィッティングされたパラメータに基づいて半導体デバイスの設計を修正し、再度デバイスを製作することもできる。

【0003】

HBTの等価回路モデルとしては、特開平6−266789号公報に開示されているように、ガンメルプーンモデルが広く使用されている。ガンメルプーンモデルは、HBTの等価回路を形成する各種素子(抵抗、容量)の値を示す多数のパラメータを含んでおり、それらにより形成される。

【0004】

GaAs HBTは高周波パワー素子として研究、開発が進められているが、GaAs基板は熱抵抗が高い。このためデバイスの自己発熱がデバイス特性に与える影響を無視できなくなる。

【0005】

図10を参照して、エミッタ接地のGaAs HBTの特性を説明する。ベース電流Ibが一定の場合に、エミッタ−コレクタ電圧Vceの増加とともに、コレクタ電流Icの低下、すなわち電流利得の低下が観測される。またコレクタ電流Icが大きいほど電流利得の低下が顕著になる。したがって高周波パワー素子であるGaAs HBTのシミュレーションにおいては、電流利得の低下を表現するため、自己発熱効果を取り入れた等価回路モデルを使用することが不可欠である。

【0006】

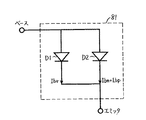

以下従来のHBT等価回路モデルについて説明する。図11および図12を参照して、HBT等価回路モデル80は、ダイオードモデル部81を含む。ダイオードモデル部81は、ダイオードモデルD1とダイオードモデルD2とを含む。従来のダイオードモデル部81においては、ダイオードモデルD1は再結合電流Ibrを表わし、ダイオードモデルD2は電子注入電流Ibnとホール注入電流Ibpとの和、すなわちIbn+Ibpを表わす。

【0007】

以下、自己発熱効果による利得低下のメカニズムについて説明する。npn型のHBTにおいて、ベース電流Ibは、

Ib=Ibr+Ibn+Ibp (1)

で表わされる。ただし、

Ibr:エミッタ接合の空乏層中の再結合電流

Ibn:エミッタからベースへの電子注入電流

Ibp:ベースからエミッタへのホール注入電流

である。

【0008】

「Procedings of IEEE、1982年1月、第70巻第1号、13頁〜25頁」に開示されているように、電子注入電流Ibnとホール注入電流Ibpとはそれぞれ下記の式(2)と式(3)で表わされる。

【0009】

Ibn=Ne・vnb・exp(qVn/kT)/β0 (2)

Ibp=Pb・vpe・exp(−qVp/kT) (3)

ここで、

β0:ベース輸送効率によるエミッタ接地電流利得

Ne:エミッタ中のドーピングレベル

Pb:ベース中のドーピングレベル

vnb:ベース中の電子の平均速度

vpe:エミッタ中のホールの平均速度

である。

【0010】

図13を参照して、エミッタに広い禁制帯幅の半導体を用い、ベースに狭い禁制帯幅の半導体を用いるHBTの場合に、エミッタ接合のエネルギバンド構造を示す。図13からわかるように、エミッタからベースへの電子に対する障壁qVnに比べて、ベースからエミッタへのホールに対する障壁qVpが高い。さらに、式(2)、式(3)からわかるように、障壁が高いほど、温度変化による電流の変化が大きい。したがって電子注入電流とホール注入電流とが各々異なった温度特性をもっており、電子注入電流に比べてホール注入電流が温度変化の影響を受けやすい。その結果、電子電流とホール電流の割合は温度に依存することになる。

【0011】

しかし、従来のダイオードモデル部81によっては、温度変化による電子注入電流とホール注入電流の割合の変化を表現することができない。

【0012】

上記のようにガンメルプーンモデルは自己発熱効果を取り入れていないので、図10に示した電流利得の低下を表現することができない。このため従来では以下の方法により、自己発熱効果を取り入れたHBT特性のシミュレーションを行なっていた。

【0013】

たとえば「IEEE Trans. 、Microwave Theory and Techniques 、1992年3月、第40巻第3号、449 頁〜464 頁」および「IEEE Trans. 、Microwave Theory and Techniques 、1995年7月、第43巻第7号、1433頁〜1445頁」に開示されているように、ガンメルプーンモデルを構成する各々の素子に温度依存性を持たせ、その消費電力からHBTの温度上昇を計算し、その温度上昇を考慮した各素子の特性を表わすパラメータを算出し、この変化したパラメータを用いて等価回路の動作をシミュレーションする。

【0014】

【発明が解決しようとする課題】

しかしながら上記の従来の自己発熱効果を取り入れたHBT特性のシミュレーション方法においては、各素子に温度特性を持たせるために、多数の新たなパラメータが必要である。このためパラメータの個数が多いほどモデルの構築のためのパラメータの抽出に多くの労力と時間を要し、シミュレーション結果の信頼性が低下する恐れがある。さらにシミュレーションの結果を利用してデバイスの設計、製作に軌道修正をかけることも困難である。

【0015】

本発明は係る課題を解決するためになされたものであり、請求項1に記載の発明の目的は、自己発熱効果を含めたHBTの特性を精度よく表現する等価回路モデルを、少数のパラメータで作成することができるHBTの等価回路モデルの作成方法を提供することにある。

【0017】

請求項2に記載の発明の目的は、HBTのベース電流を、ベース電流中の電子注入電流を表わすダイオードモデルと、ベース電流中のホール注入電流を表わすダイオードモデルとを含むダイオードモデルで表わすHBTの等価回路モデルの作成方法を提供することにある。

【0018】

請求項3に記載の発明の目的は、請求項1に記載の発明の目的に加え、HBTのベース電流を、ベース電流中の電子注入電流を表わすダイオードモデルと、ベース電流中のホール注入電流を表わすダイオードモデルとを含むダイオードモデルで表わすHBTの等価回路モデルを、短時間で作成することのできるHBTの等価回路モデルの作成方法を提供することにある。

【0019】

請求項4に記載の発明の目的は、自己発熱効果を含めたHBTの特性を精度よくシミュレーションすることのできる回路シミュレータを提供することにある。

【0020】

【課題を解決するための手段】

請求項1に記載の発明に係るHBTの等価回路モデルの作成方法は、HBTのベース電流を、ベース電流中の電子注入電流Ibnを表わす第1のダイオードモデルと、ベース電流中のホール注入電流Ibpを表わす第2のダイオードモデルとを含むダイオードモデルで表わすことにより得られるHBTの等価回路モデルを準備するステップを含む。前記第2のダイオードモデルは以下の式で定義される。

【0021】

Ibp=C・Ibn・exp[−ΔE/k(Ta+Rth・Ic・Vce)]

ただし、

Ibn:ベース電流中の電子注入電流

Ibp:ベース電流中のホール注入電流

Ta:周囲温度

Ic:コレクタ電流

Vce:エミッタ・コレクタ電圧

C,ΔE,Rth:フィッティングパラメータ

k:ボルツマン定数

本方法はさらに、前記等価回路モデル内のパラメータをフィッティングにより定めるフィッティングステップを含む。

【0022】

請求項1に記載の発明によれば、HBTのベース電流を、ベース電流中の電子注入電流Ibnを表わす第1のダイオードモデルと、ベース電流中のホール注入電流Ibpを表わす第2のダイオードモデルとを含むダイオードモデルで表わすことにより得られるHBTの等価回路モデルが準備される。第2のダイオードモデルは所定の式で定義され、等価回路モデル内のパラメータがフィッティングにより定められる。

【0023】

したがってRth、ΔE、およびCという3個のパラメータをフィッティングで定めるだけで、HBTの等価回路モデルを作成することができる。このため少数のパラメータで自己発熱効果を取り入れたHBTの特性を精度よく表現する等価回路モデルを作成することができる。

【0025】

請求項2に記載の発明に係るHBTの等価回路モデルの作成方法は、請求項1に記載の発明の構成に加えて、前記フィッティングステップは、前記等価回路モデルの各フィッティングパラメータに初期値を設定するステップと、前記各フィッティングパラメータに与えられた値に従って前記等価回路モデルの回路シミュレーションを行なって、前記等価回路モデルの特性値を計算するシミュレーションステップと、前記回路シミュレーションにより得られた特性値と、予め準備された、実測されたHBTの特性値との相違を表わす予め定める尺度を計算するステップと、前記尺度が予め定める条件を満たすまで、各フィッティングパラメータに与えられた値を変化させながら前記シミュレーションステップと前記尺度を計算するステップとを繰返し行なうステップと、前記繰返し行なうステップの終了時に得られたフィッティングパラメータの値の組を、前記一般的な等価回路モデルに適用することにより、前記HBTの等価回路モデルを作成するステップとを含む。

【0026】

請求項2に記載の発明によれば、初期値を設定するステップで、等価回路モデルの各フィッティングパラメータに初期値を設定し、シミュレーションステップで、各フィッティングパラメータに与えられた値に従って等価回路モデルの回路シミュレーションを行なって、等価回路モデルの特性値を計算する。尺度を計算するステップにおいては、回路シミュレーションにより得られた特性値と予め準備された、実測されたHBTの特性値との相違を表わす予め定める尺度を計算する。この尺度が予め定める条件を満たすまで、各フィッティングパラメータに与えられた値を変化させながらシミュレーションステップと前記尺度を計算するステップとが繰返し実行される。繰返し行なうステップの終了時に得られたフィッティングパラメータの値の組が、一般的な等価回路モデルに適用されることにより、HBTの等価回路モデルが作成される。

【0027】

こうして計算された特性値と実測された特性値とからフィッティングされたパラメータの値が、一般的な等価回路に適用されてあるHBTの等価回路モデルが作成される。このためHBTのベース電流をベース電流中の電子注入電流を表わすダイオードモデルと、ベース電流中のホール注入電流を表わすダイオードモデルとを含むダイオードモデルで表わすHBTの一般的な等価回路モデルから特定のHBTに適合したHBTの等価回路モデルを作成することができる。

【0028】

請求項3に記載の発明は、請求項1に記載の発明であって、前記初期値を設定するステップにおいて、前記パラメータCに対して、C=β0(Ne/Pb)(vnb/vpe)

ただし、Ne:エミッタ中のドーピングレベルPb:ベース中のドーピングレベルvnb:ベース中の電子の平均速度vpe:エミッタ中のホールの平均速度β0:ベース輸送効率によるエミッタ接地電流利得なる式を適用することにより得られる値が初期値として設定されることを特徴とする。

【0029】

請求項3に記載の発明によれば、初期値を設定するステップは、パラメータCに対して、上式を適用することにより得られる値を初期値として設定する。

【0030】

したがってHBTのメカニズムに密着し、明確な物理的意味を持ち、かつその値が既に知られているか、少なくともオーダー程度は知られているパラメータから算出されたフィッティングパラメータCの値が初期値として与えられる。このため繰返しステップは実測された特性値に近い特性値を初期値として開始される。この結果尺度が予め定める条件を満たすまで、繰返し回数が少なくなり、短時間でHBTの等価回路モデルを作成することができる。また正しい収束値ではない局所的な収束値に収束する恐れも少なくなる。

【0031】

請求項4に記載の発明は、ヘテロ接合バイポーラトランジスタの等価回路モデルを用いる回路シミュレータにおいて、前記等価回路は、ヘテロ接合バイポーラトランジスタのベース電流を、ベース電流中の電子注入電流Ibnを表わす第1のダイオードモデルと、ベース電流中のホール注入電流Ibpを表わす第2のダイオードモデルとを含むダイオードモデルで表わすことにより得られる等価回路モデルである。

【0032】

前記第2のダイオードモデルは、

Ibp=C・Ibn・exp[−ΔE/k(Ta+Rth・Ic・Vce)]

ただし、

Ibn:ベース電流中の電子注入電流

Ibp:ベース電流中のホール注入電流

Ta:周囲温度Ic:コレクタ電流

Vce:エミッタ・コレクタ電圧

C,ΔE,Rth:フィッティングパラメータ

k:ボルツマン定数、という前記ホール注入電流Ibpの式で表される。

【0033】

請求項4に記載の発明によれば、HBTのベース電流を、ベース電流中の電子注入電流Ibnを表わす第1のダイオードモデルと、ベース電流中のホール注入電流Ibpを表わす第2のダイオードモデルとを含むダイオードモデルで表わすことにより得られるHBTの等価回路モデルが準備される。第2のダイオードモデルは自己発熱を精度よく、かつ少ないパラメータしか用いない所定の式で定義される。等価回路モデル内のパラメータがフィッティングにより定められ、HBTの等価回路が作成される。さらに、シミュレーション対象の回路の等価回路は回路シミュレータを用いてシミュレーションされる。

【0034】

ベース電流中の電子注入電流Ibnを表わす第1のダイオードモデルと、ベース電流中のホール注入電流Ibpを表わす第2のダイオードモデルとを含むダイオードモデルで表わすことにより得られるHBTの等価回路モデルでは、自己発熱の影響がより精度よく表わされ、かつ少ないパラメータしか必要としない。パラメータは効率よく抽出でき、そのパラメータを用いて作成された等価回路を含む回路が回路シミュレータでシミュレーションされる。このため自己発熱効果を取り入れたHBTを含む回路の特性を精度よくシミュレーションすることができる。

【0038】

【発明の実施の形態】

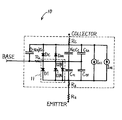

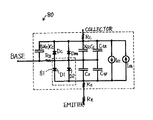

以下本願発明の実施の形態を図面を参照して説明する。図1および図2を参照して、HBT等価回路モデル10はダイオードモデル部11を含む。ダイオードモデル部11は、ダイオードモデルD1とダイオードモデルD2AとダイオードモデルD2Bとを含む。本実施の形態のHBT等価回路モデル10の特徴は、ダイオードモデル部11において、ベース電流Ibのうち、ダイオードモデルD1が再結合電流Ibrを表わし、ダイオードモデルD2Aが電子注入電流Ibnを表わし、ダイオードモデルD2Bがホール注入電流Ibpを表わすことにある。

【0039】

ダイオードモデルD2Bで表わされたホール注入電流Ibpは下記の式により定義される。

【0040】

Ibp=C・Ibn・exp[−ΔE/k(Ta+Rth・Ic・Vce)]

ただし、

Ibn:ベース電流中の電子注入電流

Ibp:ベース電流中のホール注入電流

Ta:周囲温度

Ic:コレクタ電流

Vce:エミッタ・コレクタ電圧

Rth:熱抵抗

ΔE:エミッタ接合界面におけるホール注入電流に対する障壁と電子注入電流に対する障壁との差

C:ΔE=0の場合のベース電流中のホール注入電流と電子注入電流との比

k:ボルツマン定数

上記値のうち、Rth,C,ΔEはフィッティングパラメータである。

【0041】

またフィッティングパラメータCは下記の式のように定義される。

C=β0(Ne/Pb)(vnb/vpe)

ただし、

Ne:エミッタ中のドーピングレベル

Pb:ベース中のドーピングレベル

vnb:ベース中の電子の平均速度

vpe:エミッタ中のホールの平均速度

β0:ベース輸送効率によるエミッタ接地電流利得

これら値のうち、Ne,Pb,β0の値は予め知ることができる。また、vnb/vpeの正確な値はわからないが、そのオーダー程度であれば予め知ることができる。

【0042】

このように、2つの異なった温度特性を有するダイオードモデルD2Aと、ダイオードモデルD2Bとを用いることにより、電子注入電流Ibnとホール注入電流Ibpとの割合による温度の依存特性を表現することができる。その結果、ガンメルプーンモデルをベースに、3つのパラメータC、ΔE、およびRthを新たに導入するのみで、精度よく電流利得の低下を表現することができる。また導入された3つのパラメータΔE、Rth、およびCは物理的な意味を持っている。したがってパラメータフィッティングにより、ΔE、Rth、およびCの値を抽出することにより、デバイス設計に対してフィードバックをかけることもできる。

【0043】

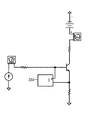

図3を参照して、回路シミュレータを用いて構築された本実施の形態の等価回路モデルについて説明する。回路シミュレータのシンボル定義がなされたデバイスSDDを用いて、

Ibp=C・Ibn・exp[−ΔE/k(Ta+Rth・Ic・Vce)]で定義されたダイオードを構築し、さらに得られたダイオードを回路シミュレータに組込まれたガンメルプーンモデルのベース/エミッタの間に挿入するだけで、電流利得の低下を表現することができる等価回路モデルを構築することができる。

【0044】

図4を参照して、GaInP/GaAs HBTのI/V特性の測定値と本実施の形態の等価回路モデルによる計算値との比較結果について説明する。図4に示されているように、コレクタ電流Icの測定値と計算値とはよく一致している。

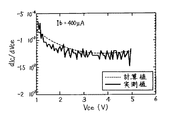

【0045】

図5を参照して、コレクタ電流Icの測定値と計算値との電圧に対する微分、すなわち出力コンダクタンスについて説明する。等価回路モデルを用いてパワーアンプを設計する場合においては、等価回路モデルによるコレクタ電流の表現だけではなく出力コンダクタンスの表現も重要である。図5に示されているように、出力コンダクタンスの測定値と計算値とはかなり一致している。

【0046】

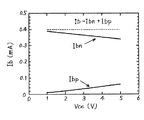

図6を参照して、ベース電流中の電子注入電流とホール注入電流の電圧依存性について説明する。HBTにおいて、トータルのベース電流Ibを測定することはできるが、ベース電流Ib中の電子注入電流Ibnとホール注入電流Ibpとを分離することは難しい。このため電子注入電流Ibnとホール注入電流Ibpとの割合はデバイスの解析にあたって重要であるにもかかわらず、それに関する測定結果はほとんど報告されていない。本実施の形態に係る等価回路モデルを用いることにより、従来分離することができなかった電子注入電流Ibnとホール注入電流Ibpとをそれぞれ計算することができる。さらに本実施の形態に係る等価回路モデルを構築する際に、HBTの回路特性の実測値から、抽出されたフィッティングパラメータC、Rth、およびΔEを本実施の形態の等価回路モデルに適用することにより、HBTを設計製作するための修正されたプロセス変数を得て、半導体デバイスの解析と開発に対してフィードバックをかけることもできる。

【0047】

図7を参照して、本実施の形態に係るHBTの等価回路モデルを作成する方法の手順を説明する。まずガンメルプーンモデルにおいて、HBTのベース電流を、ベース電流中の電子注入電流Ibnを表わす第1のダイオードモデルと、ベース電流中のホール注入電流Ibpを表わす第2のダイオードモデルとを含むダイオードモデルで表わすことにより得られるHBTの一般的な等価回路モデルが準備される(S701)。次に等価回路モデルの各フィッティングパラメータに初期値が設定される(S702)。ここで、既に述べたようにパラメータCの初期値として、β0、Ne、Pb、vnb、vpeを用いて真の値に近いと思われる値を設定でき、以後の繰り返しにおける収束を良くすることができる。また誤った局所的最小値を解としてしまうおそれも減少する。次に各フィッティングパラメータに与えられた値に従って等価回路モデルの回路シミュレーションを行なって等価回路モデルの特性値が計算される(S703)。次に回路シミュレーションにより得られた特性値と、予め準備された、実測されたHBTの特性値との相違を表わす予め定められた尺度が計算される(S704)。この尺度の計算としては、たとえば実測値と計算値との差の最小二乗法などが用いられる。次に計算された尺度が予め定められた条件を満たすか否かが判断される(S705)。

【0048】

計算された尺度が予め定められた条件を満たしていないと判断された場合には、各フィッティングパラメータに与えられた値が変更される(S706)。次に特性値を計算するシミュレーションステップ(S703)と実測値との相違を表わす尺度を計算するステップ(S704)が繰返し実行される。

【0049】

一方計算された尺度が予め定められた条件を満たしていると判断された場合には、得られたフィッティングパラメータの値の組が、一般的な等価回路モデルに適用される。これにより特定のHBTの等価回路モデルが作成される(S707)。次に本手順は終了する。

【0050】

図8を参照して、本実施の形態に係るHBTの開発方法の手順について説明する。まず予め与えられた物理的パラメータを実現すべく定められたプロセス変数を用いてHBTが作成される(S801)。次に作成されたHBTの回路特性が測定される(S802)。次にガンメルプーンモデルにおいて、HBTのベース電流を、ベース電流中のベース注入電流Ibnを表わす第1のダイオードモデルと、ベース電流中のホール注入電流Ibpを表わす第2のダイオードモデルとを含むダイオードモデルで表わす変更を行なうことにより得られるHBTの一般的な等価回路モデルが準備される(S803)。次に等価回路モデル内のパラメータが、HBTの回路特性の測定値を用いたフィッティングにより定められる(S804)。次にフィッティングにより決定されたパラメータの値から、HBTの物理的パラメータの値が推定される(S805)。次に、推定された物理的パラメータの値に基づいて、プロセス変数のうちの少なくとも1つの値を変化させるべきか否かの判定が行なわれる(S806)。

【0051】

プロセス変数のうちの少なくとも1つの値を変化させるべきであると判定された場合には、推定されたパラメータに基づいて変化させたプロセス変数を用いて、再度HBTが作成され、以上の手順が再度繰り返される(S801)。

【0052】

一方いずれのプロセス変数も変化させるべきではないと判定された場合には本手順は終了する。

【0053】

なお図7で説明したHBTの等価回路モデルを作成する方法の手順は、図8のHBTの開発方法の手順においては、一般的な等価回路モデルを準備するステップ(S803)、およびパラメータフィッティングのステップ(S804)に相当する。

【0054】

図9を参照して、本実施の形態に係るHBTを含む回路のシミュレーション方法の手順について説明する。まずシミュレーション対象の回路の等価回路が準備される(S901)。次にこの等価回路内のHBTを含む等価回路モデルのパラメータをパラメータフィッティングにより定めることにより特定のシミュレーション対象の回路の等価回路が作成される(S902)。次にシミュレーション対象の回路の等価回路が回路シミュレータによりシミュレーションされる(S903)。次に本手順は終了する。

【0055】

なお図7で説明した、HBTの等価回路モデルを作成する方法の手順は、図9のHBTを含む回路のシミュレーション方法においては、等価回路モデルを作成するステップ(S902)に該当する。

【0056】

以上のように本実施の形態によれば、HBTのベース電流中の電子注入電流とホール注入電流との異なる温度依存性に注目し、異なる温度特性を持つ2つのダイオードモデルを用いて電子注入電流とホール注入電流を各々表わすこととしている。したがって熱抵抗Rth、エミッタ接合界面におけるホール注入電流に対する障壁と電子注入電流に対する障壁との差ΔE、およびΔE=0の場合のベース電流中のホール注入電流と電子注入電流との比Cという、物理的な意味を持つ3個のパラメータをガンメルプーンモデルに導入するのみで、HBTの等価回路モデルを作成することができる。このため少数のパラメータで自己発熱効果を取り入れたHBTの特性を精度よく表現できる等価回路モデルを作成することができる。

【0057】

また計算された特性値と実測された特定値とからフィッティングされたパラメータの値が一般的な等価回路モデルに適用されるため、HBTのベース電流をベース電流中の電子注入電流を表わすダイオードモデルと、ベース電流中のホール注入電流を表わすダイオードモデルとを含むダイオードモデルで表わすHBTの一般的な等価回路モデルから、HBTの等価回路モデルを作成することができる。

【0058】

またHBTのメカニズムに密着し、明確な物理的意味を持つパラメータから算出されたフィッティングパラメータCの値が初期値として与えられるため、繰返しステップは実測された特性値に近い特性値が計算されるステップから開始される。この結果尺度が予め定める条件を満たすまで繰返しを行なう回数が少なくなり、短時間でHBTの等価回路モデルを作成することができる。

【0059】

さらに測定されたHBTの回路特性に基づき、等価回路モデル内のパラメータのフィッティングの結果に従って、再度HBTを作製することができる。このため効率よくHBTを開発することができる。

【0060】

またHBTのベース電流を電子注入電流とホール注入電流とで表現した一般的な等価回路モデル内のパラメータをフィッティングにより定めることができる。こうして作成された等価回路モデルが、回路シミュレータでシミュレーションされる。このため自己発熱効果を取り入れたHBTの特性を精度よくシミュレーションすることができる。

【図面の簡単な説明】

【図1】本実施の形態に係るHBT等価回路モデルの全体構成図である。

【図2】本実施の形態に係るHBT等価回路モデルの要部の説明図である。

【図3】本実施の形態に係るシミュレータを用いて構成されたHBT等価回路モデルの説明図である。

【図4】本実施の形態に係るHBTの出力電流電圧特性の測定値と等価回路モデルによる計算値とを比較するためのグラフ図である。

【図5】本実施の形態に係るGaAs HBTの出力コンダクタンスの測定値と等価回路モデルによる計算値とを比較するためのグラフ図である。

【図6】GaAs HBTのベース電流中の電子注入電流とホール注入電流との割合の電圧依存性を示すグラフ図である。

【図7】本実施の形態に係るHBTの等価回路モデルを作成する方法の手順を示すフローチャートである。

【図8】本実施の形態に係るHBTの開発方法の手順を示すフローチャートである。

【図9】本実施の形態に係るHBTを含む回路のシミュレーション方法の手順を示すフローチャートである。

【図10】GaAs HBTの出力電流電圧特性の測定値を示すグラフ図である。

【図11】従来のHBT等価回路モデルの全体構成図である。

【図12】従来のHBT等価回路モデルの要部の説明図である。

【図13】HBTのエミッタ接合のエネルギバンド構造の説明図である。

【符号の説明】

10 HBT等価回路モデル

11 ダイオードモデル部

D1、D2、D2A、D2B ダイオードモデル

Claims (4)

- ヘテロ接合バイポーラトランジスタの等価回路モデルの作成方法において、

ヘテロ接合バイポーラトランジスタのベース電流を、ベース電流中の電子注入電流Ibnを表わす第1のダイオードモデルと、ベース電流中のホール注入電流Ibpを表わす第2のダイオードモデルとを含むダイオードモデルで表わすことにより得られるヘテロ接合バイポーラトランジスタの等価回路モデルを準備するステップを備え、

前記第2のダイオードモデルは以下の式で定義され、

Ibp=C・Ibn・exp[−ΔE/k(Ta+Rth・Ic・Vce)]

ただし、Ibn:ベース電流中の電子注入電流

Ibp:ベース電流中のホール注入電流

Ta:周囲温度

Ic:コレクタ電流

Vce:エミッタ・コレクタ電圧

C,ΔE,Rth:フィッティングパラメータ

k:ボルツマン定数

前記等価回路モデル内のパラメータをフィッティングにより定めるフィッティングステップをさらに備える、ヘテロ接合バイポーラトランジスタの等価回路モデルの作成方法。 - 前記フィッティングステップは、

前記等価回路モデルの各フィッティングパラメータに初期値を設定するステップと、

前記各フィッティングパラメータに与えられた値に従って前記等価回路モデルの回路シミュレーションを行なって、前記等価回路モデルの特性値を計算するシミュレーションステップと、

前記回路シミュレーションにより得られた特性値と、予め準備された、実測されたHBTの特性値との相違を表わす予め定める尺度を計算するステップと、

前記尺度が予め定める条件を満たすまで、各フィッティングパラメータに与えられた値を変化させながら前記シミュレーションステップと前記尺度を計算するステップとを繰返し行なうステップと、

前記繰返し行なうステップの終了時に得られたフィッティングパラメータの値の組を、前記等価回路モデルに適用することにより、前記ヘテロ接合バイポーラトランジスタの等価回路モデルを作成するステップとを含む、請求項1に記載のヘテロ接合バイポーラトランジスタの等価回路モデルの作成方法。 - 前記初期値を設定するステップにおいて、前記パラメータCに対して、C=β0(Ne/Pb)(vnb/vpe)

ただし、Ne:エミッタ中のドーピングレベル

Pb:ベース中のドーピングレベル

vnb:ベース中の電子の平均速度

vpe:エミッタ中のホールの平均速度

β0:ベース輸送効率によるエミッタ接地電流利得なる式を適用することにより得られる値が初期値として設定される、請求項1に記載のヘテロ接合バイポーラトランジスタの等価回路モデルの作成方法。 - ヘテロ接合バイポーラトランジスタの等価回路モデルを用いる回路シミュレータにおいて、

前記等価回路は、ヘテロ接合バイポーラトランジスタのベース電流を、

ベース電流中の電子注入電流Ibnを表わす第1のダイオードモデルと、

ベース電流中のホール注入電流Ibpを表わす第2のダイオードモデルとを含むダイオードモデルで表わすことにより得られる等価回路モデルであり、

前記第2のダイオードモデルは、

Ibp=C・Ibn・exp[−ΔE/k(Ta+Rth・Ic・Vce)]

ただし、Ibn:ベース電流中の電子注入電流

Ibp:ベース電流中のホール注入電流

Ta:周囲温度Ic:コレクタ電流

Vce:エミッタ・コレクタ電圧

C,ΔE,Rth:フィッティングパラメータ

k:ボルツマン定数

という前記ホール注入電流Ibpの式で表されることを特徴とする、回路シミュレータ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP31988796A JP3649828B2 (ja) | 1996-11-29 | 1996-11-29 | ヘテロ接合バイポーラトランジスタの等価回路モデルの作成方法および回路のシミュレータ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP31988796A JP3649828B2 (ja) | 1996-11-29 | 1996-11-29 | ヘテロ接合バイポーラトランジスタの等価回路モデルの作成方法および回路のシミュレータ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JPH10163222A JPH10163222A (ja) | 1998-06-19 |

| JPH10163222A5 JPH10163222A5 (ja) | 2004-11-18 |

| JP3649828B2 true JP3649828B2 (ja) | 2005-05-18 |

Family

ID=18115353

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP31988796A Expired - Fee Related JP3649828B2 (ja) | 1996-11-29 | 1996-11-29 | ヘテロ接合バイポーラトランジスタの等価回路モデルの作成方法および回路のシミュレータ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3649828B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8745569B2 (en) | 2011-06-23 | 2014-06-03 | Panasonic Corporation | Equivalent circuit of bidirectional switch, simulation method for bidirectional switch, and simulation device for bidirectional switch |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20030083889A (ko) * | 2002-04-23 | 2003-11-01 | 엘지전자 주식회사 | 이종접합 바이폴라 트랜지스터의 소신호 모델 자동 추출방법 |

| CN116314174B (zh) * | 2022-09-09 | 2023-11-24 | 燕山大学 | 锗硅异质结双极晶体管低温大信号等效电路模型 |

-

1996

- 1996-11-29 JP JP31988796A patent/JP3649828B2/ja not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8745569B2 (en) | 2011-06-23 | 2014-06-03 | Panasonic Corporation | Equivalent circuit of bidirectional switch, simulation method for bidirectional switch, and simulation device for bidirectional switch |

Also Published As

| Publication number | Publication date |

|---|---|

| JPH10163222A (ja) | 1998-06-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| Rinaldi | Small-signal operation of semiconductor devices including self-heating, with application to thermal characterization and instability analysis | |

| Shi et al. | Compact representation and efficient generation of s-expanded symbolic network functions for computer-aided analog circuit design | |

| JP3660137B2 (ja) | シミュレーション方法、シミュレータ、シミュレーションプログラムを記録した記録媒体および半導体装置の製造方法 | |

| CN113221298A (zh) | 一种机电暂态过程的仿真方法及系统 | |

| Balanethiram et al. | Accurate modeling of thermal resistance for on-wafer SiGe HBTs using average thermal conductivity | |

| Schroter et al. | A computationally efficient physics-based compact bipolar transistor model for circuit design-Part I: Model formulation | |

| JP3649828B2 (ja) | ヘテロ接合バイポーラトランジスタの等価回路モデルの作成方法および回路のシミュレータ | |

| Huszka et al. | Extraction of compact static thermal model parameters for SiGe HBTs | |

| CN101201850B (zh) | 双极结型晶体管spice模型的建模方法 | |

| Jaoul et al. | Avalanche compact model featuring SiGe HBTs characteristics up to BVcbo | |

| US20040073879A1 (en) | Modeling devices in consideration of process fluctuations | |

| JP4286924B2 (ja) | 半導体装置の製造方法、半導体装置の特性評価装置、半導体装置の特性評価方法、及び、半導体装置の特性評価プログラムを記録した機械読み取り可能な記録媒体 | |

| Mazeau et al. | Behavioral thermal modeling for microwave power amplifier design | |

| Sommet et al. | From 3D thermal simulation of HBT devices to their thermal model integration into circuit simulators via Ritz vectors reduction technique | |

| Schröter et al. | Why is there no internal collector resistance in HICUM? | |

| US20060100830A1 (en) | Moment computations of nonuniform distributed coupled RLC trees with applications to estimating crosstalk noise | |

| JPH10163222A5 (ja) | ||

| JPH08327698A (ja) | 回路シミュレーション方法及びその装置 | |

| Scognamillo et al. | Improved nonlinear electrothermal simulation of bipolar transistors: Application to InP/InGaAs DHBTs | |

| JP3214108B2 (ja) | 半導体デバイスのシミュレーション方法 | |

| Xia et al. | A new approach to implementing high-frequency correlated noise for bipolar transistor compact modeling | |

| Sommet et al. | Model order reduction of linear and nonlinear 3D thermal finite‐element description of microwave devices for circuit analysis | |

| Issaoun et al. | An accurate and compact large signal model for III–V HBT devices | |

| La Spina et al. | Thermally induced current bifurcation in bipolar transistors | |

| Ko et al. | A nonquasi-static table-based small-signal model of heterojunction bipolar transistor |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040917 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040928 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041126 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050201 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050216 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080225 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090225 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |