JP3616268B2 - リングオシレータ用遅延回路 - Google Patents

リングオシレータ用遅延回路 Download PDFInfo

- Publication number

- JP3616268B2 JP3616268B2 JP03348899A JP3348899A JP3616268B2 JP 3616268 B2 JP3616268 B2 JP 3616268B2 JP 03348899 A JP03348899 A JP 03348899A JP 3348899 A JP3348899 A JP 3348899A JP 3616268 B2 JP3616268 B2 JP 3616268B2

- Authority

- JP

- Japan

- Prior art keywords

- pair

- transistor

- transistors

- output

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 claims description 6

- 238000010586 diagram Methods 0.000 description 8

- 230000010355 oscillation Effects 0.000 description 7

- 102100037224 Noncompact myelin-associated protein Human genes 0.000 description 5

- 101710184695 Noncompact myelin-associated protein Proteins 0.000 description 5

- 230000010354 integration Effects 0.000 description 5

- 230000000694 effects Effects 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03B—GENERATION OF OSCILLATIONS, DIRECTLY OR BY FREQUENCY-CHANGING, BY CIRCUITS EMPLOYING ACTIVE ELEMENTS WHICH OPERATE IN A NON-SWITCHING MANNER; GENERATION OF NOISE BY SUCH CIRCUITS

- H03B27/00—Generation of oscillations providing a plurality of outputs of the same frequency but differing in phase, other than merely two anti-phase outputs

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/027—Generators characterised by the type of circuit or by the means used for producing pulses by the use of logic circuits, with internal or external positive feedback

- H03K3/03—Astable circuits

- H03K3/0315—Ring oscillators

- H03K3/0322—Ring oscillators with differential cells

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/133—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals using a chain of active delay devices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K2005/00013—Delay, i.e. output pulse is delayed after input pulse and pulse length of output pulse is dependent on pulse length of input pulse

- H03K2005/0015—Layout of the delay element

- H03K2005/00195—Layout of the delay element using FET's

- H03K2005/00208—Layout of the delay element using FET's using differential stages

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Amplifiers (AREA)

- Networks Using Active Elements (AREA)

Description

【発明の属する技術分野】

本発明は、リングオシレータ用遅延回路に関し、特に、CMOS集積化が可能であり、VCO(Voltage−controlled Oscillator)をリングオシレータで実現するCMOS集積化PLL(Phase Lock Loop)への適用に適しているリングオシレータ用遅延回路に関する。

【0002】

【従来の技術】

CMOS集積回路に適したPLL回路のリングオシレータには、リングオシレータ用遅延回路が用いられる。このようなリングオシレータ用遅延回路は、一般的には、単一入力・単一出力型、又は、差動入力・差動出力型の回路構成を有し利得が1以上である増幅回路が用いられている。リングオシレータ用遅延回路は、近年、集積回路化に適した回路構成であるCMOS回路でその実現が可能であること、且つ、温度プロセス変動に対しその回路が持つ入出力間の遅延時間が電子的に調整可能であることが要求されている。

【0003】

このような要求に応えるためのリングオシレータ用遅延回路が、文献(*1)により知られている。

(*1):アイ・イー・イー・イー・ジャーナル・オブ・ソリッド・ステート・サーキッツ、第SC−25巻、第6号、第1385〜1394頁、1990年12月。

この文献に開示されているリングオシレータ用遅延回路は、図8に示されるように、基準電圧回路101を用いてPMOSトランジスタMP11、MP12を三極管領域に常にバイアスすることにより、同相利得を1以下に抑制して差動信号成分でのみ発振するように工夫されている。この公知技術は、更に、VBIAS端子の電圧により当該遅延回路の入力電圧−出力電圧間の応答時間である遅延時間が可変である。この公知技術は、このように、CMOS集積回路化に適したリングオシレータ用遅延回路として形成されている。

【0004】

同相利得が1以上である遅延回路を用いてリングオシレータを構成しその遅延回路を図4に示されるように奇数個用いると、そのリングオシレータの同相信号成分のループ利得が1以上になって、出力信号には差動信号成分による発振出力だけでなく同相信号成分の発振出力も含まれる。同相利得が1以上である遅延回路を用いてリングオシレータを構成しその遅延回路を図5に示されるように偶数個用いると、同様に、そのリングオシレータの同相信号成分のループ利得が1以上になり、この場合は、双安定な回路が形成されて、そのリングオシレータの出力電圧は、最終的には高電位側VDD又は低電位側VSSのいずれかの電圧状態になる。通常、差動入力−差動出力型遅延回路を用いるリングオシレータは、差動信号成分で発振するように設計されているので、同相信号成分のループ利得は1以下に設定されており、同相信号成分による発振出力の不安定化の影響を取り除くことが必要である。

【0005】

図8に示される技術は、負荷であるPMOSトランジスタMP11,MP12のそれぞれのドレイン・ソース間コンダクタンスを意図的に高くすることにより、その同相利得が1以上になることを防いでいる。より具体的には、その負荷であるPMOSトランジスタMP11,MP12を常に三極管領域動作となるようにそのPMOSトランジスタMP11,MP12のゲート電圧を設定している。一般に、MOSトランジスタのドレイン・ソース間コンダクタンスに関して、三極管領域におけるドレイン・ソース間コンダクタンスと比較して、飽和領域におけるドレイン・ソース間コンダクタンスは非常に小さく、PMOSトランジスタMP11とPMOSトランジスタMP12が三極管領域から外れて飽和領域で動作する場合、同相利得が1以上になり、このようなトランジスタでリングオシレータを構成すれば、図4に示されるような奇数段構成のリングオシレータは、同相信号成分で発振する状態がありうる。更に、差動入力と差動出力を持つ回路である図8の回路は、図5に示されるような偶数段構成のリングオシレータを実現することができるが、その遅延回路の同相利得が1以上である場合、双安定な回路になって発振が行われない状態がありうる。

【0006】

このような状態になると、PMOSトランジスタを三極管領域で常に動作させるために、このPMOSトランジスタのゲート電圧には、温度変動及びプロセス変動に対して常に一定電圧を供給する基準電圧回路が必要であり、その結果、チップ面積が増大するという問題が派生する。

【0007】

基準電圧回路を用いることなく、1以上の差動利得と1以下の同相利得を容易に実現することが望まれる。更に、1以上の差動利得と1以下の同相利得を実現することにより、CMOS集積化に適したリングオシレータ用遅延回路の提供が望まれる。

【0008】

【発明が解決しようとする課題】

本発明の課題は、基準電圧回路を用いることなく、1以上の差動利得と1以下の同相利得を容易に実現することができるリングオシレータ用遅延回路を提供することにある。

本発明の他の課題は、1以上の差動利得と1以下の同相利得を実現することにより、CMOS集積化に適したリングオシレータ用遅延回路を提供することにある。

【0009】

【課題を解決するための手段】

その課題を解決するための手段が、下記のように表現される。その表現中の請求項対応の技術的事項には、括弧()つきで、番号、記号等が添記されている。その番号、記号等は、請求項対応の技術的事項と実施の複数・形態のうちの少なくとも1つの形態の技術的事項との一致・対応関係を明白にしているが、その請求項対応の技術的事項が実施の形態の技術的事項に限定されることを示すためのものではない。

【0010】

本発明によるリングオシレータ用遅延回路は、第1電位線(VDD)と、一対の出力線(2A,2B)と、第1電位線(VDD)と一対の出力線(2A,2B)との間にそれぞれに介設される1対の2つの第1トランジスタ(MP1,MP2)と、第2電位線(5)と、第2電位線(5)と一対の出力線(2A,2B)との間にそれぞれに介設される1対の2つの第2トランジスタ(MN1,MN2)とからなり、第1トランジスタ(MP1,MP2)のそれぞれのゲートが一対の出力線(2A,2B)にそれぞれに接続され、2つの第1トランジスタ(MP1,MP2)は中心対称に接続され、2つの第2トランジスタ(MN1,MN2)は中心対称に接続され、更に、第3電位線(図2,図3,図7の接地線又は図6のVDD)からなり、一対の出力線(2A,2B)は第3電位線(図2,図3,図7の接地線又は図6のVDD)に接続されている。このような回路は、1以上の差動利得と1以下の同相利得を容易に実現することができる。

【0011】

第1トランジスタ(MP1,MP2)がPMOSトランジスタであれば第2トランジスタ(MN1,MN2)はNMOSトランジスタであり、第1トランジスタ(MP1,MP2)がNMOSトランジスタであれば第2トランジスタはPMOSトランジスタであることが好ましい。更に、一対の出力線(2A,2B)と第1電位線との間に介設される一対の第3トランジスタ(MP3,MP4)を設けることが好ましい。この場合、第1トランジスタ(MP1,MP2)のゲートが第3トランジスタ(MP3,MP4)のゲートにそれぞれに中心対称に接続されている。更に、一対の出力線(2A,2B)と第3電位線との間に介設される一対の第4トランジスタ(MN3,MN4)を設けることも好ましい。この場合、第4トランジスタ(MN3,MN4)のゲートが出力線(2A,2B)にそれぞれに接続されている。

【0012】

2つの第2トランジスタ(MN1,MN2)のゲートにそれぞれに印加される入力電圧がV1,V2で表され、入力電圧V1,V2に関する同相入力電圧がVIQで表わされ、2つの入力V1,V2の入力差の形で含まれる差動入力電圧がΔVIで表され、出力線(2A,2B)に現れる2つの出力電圧がVo1,Vo2で表され、出力電圧Vo1,Vo2に共通に含まれる同相出力電圧がVOQで表され、出力電圧Vo1,Vo2の出力差の形で含まれる差動出力電圧がΔVOで表わされ、第1トランジスタ(MP1,MP2)のトランスコンダクタンスがGmpで表され、第2トランジスタ(MN1,MN2)のトランスコンダクタンスがGmnで表され、出力線(2A,2B)と第3電位線との間のトランスコンダクタンスがGmで表される。

【0013】

設計定数としてのコンダクタンスがGdsに設定されれば、当該回路の同相利得VOQ/VIQは、次式:VOQ/VIQ=−(Gmn*Gds/2)/{(Gmp+Gm)*(Gmn+Gds/2)}で求められる。Gmn>>Gds/2であるようにその設計定数が定められると、この式はGmnが消去されて、近似式:VOQ/VIQ=−(Gds/2)/(Gmp+Gm)が得られる。この同相利得が十分に小さくなるように設計定数Gdsを更に適正に設定することができる。この場合、差動利得ΔVO/ΔVIは、次式:ΔVO/ΔVI=Gmn/(Gmp−Gm)で表される。Gmn>(Gmp−Gm)であるようにパラメータGmn,Gmp,Gmの値が設定される。更に、第4電位線(VSS)と、第4電位線(VSS)と第2電位線との間に介設されるバイアス・トランジスタ(MNB)とからなり、バイアス・トランジスタ(MNB)のドレイン・ソース間コンダクタンスが設計定数Gdsに一致している。このような回路は、1以上の差動利得と1以下の同相利得を確実に実現している。

【0014】

【発明の実施の形態】

図に一致対応して、本発明によるリングオシレータ用遅延回路の実施の形態は、ソース結合対回路が設けられている。そのソース結合対回路は、第1NMOSトランジスタMN1と第2NMOSトランジスタMN2とが、ソース対結合している。バイアス電流源用NMOSトランジスタMNBが、第1NMOSトランジスタMN1と第2NMOSトランジスタMN2に接続している。バイアス電流源用NMOSトランジスタMNBは、第1NMOSトランジスタMN1と第2NMOSトランジスタMN2とにバイアス電流を供給する電流源である。

【0015】

出力負荷として作用する第1PMOSトランジスタMP1と第2PMOSトランジスタMP2とが、出力線2に接続している。第1PMOSトランジスタMP1と第2PMOSトランジスタMP2は、高電位側電源線VDDと出力線2の間に介設されている。

【0016】

出力線2は、第2出力線2Bと第1出力線2Aとから形成されている。第2出力線2Bは第1PMOSトランジスタMP1の第1ゲート3Aに短絡し、第1出力線2Aは第2PMOSトランジスタMP2の第2ゲート3Bに短絡している。第1PMOSトランジスタMP1と第2PMOSトランジスタMP2は、それらのそれぞれの第1ゲート3A、第2ゲート3Bがそれらのそれぞれのドレイン4A,4Bに短絡している。

【0017】

第1電圧制御電流源I1、第2電圧制御電流源I2が、出力線2に接続されている。第1電圧制御電流源I1と第2電圧制御電流源I2は、出力電圧節点と任意の定電位に接続され、出力電圧により制御される。バイアス電源VBIASが、バイアス電流源用NMOSトランジスタMNBのゲートに接続されている。

【0018】

バイアス電源VBIASは、バイアス電流源用NMOSトランジスタMNBが飽和領域になるようにバイアスする。バイアス電流源用NMOSトランジスタMNBは、第1NMOSトランジスタMN1と第2NMOSトランジスタMN2を対接合している対接合線5と低電位側電源線VSSとの間に介設されている。

【0019】

第1NMOSトランジスタMN1のゲートと第2NMOSトランジスタMN2のゲートに、第1入力電圧V1と第2入力電圧V2とがそれぞれに入力される。第1NMOSトランジスタMN1、第2NMOSトランジスタMN2、バイアス電流源用NMOSトランジスタMNBが飽和領域にあり、且つ、第1NMOSトランジスタMN1と第2NMOSトランジスタMN2の電気的特性が等しく、且つ、第1PMOSトランジスタMP1と第2PMOSトランジスタMP2の電気的特性が等しい場合、第1入力電圧V1と第2入力電圧V2に共通に含まれる信号である同相信号入力に対して、1組の左右の第1NMOSトランジスタMN1と第2NMOSトランジスタMN2、1組の左右の第1PMOSトランジスタMP1と第2PMOSトランジスタMP2、及び、左右の1組の第1電圧制御電流源I1と第2電圧制御電流源I2は、それぞれに対称に動作する。このように対称に動作する当該遅延回路は、その回路の対称中心線で2分した図2に示される片側のみの回路で表現することができる。

【0020】

図2に示される回路は、同相信号成分に着目すれば、図1の回路の片側分に等価である等価回路に相当している。図2のその等価回路で、第1NMOSトランジスタMN1のトランスコンダクタンスをGmnで表し、第1PMOSトランジスタMP1のトランスコンダクタンスをGmpで表し、第1電圧制御電流源I1のトランスコンダクタンスをGmで表し、バイアス電流源用NMOSトランジスタMNBのドレイン・ソース間コンダクタンスをGdsで表し、同相信号成分に対するコンダクタンス成分をy3で表す。同相信号成分に対するコンダクタンス成分は、バイアス電流源用NMOSトランジスタMNBのドレイン・ソース間コンダクタンスの半分のコンダクタンスのみ同相信号成分に対して寄与するので、y3=Gds/2となる。

【0021】

同様に、第1NMOSトランジスタMN1、第2NMOSトランジスタMN2、バイアス電流源用NMOSトランジスタMNBが飽和領域にあり、且つ、第1NMOSトランジスタMN1と第2NMOSトランジスタMN2の電気的特性が等しく、且つ、第1PMOSトランジスタMP1と第2PMOSトランジスタMP2の電気的特性が等しい場合、第1入力電圧V1と第2入力電圧V2の入力差の形で含まれる信号成分である差動信号入力に対しては、1組の左右の第1NMOSトランジスタMN1と第2NMOSトランジスタMN2、1組の左右の第1PMOSトランジスタMP1と第2PMOSトランジスタMP2、及び、左右の1組の第1電圧制御電流源I1と第2電圧制御電流源I2は、それぞれに逆向きの動作をする。このように逆向きの動作をする第1NMOSトランジスタMN1と第2NMOSトランジスタMN2は、それらのそれぞれのソース電位が等価的に接地電位であると考えることができ、図3に示される片側のみの回路で表現することができる。

【0022】

図3に示される回路は、差動信号成分に着目すれば、図1の回路の片側分に等価である等価回路に相当している。図2の等価回路と同じく、図3の等価回路でも、第1NMOSトランジスタMN1のトランスコンダクタンスは既述のGmnで表され、第1PMOSトランジスタMP1のトランスコンダクタンスは既述のGmpで表され、第1電圧制御電流源I1のトランスコンダクタンスは既述のGmで表わされる。

【0023】

第1PMOSトランジスタMP1は、そのゲートとドレインが短絡されているので、常に飽和領域で動作し、そのコンダクタンスy1は、トランスコンダクタンスGmpに等しい。2つの入力V1,V2に含まれる同相入力電圧をVIQで表し、2つの入力V1,V2の入力差の形で含まれる信号成分である差動入力電圧をΔVIで表して、同相入力電圧と差動入力電圧を次式により定義する。

同相入力電圧:VIQ=(V1+V2)/2,・・・(1)

差動入力電圧:ΔVI=(V1−V2).・・・(2)

【0024】

同様に、2つの出力Vo1,Vo2に共通に含まれる信号成分である同相出力電圧をVOQで表し、2つの出力Vo1,Vo2の出力差の形で含まれる信号成分である差動出力電圧をΔVOで表して、同相出力電圧と差動出力電圧を次式により定義する。

同相出力電圧:VOQ=(Vo1+Vo2)/2,・・・(3)

差動出力電圧:ΔVO=(Vo1−Vo2).・・・(4)

【0025】

このような定義に従うと、入力電圧V1,V2と出力電圧Vo1,Vo2は、それぞれに、次式により表される。

V1=ΔVI/2+VIQ,・・・(5)

V2=−ΔVI/2+VIQ,・・・(6)

Vo1=ΔVO/2+VOQ,・・・(7)

Vo2=−ΔVI/2+VOQ.・・・(8)

【0026】

図2に示される同相成分の等価回路で、y3のコンダクタンス間電圧をVXで表せば、VXは次式で表される。

VX=Gmn*VIQ/(Gmn+Gds/2)・・・(9)

同相出力電圧VOQが現れる出力節点に関して、次式が成立する。

Gmn*(VIQ−VX)+Gmp*VOQ+Gm*VOQ=0.・・・(10)

同相利得をVOQ/VIQと定義すれば、式(10)から、

VOQ/VIQ=−(Gmn*Gds/2)/{(Gmp+Gm)*(Gmn+Gds/2)}.・・・(11)

【0027】

一般に、飽和領域にバイアスされたMOSトランジスタに関して、トランスコンダクタンスは、ドレイン・ソース間コンダクタンスに比較して十分に大きい。更に、バイアス電流源用NMOSトランジスタMNBは電流源として作用するので、そのドレイン・ソース間コンダクタンスは十分に小さくなるように、ゲート電圧VBIASが通常は設定されている。従って、Gmn>>Gds/2、であると考えることができる。式(11)は、次式のように簡略化される。

【0028】

VOQ/VIQ=−(Gds/2)/{(Gmp+Gm)<<1.・・・(12)

このように利得は、1よりも十分に小さい。同様に、図3で示される差動信号成分の等価回路では、差動出力電圧ΔVOが現れる出力接点に関して、次式が成立する。

Gmn*(ΔVI/2)+Gmp*(−ΔVO/2)+Gm*(ΔVO/2)=0.・・・(13)

差動利得ΔVO/ΔVIについては、

ΔVO/ΔVI=Gmn/(Gmp−Gm).・・・(14)

式(14)から明らかなように、

Gmn>(Gmp−Gm)、・・・(15)

であるように選ぶことにより、差動利得を1以上にすることができる。

【0029】

第1PMOSトランジスタMP1と第2PMOSトランジスタMP2のトランスコンダクタンスGmpと電圧制御電流源I1,I2のトランスコンダクタンスGmを近い値に設定することにより、差動利得を1以上の値で任意に設定可能である。一般に、MOSトランジスタは、ゲートの形状であるチャンネル幅及びチャンネル長さを調整することにより、そのトランスコンダクタンスを任意の値に設計可能である。従って、設計者はNMOSトランジスタMN1,MN2、PMOSトランジスタMP1,MP2のゲート形状を調整することにより、式(15)の関係を容易に得ることができる。

【0030】

図1に示される実施の形態では、NMOSトランジスタMN1,MN2,MNBをそれぞれにPMOSトランジスタに、PMOSトランジスタMP1,MP2をそれぞれにNMOSトランジスタに取り替えることができる。その場合、電圧制御電流源I1,I2は、電圧出力節点に対して注入電流源型になる。

【0031】

本発明による既述のリングオシレータ用遅延回路を用いれば、図4に示される3個の遅延回路であるDELAY0、DELAY1、DELAY2により奇数段のリングオシレータを構成した場合、ループ利得が差動信号成分で1以上、同相信号成分で1以下に設定することができるので、同相信号成分での発振を抑えることができ、差動信号成分のみ発振するリングオシレータを実現することができる。

【0032】

同様に、図5に示される4個の遅延回路DELAY0、DELAY1、DELAY2、DELAY3により偶数段のリングオシレータを構成した場合、上述の奇数段のリングオシレータと同様にループ利得が差動信号成分で1以上、同相信号成分で1以下にすることができるので、同相信号成分に対して双安定な状態を抑制することができ、差動信号成分でのみ発振するリングオシレータを実現することができる。遅延回路の個数は、3、4に限られず、任意に増加させることができる。

【0033】

本発明によるリングオシレータ用遅延回路は、従来技術で実現されているリングオシレータ用遅延回路と同じく、VBIAS端子の電圧で回路のバイアスを調整することにより、その入力電圧−出力電圧の応答時間である遅延時間を可変にすることができる。リングオシレータの発振周波数は、遅延回路が持つ遅延時間とループ内に存在する遅延回路の個数により決まるので、本発明による遅延回路を用いて実現するリングオシレータは、電子的にその発振周波数を制御することができる。従って、本発明によるリングオシレータ用遅延回路は、PLLの基本構成素子であるVCOへの応用に適している。遅延回路を用いたリングオシレータの原理、リングオシレータのPLLへの応用については、当該技術分野では周知であり、その記述は省略されている。

【0034】

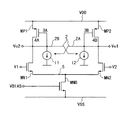

図6は、本発明による既述の実施の形態を更に具体化した回路構成を示している。第1NMOSトランジスタMN1、第2NMOSトランジスタMN2、第1PMOSトランジスタMP1、第2PMOSトランジスタMP2の相互接続関係、入力電圧V1、V2の作用点、出力電圧Vo1,Vo2の端子点と第1NMOSトランジスタMN1、第2NMOSトランジスタMN2、第1PMOSトランジスタMP1、第2PMOSトランジスタMP2の接続関係、第1NMOSトランジスタMN1、第2NMOSトランジスタMN2、第1PMOSトランジスタMP1、第2PMOSトランジスタMP2に対する高電位側電源線VDD,出力線2、対接合線5、低電位側電源線VSSの配線関係は、図1のそれらと全く同じである。

【0035】

第2出力線2Bは、第3PMOSトランジスタMP3を介して高電位側電源線VDDに接続されている。第1出力線2Aは、第4PMOSトランジスタMP4を介して高電位側電源線VDDに接続されている。第3PMOSトランジスタMP3のゲートは、第2PMOSトランジスタMP2のゲートとドレインに接続されている。第4PMOSトランジスタMP4のゲートは、第1PMOSトランジスタMP1のゲートとドレインに接続されている。第3,4PMOSトランジスタMP3,4は、出力電圧を検出して電流に変換する電圧制御電流源である。VBIASは、バイアス電流源用NMOSトランジスタMNBの電流を制御するバイアス電源線である点も、図1のそれに同じである。

【0036】

図1に示される出力電圧Vo1を検出して電流に変換する電圧制御電流源I1を第3PMOSトランジスタMP3に置換し、図1に示される出力電圧Vo2を検出して電流に変換する電圧制御電流源I2を第4PMOSトランジスタMP4に置換することにより、図6に示される実施の形態が実現している。

【0037】

図6に示される回路に関して、第1NMOSトランジスタMN1と第2NMOSトランジスタMN2のチャンネル幅とチャンネル長さは、両トランジスタが同一の電気的特性を得るように、両トランジスタで同じに設定されている。同様に、第1PMOSトランジスタMP1と第2PMOSトランジスタMP2のチャンネル幅とチャンネル長さは、両トランジスタが同一の電気的特性を得るように、両トランジスタで同じに設定されている。更に同様に、第3PMOSトランジスタMP3と第4PMOSトランジスタMP4のチャンネル幅とチャンネル長さは、両トランジスタが同一の電気的特性を得るように、両トランジスタで同じに設定されている。

【0038】

トランジスタMN1,MN2,MNBがそれぞれに飽和領域にある場合、第1入力電圧V1と第2入力電圧V2に共通に含まれる信号である同相信号入力に対して、1組の左右の第1NMOSトランジスタMN1と第2NMOSトランジスタMN2、1組の左右の第1PMOSトランジスタMP1と第2PMOSトランジスタMP2、及び、1組の左右の第3PMOSトランジスタMP3と第4PMOSトランジスタMP4は、それぞれに対称に動作する。このように対称に動作する当該遅延回路は、その回路の対称中心線で2分した図2に示される片側のみの回路と同一の回路である。

【0039】

従って、図2に関して、Gmnは図6中のトランジスタMN1のトランスコンダクタンス、Gmpは図6中のトランジスタMP1のトランスコンダクタンス、Gmは図6中の第3PMOSトランジスタMP3のトランスコンダクタンス、Gdsは図6中のバイアス電流源用NMOSトランジスタMNBのドレイン・ソース間コンダクタンスにそれぞれに置き換えられる。一方、2つの入力差の形で含まれる信号成分である差動信号入力に対しては、図6で、1組の左右のトランジスタMN1とMN2、1組の左右のトランジスタMP1とMP2、及び、1組の左右のトランジスタMP3とMP4は、それぞれに逆向きの動作をするので、図6の第1NMOSトランジスタMN1と第2NMOSトランジスタMN2のソース電位は等価的に接地と考えることができ、図6に示される実施の形態の回路の差動信号成分について、片側の等価回路は、図3に示される既述の片側の等価回路に同一である。従って、図3に関して、Gmnは図6中のトランジスタMN1のトランスコンダクタンス、Gmpは図6中の第1PMOSトランジスタMP1のトランスコンダクタンス、Gmは図6中の第3PMOSトランジスタMP3のトランスコンダクタンスにそれぞれに置き換えられる。

【0040】

図6に示される回路に関して、式(15)が成り立つようにトランジスタMN1,MN2,MP1,MP2,MP3,MP4のそれぞれのチャンネル幅、チャンネル長さを選べば、図1に示したリングオシレータ用遅延回路と同じ特性を得ることができ、図6の同相利得は式(12)により、差動利得は式(14)によりそれぞれに与えられる。

【0041】

図6に示される実施の形態で、PMOSトランジスタMP1,MP2,MP3,MP4をそれぞれにNMOSトランジスタに、NMOSトランジスタMN1,MN2,MNBをそれぞれにPMOSトランジスタで構成することができることは、既述の通りである。

【0042】

図7は、本発明による既述の実施の形態を更に具体化した他の回路構成を示している。第1NMOSトランジスタMN1、第2NMOSトランジスタMN2、第1PMOSトランジスタMP1、第2PMOSトランジスタMP2の相互接続関係、入力電圧V1、V2の作用点、出力電圧Vo1,Vo2の端子点と第1NMOSトランジスタMN1、第2NMOSトランジスタMN2、第1PMOSトランジスタMP1、第2PMOSトランジスタMP2の接続関係、第1NMOSトランジスタMN1、第2NMOSトランジスタMN2、第1PMOSトランジスタMP1、第2PMOSトランジスタMP2に対する高圧電位側電源線VDD,出力線2、対接合線5、低電位側電源線VSSの配線関係は、図1のそれらと全く同じである。

【0043】

第2出力線2Bは、第3NMOSトランジスタMN3を介して接地線に接続されている。第1出力線2Aは、第4NMOSトランジスタMN4を介して接地線に接続されている。第3NMOSトランジスタMN3のゲートは、第2PMOSトランジスタMP2のゲートとドレインに接続されている。第4NMOSトランジスタMN4のゲートは、第1PMOSトランジスタMP1のゲートとドレインに接続されている。第3,4NMOSトランジスタMN3,4は、出力電圧を検出して電流に変換する電圧制御電流源である。VBIASは、バイアス電流源用NMOSトランジスタMNBの電流を制御するバイアス電源線である点も、図1のそれに同じである。

【0044】

図1に示される出力電圧Vo1を検出して電流に変換する電圧制御電流源I1を第3NMOSトランジスタMN3に置換し、図1に示される出力電圧Vo2を検出して電流に変換する電圧制御電流源I2を第4NMOSトランジスタMN4に置換することにより、図7に示される実施の形態が実現している。

【0045】

図7に示される回路に関して、第1NMOSトランジスタMN1と第2NMOSトランジスタMN2のチャンネル幅とチャンネル長さは、両トランジスタが同一の電気的特性を得るように、両トランジスタで同じに設定されている。同様に、第1PMOSトランジスタMP1と第2PMOSトランジスタMP2のチャンネル幅とチャンネル長さは、両トランジスタが同一の電気的特性を得るように、両トランジスタで同じに設定されている。更に同様に、第3NMOSトランジスタMN3と第4NMOSトランジスタMN4のチャンネル幅とチャンネル長さは、両トランジスタが同一の電気的特性を得るように、両トランジスタで同じに設定されている。

【0046】

トランジスタMN1,MN2,MNBがそれぞれに飽和領域にある場合、第1入力電圧V1と第2入力電圧V2に共通に含まれる信号である同相信号入力に対して、1組の左右の第1NMOSトランジスタMN1と第2NMOSトランジスタMN2、1組の左右の第1PMOSトランジスタMP1と第2PMOSトランジスタMP2、及び、左右の1組の第3NMOSトランジスタMN3と第4NMOSトランジスタMN4は、それぞれに対称に動作する。このように対称に動作する当該遅延回路は、その回路の対称中心線で2分した図2に示される片側のみの回路と同一の回路である。

【0047】

従って、図2に関して、Gmnは図7中のトランジスタMN1のトランスコンダクタンス、Gmpは図7中のトランジスタMP1のトランスコンダクタンス、Gmは図7中の第3NMOSトランジスタMN3のトランスコンダクタンス、Gdsは図7中のバイアス電流源用NMOSトランジスタMNBのドレイン・ソース間コンダクタンスにそれぞれに置き換えられる。一方、2つの入力差の形で含まれる信号成分である差動信号入力に対しては、図7で、1組の左右のトランジスタMN1とMN2、1組の左右のトランジスタMP1とMP2、及び、1組の左右のトランジスタMN3とMN4は、それぞれに逆向きの動作をするので、図7の第1NMOSトランジスタMN1と第2NMOSトランジスタMN2のソース電位は等価的に接地と考えることができ、図7に示される実施の形態の回路の差動信号成分について、片側の等価回路は、図3に示される既述の片側の等価回路に同一である。従って、図3に関して、Gmnは図7中のトランジスタMN1のトランスコンダクタンス、Gmpは図7中の第1PMOSトランジスタMP1のトランスコンダクタンス、Gmは図7中の第3NMOSトランジスタMN3のトランスコンダクタンスにそれぞれに置き換えられる。

【0048】

図7に示される回路に関して、式(15)が成り立つようにトランジスタMN1,MN2,MP1,MP2,MN3,MN4のそれぞれのチャンネル幅、チャンネル長さを選べば、図1に示したリングオシレータ用遅延回路と同じ特性を得ることができ、図7の同相利得は式(12)により、差動利得は式(14)によりそれぞれに与えられる。

【0049】

図7で示される実施の形態で、NMOSトランジスタMN1,MN2,MN3,MN4,MNBをそれぞれにPMOSトランジスタに、PMOSトランジスタMP1,MP2をそれぞれにNMOSトランジスタで構成することができることは、既述の通りである。

【0050】

【発明の効果】

本発明によるリングオシレータ用遅延回路は、1以上の差動利得と1以下の同相利得を容易に実現している。

【図面の簡単な説明】

【図1】図1は、本発明によるリングオシレータ用遅延回路の実施の形態を示す回路図である。

【図2】図2は、図1の回路の同相信号成分について等価な回路を示す回路図である。

【図3】図3は、図1の回路の差動信号成分について等価な回路を示す回路図である。

【図4】図4は、公知のリングオシレータを示す回路図である。

【図5】図5は、公知の他のリングオシレータを示す回路図である。

【図6】図5は、本発明によるリングオシレータ用遅延回路の実施の他の形態を示す回路図である。

【図7】図7は、本発明によるリングオシレータ用遅延回路の実施の更に他の形態を示す回路図である。

【図8】図8は、公知のリングオシレータ用遅延回路を示す回路図である。

【符号の説明】

2A,2B…一対の出力線

5…第2電位線

VDD…第1電位線(第3電位線であることがある)

MP1,MP2…第1トランジスタ

MN1,MN2…第2トランジスタ

MP3,MP4…第3トランジスタ

MN3,MN4…第4トランジスタ

V1,V2…入力電圧

Vo1,Vo2…出力電圧

VIQ…同相入力電圧

VOQ…同相出力電圧

ΔVI…差動入力電圧

ΔVO…差動出力電圧

Gmp…第1トランジスタのトランスコンダクタンス

Gmn…第2トランジスタのトランスコンダクタンス

Gm…出力線と第3電位線との間のトランスコンダクタンス

Gds…設計定数としてのトランスコンダクタンス

Claims (6)

- 第1電位線と、

一対の出力線と、

前記第1電位線と前記一対の出力線との間にそれぞれに介設される1対の第1トランジスタと、

第2電位線と、

前記第2電位線と前記一対の出力線との間にそれぞれに介設される1対の第2トランジスタと、

前記1対の出力線にそれぞれに接続する1対の電圧制御電流源と、

前記一対の電圧制御電流源の出力側に接続する第3電位線とを含み、

前記一対の第2トランジスタのゲートにはそれぞれに入力電圧が印加され、

前記一対の第1トランジスタのゲートはそれぞれに前記一対の出力線に短絡し、

前記一対の電圧制御電流源の一方は前記一対の出力線の他方の出力電圧により制御され、前記一対の電圧制御電流源の他方は前記一対の出力線の一方の出力電圧により制御されることを特徴とするリングオシレータ用遅延回路。 - 請求項1において、前記第1トランジスタはPMOSトランジスタであり且つ前記第2トランジスタはNMOSトランジスタであり、又は前記第1トランジスタはNMOSトランジスタであり且つ前記第2トランジスタはPMOSトランジスタであることを特徴とするリングオシレータ用遅延回路。

- 請求項1において、前記第3電位線は前記第1電位線であり、前記1対の電圧制御電流源は1対の第3のトランジスタであり、前記1対の第3のトランジスタの一方は前記一対の出力線の一方と前記第1電位線との間に介設され且つそのゲートが前記1対の出力線の他方に接続され、前記1対の第3のトランジスタの他方は前記一対の出力線の他方と前記第1電位線との間に介設され且つそのゲートが前記1対の出力線の一方に接続されたことを特徴とするリングオシレータ用遅延回路。

- 請求項1において、前記第3電位線は接地線であり、前記1対の電圧制御電流源は1対の第3のトランジスタであり、前記1対の第3のトランジスタの一方は前記一対の出力線の一方と前記第3電位線との間に介設され且つそのゲートが前記1対の出力線の他方に接続され、前記1対の第3のトランジスタの他方は前記1対の出力線の他方と前記第1電位線との間に介設され且つそのゲートが前記1対の出力線の一方に接続されたことを特徴とするリングオシレータ用遅延回路。

- 請求項1において、前記一対の第 2 のトランジスタをバイアスするバイアストランジスタを更に有し、2つの前記第2トランジスタのゲートにそれぞれに印加される入力電圧がV1,V2で表わされ、前記入力電圧V1,V2に関する同相入力電圧がVIQで表わされ、前記入力電圧V1,V2の入力差の形で含まれる差動入力電圧がΔVIで表わされ、前記出力線に現れる2つの出力電圧がVo1,Vo2で表わされ、前記出力電圧Vo1,Vo2に共通に含まれる同相出力電圧がVOQで表わされ、前記出力電圧Vo1,Vo2の出力差の形で含まれる差動出力電圧がΔVOで表わされ、前記第1トランジスタのトランスコンダクタンスがGmpで表わされ、前記第2トランジスタのトランスコンダクタンスがGmnで表わされ、前記出力線と前記第3電位線との間のトランスコンダクタンスがGmで表わされ、設計定数として前記バイアス・トランジスタのドレイン・ソース間のコンダクタンスがGdsで表わされ、当該回路の同相利得VOQ/VIQは、式:

VOQ/VIQ=−(Gmn*Gds/2)/{(Gmp+Gm)*(Gmn+Gds/2)}.

で求められ、Gmn>>Gds/2であるように前記設計定数が定められ、前記式は、Gmnが消去されて、式:

VOQ/VIQ=−(Gds/2)/(Gmp+Gm).

によりよい近似で再表現され、前記同相利得が十分に小さくなるように前記設計定数Gdsが更に適正に設定されていることを特徴とするリングオシレータ用遅延回路。 - 請求項5において、差動利得ΔVO/ΔVIは、式:

ΔVO/ΔVI=Gmn/(Gmp−Gm).

で表わされ、Gmn>(Gmp−Gm)であるようにパラメータGmn,Gmp,Gmの値が設定されていることを特徴とするリングオシレータ用遅延回路。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP03348899A JP3616268B2 (ja) | 1999-02-10 | 1999-02-10 | リングオシレータ用遅延回路 |

| US09/498,993 US6348839B1 (en) | 1999-02-10 | 2000-02-07 | Delay circuit for ring oscillator |

| SG200000744A SG88768A1 (en) | 1999-02-10 | 2000-02-09 | Delay circuit for ring oscillator |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP03348899A JP3616268B2 (ja) | 1999-02-10 | 1999-02-10 | リングオシレータ用遅延回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2000232340A JP2000232340A (ja) | 2000-08-22 |

| JP3616268B2 true JP3616268B2 (ja) | 2005-02-02 |

Family

ID=12387954

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP03348899A Expired - Fee Related JP3616268B2 (ja) | 1999-02-10 | 1999-02-10 | リングオシレータ用遅延回路 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6348839B1 (ja) |

| JP (1) | JP3616268B2 (ja) |

| SG (1) | SG88768A1 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6502050B1 (en) * | 2000-06-20 | 2002-12-31 | Xilinx, Inc. | Measuring a minimum lock frequency for a delay locked loop |

| JP2002261590A (ja) * | 2001-02-28 | 2002-09-13 | Asahi Kasei Microsystems Kk | 遅延装置 |

| US20020175729A1 (en) * | 2001-05-25 | 2002-11-28 | Infineon Technologies North America Corp. | Differential CMOS controlled delay unit |

| US6690242B2 (en) * | 2001-12-21 | 2004-02-10 | Texas Instruments Incorporated | Delay circuit with current steering output symmetry and supply voltage insensitivity |

| US6894552B2 (en) * | 2003-02-28 | 2005-05-17 | Teradyne, Inc. | Low-jitter delay cell |

| US6987423B2 (en) * | 2003-08-19 | 2006-01-17 | Freescale Semiconductor, Inc. | Two port voltage controlled oscillator for use in wireless personal area network synthesizers |

| KR100555733B1 (ko) * | 2004-02-14 | 2006-03-03 | 삼성전자주식회사 | 차동 및 직교 고조파 신호를 발생하는 전압 제어 발진기 |

| US20080043545A1 (en) * | 2004-04-29 | 2008-02-21 | Jan Vink | Multiple Data Rate Ram Memory Controller |

| KR100714586B1 (ko) | 2005-08-03 | 2007-05-07 | 삼성전기주식회사 | 듀티보정기능을 갖는 전압 제어 발진기 |

| CN100539428C (zh) * | 2007-03-12 | 2009-09-09 | 启攀微电子(上海)有限公司 | 一种高性能时间数字转换器电路架构 |

| JP4956460B2 (ja) * | 2008-02-14 | 2012-06-20 | 株式会社リコー | 電圧比較回路、その電圧比較回路を有する半導体集積回路及び電子機器 |

| US8810323B2 (en) * | 2012-01-26 | 2014-08-19 | Mohammad Ardehali | Low-power voltage-controlled oscillator |

| CN112383304B (zh) * | 2020-10-13 | 2021-06-08 | 华南理工大学 | 一种基于单极型薄膜晶体管的电荷泵锁相环、芯片及方法 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5475344A (en) * | 1994-02-22 | 1995-12-12 | The Board Of Trustees Of The Leland Stanford Junior University | Multiple interconnected ring oscillator circuit |

| US5576647A (en) * | 1995-06-22 | 1996-11-19 | Marvell Technology Group, Ltd. | Charge pump for phase lock loop |

-

1999

- 1999-02-10 JP JP03348899A patent/JP3616268B2/ja not_active Expired - Fee Related

-

2000

- 2000-02-07 US US09/498,993 patent/US6348839B1/en not_active Expired - Fee Related

- 2000-02-09 SG SG200000744A patent/SG88768A1/en unknown

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000232340A (ja) | 2000-08-22 |

| US6348839B1 (en) | 2002-02-19 |

| SG88768A1 (en) | 2002-05-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6476656B2 (en) | Low-power low-jitter variable delay timing circuit | |

| US6452458B1 (en) | Voltage-controlled oscillator | |

| US5847616A (en) | Embedded voltage controlled oscillator with minimum sensitivity to process and supply | |

| US6111445A (en) | Phase interpolator with noise immunity | |

| US6084452A (en) | Clock duty cycle control technique | |

| US5600280A (en) | Differential amplifier and variable delay stage for use in a voltage controlled oscillator | |

| US7298183B2 (en) | High frequency divider circuits and methods | |

| JP3260615B2 (ja) | 電圧制御発振器 | |

| US7126431B2 (en) | Differential delay cell having controllable amplitude output | |

| US20120075025A1 (en) | Oscillating circuit | |

| JP3616268B2 (ja) | リングオシレータ用遅延回路 | |

| KR20020025663A (ko) | 넓은 출력 주파수 범위를 갖는 전압 제어 발진 회로 및그것을 구비하는 위상 동기 루프 회로 | |

| WO1999037024A1 (en) | A variable delay cell with a self-biasing load | |

| CN205385473U (zh) | 一种延迟模块和多路环形振荡器 | |

| US6690242B2 (en) | Delay circuit with current steering output symmetry and supply voltage insensitivity | |

| CN109995363B (zh) | 一种自偏置结构的环形压控振荡器 | |

| KR20040007490A (ko) | 전압 제어 발진기를 위한 정출력 스윙 및 가변시간 지연을갖는 씨모스 회로 | |

| CN101425803A (zh) | 环路压控振荡器 | |

| JP2000077985A (ja) | 電圧制御発振器 | |

| KR100719987B1 (ko) | 발진기 | |

| US7642867B2 (en) | Simple technique for reduction of gain in a voltage controlled oscillator | |

| JPH0537307A (ja) | 電圧制御発振回路および位相同期ループ回路 | |

| JPH1093405A (ja) | コモンモード発振及び入力ヒステリシス防止用差分遅延要素 | |

| JP3119653B2 (ja) | 高チューニング性cmos遅延素子 | |

| KR100405935B1 (ko) | 이단으로 구성된 저전력 링 오실레이터 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20011121 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040730 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20041104 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20071112 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081112 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081112 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091112 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |