JP2022040150A - メモリシステムのための省電力化技法 - Google Patents

メモリシステムのための省電力化技法 Download PDFInfo

- Publication number

- JP2022040150A JP2022040150A JP2021207223A JP2021207223A JP2022040150A JP 2022040150 A JP2022040150 A JP 2022040150A JP 2021207223 A JP2021207223 A JP 2021207223A JP 2021207223 A JP2021207223 A JP 2021207223A JP 2022040150 A JP2022040150 A JP 2022040150A

- Authority

- JP

- Japan

- Prior art keywords

- data

- memory

- host processor

- memory system

- lanes

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/325—Power saving in peripheral device

- G06F1/3275—Power saving in memory, e.g. RAM, cache

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3206—Monitoring of events, devices or parameters that trigger a change in power modality

- G06F1/3215—Monitoring of peripheral devices

- G06F1/3225—Monitoring of peripheral devices of memory devices

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/325—Power saving in peripheral device

- G06F1/3278—Power saving in modem or I/O interface

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/06—Addressing a physical block of locations, e.g. base addressing, module addressing, memory dedication

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

- G06F13/1673—Details of memory controller using buffers

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4204—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus

- G06F13/4234—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus being a memory bus

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/0608—Saving storage space on storage systems

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/0625—Power saving in storage systems

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0655—Vertical data movement, i.e. input-output transfer; data movement between one or more hosts and one or more storage devices

- G06F3/0659—Command handling arrangements, e.g. command buffers, queues, command scheduling

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0673—Single storage device

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1006—Data managing, e.g. manipulating data before writing or reading out, data bus switches or control circuits therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/10—Aspects relating to interfaces of memory device to external buses

- G11C2207/102—Compression or decompression of data before storage

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

- Memory System (AREA)

- Bus Control (AREA)

- Power Sources (AREA)

Abstract

Description

本出願は、参照により内容全体が本明細書に組み込まれる、2016年3月3日出願の「POWER SAVING TECHNIQUES FOR MEMORY SYSTEMS」と題する米国仮特許出願第62/302,891号の優先権を主張する。

12 ホストプロセッサ

14 メモリシステム

16 デジタル信号プロセッサ(DSP)

18 マルチメディアエンジン

20 マルチコア中央処理ユニット(CPU)

22 メモリコントローラ

24 システムバス

26 メモリインターフェース物理層

28 メモリバス

30(1)~30(2) データレーンIOブロック

32 コマンド/アドレス/クロックブロック

34 デコーダおよびデータラッチ

36(1)~36(N) メモリバンク

200 コードスニペット

202、204 領域

210 データブロック

212、214 領域

300 データバースト

310 データブロック

312 スロットD0~D7

314 スロットD16~D23

316 スロットD24~D31

322、324 グループ

330 データブロック

332、334、336、338 グループ

400 コンピューティングデバイス

402 ホストプロセッサ

404 メモリシステム

406 DSP

408 GPUおよびマルチメディアエンジン

410 マルチコアCPU

412 メモリコントローラ

414 システムバス

416 メモリインターフェースPHY

418 メモリバス

420(1)~420(2) データレーンIOブロック

422 コマンド/アドレス/クロックブロック

424 デコーダおよびデータラッチ

426(1)~426(N) メモリバンク

430 データパターンチェッカー論理回路

432 メモリアドレスルックアップテーブル

434 読取りデータコピーレジスタ

436(1)~436(2) 書込みデータコピーレジスタ

500 コンピューティングデバイス

502 ホストプロセッサ

504 メモリシステム

520(1)~520(2) データレーンIOブロック

522 コマンド/アドレス/クロックブロック

524 デコーダおよびデータラッチ

526(1)~526(N) メモリバンク

528 内部書込みデータコピーレジスタ

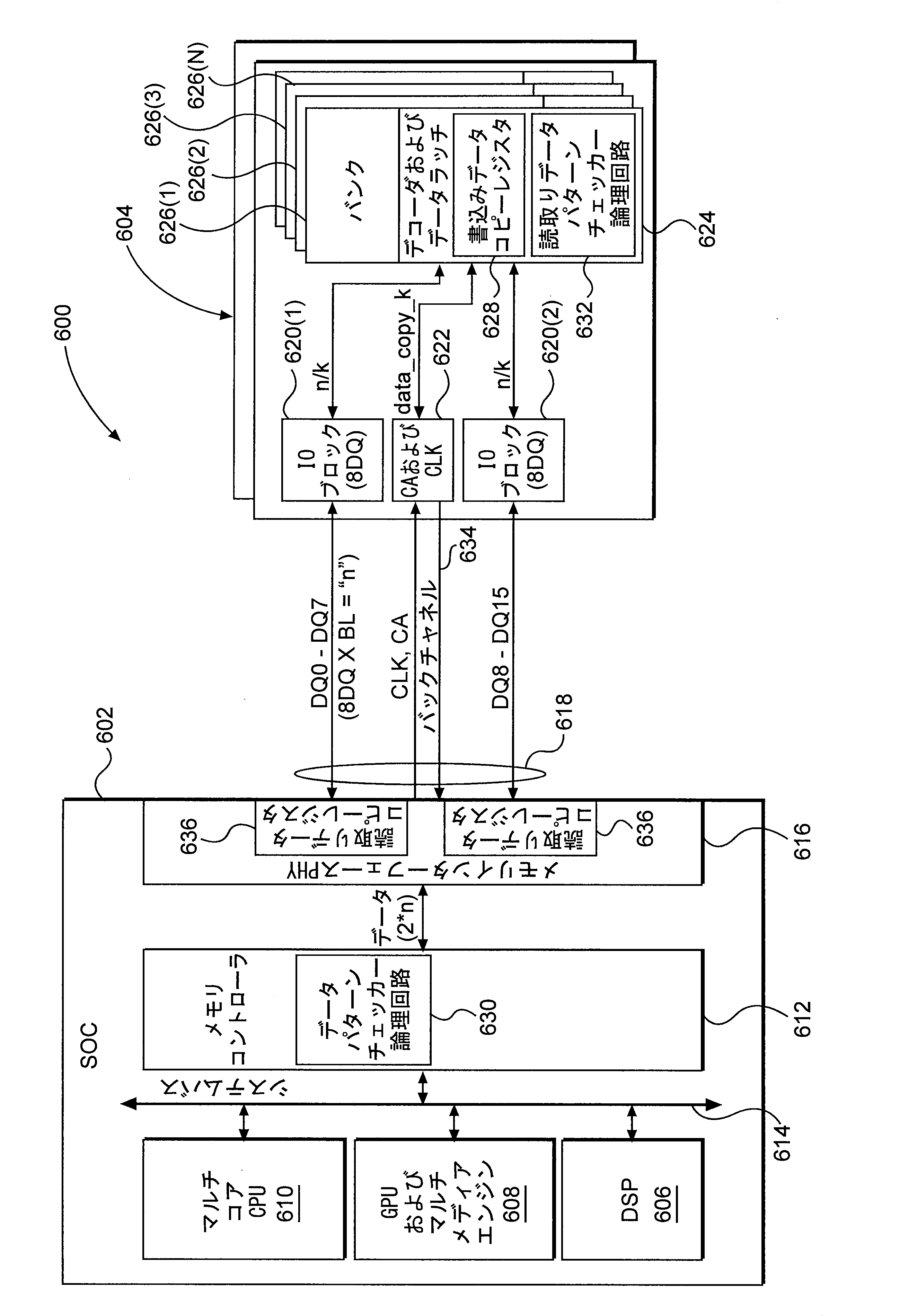

600 コンピューティングデバイス

602 ホストプロセッサ

604 メモリシステム

606 DSP

608 GPUおよびマルチメディアエンジン

610 マルチコアCPU

612 メモリコントローラ

614 システムバス

616 メモリインターフェースPHY

618 メモリバス

620(1)~620(2) データレーンIOブロック

622 コマンド/アドレス/クロックブロック

624 デコーダおよびデータラッチ

626(1)~626(N) メモリバンク

628 書込みデータコピーレジスタ

630 データパターンチェッカー論理回路

632 読取りデータパターンチェッカー論理回路

634 バックチャネルレーン

636 読取りデータコピーレジスタ

700 書込み動作プロセス

800 読取り動作プロセス

900 書込みデータパス

902 コマンドデコーダ

904 データコピー制御ブロック回路

906(1)~906(M) ゲーティング論理回路

908(1)~908(M) レジスタ

910 書込みデータ先入れ先出し(FIFO)バッファ

1000 データパターンチェッカー論理回路

1002 データバス

1004(1)~1004(8) バイトチェッカー

1006 パケットチェッカー

1008 制御論理

1102 通常の書込みコマンド

1104 通常の読取りコマンド

1106 修正された書込みコマンド

1108 修正された読取りコマンド

1400 プロセッサベースのシステム

1402 CPU

1404 プロセッサ

1406 キャッシュメモリ

1408 システムバス

1410 メモリコントローラ

1412 メモリシステム

1414 入力デバイス

1416 出力デバイス

1418 ネットワークインターフェースデバイス

1420 ディスプレイコントローラ

1422 ネットワーク

1424 ディスプレイ

1426 ビデオプロセッサ

C4~C9 列アドレス

CA0~CA5 レーン

D0~D127 スロット

DQ0~DQ15 データレーン

Claims (33)

- メモリバスの複数のデータレーンに結合されるように構成された物理層(PHY)インターフェースと、

前記PHYインターフェースに結合されたメモリコントローラであって、データパターンチェッカー論理回路を備え、

前記データパターンチェッカー論理回路を使用して、前記メモリバスを介してメモリ要素に書き込むべきデータに繰り返し可能なデータのパターンが存在するかどうかを判定し、

前記データをより少ないレーン内に統合し、前記データを前記メモリバスの前記複数のデータレーンのうちのいくつかのデータレーンのみを介して送る

ように構成された、メモリコントローラと

を備えるホストプロセッサ。 - 前記メモリコントローラは、ルックアップテーブルをさらに備え、前記メモリコントローラは、前記メモリ要素に書き込まれるデータに関するアドレス情報を前記ルックアップテーブルに書き込む、請求項1に記載のホストプロセッサ。

- 前記メモリコントローラは、前記ルックアップテーブルを使用して、統合された読取りコマンドが使用されてもよいように、前記メモリ要素から読み取られるデータが繰り返し可能なデータの前記パターンを有するかどうかを判定するように構成される、請求項2に記載のホストプロセッサ。

- 前記PHYインターフェースに結合された読取りデータコピーレジスタをさらに備え、前記読取りデータコピーレジスタは、読取りデータを複製するように構成される、請求項1に記載のホストプロセッサ。

- 前記メモリコントローラは、8つのレーンからの複製されたデータを1つのデータレーン上に統合するように構成される、請求項1に記載のホストプロセッサ。

- 前記メモリコントローラは、8つのレーンからの複製されたデータを2つまたは4つのデータレーン上に統合するように構成される、請求項1に記載のホストプロセッサ。

- 前記PHYインターフェースはバックチャネルレーンを備える、請求項1に記載のホストプロセッサ。

- 前記メモリコントローラは、前記メモリコントローラからのデータが統合されたデータであることの表示を受信するように構成される、請求項7に記載のホストプロセッサ。

- 集積回路(IC)に組み込まれた、請求項1に記載のホストプロセッサ。

- メモリバスに結合されるように構成された入出力(IO)ブロックと、

メモリ要素を備え、前記IOブロックに通信可能に結合されたメモリバンクと、

前記IOブロックを介して前記メモリバスからデータを受信し、ホストプロセッサからのコマンドに応じた回数だけ前記データを複製するように動作可能な書込みレジスタと

を備えるメモリシステム。 - 前記メモリバンクは、前記メモリ要素内の前記書込みレジスタからの前記複製されたデータを記憶するように構成される、請求項10に記載のメモリシステム。

- 前記メモリバンクに結合されたデータパターンチェッカー論理回路をさらに備える、請求項10に記載のメモリシステム。

- 前記データパターンチェッカー論理回路は、前記メモリ要素から読み取られたデータに繰り返し可能なデータのパターンが存在するかどうかを判定し、前記データをより少ないレーン内に統合し、前記メモリバスの複数のデータレーンのうちのいくつかのデータレーンのみを介して前記データを送るように構成される、請求項12に記載のメモリシステム。

- バックチャネルレーン出力をさらに含む、請求項10に記載のメモリシステム。

- 前記メモリシステムは、複製されたデータの表示をバックチャネルレーンを介して前記バックチャネルレーン出力によって前記ホストプロセッサに送るように構成される、請求項14に記載のメモリシステム。

- メモリバスの複数のデータレーンに結合されるように構成された物理層(PHY)インターフェースと、

読取りレジスタと、

前記PHYインターフェースに結合されたメモリコントローラであって、

前記PHYインターフェースを介してメモリシステムからデータを受信し、

前記メモリシステムから受信された情報に基づいて前記読取りレジスタ内のデータを複製させる

ように構成された、メモリコントローラと

を備えるホストプロセッサ。 - 前記メモリコントローラは、読取りコマンドに応答して前記メモリシステムから受信されたデータが統合されたデータであることの表示を受信するように構成される、請求項16に記載のホストプロセッサ。

- 前記メモリコントローラは、前記メモリバスのバックチャネルレーンを介して受信された情報に基づいて前記読取りレジスタ内の前記データを複製させる、請求項16に記載のホストプロセッサ。

- メモリバスに結合されるように構成された入出力(IO)ブロックと、

メモリ要素を備えるメモリバンクであって、前記IOブロックに通信可能に結合され、統合されたデータを前記メモリバスを介してホストプロセッサに送ることによって読取りコマンドに応答するように構成された、メモリバンクと

を備えるメモリシステム。 - 前記統合されたデータが前記読取りコマンドに応答して送られることを示す情報を前記ホストプロセッサに与えるように構成されたバックチャネル出力をさらに備える、請求項19に記載のメモリシステム。

- 前記メモリバンクに結合されたデータパターンチェッカー論理回路をさらに備える、請求項19に記載のメモリシステム。

- データパターンチェッカー論理回路は、前記ホストプロセッサに送られるデータに、前記統合されたデータとして統合される繰り返しがないかどうかを確認するように構成される、請求項21に記載のメモリシステム。

- 前記メモリシステムは、前記ホストプロセッサに送られる統合されたデータの表示を送るように構成される、請求項19に記載のメモリシステム。

- メモリコントローラと物理層(PHY)インターフェースとを備えるホストプロセッサと、

メモリシステムと、

メモリバスとを備え、前記ホストプロセッサは、前記メモリシステムに書き込むべきデータを前記PHYインターフェースおよび前記メモリバスを介して送り、

前記メモリコントローラは、データパターンチェッカー論理回路を備え、

前記データパターンチェッカー論理回路を使用して、前記メモリバスを介して前記メモリシステムに書き込むべき前記データに繰り返し可能なデータのパターンが存在するかどうかを判定し、

前記データを統合して前記メモリバスを介して送られるデータを減らす

ように動作可能である装置。 - 前記メモリコントローラは、ルックアップテーブルをさらに備え、前記メモリコントローラは、前記メモリシステムに書き込まれるデータに関するアドレス情報を前記ルックアップテーブルに書き込む、請求項24に記載の装置。

- 前記メモリコントローラは、8つのレーンからの複製されたデータを1つのデータレーン、2つのデータレーン、または4つのデータレーン上に統合するように構成される、請求項24に記載の装置。

- 前記メモリコントローラは、前記メモリバスを介して送られる前記データが統合されたデータであることの表示を前記メモリシステムに与えるようにさらに動作可能である、請求項24に記載の装置。

- セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、全地球測位システム(GPS)デバイス、モバイルフォン、セルラーフォン、スマートフォン、セッション開始プロトコル(SIP)フォン、タブレット、ファブレット、サーバ、コンピュータ、ポータブルコンピュータ、モバイルコンピューティングデバイス、装着型コンピューティングデバイス、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、ポータブルデジタルビデオプレーヤ、自動車、車両構成要素、アビオニクスシステム、ドローン、およびマルチコプターからなるグループから選択されたデバイスに組み込まれる、請求項24に記載の装置。

- メモリコントローラと物理層(PHY)インターフェースとを備えるホストプロセッサと、

メモリシステムと、

メモリバスとを備え、前記ホストプロセッサは、前記メモリシステムから読み取られたデータを前記PHYインターフェースおよび前記メモリバスを介して受信し、

前記メモリシステムは、前記メモリシステムから読み取られる前記データに繰り返し可能なデータのパターンが存在するかどうかを判定し、前記ホストプロセッサからの読取りコマンドに応答して前記データを統合して前記メモリバスを介して送られるデータを減らすように動作可能である装置。 - 前記統合されたデータが前記読取りコマンドに応答して送られることを示す情報を前記メモリシステムが前記ホストプロセッサに送るためのバックチャネルレーンをさらに備える、請求項29に記載の装置。

- 前記メモリシステムは、データパターンチェッカー論理回路をさらに備える、請求項29に記載の装置。

- 前記データパターンチェッカー論理回路は、前記ホストプロセッサに送られるデータに、前記統合されたデータとして統合される繰り返しがないかどうかを確認する、請求項31に記載の装置。

- 前記メモリシステムは、前記ホストプロセッサに送られる統合されたデータの表示を送る、請求項29に記載の装置。

Applications Claiming Priority (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201662302891P | 2016-03-03 | 2016-03-03 | |

| US62/302,891 | 2016-03-03 | ||

| US15/448,327 US10222853B2 (en) | 2016-03-03 | 2017-03-02 | Power saving techniques for memory systems by consolidating data in data lanes of a memory bus |

| US15/448,327 | 2017-03-02 | ||

| JP2018544830A JP6999565B2 (ja) | 2016-03-03 | 2017-03-03 | メモリシステムのための省電力化技法 |

| PCT/US2017/020582 WO2017152005A1 (en) | 2016-03-03 | 2017-03-03 | Power saving techniques for memory systems |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018544830A Division JP6999565B2 (ja) | 2016-03-03 | 2017-03-03 | メモリシステムのための省電力化技法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2022040150A true JP2022040150A (ja) | 2022-03-10 |

| JP7417576B2 JP7417576B2 (ja) | 2024-01-18 |

Family

ID=59722700

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018544830A Active JP6999565B2 (ja) | 2016-03-03 | 2017-03-03 | メモリシステムのための省電力化技法 |

| JP2021207223A Active JP7417576B2 (ja) | 2016-03-03 | 2021-12-21 | メモリシステムのための省電力化技法 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018544830A Active JP6999565B2 (ja) | 2016-03-03 | 2017-03-03 | メモリシステムのための省電力化技法 |

Country Status (9)

| Country | Link |

|---|---|

| US (2) | US10222853B2 (ja) |

| EP (1) | EP3423947B1 (ja) |

| JP (2) | JP6999565B2 (ja) |

| KR (1) | KR102420909B1 (ja) |

| CN (1) | CN108701099B (ja) |

| CA (1) | CA3013090A1 (ja) |

| ES (1) | ES2804604T3 (ja) |

| HU (1) | HUE049615T2 (ja) |

| WO (1) | WO2017152005A1 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10222853B2 (en) | 2016-03-03 | 2019-03-05 | Qualcomm Incorporated | Power saving techniques for memory systems by consolidating data in data lanes of a memory bus |

| US10394724B2 (en) * | 2016-08-22 | 2019-08-27 | Qualcomm Incorporated | Low power data transfer for memory subsystem using data pattern checker to determine when to suppress transfers based on specific patterns |

| KR20190035392A (ko) * | 2017-09-26 | 2019-04-03 | 삼성전자주식회사 | 데이터 다중 기록을 수행하는 메모리 장치, 메모리 장치의 동작방법 및 메모리 컨트롤러의 동작방법 |

| KR102731057B1 (ko) * | 2018-09-21 | 2024-11-15 | 삼성전자주식회사 | 메모리 장치와 통신하는 데이터 처리 장치 및 방법 |

| KR20200071396A (ko) * | 2018-12-11 | 2020-06-19 | 에스케이하이닉스 주식회사 | 반도체장치 및 반도체시스템 |

| KR102698036B1 (ko) * | 2019-04-10 | 2024-08-22 | 에스케이하이닉스 주식회사 | 반도체장치 |

| US11722152B1 (en) | 2020-11-25 | 2023-08-08 | Astera Labs, Inc. | Capacity-expanding memory control component |

| US12061793B1 (en) * | 2020-11-25 | 2024-08-13 | Astera Labs, Inc. | Capacity-expanding memory control component |

| KR20220135504A (ko) | 2021-03-30 | 2022-10-07 | 삼성전자주식회사 | 데이터 처리 시스템 및 데이터 처리 장치의 동작 방법 |

| US11785424B1 (en) | 2021-06-28 | 2023-10-10 | Wm Intellectual Property Holdings, L.L.C. | System and method for asset tracking for waste and recycling containers |

| CN116264085B (zh) * | 2021-12-14 | 2025-08-15 | 长鑫存储技术有限公司 | 存储系统以及存储系统的数据写入方法 |

| CN116264083B (zh) * | 2021-12-14 | 2025-08-15 | 长鑫存储技术有限公司 | 存储系统以及存储系统的数据读取方法 |

| US20230197123A1 (en) * | 2021-12-20 | 2023-06-22 | Advanced Micro Devices, Inc. | Method and apparatus for performing a simulated write operation |

| US11899598B2 (en) * | 2022-05-31 | 2024-02-13 | Western Digital Technologies, Inc. | Data storage device and method for lane selection based on thermal conditions |

| KR20240009813A (ko) | 2022-07-14 | 2024-01-23 | 삼성전자주식회사 | 단일 직렬 쓰기 인터페이싱 방식을 지원하는 스토리지 모듈 및 그것의 동작 방법 |

| US12356292B1 (en) | 2023-07-21 | 2025-07-08 | Wm Intellectual Property Holdings, L.L.C. | Apparatus and method for asset tracking for metal waste and recycling containers |

| US12277350B1 (en) | 2023-10-30 | 2025-04-15 | Astera Labs, Inc. | Virtual metadata storage |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1011360A (ja) * | 1996-06-24 | 1998-01-16 | Toshiba Corp | キャッシュメモリ |

| US7631207B1 (en) * | 2006-04-21 | 2009-12-08 | Sun Microsystems, Inc. | Reducing power consumption for processing of common values in microprocessor registers and execution units |

| WO2015042469A1 (en) * | 2013-09-20 | 2015-03-26 | Qualcomm Incorporated | System and method for conserving memory power using dynamic memory i/o resizing |

| US20150186282A1 (en) * | 2013-12-28 | 2015-07-02 | Saher Abu Rahme | Representing a cache line bit pattern via meta signaling |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7190284B1 (en) * | 1994-11-16 | 2007-03-13 | Dye Thomas A | Selective lossless, lossy, or no compression of data based on address range, data type, and/or requesting agent |

| JP2921505B2 (ja) * | 1996-08-09 | 1999-07-19 | 日本電気株式会社 | 半導体記憶装置 |

| US6009026A (en) * | 1997-07-28 | 1999-12-28 | International Business Machines Corporation | Compressed input/output test mode |

| US6145069A (en) * | 1999-01-29 | 2000-11-07 | Interactive Silicon, Inc. | Parallel decompression and compression system and method for improving storage density and access speed for non-volatile memory and embedded memory devices |

| US6785793B2 (en) | 2001-09-27 | 2004-08-31 | Intel Corporation | Method and apparatus for memory access scheduling to reduce memory access latency |

| US7383399B2 (en) * | 2004-06-30 | 2008-06-03 | Intel Corporation | Method and apparatus for memory compression |

| GB2457667B (en) | 2008-02-19 | 2012-01-11 | Advanced Risc Mach Ltd | Data transfer between devices within an integrated circuit |

| US8694703B2 (en) * | 2010-06-09 | 2014-04-08 | Brocade Communications Systems, Inc. | Hardware-accelerated lossless data compression |

| MX2013002773A (es) | 2010-09-16 | 2013-04-05 | Apple Inc | Controlador de memoria con multiples puertos con puertos asociados con las clases de trafico. |

| KR101854251B1 (ko) | 2010-11-30 | 2018-05-03 | 삼성전자주식회사 | 멀티 채널 반도체 메모리 장치 및 그를 구비하는 반도체 장치 |

| US9189394B2 (en) * | 2012-08-08 | 2015-11-17 | Wisconsin Alumni Research Foundation | Memory-link compression for graphic processor unit |

| JP2014053058A (ja) * | 2012-09-06 | 2014-03-20 | Toshiba Corp | 半導体記憶装置 |

| EP2979188A4 (en) | 2013-06-28 | 2016-12-07 | Hewlett Packard Entpr Dev Lp | MEMORY COMPONENT THAT MAY COMMUNICATE TO A PLURALITY OF DATA WIDTHS |

| US9568542B2 (en) * | 2013-09-25 | 2017-02-14 | Cavium, Inc. | Memory interface with integrated tester |

| US20150121111A1 (en) * | 2013-10-24 | 2015-04-30 | Qualcomm Incorporated | System and method for providing multi-user power saving codebook optmization |

| US9864536B2 (en) * | 2013-10-24 | 2018-01-09 | Qualcomm Incorporated | System and method for conserving power consumption in a memory system |

| KR102017808B1 (ko) | 2013-12-31 | 2019-09-03 | 에스케이하이닉스 주식회사 | 데이터 처리 장치 및 데이터 처리 방법 |

| CN103714026B (zh) * | 2014-01-14 | 2016-09-28 | 中国人民解放军国防科学技术大学 | 一种支持原址数据交换的存储器访问方法及装置 |

| KR102616804B1 (ko) * | 2015-05-21 | 2023-12-26 | 제로포인트 테크놀로지 에이비 | 시맨틱 값 데이터 압축 및 압축해제를 위한 방법, 장치 및 시스템 |

| US20170115900A1 (en) * | 2015-10-23 | 2017-04-27 | International Business Machines Corporation | Dummy page insertion for flexible page retirement in flash memory storing multiple bits per memory cell |

| US10222853B2 (en) * | 2016-03-03 | 2019-03-05 | Qualcomm Incorporated | Power saving techniques for memory systems by consolidating data in data lanes of a memory bus |

| US10394724B2 (en) * | 2016-08-22 | 2019-08-27 | Qualcomm Incorporated | Low power data transfer for memory subsystem using data pattern checker to determine when to suppress transfers based on specific patterns |

-

2017

- 2017-03-02 US US15/448,327 patent/US10222853B2/en active Active

- 2017-03-03 WO PCT/US2017/020582 patent/WO2017152005A1/en not_active Ceased

- 2017-03-03 HU HUE17711926A patent/HUE049615T2/hu unknown

- 2017-03-03 ES ES17711926T patent/ES2804604T3/es active Active

- 2017-03-03 CN CN201780013577.8A patent/CN108701099B/zh active Active

- 2017-03-03 CA CA3013090A patent/CA3013090A1/en not_active Abandoned

- 2017-03-03 KR KR1020187025182A patent/KR102420909B1/ko active Active

- 2017-03-03 EP EP17711926.0A patent/EP3423947B1/en active Active

- 2017-03-03 JP JP2018544830A patent/JP6999565B2/ja active Active

-

2019

- 2019-02-06 US US16/268,634 patent/US10852809B2/en active Active

-

2021

- 2021-12-21 JP JP2021207223A patent/JP7417576B2/ja active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1011360A (ja) * | 1996-06-24 | 1998-01-16 | Toshiba Corp | キャッシュメモリ |

| US7631207B1 (en) * | 2006-04-21 | 2009-12-08 | Sun Microsystems, Inc. | Reducing power consumption for processing of common values in microprocessor registers and execution units |

| WO2015042469A1 (en) * | 2013-09-20 | 2015-03-26 | Qualcomm Incorporated | System and method for conserving memory power using dynamic memory i/o resizing |

| US20150186282A1 (en) * | 2013-12-28 | 2015-07-02 | Saher Abu Rahme | Representing a cache line bit pattern via meta signaling |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2017152005A1 (en) | 2017-09-08 |

| JP7417576B2 (ja) | 2024-01-18 |

| CA3013090A1 (en) | 2017-09-08 |

| JP6999565B2 (ja) | 2022-01-18 |

| US20170255394A1 (en) | 2017-09-07 |

| US20190179399A1 (en) | 2019-06-13 |

| EP3423947A1 (en) | 2019-01-09 |

| JP2019507436A (ja) | 2019-03-14 |

| KR20180119584A (ko) | 2018-11-02 |

| CN108701099A (zh) | 2018-10-23 |

| KR102420909B1 (ko) | 2022-07-13 |

| HUE049615T2 (hu) | 2020-09-28 |

| EP3423947B1 (en) | 2020-04-22 |

| ES2804604T3 (es) | 2021-02-08 |

| US10222853B2 (en) | 2019-03-05 |

| US10852809B2 (en) | 2020-12-01 |

| BR112018067531A2 (pt) | 2019-01-02 |

| CN108701099B (zh) | 2022-05-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7417576B2 (ja) | メモリシステムのための省電力化技法 | |

| US7907470B2 (en) | Multi-column addressing mode memory system including an integrated circuit memory device | |

| US7636272B2 (en) | Multi-port memory device | |

| CN109964213B (zh) | 在基于处理器的系统中提供经扩展动态随机存取存储器突发长度 | |

| CN114365225B (zh) | 具有系统ecc的存储器 | |

| US20160224414A1 (en) | DUAL IN-LINE MEMORY MODULES (DIMMs) SUPPORTING STORAGE OF A DATA INDICATOR(S) IN AN ERROR CORRECTING CODE (ECC) STORAGE UNIT DEDICATED TO STORING AN ECC | |

| KR20130119545A (ko) | 메모리 장치, 메모리 컨트롤러, 메모리 시스템 및 이의 동작 방법 | |

| US10236917B2 (en) | Providing memory bandwidth compression in chipkill-correct memory architectures | |

| CN102282619B (zh) | 用以在ddr dram写入期间三态控制未使用数据字节的方法、系统及设备 | |

| US10156887B2 (en) | Cache memory clock generation circuits for reducing power consumption and read errors in cache memory | |

| CN110720126B (zh) | 传输数据掩码的方法、内存控制器、内存芯片和计算机系统 | |

| CN101568970B (zh) | 存储器装置、存储系统及用于存储系统的方法 | |

| CN100354814C (zh) | 存储器写入方法与控制装置 | |

| US12047302B2 (en) | Data encoding and packet sharing in a parallel communication interface | |

| BR112018067531B1 (pt) | Processador hospedeiro e sistema de memória |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220119 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20220119 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20230403 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230523 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20230911 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20231114 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20231211 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20240105 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7417576 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |