JP2015515225A - 加速されたビデオ圧縮マルチタップフィルタおよび双線形補間器 - Google Patents

加速されたビデオ圧縮マルチタップフィルタおよび双線形補間器 Download PDFInfo

- Publication number

- JP2015515225A JP2015515225A JP2015507184A JP2015507184A JP2015515225A JP 2015515225 A JP2015515225 A JP 2015515225A JP 2015507184 A JP2015507184 A JP 2015507184A JP 2015507184 A JP2015507184 A JP 2015507184A JP 2015515225 A JP2015515225 A JP 2015515225A

- Authority

- JP

- Japan

- Prior art keywords

- pixels

- interpolated

- numbered

- odd

- subpixels

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 230000006835 compression Effects 0.000 title description 3

- 238000007906 compression Methods 0.000 title description 3

- 238000000034 method Methods 0.000 claims description 72

- 238000004891 communication Methods 0.000 claims description 9

- 239000004065 semiconductor Substances 0.000 claims description 8

- 230000008569 process Effects 0.000 description 32

- 238000010586 diagram Methods 0.000 description 14

- 208000033986 Device capturing issue Diseases 0.000 description 10

- 230000006870 function Effects 0.000 description 6

- 238000012545 processing Methods 0.000 description 6

- 239000013598 vector Substances 0.000 description 6

- 230000008859 change Effects 0.000 description 4

- 238000013461 design Methods 0.000 description 4

- 238000009825 accumulation Methods 0.000 description 3

- 230000009471 action Effects 0.000 description 3

- 230000008878 coupling Effects 0.000 description 3

- 238000010168 coupling process Methods 0.000 description 3

- 238000005859 coupling reaction Methods 0.000 description 3

- 238000006073 displacement reaction Methods 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 238000005070 sampling Methods 0.000 description 3

- 238000012935 Averaging Methods 0.000 description 2

- 241000023320 Luma <angiosperm> Species 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- OSWPMRLSEDHDFF-UHFFFAOYSA-N methyl salicylate Chemical compound COC(=O)C1=CC=CC=C1O OSWPMRLSEDHDFF-UHFFFAOYSA-N 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 241000272878 Apodiformes Species 0.000 description 1

- 125000002066 L-histidyl group Chemical group [H]N1C([H])=NC(C([H])([H])[C@](C(=O)[*])([H])N([H])[H])=C1[H] 0.000 description 1

- 230000003466 anti-cipated effect Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 238000012512 characterization method Methods 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000006249 magnetic particle Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/50—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using predictive coding

- H04N19/503—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using predictive coding involving temporal prediction

- H04N19/51—Motion estimation or motion compensation

- H04N19/523—Motion estimation or motion compensation with sub-pixel accuracy

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/42—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals characterised by implementation details or hardware specially adapted for video compression or decompression, e.g. dedicated software implementation

- H04N19/43—Hardware specially adapted for motion estimation or compensation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/80—Details of filtering operations specially adapted for video compression, e.g. for pixel interpolation

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Image Processing (AREA)

- Compression Or Coding Systems Of Tv Signals (AREA)

Abstract

Description

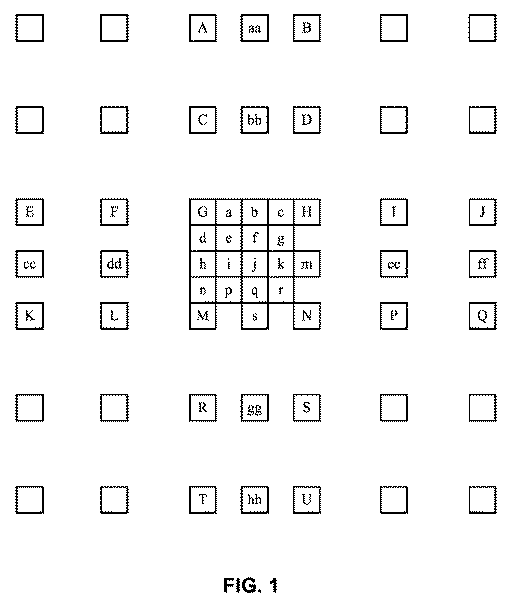

j1=cc-5dd+20h1+20m1-5ee+ff Eq. (5)

によって得られてよく、cc、dd、ee、m1、およびffによって示される中間値は、h1と同様の方式で得られる。そして、最終予測値jは、

j=(j1+512)>>10 Eq. (6)

として計算され、0〜255nの範囲にとどめられ得る。

a=(G+b+1)>>1 Eq. (7)

として、整数サンプル位置および1/2サンプル位置における2つの最も近いサンプルの上方丸めを伴って平均することによって導出される。

e=(b+h+1)>>1 Eq. (8)

として、対角方向にある1/2サンプル位置における最も近い2つのサンプルを上方丸めを伴って平均することによって導出される。

202 ピクセルウィンドウレジスタ

204 乗算器

206 タップ係数セットレジスタ

208 加算デバイス

210 累算器

212 2Sビットの符号付き飽和論理

300 ステップ移行のグラフィカルなモデル

302 ピクセルウィンドウ

402 状態

406 状態

410 内容

502 状態

572 領域

602 状態

606 状態

610 内容

672 領域

702 状態

772 領域

802 状態

806 状態

872 領域

902 状態

972 領域

1100 入力

1102_0 ピクセル行セクション

1102_2 ピクセル行セクション

1200 インターリーブされたクロマ成分の構成

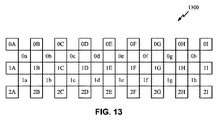

1300 ピクセルのアレイ

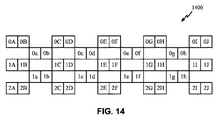

1400 ピクセルのアレイ

1500 ワイヤレス通信システム

1520 リモートユニット

1525 半導体デバイス

1530 リモートユニット

1535 半導体デバイス

1540 基地局

1550 リモートユニット

1555 半導体デバイス

1580 順方向リンク信号

1590 逆方向リンク信号

Claims (23)

- ピクセルアレイに対する補間されたピクセルを生成するための方法であって、

前記ピクセルアレイからのピクセルのウィンドウレジスタと、所与のタップ係数セットを有するタップ係数レジスタとに基づいて、偶数番目の補間されたサブピクセルのセットを形成するステップと、

別の前記ピクセルによって前記ウィンドウレジスタを更新するステップと、

前記ウィンドウレジスタと前記タップ係数レジスタとに基づいて、奇数番目の補間されたサブピクセルのセットを形成するステップと、

所与の終了条件が満たされるまで、前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを累算するステップであって、各累算するステップが、

別のタップ係数セットに基づいて前記タップ係数レジスタを更新し、別の前記ピクセルによって前記ウィンドウレジスタを更新するステップと、

前記ウィンドウレジスタと前記タップ係数レジスタとに基づいて、前記偶数番目の補間されたサブピクセルをインクリメントするステップと、

別の前記ピクセルによって前記ウィンドウレジスタを再び更新するステップと、

前記ウィンドウレジスタと前記タップ係数レジスタとに基づいて、前記奇数番目の補間されたサブピクセルをインクリメントするステップと

を含む、累算するステップと、

前記終了条件が満たされると、偶数番目の補間されたサブピクセルの前記セットおよび奇数番目の補間されたサブピクセルの前記セットを出力するステップとを含む、方法。 - 前記終了条件が、前記偶数番目の補間されたピクセルの少なくとも1つが6個の積の合計を有することに対応する、請求項1に記載の方法。

- 偶数番目の補間されたサブピクセルの前記セットを形成するステップが、単一のマシンサイクルの間に行われ、奇数番目の補間されたサブピクセルの前記セットを形成するステップが、単一のマシンサイクルの間に行われる、請求項1に記載の方法。

- 偶数番目の補間されたサブピクセルの前記セットを形成するステップが、4個の偶数番目の補間されたサブピクセルを含むように前記セットを形成し、前記4個の偶数番目の補間されたサブピクセルの各々が2個の積の合計を有し、奇数番目の補間されたサブピクセルの前記セットを形成するステップが、4個の奇数番目の補間されたサブピクセルを含むように前記セットを形成し、前記4個の奇数番目の補間されたサブピクセルの各々が、対応する2個の積の合計を有する、請求項3に記載の方法。

- 前記偶数番目の補間されたサブピクセルをインクリメントする各ステップが、別の対応する2個の積の合計によって、前記4個の偶数番目の補間されたサブピクセルの各々をインクリメントするステップを含み、

前記奇数番目の補間されたサブピクセルをインクリメントする各ステップが、別の対応する2個の積の合計によって、前記4個の奇数番目の補間されたサブピクセルの各々をインクリメントするステップを含む、請求項4に記載の方法。 - 前記タップ係数レジスタを更新し、前記ウィンドウレジスタを更新するステップが、前記偶数番目の補間されたサブピクセルをインクリメントするステップと組み合わされて、単一のマシンサイクルの間に行われ、前記奇数番目の補間されたサブピクセルをインクリメントするステップと組み合わされた、前記ウィンドウレジスタを再び更新する前記ステップが、単一のマシンサイクルの間に行われる、請求項5に記載の方法。

- 前記偶数番目の補間されたサブピクセルを形成するステップが、少なくとも4個の偶数番目の補間されたサブピクセルを形成し、前記4個の偶数番目の補間されたサブピクセルの各々が2個の積の合計を有し、

前記奇数番目の補間されたサブピクセルを形成するステップが、少なくとも4個の奇数番目の補間されたサブピクセルを形成し、前記4個の奇数番目の補間されたサブピクセルの各々が、対応する2個の積の合計を有し、

前記偶数番目の補間されたサブピクセルをインクリメントする各ステップが、別の対応する2個の積の合計によって、前記4個の偶数番目の補間されたサブピクセルの各々をインクリメントするステップを含み、

前記奇数番目の補間されたサブピクセルをインクリメントする各ステップが、別の対応する2個の積の合計によって、前記4個の奇数番目の補間されたサブピクセルの各々をインクリメントするステップを含む、請求項1に記載の方法。 - 前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを2回累算すると、前記終了条件が満たされる、請求項1に記載の方法。

- 前記偶数番目の補間されたサブピクセルを形成するステップが、ウィンドウからのピクセルを、前記タップ係数セットからの対応するタップ係数と乗算して、対応する積の合計を生成するステップと、積の前記合計のペアを合計して積の合計のセットを生成するステップと、積の合計の前記セットを、偶数番目の補間されたサブピクセルの前記セットとして累算器へとロードするステップと、偶数番目の補間されたサブピクセルの前記セットを、累算器レジスタからメモリへとオフロードするステップとを含み、

前記奇数番目の補間されたサブピクセルを形成するステップが、前記更新されたウィンドウからのピクセルを、前記タップ係数セットからの対応するタップ係数と乗算して、対応する積の合計を生成するステップと、積の前記合計のペアを合計して積の合計のセットを生成するステップと、積の合計の前記セットを、奇数番目の補間されたサブピクセルの前記セットとして前記累算器へとロードするステップと、奇数番目の補間されたサブピクセルの前記セットを、前記累算器レジスタから前記メモリへとオフロードするステップとを含む、請求項1に記載の方法。 - 偶数番目の補間されたサブピクセルの前記セットを形成するステップが、単一のマシンサイクルの間に行われ、奇数番目の補間されたサブピクセルの前記セットを形成するステップが、単一のマシンサイクルの間に行われる、請求項9に記載の方法。

- 前記偶数番目の補間されたサブピクセルをインクリメントする各ステップが、偶数番目の補間されたサブピクセルの前記セットを前記メモリから前記累算器レジスタへとロードするステップと、前記更新されたウィンドウからのピクセルを、前記更新されたタップ係数セットからの対応するタップ係数と乗算して、対応する積の合計を生成するステップと、積の前記合計のペアを前記累算器レジスタからの対応する偶数番目の補間されたサブピクセルと合計して、累算された積の合計のセットを生成するステップと、累算された積の合計の前記セットを、偶数番目の補間されたサブピクセルの更新されたセットとして前記累算器レジスタへとロードするステップと、偶数番目の補間されたサブピクセルの前記セットを、前記累算器レジスタから前記メモリへとオフロードするステップとを含み、

前記奇数番目の補間されたサブピクセルをインクリメントする各ステップが、奇数番目の補間されたサブピクセルの前記セットを前記メモリから前記累算器レジスタへとロードするステップと、別の更新されたウィンドウからのピクセルを、前記タップ係数セットからの対応するタップ係数と乗算して、対応する積の合計を生成するステップと、積の前記合計のペアを前記累算器レジスタからの対応する奇数番目の補間されたサブピクセルと合計して、累算された積の合計のセットを生成するステップと、累算された積の合計の前記セットを、奇数番目の補間されたサブピクセルの更新されたセットとして前記累算器レジスタへとロードするステップと、奇数番目の補間されたサブピクセルの前記セットを、前記累算器レジスタから前記メモリへとオフロードするステップとを含む、請求項9に記載の方法。 - 偶数番目の補間されたサブピクセルの前記セットをインクリメントするステップが、単一のマシンサイクルの間に行われ、奇数番目の補間されたサブピクセルの前記セットをインクリメントするステップが、単一のマシンサイクルの間に行われる、請求項11に記載の方法。

- ピクセルアレイに対する補間されたピクセルを生成するための装置であって、

前記ピクセルアレイからのピクセルのウィンドウと、所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットを形成するための手段と、

別の前記ピクセルによって前記ウィンドウを更新するための手段と、

ピクセルの前記ウィンドウと、前記所与のタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットを形成するための手段と、

所与の終了条件が満たされるまで、前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを累算するための手段であって、

前記タップ係数セットを更新して別の前記ピクセルによって前記ウィンドウを更新し、

ピクセルの前記ウィンドウと前記タップ係数セットとに基づいて、前記偶数番目の補間されたサブピクセルをインクリメントし、

別の前記ピクセルによってピクセルの前記ウィンドウを更新し、

ピクセルの前記ウィンドウと前記タップ係数セットとに基づいて、前記奇数番目の補間されたサブピクセルをインクリメントする

ように構成される、手段と、

前記所与の終了条件が満たされると、前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを出力するための手段とを含む、装置。 - 偶数番目の補間されたサブピクセルの前記セットを形成するための前記手段が、4個の偶数番目の補間されたサブピクセルを含むように前記セットを形成するように構成され、前記4個の偶数番目の補間されたサブピクセルの各々が2個の積の合計を有し、

奇数番目の補間されたサブピクセルの前記セットを形成するための前記手段が、4個の奇数番目の補間されたサブピクセルを含むように前記セットを形成するように構成され、前記4個の奇数番目の補間されたサブピクセルの各々が、対応する2個の積の合計を有する、請求項13に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。 - 前記偶数番目のサブピクセルおよび前記奇数番目の補間されたサブピクセルを累算するための前記手段が、前記4個の偶数番目の補間されたサブピクセルの各々を、別の対応する2個の積の合計によってインクリメントすることによって、前記偶数番目の補間されたサブピクセルをインクリメントし、前記4個の奇数番目の補間されたサブピクセルの各々を、別の対応する2個の積の合計によってインクリメントすることによって、前記奇数番目の補間されたサブピクセルをインクリメントするように構成される、請求項14に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

- 少なくとも1つの半導体ダイにおいて集積される、請求項13に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

- セットトップボックス、音楽プレーヤ、ビデオプレーヤ、娯楽ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータからなる群から選択されるデバイスをさらに含み、前記デバイスに前記装置が組み込まれる、請求項13に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

- ワイヤレス通信システム中のプロセッサ装置によって実行されると、プロセッサ装置に、ピクセルアレイに対する補間されたピクセルを生成するための方法を実施する動作を実行させる命令を含む、コンピュータ可読記録媒体であって、前記プロセッサ装置に、

前記ピクセルアレイからのピクセルのウィンドウと、所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットを形成させ、

別の前記ピクセルによって前記ウィンドウを更新させ、

ピクセルの前記ウィンドウと、前記所与のタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットを形成させ、

所与の終了条件が満たされるまで、偶数番目の補間されたサブピクセルおよび奇数番目の補間されたサブピクセルの前記セットを累算させる命令を含み、前記命令が、前記プロセッサ装置に、

前記タップ係数セットを更新して別の前記ピクセルによってピクセルの前記ウィンドウを更新し、

ピクセルの前記ウィンドウおよび前記タップ係数セットに基づいて、前記偶数番目の補間されたサブピクセルをインクリメントし、

別の前記ピクセルによってピクセルの前記ウィンドウを再び更新し、

ピクセルの前記ウィンドウと前記タップ係数セットとに基づいて、前記奇数番目の補間されたサブピクセルをインクリメントする

ことによって累算させ、

前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを出力させる、コンピュータ可読記録媒体。 - 前記プロセッサ装置に、偶数番目の補間されたサブピクセルの前記セットを形成させる前記命令が、前記プロセッサ装置に、4個の偶数番目の補間されたサブピクセルを含むように前記セットを形成させ、前記4個の偶数番目の補間されたサブピクセルの各々が2個の積の合計を有し、前記プロセッサ装置に、奇数番目の補間されたサブピクセルの前記セットを形成させる前記命令が、前記プロセッサ装置に、4個の奇数番目の補間されたサブピクセルを含むように前記セットを形成させ、前記4個の奇数番目の補間されたサブピクセルの各々が、対応する2個の積の合計を有する、請求項18に記載のコンピュータ可読記録媒体。

- 前記プロセッサ装置に、前記偶数番目の補間されたサブピクセルをインクリメントさせる前記命令が、前記プロセッサ装置に、前記4個の偶数番目の補間されたサブピクセルの各々を、別の対応する2個の積の合計によってインクリメントさせ、

前記プロセッサ装置に、前記奇数番目の補間されたサブピクセルをインクリメントさせる前記命令が、前記プロセッサ装置に、前記4個の奇数番目の補間されたサブピクセルの各々を、別の対応する2個の積の合計によってインクリメントさせ、

前記奇数番目の補間されたサブピクセルをインクリメントする各ステップが、別の対応する2個の積の合計によって、前記4個の奇数番目の補間されたサブピクセルの各々をインクリメントするステップを含む、請求項18に記載のコンピュータ可読記録媒体。 - ピクセルアレイからのピクセルを受け取るための入力を有する論理回路を含む、ピクセルアレイに対する補間されたピクセルを生成するための装置であって、前記論理回路が、

前記ピクセルアレイからのピクセルのウィンドウと、所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットを形成し、

別の前記ピクセルによって前記ウィンドウを更新し、

ピクセルの前記ウィンドウと、前記所与のタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットを形成し、

所与の終了条件が満たされるまで、前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを累算するように構成され、前記論理回路が、

前記タップ係数セットを更新して前記別のピクセルによって前記ウィンドウを更新し、

ピクセルの前記ウィンドウおよび前記タップ係数セットに基づいて、前記偶数番目の補間されたサブピクセルをインクリメントし、

別の前記ピクセルによってピクセルの前記ウィンドウを更新し、

ピクセルの前記ウィンドウと前記タップ係数セットとに基づいて、前記奇数番目の補間されたサブピクセルをインクリメントする

ことによって累算し、

前記所与の終了条件が満たされると、前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを出力するように構成される、装置。 - 前記論理回路が少なくとも1つの半導体ダイにおいて集積される、請求項21に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

- セットトップボックス、音楽プレーヤ、ビデオプレーヤ、娯楽ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータからなる群から選択されるデバイスをさらに含み、前記デバイスに前記論理回路が組み込まれる、請求項21に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/450,734 | 2012-04-19 | ||

| US13/450,734 US8855446B2 (en) | 2012-04-19 | 2012-04-19 | Accelerated video compression multi-tap filter and bilinear interpolator |

| PCT/US2013/037206 WO2013158903A1 (en) | 2012-04-19 | 2013-04-18 | Accelerated multi-tap filter and bilinear interpolator for video compression |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015515225A true JP2015515225A (ja) | 2015-05-21 |

| JP2015515225A5 JP2015515225A5 (ja) | 2016-06-02 |

| JP6382795B2 JP6382795B2 (ja) | 2018-08-29 |

Family

ID=48325888

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015507184A Expired - Fee Related JP6382795B2 (ja) | 2012-04-19 | 2013-04-18 | 加速されたビデオ圧縮マルチタップフィルタおよび双線形補間器 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8855446B2 (ja) |

| EP (1) | EP2839650A1 (ja) |

| JP (1) | JP6382795B2 (ja) |

| CN (1) | CN104247435B (ja) |

| WO (1) | WO2013158903A1 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11409525B2 (en) * | 2018-01-24 | 2022-08-09 | Intel Corporation | Apparatus and method for vector multiply and accumulate of packed words |

| CN108322759B (zh) * | 2018-02-24 | 2021-02-05 | 北京奇艺世纪科技有限公司 | 一种像素值获取方法、装置及电子设备 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10124656A (ja) * | 1996-10-18 | 1998-05-15 | Sony Corp | 画像処理装置および方法 |

| EP1605704A2 (en) * | 2004-05-28 | 2005-12-14 | Samsung Electronics Co., Ltd. | Image interpolation apparatus and methods |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5500811A (en) | 1995-01-23 | 1996-03-19 | Microunity Systems Engineering, Inc. | Finite impulse response filter |

| US6470370B2 (en) | 1995-09-05 | 2002-10-22 | Intel Corporation | Method and apparatus for multiplying and accumulating complex numbers in a digital filter |

| US6188803B1 (en) | 1996-10-18 | 2001-02-13 | Sony Corporation | Image processing device |

| US6061521A (en) | 1996-12-02 | 2000-05-09 | Compaq Computer Corp. | Computer having multimedia operations executable as two distinct sets of operations within a single instruction cycle |

| US6175592B1 (en) | 1997-03-12 | 2001-01-16 | Matsushita Electric Industrial Co., Ltd. | Frequency domain filtering for down conversion of a DCT encoded picture |

| US8463837B2 (en) | 2001-10-29 | 2013-06-11 | Intel Corporation | Method and apparatus for efficient bi-linear interpolation and motion compensation |

| CN101616330B (zh) * | 2003-07-16 | 2012-07-04 | 三星电子株式会社 | 用于色彩图像的视频编码/解码装置和方法 |

| CN100455025C (zh) * | 2005-07-21 | 2009-01-21 | 华为技术有限公司 | 一种分数像素插值方法和编解码设备 |

| CN101009842B (zh) * | 2006-01-11 | 2012-02-01 | 华为技术有限公司 | 可分级视频压缩中插值的方法与装置 |

| CN101938644A (zh) * | 2009-07-03 | 2011-01-05 | 哈尔滨工业大学深圳研究生院 | 视频压缩1/2像素精度运动估计硬件实现方法 |

-

2012

- 2012-04-19 US US13/450,734 patent/US8855446B2/en not_active Expired - Fee Related

-

2013

- 2013-04-18 CN CN201380020605.0A patent/CN104247435B/zh not_active Expired - Fee Related

- 2013-04-18 WO PCT/US2013/037206 patent/WO2013158903A1/en not_active Ceased

- 2013-04-18 EP EP13721171.0A patent/EP2839650A1/en not_active Withdrawn

- 2013-04-18 JP JP2015507184A patent/JP6382795B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10124656A (ja) * | 1996-10-18 | 1998-05-15 | Sony Corp | 画像処理装置および方法 |

| EP1605704A2 (en) * | 2004-05-28 | 2005-12-14 | Samsung Electronics Co., Ltd. | Image interpolation apparatus and methods |

Non-Patent Citations (1)

| Title |

|---|

| JUYUP LEE(外2名): "H.264 DECODER OPTIMIZATION EXPLOITING SIMD INSTRUCTIONS", CIRCUITS AND SYSTEMS, 2004. PROCEEDINGS. THE 2004 IEEE ASIA-PACIFIC CONFERENCE ON, JPN6017015061, 6 December 2004 (2004-12-06), US, pages 1149 - 1152, XP010783438, DOI: doi:10.1109/APCCAS.2004.1413088 * |

Also Published As

| Publication number | Publication date |

|---|---|

| US8855446B2 (en) | 2014-10-07 |

| WO2013158903A1 (en) | 2013-10-24 |

| CN104247435A (zh) | 2014-12-24 |

| US20130279827A1 (en) | 2013-10-24 |

| EP2839650A1 (en) | 2015-02-25 |

| CN104247435B (zh) | 2018-03-30 |

| JP6382795B2 (ja) | 2018-08-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP1120747A2 (en) | Motion estimator | |

| KR101578052B1 (ko) | 움직임 추정 장치 및 이를 구비하는 동영상 부호화 장치 | |

| EP2528320B1 (en) | Image processing device, imaging device, program, and image processing method | |

| US9210341B2 (en) | Image processing device, imaging device, information storage medium, and image processing method | |

| JP4837615B2 (ja) | 画像処理方法および画像処理装置 | |

| US20090016634A1 (en) | Half pixel interpolator for video motion estimation accelerator | |

| KR101354659B1 (ko) | 멀티 코덱을 지원하는 움직임 보상 방법 및 장치 | |

| JP6382795B2 (ja) | 加速されたビデオ圧縮マルチタップフィルタおよび双線形補間器 | |

| JP4406892B1 (ja) | 繰り返しオブジェクト検出装置及び方法 | |

| JP4824703B2 (ja) | 2次元フィルタ演算装置及び方法 | |

| JP2009015637A (ja) | 演算ユニット及び画像フィルタリング装置 | |

| EP1605704A2 (en) | Image interpolation apparatus and methods | |

| JP2007096431A (ja) | 任意の変換比率を有するデジタル・ビデオ・フォーマット下方変換装置及び方法 | |

| Wu et al. | Efficient hierarchical motion estimation algorithm and its VLSI architecture | |

| Celebi et al. | An all binary sub-pixel motion estimation approach and its hardware architecture | |

| JP2009239698A (ja) | 映像変換装置及び映像変換方法 | |

| Jung et al. | A 4-way pipelined processing architecture for three-step search block-matching motion estimation | |

| KR101059649B1 (ko) | 적응적 보간 필터를 이용한 부호화 장치, 그 방법 및 복호화 장치 | |

| JP2002509627A (ja) | 半ピクセルsad発生方法及び装置 | |

| US10397579B2 (en) | Sampling rate converter | |

| EP1056295A1 (en) | Filter arithmetic device | |

| KR101428531B1 (ko) | 움직임 벡터의 정규화 및 윤곽선의 패턴 분석을 이용한 복수 영상 기반 초해상도 영상 생성 방법 | |

| Tasdizen et al. | A high performance reconfigurable motion estimation hardware architecture | |

| RU2308817C1 (ru) | Способ и устройство масштабирования динамического видеоизображения | |

| JP4972321B2 (ja) | 時間リカレンスを表す画像のシーケンスにおけるピクセルをスキャンする方法及び装置及び参照フレームに関して現在のフレームの動きを推定するための方法及び装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A529 | Written submission of copy of amendment under article 34 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A529 Effective date: 20141020 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160404 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160404 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170324 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170508 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170621 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20171211 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180307 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180709 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180802 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6382795 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |