JP2015041996A - 増幅回路 - Google Patents

増幅回路 Download PDFInfo

- Publication number

- JP2015041996A JP2015041996A JP2013173858A JP2013173858A JP2015041996A JP 2015041996 A JP2015041996 A JP 2015041996A JP 2013173858 A JP2013173858 A JP 2013173858A JP 2013173858 A JP2013173858 A JP 2013173858A JP 2015041996 A JP2015041996 A JP 2015041996A

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- voltage

- node

- switching power

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 230000003321 amplification Effects 0.000 title abstract description 16

- 238000003199 nucleic acid amplification method Methods 0.000 title abstract description 16

- 238000010586 diagram Methods 0.000 description 30

- 239000003990 capacitor Substances 0.000 description 17

- 230000000052 comparative effect Effects 0.000 description 14

- 238000000034 method Methods 0.000 description 13

- 238000001514 detection method Methods 0.000 description 8

- 230000001360 synchronised effect Effects 0.000 description 6

- 230000007423 decrease Effects 0.000 description 4

- 238000009499 grossing Methods 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- 150000004767 nitrides Chemical class 0.000 description 2

- 229910002704 AlGaN Inorganic materials 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000001172 regenerating effect Effects 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

Images

Landscapes

- Amplifiers (AREA)

Abstract

【課題】増幅回路を高効率化すること。【解決手段】入力信号のエンベロープに追従する電圧を第1ノードN1に出力するリニア電源14と、前記第1ノードに接続された低電圧側および高電圧側のいずれか一方の電源端子と、電源に接続された前記低電圧側および高電圧側の他方の電源端子と、を有するスイッチング電源12と、前記リニア電源の出力する電力と前記スイッチング電源が出力する電力とが合成された電力が前記第1ノードから電源電力として供給され、入力信号を増幅する増幅部10と、を具備する増幅回路。【選択図】図1

Description

本発明は、増幅回路に関し、例えば入力信号のエンベロープ信号に基づき増幅部の電源電圧を変調する増幅回路に関する。

高出力の高周波増幅回路において、高効率化する方法としてエンベロープトラッキング方式がある。エンベロープトラッキング方式は入力信号のエンベロープに基づき増幅段の電源電圧を変調する方式である。

エンベロープトラッキング方式増幅回路において、電源電圧の変調にスイッチング電源を用いることにより高効率化が可能となる。しかしながら、さらなる高効率化が求められている。

本発明は、上記課題に鑑みなされたものであり、増幅回路を高効率化することを目的とする。

本発明は、入力信号のエンベロープに追従する電圧を第1ノードに出力するリニア電源と、前記第1ノードに接続された低電圧側および高電圧側のいずれか一方の電源端子と、電源に接続された前記低電圧側および高電圧側の他方の電源端子と、を有するスイッチング電源と、前記リニア電源の出力する電力と前記スイッチング電源が出力する電力とが合成された電力が前記第1ノードから電源電力として供給され、入力信号を増幅する増幅部と、を具備することを特徴とする増幅回路である。

上記構成において、前記スイッチング電源を、前記リニア電源の出力電流が所定電流以下となるように制御する制御回路を具備する構成とすることができる。

上記構成において、前記スイッチング電源の出力電流が負帰還される構成とすることができる。

上記構成において、前記リニア電源の出力電流に対応する第1信号と参照電位とを差動増幅する第1差動増幅回路と、前記第1差動増幅回路の出力信号と前記昇圧型スイッチング電源の出力電流に対応する第2信号とを差動増幅し、前記昇圧型スイッチング電源に出力する第2差動増幅回路と、を具備する構成とすることができる。

上記構成において、前記スイッチング電源は昇圧型スイッチング電源であり、前記スイッチング電源の出力端子は、前記低電圧側および高電圧側の前記他方の電源端子に接続されている構成とすることができる。

上記構成において、前記スイッチング電源は降圧型スイッチング電源であり、前記スイッチング電源の出力端子は、前記第1ノードに接続されている構成とすることができる。

上記構成において、前記スイッチング電源は、前記高電圧側の電源端子と前記低電圧側の電源端子との間に直列に接続された第1スイッチと、前記高電圧側の電源端子と前記低電圧側の電源端子との間に前記第1スイッチと直列に接続されたインダクタと、を備える構成とすることができる。

上記構成において、前記スイッチング電源は、前記第1スイッチと前記出力端子との間の第2ノードと、前記昇圧型スイッチング電源の出力端子と、の間に、前記第2ノードの電圧が前記昇圧型スイッチング電源の出力端子の電圧より低いときオフし、高いときオンする第2スイッチを備える構成とすることができる。

上記構成において、前記スイッチング電源は、前記高電圧側の電源端子と第2ノードとの間に直列に接続された第1スイッチと、前記第2ノードと前記低電圧側の電源端子との間に直接に接続された第2スイッチと、前記第2ノードと出力端子との間に直列に接続されたインダクタと、を備える構成とすることができる。

上記構成において、前記第2スイッチは、前記第2ノードの電圧が前記低電圧側の電源端子より低いときオンし、高いときオフする構成とすることができる。

本発明によれば、増幅回路を高効率化することができる。

以下、図面を参照し本発明の実施例について説明する。

図1は、実施例1に係る増幅回路のブロック図である。図1に示すように、増幅回路100は、最終増幅部10、ドライバ増幅部11、昇圧型スイッチング電源12、リニア電源14、エンベロープ検出回路16、制御回路18および抵抗Rsを備えている。入力端子から高周波入力信号VRFが入力する。ドライバ増幅部11は、入力信号を増幅する。最終増幅部10は、ドライバ増幅部11が増幅した入力信号を増幅し、出力信号として出力する。エンベロープ検出回路16は入力信号VRFのエンベロープ(包絡線)を検出し、エンベロープ信号Venvを出力する。リニア電源14はエンベロープ信号Venvに対応した電圧を生成し出力電圧VLおよび出力電流ILをノードN1(第1ノード)に出力する。昇圧型スイッチング電源12は、低電圧側の電源端子がノードN1に接続され、高電圧側の電源端子が電源Vccに接続され、出力端子が高電圧側の電源端子に接続されている。抵抗RsがノードN1とリニア電源14の出力端子との間に接続されている。昇圧型スイッチング電源12は、出力端子の電圧Vswを電源Vccより若干高くする。これにより、昇圧型スイッチング電源12の出力端子から高電圧側の電源端子、低電圧側の電源端子を介しノードN1に電流Iswが流れる。制御回路18は、抵抗Rsの両端の電位差からリニア電源14の出力電流ILを検出し、リニア電源14の出力電流ILが所定電流値以下となるように昇圧型スイッチング電源12を制御する。ノードN1は、最終増幅部10の電源端子に接続されている。ノードN1の電圧Vdは、ほぼ電圧VLとなる。電圧VLが最終増幅部10の電源端子に印加される。電流ILとIswとが合成され最終増幅部10の電源端子に供給される。すなわち、リニア電源14の出力する電力とスイッチング電源12が出力する電力とが合成された電力が第1ノードから最終増幅部10に供給される。

エンベロープトラッキング方式増幅回路においては、増幅部10の電源電圧をエンベロープ信号を用い変調することにより、高効率化が可能となる。リニア電源14は、エンベロープ信号に高速に追従し電源電圧を変調できる。しかし、リニア電源14は、効率が悪い。スイッチング電源12は、高効率であるがエンベロープ信号に高速に追従することが難しい。エンベロープ信号が高速に変化するときは主にリニア電源14により増幅部10に電源電力を供給する。エンベロープ信号が低速に変化するときは主にスイッチング電源12により増幅部10に電源電力を供給する。これにより、高速なエンベロープ信号に応答可能であり、かつ高効率な増幅回路となる。例えば携帯電話通信の基地局用増幅回路においては、エンベロープ信号の大部分は低速である。よって、増幅回路100はより高効率となる。

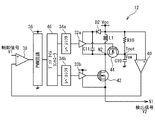

図2は、実施例1における増幅回路の一部を示す回路図である。図2に示すように、リニア電源14は、差動増幅回路20とトランジスタ22を備えている。差動増幅回路20の正入力端子にエンベロープ信号Venvが入力し、負入力端子にリニア電源14の出力端子が接続される。トランジスタ22は、n型MOSFET(Metal Oxide Semiconductor Field Effect Transistor)である。トランジスタ22のゲート(制御端子)に差動増幅回路20の出力端子が接続される。トランジスタ22のソースがリニア電源14の出力端子に接続され、ドレインが電源に接続される。差動増幅回路20は、出力端子の電圧がエンベロープ信号Venvに対応して変調されるように、トランジスタ22を制御する。トランジスタ22がオンすることにより、リニア電源14は大きな電流ILを出力することができる。

制御回路18は、差動増幅回路24、26、抵抗R1からR4および参照電源Vrefを備えている。抵抗Rsのリニア電源14側のノードとグランドとの間に抵抗R1およびR2が直列に接続されている。抵抗R1とR2との間のノードが差動増幅回路24の正入力端子に接続されている。抵抗RsのノードN1側のノードが抵抗R3を介し差動増幅回路24の負入力端子に接続されている。差動増幅回路24の出力端子が抵抗R4を介し負入力端子に接続されている。差動増幅回路24は、抵抗Rsの両端の電位差を増幅して出力する。抵抗R1からR4を設定することにより増幅率を設定できる。差動増幅回路26の正入力端子に差動増幅回路24の出力が入力する。差動増幅回路26の負入力端子に参照電圧が入力する。差動増幅回路26は、抵抗Rsを流れる電流ILと所定値との差に比例する制御信号V1をスイッチング電源12に出力する。このように、制御回路18は、電流ILが大きくなると大きな制御信号V1を出力する。

最終増幅部10は、トランジスタ28、キャパシタC1からC3およびスタブ29を備えている。トランジスタ28は、例えば窒化物半導体を用いたHEMT(High Electron Mobility Transistor)等のFETである。窒化物半導体を用いたHEMTは、例えば基板上に形成されたGaNチャネル層と、チャネル層上に形成されたAlGaN電子供給層を有する。トランジスタ28のソースはグランドに接続されている。ゲートにはキャパシタC2を介し入力信号が入力する。ドレインからキャパシタC3を介し出力信号が出力される。キャパシタC2およびC3は、直流カットキャパシタである。ドレインはさらにスタブ29を介し増幅部10の電源端子に接続される。電源端子はキャパシタC1を介し接地される。キャパシタC1はバイバルコンデンサである。スタブ29はチョーク用素子である。増幅部10は、GaAs系半導体を用いたFETでもよいし、FET以外のトランジスタを含んでもよい。

図3は、実施例1の昇圧型スイッチング電源の回路図である。図3に示すように、スイッチング電源12は、FET30(第1スイッチ)、ゲートドライバ32、レベルシフタ34、PWM(Pulse Width Modulation)回路36、差動増幅回路38および40、ダイオードD1、キャパシタC10、インダクタL1、並びに抵抗R10を備えている。FET30は、例えばn型MOSFETである。

FET30のドレインがノードN2(第2ノード)に、ソースが低電圧側の電源端子を介しノードN1に、ゲートがゲートドライバ32に接続されている。インダクタL1の一端が電源Vccに、他端がノードN2に接続されている。ダイオードD1のカソードが出力端子Toutに、アノードがノードN2に接続されている。ダイオードD1(第2スイッチ)は、出力端子Toutの電圧がノードN2より低いときに、出力端子ToutからノードN2に電流が流れることを抑制し、出力端子Toutの電圧がノードN2より高いときに、ノードN2から出力端子Toutに電流を流す。キャパシタC10は、平滑コンデンサであり、電荷を蓄積し、出力端子の電圧を電源Vccより昇圧する。ゲートドライバ32の負電源端子はノードN1に、正電源端子は電源Vccに接続されている。

抵抗R10は、出力端子Toutと正電圧側の電源端子との間に接続されている。差動増幅回路40は、抵抗R10の両端の電位差を差動増幅し検出信号V2を出力する。これにより、抵抗R10を流れる電流を検出できる。

差動増幅回路38は、検出信号V2と制御信号V1とを差動増幅する。PWM回路36は、差動増幅回路38の出力をPWM処理し、PWM信号に変換する。PWM回路36は、差動増幅回路38の出力に応じPWM信号のデュティ比を変える。例えば、差動増幅回路38の出力が高いときは、デュティ比を高くする。レベルシフタ34は、PWM信号をFET30を駆動するのに適した電圧または振幅に変換し、FET30のゲートにPWM信号を出力する。

検出信号V2が制御信号V1より小さいと、出力電流Iswが大きくなるようにスイッチング電源12が制御される。制御信号V1は、リニア電源14の出力電流ILと所定値との差に比例する。リニア電源14の出力電流ILとスイッチング電源12の出力電流Iswの和が増幅部10に供給される電流Idである。よって、スイッチング電源12は、リニア電源14の出力電流ILが所定電流値以下となるように、出力電流Iswを大きくする。スイッチング電源12が出力電圧Vswを高くするように制御されれば、出力電流Iswが大きくなる。

以上により、エンベロープ信号の変化が速く、スイッチング電源12がエンベロープ信号に追従できない場合は、応答速度の速いリニア電源14が増幅部10に主に電力を供給する。エンベロープ信号の変化は遅く、スイッチング電源12がエンベロープ信号に追従できる場合は、応答速度は遅いが効率のよいスイッチング電源12が増幅部10に主に電力を供給する。これにより、応答が速くかつ高効率な増幅回路を実現できる。

図3では、非同期整流方式を例に説明したが同期整流方式でもよい。また、FET30としてn型FETを例に説明したが、p型FETでもよい。さらに、FET30は、FET以外のスイッチでもよい。

図4は、昇圧型スイッチング電源の別の例の回路図である。図4に示すように、スイッチング電源12は、同期整流方式の昇圧型スイッチング電源である。電源VccとノードN2との間にインダクタL1が接続されている。FET42(第1スイッチ)のソースがノードN1に、ドレインがノードN2に、ゲートがゲートドライバ32bに接続されている。FET44(第2スイッチ)のソースがノードN2に、ドレインが出力端子Toutに、ゲートがゲートドライバ32aに接続されている。FET42および44は、n型MOSFETである。デッドタイムコントローラ46は、PWM信号を調整してゲートドライバ32aおよび32bにPWM信号を出力する。レベルシフタ34aおよび34bは、PWM信号の電圧または振幅を変換する。その他の構成は図3と同じであり説明を省略する。

図4では、同期整流方式を例に説明したが非同期整流方式でもよい。また、FET42および44としてn型FETを例に説明したが、p型FETでもよい。さらに、FET42および44は、FET以外のスイッチでもよい。

図3および図4に示すように、昇圧型スイッチング電源12において、FET30または42(第1スイッチ)は、電源Vcc(高電圧側の電源端子)とノードN1(低電圧側の電源端子)との間に直列に接続されている。インダクタL1は、電源VccとノードN1との間にFET30または42と直列に接続されている。このように、FET30または42は、ノードN2とノードN1との間に接続されていてもよい。これにより、ノードN2の電圧を電源Vccより昇圧できる。

また、昇圧型スイッチング電源12において、ダイオードD1またはFET44(第2スイッチ)は、ノードN2と出力端子Toutとの間に接続されている。ダイオードD1またはFET44は、ノードN2の電圧が出力端子Toutの電圧より低いときオフし、高いときオンする。これにより、出力端子Toutの電圧がノードN2より高くなっても、電流が出力端子からノードN2に逆流することを抑制できる。

図5(a)および図5(b)は、時間に対する入力信号VRFおよびエンベロープ信号Venvをそれぞれ示す図である。図5(a)に示すように、時間t0とt1との間の期間T1において、入力信号VRFの振幅は小さい。時間t1とt2との間の期間T2において、入力信号VRFの振幅は期間T1より大きくなる。時間t2とt3との間の期間T3において、入力信号VRFの振幅は期間T2よりさらに大きくなる。時間t3とt4との間の期間T4において、入力信号VRFの振幅は期間T1と同程度となる。図5(b)に示すように、エンベロープ信号Venvは、入力信号VRFのエンベロープに対応する。例えば、期間T1およびT4において、エンベロープ信号は1Vであり、期間T2においてエンベロープ信号は1.5Vであり、期間T3においてエンベロープ信号は3.0Vである。なお、説明を簡略化するため、各期間T1からT4における入力信号VRFの振幅をほぼ一定としているが、時間より変化していてもよい。

図6(a)から図6(c)は、リニア電源の出力電圧、出力電流および出力電力をそれぞれ示す図である。図6(a)に示すように、リニア電源14は、エンベロープ信号Venvに追従して出力電圧VLを出力する。リニア電源14は高速な追従が可能であり、期間T1、T2、T3およびT4において出力電圧をそれぞれ10V、30V、50Vおよび10Vとする。なお、電源Vccの電圧は55Vである。図6(b)に示すように、リニア電源14の出力電流ILは、時間t1、t2およびt3直後は大きくなるが、その後小さくなる。これは、制御回路18が電流ILが小さくなるようにスイッチング電源12を制御するためである。図6(c)に示すように、出力電力PLは、時間t1、t2およびt3直後は大きくなるが、その後小さくなる。

図7(a)から図7(c)は、スイッチング電源のノードN2における電圧、電流および電力をそれぞれ示す図である。図7(a)に示すように、リニア期間T1およびT4において、電圧VswのローレベルはノードN1の電圧である10Vであり、ハイレベルは、50Vよりやや高い電圧である。デュティ比は、小さい。リニア期間T2において、電圧VswのローレベルはノードN1の電圧である30Vであり、ハイレベルは、50Vよりやや高い電圧である。デュティ比は、期間T1より大きくなる。リニア期間T3において、電圧VswのローレベルはノードN1の電圧である50Vであり、ハイレベルは、50Vよりやや高い電圧である。デュティ比は、期間T2よりさらに大きくなる。

図7(b)に示すように、期間T1およびT4において電流Iswは小さい。期間T2において、電圧VLが大きくなると、電流ILが大きくなる(図6(b)参照)。制御回路18は、電流Iswが大きくなるように昇圧型スイッチング電源12を制御する。これにより、電流Iswが大きくなる。期間T3において、電圧VLが大きくなると、電流Iswはさらに大きくなる。電流Iswは、スイッチングに応じ上下する。

図7(c)に示すように、スイッチング電源12は電源VccとノードN1との間に接続されているため、スイッチング電源12が消費する電力Pswは、電圧VswとノードN1との電圧(ほぼ電圧VLとなる)の差と、電流Iswの積となる。期間T1およびT4において、電圧Vswと電圧VLとの差は約40Vと大きいが、電流Iswが小さいため、スイッチング電源12が供給する電力Pswは小さい。期間T2において、電圧Vswと電圧VLとの差は約20Vと小さくなるが、電流Iswが大きくなり電力Pswは大きくなる。期間T3において、電流Iswは大きくなるが、電圧Vswと電圧VLとの差は約0Vと小さくなるため、電力Pswは小さくなる。

図8(a)から図8(c)は、スイッチング電源の出力電圧、出力電流および出力電力をそれぞれ示す図である。スイッチング電源12の出力電圧Vsw_avg、出力電流Isw_avgおよび出力電力Psw_avgは、ノードN2の電圧Vsw、電流Iswおよび電力PswがキャパシタC10により平滑化されたものである。図8(a)を参照し、期間T1およびT4におけるスイッチング電源の出力電圧Vsw_avgは、約10Vである。期間T2における電圧Vsw_avgは、時間t1から大きくなり、約30Vとなる。期間T3における電圧Vsw_avgは、時間t2から大きくなり、約50Vとなる。図8(b)に示すように、期間T1およびT4においてスイッチング電源12の出力電流Isw_avgは、小さい。期間T2における電流Isw_avgは、時間t1から大きくなり、一定となる。期間T3における電流Isw_avgは、時間t2から大きくなり、一定となる。図8(c)に示すように、期間T1、T3およびT4におけるスイッチング電源の出力電力Psw_avgは、小さい。期間T2における出力電力Psw_avgは若干大きい。

図9(a)から図9(c)は、電源部の電源端子に供給される電圧、電流および電力をそれぞれ示す図である。図9(a)に示すように、増幅部10の電源端子の電圧Vdは、ほぼ電圧VLと同じである。期間T1、T2、T3およびT4における電圧Vdは、それぞれほぼ10V、30V、50V、10Vであり、各期間内でほぼ一定である。図9(b)に示すように、増幅部10の電源端子に供給される電流Idは、ほぼ電流ILとIswの和となる。期間T1からT4における電流Idはほぼ一定である。図9(c)に示すように、増幅部10の電源端子に供給される電力Pdは、電圧Vdと電流ILとの積となる。

以上のように、図6(a)および図6(b)に示す入力信号VRFのエンベロープ信号Venvに応じ、図9(a)のように増幅部10の電源端子の電圧Vdを変調できる。エンベロープ信号Venvの変化が高速な場合、図6(b)および図6(c)の時間t1からt3の直後のように応答速度の速いリニア電源14が増幅部10に電流および電力を供給する。エンベロープ信号Venvの変化が低速な場合、図8(b)および図8(c)のように応答速度が遅いが効率のよいスイッチング電源12が増幅部10に電流および電力を供給する。

以下、比較例1と比較し、実施例1に係る増幅回路がさらに高効率化できることを説明する。図10は、比較例1に係る増幅回路のブロック図である。図10に示すように、降圧型スイッチング電源12aがグランドと電源Vccとの間に接続されている。降圧型スイッチング電源12aは電源Vccの電圧を降圧してノードN1に出力する。制御回路18は、電流ILが小さくなるように降圧型スイッチング電源12aを制御する。その他の構成は実施例1と同じであり説明を省略する。

入力信号VRF、エンベロープ信号Venv、リニア電源14の出力電圧VL、出力電流IL、出力電力PL、増幅部10に供給される電圧Vd、電流Idおよび電力Pdは、実施例1における図5(a)から図6(c)、図9(a)から図9(c)とそれぞれほぼ同じであり、説明を省略する。

図11(a)から図11(c)は、比較例1におけるスイッチング電源の中間ノードの電圧、電流および電力をそれぞれ示す図である。図11(a)に示すように、スイッチング電源12aの中間ノードの電圧Vswのローレベルは0Vであり、ハイレベルは電源Vccの電圧である。期間T1およびT4における出力電圧Vswのデュティ比は小さい。期間T2における出力電圧Vswのデュティ比は大きい。期間T3における出力電圧Vswのデュティ比はさらに大きい。図11(b)に示すように、スイッチング電源12の中間ノードの電流Iswは、実施例1と同様である。図11(c)に示すように、期間T1およびT4における中間ノードの電力Pswは小さい。期間T2における電力Pswは大きい。期間T3における出力電力Pswはさらに大きい。

図12(a)から図12(c)は、比較例1におけるスイッチング電源の出力電圧、出力電流および出力電力をそれぞれ示す図である。スイッチング電源12aの出力電圧Vsw_avg、出力電流Isw_avgおよび出力電力Psw_avgは、中間ノードの電圧Vsw、電流Iswおよび電力Pswが平滑回路により平滑化されたものである。図12(a)に示すように、期間T1からT4におけるスイッチング電源12aの出力電圧Vsw_avgは、約10V、30V、50Vおよび10Vである。図12(b)に示すように、期間T1およびT4においてスイッチング電源12の出力電流Isw_avgは小さい。期間T2における電流Isw_avgは、時間t1から大きくなり、一定となる。期間T3における電流Isw_avgは、時間t2から大きくなり、一定となる。図12(c)を参照し、期間T1およびT4におけるスイッチング電源の出力電力Psw_avgは小さい。期間T2における出力電力Psw_avgは大きい。期間T3における出力電力Psw_avgはさらに大きい。

比較例1においては、降圧型スイッチング電源12aがグランドと電源Vccとの間に接続されている。これにより、降圧型スイッチング電源12aの消費電力Pswは、電圧Vswと電流Iswの積となる。よって、電圧Vswが高くなると、消費電力Pswも大きくなる。一方、実施例1においては、昇圧型スイッチング電源12がノードN1と電源Vccとの間に接続されている。これにより、昇圧型スイッチング電源12の消費電力Pswは、電圧Vswが電圧Vccの近くでも小さくなる。よって、期間T3における消費電力Pswを比較例1より小さくできる。これは、比較例1において電源VccとノードN1との間で無駄になる電力を、実施例1において回生電流として電源Vccに流し込むためである。

例えば、比較例1における降圧型スイッチング電源12aの効率が95%とする。比較例1では、図11(c)のように電圧Vdが最大のとき電力損失が最も大きい。そこで、最大電力が50V×4A=200Wとする。このとき、降圧型スイッチング電源12aによる損失は、200W×0.05=10Wとなる。

一方、非同期整流方式の昇圧型スイッチング電源12の効率は降圧型スイッチング電源より悪く90%とする。実施例1では、図7(c)のように電圧Vdが中程度のとき電力損出が最も大きい。そこで、電力が25V×2A=50Wとする。このとき、昇圧型スイッチング電源12による損失は、50W×0.1=5Wとなる。さらに、同期整流方式の昇圧型スイッチング電源12を用いることによりスイッチング電源の効率が95%となると、昇圧型スイッチング電源12による損失は、2.5Wとなる。

このように、実施例1によれば、昇圧型スイッチング電源12の低電圧側の電源端子がノードN1に、高電圧側の電源端子が電源Vccに、出力端子が電源Vccに接続されている。スイッチング電源12の低電圧側の電源端子がノードN1に電流を供給する。これにより、比較例1に比べ、スイッチング電源による電力損失を抑制できる。また、昇圧型スイッチング電源12の出力電力が比較例1の降圧型スイッチング電源12aより小さいため、インダクタL1および/またはキャパシタC10として許容電力が小さな部品を用いることができる。よって、スイッチング電源12の低コスト化および小型化が可能となる。なお、ノードN1に接続されるのは低電圧側および高電圧側のいずれか一方であればよく、電源Vccに接続されるのは低電圧側および高電圧側の他方であればよい。

制御回路18は、昇圧型スイッチング電源12を、リニア電源14の出力電流ILが所定電流以下となるように制御する。これにより、効率の高いスイッチング電源12が増幅部10に電力を供給できる。

また、スイッチング電源12の出力電流Iswが負帰還される。これにより、スイッチング電源12の出力電流Iswを制御できる。

図2の差動増幅回路26(第1差動増幅回路)がリニア電源14の出力電流ILに対応する出力(第1信号)と参照電位とを差動増幅し、制御信号V1を出力する。図3の差動増幅回路38(第2差動増幅回路)が制御信号とスイッチング電源12の出力電流Iswに対応する検出信号(第2信号)とを差動増幅し、スイッチング電源12に出力する。これにより、スイッチング電源12の出力電流Iswを制御できる。

図13は、実施例2に係る増幅回路を示すブロック図である。増幅回路102においては、降圧型スイッチング電源12bが用いられている。降圧型スイッチング電源12bの低電圧側の電源端子はノードN1に接続され、高電圧側の電源端子は電源Vccに接続されている。出力端子はノードN1に接続されている。

図14は、実施例2の降圧型スイッチング電源の回路図である。図14に示すように、降圧型スイッチング電源12bは非同期整流方式である。ダイオードD1のカソードがノードN2に、アノードがノードN1に接続されている。ダイオードD1は、ノードN2の電圧がノードN1より高いときに、ノードN2からノードN1に電流が流れることを抑制し、ノードN2の電圧がノードN1より低いときに、ノードN1からノードN2に電流を流す。インダクタL1の一端がノードN2に、他端が出力端子Toutに接続されている。キャパシタC10の一端が出力端子Toutに、他端がノードN1に接続されている。インダクタL1およびキャパシタC10は、ノードN2の電圧を平滑化して出力端子Toutに出力する。

ゲートドライバ32の負電源端子はノードN2に、正電源端子はダイオードD2を逆方向に介し電源Vccに接続されている。正電源端子とノードN2との間にキャパシタC11が接続されている。ダイオードD2およびキャパシタC11はゲートドライバ32の正電圧端子の電圧を生成するブートストラップ回路として機能を有する。FET30がp型FETの場合、ブートストラップ回路は設けなくてもよい。

抵抗R10は、出力端子ToutとノードN1との間に接続されている。差動増幅回路40は、抵抗R10の両端の電位差を差動増幅し検出信号V2を出力する。これにより、抵抗R10を流れる電流を検出できる。その他の構成は実施例1の図3と同じであり説明を省略する。

図15は、降圧型スイッチング電源の別の例の回路図である。図15に示すように、降圧型スイッチング電源12bは、同期整流方式である。FET31のドレインがノードN2に、ソースがノードN1に、ゲートがゲートドライバ32bに接続されている。その他の構成は、図14と同じであり説明を省略する。

図14および図15のように、降圧型スイッチング電源12bは、非同期整流方式でもよいし、同期整流方式でもよい。また、FET30、31としてn型FETを例に説明したが、p型FETでもよい。さらに、FET30、31は、FET以外のスイッチでもよい。

図14および図15に示すように、FET30(第1スイッチ)は、電源Vcc(高圧側の電源端子)とノードN2との間に直列に接続されている。FET31またはダイオードD1(第2スイッチ)は、ノードN2とノードN1(低電圧側の電源端子)との間に直接に接続されている。インダクタL1は、ノードN2と出力端子Toutとの間に直列に接続されている。これにより、ノードN2の電圧を電源Vccより降圧できる。

FET31またはダイオードD1は、ノードN2の電圧がノードN1より低いときオンし、高いときオフする。これにより、ノードN2からN1に電流が逆流することを抑制できる。

実施例2によれば、降圧型スイッチング電源12bの低電圧側の電源端子をノードN1に、高電圧側の電源端子を電源Vccに、出力端子ToutをノードN1に接続する。そして、降圧型スイッチング電源12bの出力電圧をノードN1の電圧Vdより少し高くする。これにより、最終増幅段10に供給される電流Idのほとんどをスイッチング電源12bの出力電流Iswとすることができる。

これにより、エンベロープ信号の変化が速い場合は、応答速度の速いリニア電源14が増幅部10に主に電力を供給する。エンベロープ信号の変化が遅い場合は、応答速度は遅いが効率のよいスイッチング電源12bが増幅部10に主に電力を供給する。これにより、応答が速くかつ高効率な増幅回路を実現できる。

このように、実施例1の昇圧型スイッチング電源12を降圧型スイッチング電源12bとし、低電圧側の電源端子と出力端子をノードN1に接続してもよい。

以上、本発明の実施例について詳述したが、本発明は係る特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

10 増幅部

12、12b スイッチング電源

14 リニア電源

16 エンベロープ検出回路

18 制御回路

30、31、42、44 FET

26、38 差動増幅回路

12、12b スイッチング電源

14 リニア電源

16 エンベロープ検出回路

18 制御回路

30、31、42、44 FET

26、38 差動増幅回路

Claims (10)

- 入力信号のエンベロープに追従する電圧を第1ノードに出力するリニア電源と、

前記第1ノードに接続された低電圧側および高電圧側のいずれか一方の電源端子と、電源に接続された前記低電圧側および高電圧側の他方の電源端子と、を有するスイッチング電源と、

前記リニア電源の出力する電力と前記スイッチング電源が出力する電力とが合成された電力が前記第1ノードから電源電力として供給され、入力信号を増幅する増幅部と、

を具備することを特徴とする増幅回路。 - 前記スイッチング電源を、前記リニア電源の出力電流が所定電流以下となるように制御する制御回路を具備することを特徴とする請求項1記載の増幅回路。

- 前記スイッチング電源の出力電流が負帰還されることを特徴とする請求項1または2記載の増幅回路。

- 前記リニア電源の出力電流に対応する第1信号と参照電位とを差動増幅する第1差動増幅回路と、

前記第1差動増幅回路の出力信号と前記スイッチング電源の出力電流に対応する第2信号とを差動増幅し、前記スイッチング電源に出力する第2差動増幅回路と、

を具備することを特徴とする請求項1から3のいずれか一項記載の増幅回路。 - 前記スイッチング電源は昇圧型スイッチング電源であり、前記スイッチング電源の出力端子は、前記低電圧側および高電圧側の前記他方の電源端子に接続されていることを特徴とする請求項1から4のいずれか一項記載の増幅回路。

- 前記スイッチング電源は降圧型スイッチング電源であり、前記スイッチング電源の出力端子は、前記第1ノードに接続されていることを特徴とする請求項1から4のいずれか一項記載の増幅回路。

- 前記スイッチング電源は、前記高電圧側の電源端子と前記低電圧側の電源端子との間に直列に接続された第1スイッチと、前記高電圧側の電源端子と前記低電圧側の電源端子との間に前記第1スイッチと直列に接続されたインダクタと、を備えることを特徴とする請求項5記載の増幅回路。

- 前記スイッチング電源は、前記第1スイッチと前記出力端子との間の第2ノードと、前記スイッチング電源の出力端子と、の間に、前記第2ノードの電圧が前記スイッチング電源の出力端子の電圧より低いときオフし、高いときオンする第2スイッチを備えることを特徴とする請求項7記載の増幅回路。

- 前記スイッチング電源は、前記高電圧側の電源端子と第2ノードとの間に直列に接続された第1スイッチと、前記第2ノードと前記低電圧側の電源端子との間に直接に接続された第2スイッチと、前記第2ノードと出力端子との間に直列に接続されたインダクタと、を備えることを特徴とする請求項6記載の増幅回路。

- 前記第2スイッチは、前記第2ノードの電圧が前記低電圧側の電源端子より低いときオンし、高いときオフすることを特徴とする請求項9記載の増幅回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013173858A JP2015041996A (ja) | 2013-08-23 | 2013-08-23 | 増幅回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013173858A JP2015041996A (ja) | 2013-08-23 | 2013-08-23 | 増幅回路 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2015041996A true JP2015041996A (ja) | 2015-03-02 |

Family

ID=52695886

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013173858A Pending JP2015041996A (ja) | 2013-08-23 | 2013-08-23 | 増幅回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2015041996A (ja) |

-

2013

- 2013-08-23 JP JP2013173858A patent/JP2015041996A/ja active Pending

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9641133B2 (en) | Adaptive rail power amplifier technology | |

| US10110120B2 (en) | Load adaptable boost DC-DC power converter | |

| JP4528321B2 (ja) | スイッチング回路、回路、並びにスイッチング回路及び駆動パルス生成回路を含む回路 | |

| CN106549564B (zh) | 具有供给调制的功率放大设备和方法 | |

| US10177724B2 (en) | Power amplifier circuit | |

| KR20190093209A (ko) | 게이트 드라이브 회로 및 그 동작 방법 | |

| US9853602B2 (en) | Adaptive tracking rail audio amplifier | |

| US9654055B2 (en) | Radio-frequency high power amplifier with broadband envelope tracking by means of reversed buck converter | |

| CN102047540A (zh) | 具有数字自适应电源升压的放大器系统 | |

| KR101786587B1 (ko) | 전력 증폭기의 전압을 생성하기 위한 장치 및 방법 | |

| CN102315759B (zh) | 具有抗饱和电路的栅极驱动控制器电路及其加电电路 | |

| CN107710630B (zh) | 射频功率放大器和电流增强驱动器 | |

| US5117198A (en) | Class D MOSFET amplifier and voltage supply balance circuit therefor | |

| CN103248205B (zh) | 开关驱动器电路、电源系统和用于控制电源开关的方法 | |

| US9537451B2 (en) | Amplifier having enhanced power efficiency | |

| JP6652561B2 (ja) | 電圧コンバータのためのアダプティブコントローラ | |

| JP2015041996A (ja) | 増幅回路 | |

| US10608551B2 (en) | Rectifying element and voltage converter comprising such a rectifying element | |

| US9525414B2 (en) | Gate drive circuit providing constant driving current | |

| JP2005210848A (ja) | 直流電圧変換装置 | |

| JP2006280019A (ja) | 電源回路 | |

| JP2013132095A (ja) | 電源回路及び電源制御方法 | |

| JP2015041999A (ja) | 増幅回路 | |

| JP2020058229A (ja) | 電圧コンバータのためのアダプティブコントローラ | |

| KR20140099048A (ko) | 변환 장치 및 그의 제어 방법 |