JP2013510376A - プローブアクティビティレベルの追跡による性能状態の制御 - Google Patents

プローブアクティビティレベルの追跡による性能状態の制御 Download PDFInfo

- Publication number

- JP2013510376A JP2013510376A JP2012538025A JP2012538025A JP2013510376A JP 2013510376 A JP2013510376 A JP 2013510376A JP 2012538025 A JP2012538025 A JP 2012538025A JP 2012538025 A JP2012538025 A JP 2012538025A JP 2013510376 A JP2013510376 A JP 2013510376A

- Authority

- JP

- Japan

- Prior art keywords

- probe

- performance state

- probe activity

- activity level

- threshold

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0806—Multiuser, multiprocessor or multiprocessing cache systems

- G06F12/0808—Multiuser, multiprocessor or multiprocessing cache systems with cache invalidating means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0806—Multiuser, multiprocessor or multiprocessing cache systems

- G06F12/0815—Cache consistency protocols

- G06F12/0831—Cache consistency protocols using a bus scheme, e.g. with bus monitoring or watching means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/10—Providing a specific technical effect

- G06F2212/1028—Power efficiency

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Abstract

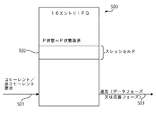

処理ノードは、その内部キャシング又はメモリシステムに関連するプローブアクティビティレベルを追跡する。プローブアクティビティレベルがスレッショルドプローブアクティビティレベルを超えると、処理ノードの性能状態がその当座の性能状態よりも高くされて、高められた性能能力をプローブ要求に応答して提供する。プローブアクティビティレベルがスレッショルドプローブアクティビティレベルを超えたことに応答してより高い性能状態にエンターした後に、処理ノードは、プローブアクティビティの低下に応答してより低い性能状態に戻る。多重スレッショルドプローブアクティビティレベル及び関連する性能状態があってよい。

【選択図】図1

Description

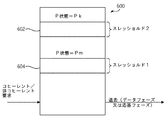

(Prob_Act>PrbActM)であれば、P状態=Pm

それ以外の場合において、(Prob_Act>PrbActN)であれば、P状態=Pn

それ以外の場合において、(Prob_Act>PrbActK)であれば、P状態=Pk

(Prob_Act<(PrbActM−HystM)且つProb_ACT>PrbActN且つ当座のP状態<Pm)であれば、P状態=Pn

それ以外の場合において、(Prob_Act<(PrbActN−HystN)且つProb_ACT>PrbActK且つ当座のP状態<Pn)であれば、P状態=Pk

それ以外の場合において、(Prob_Act<(PrbActK−HystK)且つ当座のP状態<Pk)であれば、P状態=当座のP状態

Claims (14)

- 処理ノードにおけるプローブアクティビティレベルを追跡することと、

前記プローブアクティビティレベルを第1のスレッショルドプローブアクティビティレベルと比較することと、

前記プローブアクティビティレベルが前記第1のスレッショルドプローブアクティビティレベルを超えている場合に前記処理ノードの性能状態を当座の性能状態よりも高い第1の性能状態に上げることと、を備える方法。 - 前記プローブアクティビティレベルが前記スレッショルドプローブアクティビティレベルを超えていることに応答して前記第1の性能状態をエンターした後に、前記プローブアクティビティレベルが前記第1のスレッショルドプローブアクティビティよりも低い予め定められたレベルを下回る場合に前記第1の性能状態よりも低い第2の性能状態をエンターすることを更に備える請求項1に記載の方法。

- ヒステリシス因子を差し引いた前記第1のスレッショルドよりも前記プローブアクティビティレベルが低い場合に前記第2の性能状態をエンターすることを更に備える請求項2に記載の方法。

- 前記第2の性能状態は前記処理ノードが前記第1の性能状態をエンターした性能状態である請求項3に記載の方法。

- 前記第1及び第2の性能状態は電圧及び周波数の少なくとも1つによって定義される請求項1〜4のいずれかに記載の方法。

- 前記プローブアクティビティレベルが前記第1のスレッショルドプローブアクティビティレベルよりも高い第2のスレッショルドプローブアクティビティレベルを超えて増大することに応答して前記処理ノードの前記性能状態を前記第1の性能状態よりも高い第3の性能状態に上げることと、

前記プローブアクティビティレベルが前記第2のスレッショルドプローブアクティビティレベルを超えて増大することに応答して前記処理ノードの前記性能状態を前記第3の性能状態に上げた後に前記性能状態を下げることと、を更に備える請求項1〜4のいずれかに記載の方法。 - 前記処理ノードが前記第1の性能状態を下回る性能状態にある場合に前記プローブアクティビティレベルの前記追跡することを開始することを更に備える請求項1〜4のいずれかに記載の方法。

- 前記プローブアクティビティを追跡することは、

各プローブ要求をキュー内にエンターすること並びにデータ移動及び応答の少なくとも一方を伴うプローブ要求に前記処理ノードが応答した後に前記プローブ要求を前記キューからリタイヤさせることと、

前記キュー内のエントリの数を前記第1のスレッショルドプローブアクティビティレベルと比較して前記プローブアクティビティが前記第1のスレッショルドプローブアクティビティレベルを上回っているかどうかを決定することと、を更に備える請求項1〜4のいずれかに記載の方法。 - 前記プローブアクティビティを追跡することは、プローブアクティビティの発生に応答してプローブアクティビティのレベルを表すカウント値をインクリメントすることと、予め定められた時間の経過に基づいて前記カウント値をデクリメントすることと、を更に備える請求項1〜4のいずれかに記載の方法。

- 処理ノードにおけるプローブアクティビティレベルを追跡するプローブ追跡器を備える装置であって、

前記装置は前記プローブアクティビティレベルが第1のスレッショルドプローブアクティビティレベルを超えて増大する場合に前記処理ノードの性能状態を当座の性能状態から第1の性能状態に上げるように動作し、

前記装置は前記第1のスレッショルドプローブアクティビティレベルより低い予め定められたレベルまで前記プローブアクティビティレベルが下がることに応答して前記第1の性能状態よりも低い第2の性能状態に前記処理ノードをエンターさせ、

前記第1及び第2の性能状態は電圧及び周波数の少なくとも一方によって定義される装置。 - 前記装置は前記プローブアクティビティレベルが前記第1のスレッショルドプローブアクティビティレベルよりも高い第2のスレッショルドプローブアクティビティレベルを超えて増大することに応答して前記処理ノードの前記性能状態を前記第1の性能状態よりも高い第3の性能状態に上げるように更に動作可能である請求項10に記載の装置。

- 前記プローブ追跡器は前記ノードが前記第1の性能状態より低い性能状態にあることに応答して前記プローブアクティビティレベルの追跡を開始する請求項10に記載の装置。

- 前記プローブ追跡器はキューを更に備え、

前記キュー内にプローブ要求がエンターされ、データ移動及び応答の少なくとも一方を伴うプローブ要求に前記処理ノードが応答した後に前記キュー内の前記プローブ要求は前記キューからリタイヤさせられ、

前記装置は前記キュー内のエントリの数を前記第1のスレッショルドプローブアクティビティレベルと比較して前記プローブアクティビティが第1のスレッショルドプローブアクティビティレベルを上回っているかどうかを決定するように動作可能である請求項10〜12のいずれかに記載の装置。 - 前記プローブ追跡器は、プローブアクティビティに応答してプローブアクティビティのレベルを表すカウント値をインクリメントすると共に予め定められた時間の経過に応答して前記カウント値をデクリメントするカウンタを備える請求項10〜12のいずれかに記載の装置。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US25879809P | 2009-11-06 | 2009-11-06 | |

| US61/258,798 | 2009-11-06 | ||

| US12/623,997 | 2009-11-23 | ||

| US12/623,997 US20110112798A1 (en) | 2009-11-06 | 2009-11-23 | Controlling performance/power by frequency control of the responding node |

| PCT/US2010/055598 WO2011057059A1 (en) | 2009-11-06 | 2010-11-05 | Controlling performance state by tracking probe activity level |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2013510376A true JP2013510376A (ja) | 2013-03-21 |

| JP2013510376A5 JP2013510376A5 (ja) | 2013-09-26 |

Family

ID=43536579

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012538025A Pending JP2013510376A (ja) | 2009-11-06 | 2010-11-05 | プローブアクティビティレベルの追跡による性能状態の制御 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US20110112798A1 (ja) |

| EP (1) | EP2497001A1 (ja) |

| JP (1) | JP2013510376A (ja) |

| KR (1) | KR20120102629A (ja) |

| CN (1) | CN102667665A (ja) |

| WO (1) | WO2011057059A1 (ja) |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8566628B2 (en) * | 2009-05-06 | 2013-10-22 | Advanced Micro Devices, Inc. | North-bridge to south-bridge protocol for placing processor in low power state |

| US20110112798A1 (en) * | 2009-11-06 | 2011-05-12 | Alexander Branover | Controlling performance/power by frequency control of the responding node |

| US8635381B2 (en) * | 2010-08-26 | 2014-01-21 | International Business Machines Corporation | System, method and computer program product for monitoring memory access |

| US8930589B2 (en) * | 2010-08-26 | 2015-01-06 | International Business Machines Corporation | System, method and computer program product for monitoring memory access |

| US8438416B2 (en) * | 2010-10-21 | 2013-05-07 | Advanced Micro Devices, Inc. | Function based dynamic power control |

| US20120166731A1 (en) * | 2010-12-22 | 2012-06-28 | Christian Maciocco | Computing platform power management with adaptive cache flush |

| JP5674613B2 (ja) * | 2011-09-22 | 2015-02-25 | 株式会社東芝 | 制御システム、制御方法およびプログラム |

| US9110671B2 (en) * | 2012-12-21 | 2015-08-18 | Advanced Micro Devices, Inc. | Idle phase exit prediction |

| US9600058B2 (en) * | 2014-06-24 | 2017-03-21 | Intel Corporation | Enhancing power-performance efficiency in a computer system when bursts of activity occurs when operating in low power |

| US20160116954A1 (en) * | 2014-10-28 | 2016-04-28 | Linkedln Corporation | Dynamic adjustment of cpu operating frequency |

| US10489237B2 (en) | 2014-12-19 | 2019-11-26 | Hewlett Packard Enterprise Development Lp | Flushing data content in response to a power loss event to a processor |

| US9785223B2 (en) * | 2014-12-25 | 2017-10-10 | Intel Corporation | Power management in an uncore fabric |

| US9690708B2 (en) | 2015-05-19 | 2017-06-27 | Qualcomm Incorporated | Real-time cache behavior forecast using hypothetical cache |

| CN105068639B (zh) * | 2015-07-29 | 2018-06-19 | Tcl移动通信科技(宁波)有限公司 | 一种动态控制处理器频率的方法及系统 |

| US11289133B2 (en) * | 2015-09-16 | 2022-03-29 | Arm Limited | Power state based data retention |

| US10324519B2 (en) * | 2016-06-23 | 2019-06-18 | Intel Corporation | Controlling forced idle state operation in a processor |

| US10120806B2 (en) * | 2016-06-27 | 2018-11-06 | Intel Corporation | Multi-level system memory with near memory scrubbing based on predicted far memory idle time |

| US10216256B2 (en) | 2016-10-03 | 2019-02-26 | Microsoft Technology Licensing, Llc | Power conservation of computing components using forced idle state |

| US10180793B2 (en) * | 2017-01-31 | 2019-01-15 | Hewlett Packard Enterprise Development Lp | Performance attributes for memory |

| US11243603B2 (en) * | 2017-06-27 | 2022-02-08 | Telefonaktiebolaget Lm Ericsson (Publ) | Power management of an event-based processing system |

| US10725848B2 (en) * | 2018-02-07 | 2020-07-28 | Intel Corporation | Supporting hang detection and data recovery in microprocessor systems |

| US10628321B2 (en) * | 2018-02-28 | 2020-04-21 | Qualcomm Incorporated | Progressive flush of cache memory |

| US10958555B2 (en) | 2019-03-15 | 2021-03-23 | Juniper Networks, Inc. | Real-time application-driven synthetic probing |

| US11960773B2 (en) * | 2020-07-31 | 2024-04-16 | Hewlett Packard Enterprise Development Lp | Modifying virtual persistent volumes based on analysis of performance metrics |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10268963A (ja) * | 1997-03-28 | 1998-10-09 | Mitsubishi Electric Corp | 情報処理装置 |

| JP2002221958A (ja) * | 2001-01-26 | 2002-08-09 | Nec Corp | 省電力グラフィック制御回路 |

| US20080276236A1 (en) * | 2007-05-02 | 2008-11-06 | Advanced Micro Devices, Inc. | Data processing device with low-power cache access mode |

| WO2008152790A1 (ja) * | 2007-06-12 | 2008-12-18 | Panasonic Corporation | マルチプロセッサ制御装置、マルチプロセッサ制御方法及びマルチプロセッサ制御回路 |

Family Cites Families (83)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE69432697T2 (de) * | 1993-12-01 | 2004-03-25 | Advanced Micro Devices, Inc., Sunnyvale | Stromverwaltung für Rechnersystem und Verfahren hierfür |

| US5541850A (en) * | 1994-05-17 | 1996-07-30 | Vlsi Technology, Inc. | Method and apparatus for forming an integrated circuit including a memory structure |

| AU3313795A (en) * | 1994-10-14 | 1996-04-26 | Compaq Computer Corporation | Circuit for placing a cache memory into low power mode in response to special bus cycles |

| US5530932A (en) * | 1994-12-23 | 1996-06-25 | Intel Corporation | Cache coherent multiprocessing computer system with reduced power operating features |

| US5737615A (en) * | 1995-04-12 | 1998-04-07 | Intel Corporation | Microprocessor power control in a multiprocessor computer system |

| US6282662B1 (en) * | 1995-08-04 | 2001-08-28 | Dell Usa, L.P. | Power management override for portable computers |

| US5740417A (en) * | 1995-12-05 | 1998-04-14 | Motorola, Inc. | Pipelined processor operating in different power mode based on branch prediction state of branch history bit encoded as taken weakly not taken and strongly not taken states |

| US5692202A (en) * | 1995-12-29 | 1997-11-25 | Intel Corporation | System, apparatus, and method for managing power in a computer system |

| US6125450A (en) * | 1996-12-19 | 2000-09-26 | Intel Corporation | Stop clock throttling in a computer processor through disabling bus masters |

| JP3819166B2 (ja) * | 1998-11-27 | 2006-09-06 | ヒタチグローバルストレージテクノロジーズネザーランドビーブイ | 消費エネルギー低減方法 |

| US6360337B1 (en) | 1999-01-27 | 2002-03-19 | Sun Microsystems, Inc. | System and method to perform histogrammic counting for performance evaluation |

| US6141283A (en) * | 1999-04-01 | 2000-10-31 | Intel Corporation | Method and apparatus for dynamically placing portions of a memory in a reduced power consumption state |

| US6510525B1 (en) * | 1999-04-26 | 2003-01-21 | Mediaq, Inc. | Method and apparatus to power up an integrated device from a low power state |

| US6711691B1 (en) * | 1999-05-13 | 2004-03-23 | Apple Computer, Inc. | Power management for computer systems |

| US6480965B1 (en) * | 1999-10-07 | 2002-11-12 | Intel Corporation | Power management method for a computer system having a hub interface architecture |

| US6496895B1 (en) * | 1999-11-01 | 2002-12-17 | Intel Corporation | Method and apparatus for intializing a hub interface |

| US6760852B1 (en) * | 2000-08-31 | 2004-07-06 | Advanced Micro Devices, Inc. | System and method for monitoring and controlling a power-manageable resource based upon activities of a plurality of devices |

| US6988214B1 (en) * | 2000-11-06 | 2006-01-17 | Dell Products L.P. | Processor power state transistions using separate logic control |

| US6493801B2 (en) * | 2001-01-26 | 2002-12-10 | Compaq Computer Corporation | Adaptive dirty-block purging |

| US7051218B1 (en) * | 2001-07-18 | 2006-05-23 | Advanced Micro Devices, Inc. | Message based power management |

| US7174467B1 (en) * | 2001-07-18 | 2007-02-06 | Advanced Micro Devices, Inc. | Message based power management in a multi-processor system |

| US7200544B1 (en) * | 2001-10-26 | 2007-04-03 | National Semiconductor Corporation | Systems for selectively disabling timing violations in hardware description language models of integrated circuits and methods of operating the same |

| US6976181B2 (en) * | 2001-12-20 | 2005-12-13 | Intel Corporation | Method and apparatus for enabling a low power mode for a processor |

| US6954864B2 (en) * | 2002-03-29 | 2005-10-11 | Intel Corporation | Method and apparatus for remotely placing a computing device into a low power state |

| US6920574B2 (en) * | 2002-04-29 | 2005-07-19 | Apple Computer, Inc. | Conserving power by reducing voltage supplied to an instruction-processing portion of a processor |

| US7028200B2 (en) * | 2002-05-15 | 2006-04-11 | Broadcom Corporation | Method and apparatus for adaptive power management of memory subsystem |

| US7152169B2 (en) * | 2002-11-29 | 2006-12-19 | Intel Corporation | Method for providing power management on multi-threaded processor by using SMM mode to place a physical processor into lower power state |

| US6971033B2 (en) * | 2003-01-10 | 2005-11-29 | Broadcom Corporation | Method and apparatus for improving bus master performance |

| US7162404B2 (en) * | 2003-04-28 | 2007-01-09 | International Business Machines Corporation | Method, system and program product for configuring a simulation model of a digital design |

| US7299370B2 (en) * | 2003-06-10 | 2007-11-20 | Intel Corporation | Method and apparatus for improved reliability and reduced power in a processor by automatic voltage control during processor idle states |

| US7356713B2 (en) * | 2003-07-31 | 2008-04-08 | International Business Machines Corporation | Method and apparatus for managing the power consumption of a data processing system |

| TWI307008B (en) * | 2003-08-14 | 2009-03-01 | Via Tech Inc | Computer system with power management and the method thereof |

| US7200762B2 (en) * | 2003-09-30 | 2007-04-03 | Intel Corporation | Providing a low-power state processor voltage in accordance with a detected processor type |

| US7178045B2 (en) * | 2003-12-30 | 2007-02-13 | Intel Corporation | Optimizing exit latency from an active power management state |

| US7159766B2 (en) * | 2004-01-20 | 2007-01-09 | Standard Microsystems Corporation | Peripheral device feature allowing processors to enter a low power state |

| TWI264634B (en) * | 2004-04-13 | 2006-10-21 | Acer Inc | Method for monitoring power state of computer system and apparatus therefor |

| US7272741B2 (en) * | 2004-06-02 | 2007-09-18 | Intel Corporation | Hardware coordination of power management activities |

| US7315952B2 (en) * | 2004-06-02 | 2008-01-01 | Intel Corporation | Power state coordination between devices sharing power-managed resources |

| KR20050120565A (ko) | 2004-06-17 | 2005-12-22 | 인텔 코오퍼레이션 | 전력-관리된 리소스들을 공유하는 디바이스들 간의 전력상태 조정 |

| TWI259354B (en) * | 2004-06-25 | 2006-08-01 | Via Tech Inc | System and method of real-time power management |

| US7451333B2 (en) * | 2004-09-03 | 2008-11-11 | Intel Corporation | Coordinating idle state transitions in multi-core processors |

| US7360106B2 (en) * | 2004-08-05 | 2008-04-15 | Matsushita Electric Industrial Co., Ltd. | Power-saving processing unit, power-saving processing method and program record medium |

| US7711966B2 (en) * | 2004-08-31 | 2010-05-04 | Qualcomm Incorporated | Dynamic clock frequency adjustment based on processor load |

| KR100661851B1 (ko) * | 2004-12-08 | 2006-12-27 | 한국전자통신연구원 | 플랫폼의 소비 전력 관리 방법 및 그 플랫폼 |

| US7694080B2 (en) * | 2004-12-29 | 2010-04-06 | Intel Corporation | Method and apparatus for providing a low power mode for a processor while maintaining snoop throughput |

| US7610497B2 (en) * | 2005-02-01 | 2009-10-27 | Via Technologies, Inc. | Power management system with a bridge logic having analyzers for monitoring data quantity to modify operating clock and voltage of the processor and main memory |

| TWI268424B (en) * | 2005-03-15 | 2006-12-11 | Uli Electronics Inc | Signal transmission method between computer system and peripherals adopting PCI express bus characterizing in saving power of transmitting signals |

| US7444526B2 (en) * | 2005-06-16 | 2008-10-28 | International Business Machines Corporation | Performance conserving method for reducing power consumption in a server system |

| US7454632B2 (en) * | 2005-06-16 | 2008-11-18 | Intel Corporation | Reducing computing system power through idle synchronization |

| US7373534B2 (en) * | 2005-06-23 | 2008-05-13 | Intel Corporation | Reducing storage data transfer interference with processor power management |

| US7475262B2 (en) * | 2005-06-29 | 2009-01-06 | Intel Corporation | Processor power management associated with workloads |

| US7562234B2 (en) * | 2005-08-25 | 2009-07-14 | Apple Inc. | Methods and apparatuses for dynamic power control |

| TWI286705B (en) * | 2005-09-06 | 2007-09-11 | Via Tech Inc | Power management method of central processing unit |

| US7472299B2 (en) * | 2005-09-30 | 2008-12-30 | Intel Corporation | Low power arbiters in interconnection routers |

| US7750912B2 (en) * | 2005-11-23 | 2010-07-06 | Advanced Micro Devices, Inc. | Integrating display controller into low power processor |

| US7487371B2 (en) * | 2005-12-16 | 2009-02-03 | Nvidia Corporation | Data path controller with integrated power management to manage power consumption of a computing device and its components |

| US7516342B2 (en) * | 2005-12-30 | 2009-04-07 | Intel Corporation | Method, apparatus and system to dynamically choose an optimum power state |

| US7861068B2 (en) * | 2006-03-07 | 2010-12-28 | Intel Corporation | Method and apparatus for using dynamic workload characteristics to control CPU frequency and voltage scaling |

| US8132030B2 (en) | 2006-06-27 | 2012-03-06 | Koninklijke Philips Electronics N.V. | Device and a method for managing power consumption of a plurality of data processing units |

| US7644293B2 (en) * | 2006-06-29 | 2010-01-05 | Intel Corporation | Method and apparatus for dynamically controlling power management in a distributed system |

| US7930564B2 (en) * | 2006-07-31 | 2011-04-19 | Intel Corporation | System and method for controlling processor low power states |

| US7752474B2 (en) * | 2006-09-22 | 2010-07-06 | Apple Inc. | L1 cache flush when processor is entering low power mode |

| FR2906624A1 (fr) * | 2006-10-03 | 2008-04-04 | Bull S A S Soc Par Actions Sim | Systeme et procede de stockage de masse. |

| US7949887B2 (en) * | 2006-11-01 | 2011-05-24 | Intel Corporation | Independent power control of processing cores |

| US20090150696A1 (en) * | 2007-12-10 | 2009-06-11 | Justin Song | Transitioning a processor package to a low power state |

| US7966506B2 (en) * | 2007-12-12 | 2011-06-21 | Intel Corporation | Saving power in a computer system |

| GB2455744B (en) * | 2007-12-19 | 2012-03-14 | Advanced Risc Mach Ltd | Hardware driven processor state storage prior to entering a low power mode |

| US8156362B2 (en) * | 2008-03-11 | 2012-04-10 | Globalfoundries Inc. | Hardware monitoring and decision making for transitioning in and out of low-power state |

| US8448002B2 (en) * | 2008-04-10 | 2013-05-21 | Nvidia Corporation | Clock-gated series-coupled data processing modules |

| US8131948B2 (en) * | 2008-08-29 | 2012-03-06 | Freescale Semiconductor, Inc. | Snoop request arbitration in a data processing system |

| US8112651B2 (en) * | 2008-09-25 | 2012-02-07 | Intel Corporation | Conserving power in a computer system |

| US8209559B2 (en) * | 2008-12-24 | 2012-06-26 | Intel Corporation | Low power polling techniques |

| US8725953B2 (en) * | 2009-01-21 | 2014-05-13 | Arm Limited | Local cache power control within a multiprocessor system |

| US8195887B2 (en) * | 2009-01-21 | 2012-06-05 | Globalfoundries Inc. | Processor power management and method |

| US8566628B2 (en) * | 2009-05-06 | 2013-10-22 | Advanced Micro Devices, Inc. | North-bridge to south-bridge protocol for placing processor in low power state |

| US8190939B2 (en) * | 2009-06-26 | 2012-05-29 | Microsoft Corporation | Reducing power consumption of computing devices by forecasting computing performance needs |

| US8443209B2 (en) * | 2009-07-24 | 2013-05-14 | Advanced Micro Devices, Inc. | Throttling computational units according to performance sensitivity |

| US8291249B2 (en) * | 2009-09-25 | 2012-10-16 | Advanced Micro Devices, Inc. | Method and apparatus for transitioning devices between power states based on activity request frequency |

| US20110112798A1 (en) * | 2009-11-06 | 2011-05-12 | Alexander Branover | Controlling performance/power by frequency control of the responding node |

| US8780121B2 (en) * | 2009-12-22 | 2014-07-15 | Intel Corporation | Graphics render clock throttling and gating mechanism for power saving |

| US8656198B2 (en) * | 2010-04-26 | 2014-02-18 | Advanced Micro Devices | Method and apparatus for memory power management |

| US8782456B2 (en) * | 2010-06-01 | 2014-07-15 | Intel Corporation | Dynamic and idle power reduction sequence using recombinant clock and power gating |

| US8352685B2 (en) * | 2010-08-20 | 2013-01-08 | Apple Inc. | Combining write buffer with dynamically adjustable flush metrics |

-

2009

- 2009-11-23 US US12/623,997 patent/US20110112798A1/en not_active Abandoned

-

2010

- 2010-02-08 US US12/702,085 patent/US9021209B2/en active Active

- 2010-11-05 CN CN201080048873XA patent/CN102667665A/zh active Pending

- 2010-11-05 EP EP10784608A patent/EP2497001A1/en not_active Withdrawn

- 2010-11-05 WO PCT/US2010/055598 patent/WO2011057059A1/en active Application Filing

- 2010-11-05 KR KR1020127011940A patent/KR20120102629A/ko not_active Application Discontinuation

- 2010-11-05 JP JP2012538025A patent/JP2013510376A/ja active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10268963A (ja) * | 1997-03-28 | 1998-10-09 | Mitsubishi Electric Corp | 情報処理装置 |

| JP2002221958A (ja) * | 2001-01-26 | 2002-08-09 | Nec Corp | 省電力グラフィック制御回路 |

| US20080276236A1 (en) * | 2007-05-02 | 2008-11-06 | Advanced Micro Devices, Inc. | Data processing device with low-power cache access mode |

| JP2010526374A (ja) * | 2007-05-02 | 2010-07-29 | アドバンスト・マイクロ・ディバイシズ・インコーポレイテッド | 低パワーキャッシュアクセスモードを備えたデータ処理デバイス |

| WO2008152790A1 (ja) * | 2007-06-12 | 2008-12-18 | Panasonic Corporation | マルチプロセッサ制御装置、マルチプロセッサ制御方法及びマルチプロセッサ制御回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2011057059A1 (en) | 2011-05-12 |

| KR20120102629A (ko) | 2012-09-18 |

| US9021209B2 (en) | 2015-04-28 |

| US20110112798A1 (en) | 2011-05-12 |

| US20110113202A1 (en) | 2011-05-12 |

| EP2497001A1 (en) | 2012-09-12 |

| CN102667665A (zh) | 2012-09-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2013510376A (ja) | プローブアクティビティレベルの追跡による性能状態の制御 | |

| US10564699B2 (en) | Dynamically controlling cache size to maximize energy efficiency | |

| US9760409B2 (en) | Dynamically modifying a power/performance tradeoff based on a processor utilization | |

| US7752470B2 (en) | Method and system for power management including device controller-based device use evaluation and power-state control | |

| US9618997B2 (en) | Controlling a turbo mode frequency of a processor | |

| US9074947B2 (en) | Estimating temperature of a processor core in a low power state without thermal sensor information | |

| US10204056B2 (en) | Dynamic cache enlarging by counting evictions | |

| CN107153455B (zh) | 缓存功率管理 | |

| US9075609B2 (en) | Power controller, processor and method of power management | |

| US9965023B2 (en) | Apparatus and method for flushing dirty cache lines based on cache activity levels | |

| EP4339789A1 (en) | Dynamic cache resource allocation for quality of service and system power reduction | |

| TW202414219A (zh) | 計算系統及計算系統進行共享高速緩存分配的方法 | |

| TW202414188A (zh) | 計算系統及計算系統進行部分高速緩存去激活的方法 | |

| CN117707997A (zh) | 计算系统及计算系统进行部分高速缓存去激活的方法 | |

| CN117707996A (zh) | 计算系统及计算系统进行共享高速缓存分配的方法 | |

| KR101024073B1 (ko) | 공유 2차 캐시의 누설 에너지 관리 방법 및 장치 | |

| CN111177023A (zh) | 嵌入式设备中存储区间的分配方法及装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130808 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130808 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140528 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140625 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20150106 |