JP2012123719A - プログラマブルコントローラ - Google Patents

プログラマブルコントローラ Download PDFInfo

- Publication number

- JP2012123719A JP2012123719A JP2010275719A JP2010275719A JP2012123719A JP 2012123719 A JP2012123719 A JP 2012123719A JP 2010275719 A JP2010275719 A JP 2010275719A JP 2010275719 A JP2010275719 A JP 2010275719A JP 2012123719 A JP2012123719 A JP 2012123719A

- Authority

- JP

- Japan

- Prior art keywords

- stage

- data

- memory

- bit

- read

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

- G06F9/30018—Bit or string instructions

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/3004—Arrangements for executing specific machine instructions to perform operations on memory

- G06F9/30043—LOAD or STORE instructions; Clear instruction

Landscapes

- Engineering & Computer Science (AREA)

- Software Systems (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Memory System Of A Hierarchy Structure (AREA)

- Advance Control (AREA)

- Executing Machine-Instructions (AREA)

- Programmable Controllers (AREA)

Abstract

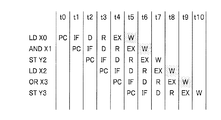

【解決手段】リードモディファイライトの対象データをバッファレジスタにロードするとともに対象データのアドレスをレジスタファイル152に保持しておくパイプラインステージR(リードステージ)の後ろに、ビット演算及びビットデータのマージを行うパイプラインステージEX(実行ステージ)を設け、その後ろにリードステージRにて保持したアドレスにマージ結果をストアするパイプラインステージW(ライトステージ)を設ける。

【選択図】図1

Description

《第1実施形態》

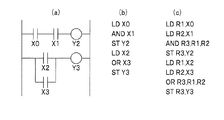

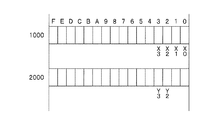

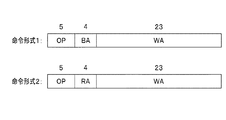

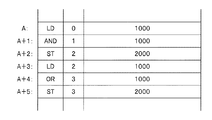

図1は、本発明の第1実施形態に係るプログラマブルコントローラが備えるビット演算プロセッサの内部構成及びパイプライン構成を示す図である。また、図13は、第1実施形態に係るパイプライン構成を図14の従来技術と対比して表現したものである。図1及び図13に示すように、本実施形態に係るパイプライン構成は、(1)プログラムカウンタ(PC)ステージ、(2)命令フェッチ(IF)ステージ、(3)デコード(D)ステージ、(4)メモリリード(R)ステージ、(5)演算実行(EX)ステージ、(6)メモリライト(W)ステージ、の6段からなる。

続いて、第1実施形態におけるデータメモリ20(図2参照)をキャッシュメモリによって構成する本発明の第2実施形態について説明する。図5は、第2実施形態に係るキャッシュメモリの構成を示す図である。図5に示すように、データメモリ20としてのキャッシュメモリ20Aは、2ウェイセットアソシアティブ方式のキャッシュメモリであり、アドレスセレクタ201A、インデックス保持レジスタ221A及び222A、ウェイセレクタ203、ライトデータセレクタ204A、ウェイ0タグメモリ205、ウェイ1タグメモリ206、LRU(Least Recently Used)メモリ207、ウェイ0データメモリ208、ウェイ1データメモリ209、ヒット判定回路210、ライトバック制御回路211、ウェイデータセレクタ212、ウェイ保持レジスタ213及び214を備えて構成される。図1のアドレス保持回路22は、インデックス保持レジスタ221A,222Aを有するアドレス保持回路1(22A)と、ウェイ保持レジスタ213,214を有するアドレス保持回路2(22B)によって構成される。

2A,2B I/Oモジュール

3 I/Oバス

4 プログラム入力装置

10 ビット演算プロセッサ

20 データメモリ

20A キャッシュメモリ

21 メモリアレイ

22,22A,22B アドレス保持回路

30 命令バッファ

40 I/Oバス制御回路

50 メモリコントローラ

60 外部RAM

70 ROM

80 汎用マイクロプロセッサ

90 通信I/F

100 システムLSI

1000 プログラマブルコントローラ

Claims (6)

- ビット演算処理の対象となる1ビットのデータを複数個まとめたワードの単位でメモリの読み書きを行うプログラマブルコントローラであって、

プログラムに含まれるビット演算処理命令列を、パイプライン処理機構によって並列に実行するビット演算プロセッサを備え、

前記ビット演算プロセッサが備えるパイプラインステージは、演算対象となるデータをワード単位でメモリから読み込むリードステージの次に演算ステージがあり、前記演算ステージの次に、前記演算ステージによって演算されたビット演算の結果を含むワードデータを前記リードステージで読み込んだデータと同じアドレスに書き込むライトステージがある

ことを特徴とするプログラマブルコントローラ。 - 前記メモリは、

少なくとも2ウェイ以上のセットアソシアティブ方式又はフルアソシアティブ方式のキャッシュメモリであり、

前記リードステージにて読み込んだキャッシュエントリのインデックス情報及びウェイ情報を、前記ライトステージまで保持するアドレス保持回路を備える

ことを特徴とする請求項1に記載のプログラマブルコントローラ。 - 前記ビット演算プロセッサは、

前記ビット演算処理命令のなかのビットデータのストア命令を実行するときに、

前記リードステージにてストア対象のビットを含む元のワードデータを読み込んで記憶部に保持しておき、

前記演算ステージにて演算された前記ビット演算の結果のビットデータを、前記保持した元のワードデータにマージする

ことを特徴とする請求項1または請求項2に記載のプログラマブルコントローラ。 - 前記メモリは、単一のパイプラインステージ処理サイクル時間内に1回以上のリードと1回以上のライトとを行うことができる2ポート以上のメモリである

ことを特徴とする請求項1または請求項2に記載のプログラマブルコントローラ。 - キャッシュヒット判定を前記リードステージで行い、前記ライトステージでは前記アドレス保持回路に保持された前記インデックス情報及びウェイ情報によって示されるキャッシュエントリに、前記ビット演算の結果を含むワードデータがマージされたラインデータを書き込む

ことを特徴とする請求項2に記載のプログラマブルコントローラ。 - ストアするアドレス範囲によってライトスルーモードとライトバックモードを切り替える

ことを特徴とする請求項2に記載のプログラマブルコントローラ。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010275719A JP5480793B2 (ja) | 2010-12-10 | 2010-12-10 | プログラマブルコントローラ |

| PCT/JP2011/077328 WO2012077516A1 (ja) | 2010-12-10 | 2011-11-28 | プログラマブルコントローラ |

| CN201180059507.9A CN103262029B (zh) | 2010-12-10 | 2011-11-28 | 可编程控制器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010275719A JP5480793B2 (ja) | 2010-12-10 | 2010-12-10 | プログラマブルコントローラ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012123719A true JP2012123719A (ja) | 2012-06-28 |

| JP5480793B2 JP5480793B2 (ja) | 2014-04-23 |

Family

ID=46207008

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010275719A Active JP5480793B2 (ja) | 2010-12-10 | 2010-12-10 | プログラマブルコントローラ |

Country Status (3)

| Country | Link |

|---|---|

| JP (1) | JP5480793B2 (ja) |

| CN (1) | CN103262029B (ja) |

| WO (1) | WO2012077516A1 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2529892B (en) | 2014-09-08 | 2017-04-12 | Imagination Tech Ltd | Efficient loading and storing of data |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05120135A (ja) * | 1991-10-25 | 1993-05-18 | Oki Electric Ind Co Ltd | キヤツシユ制御方式 |

| JPH0954694A (ja) * | 1995-08-16 | 1997-02-25 | Nec Corp | パイプラインプロセッサおよびその処理方法 |

| JPH11119995A (ja) * | 1997-10-09 | 1999-04-30 | Nec Corp | データ処理装置および方法 |

| JP2001290702A (ja) * | 2000-04-05 | 2001-10-19 | Nec Corp | 記憶装置 |

| JP2003044357A (ja) * | 2001-07-27 | 2003-02-14 | Nec Computertechno Ltd | キャッシュ先取り方式 |

| JP2003196084A (ja) * | 2001-12-25 | 2003-07-11 | Toshiba Corp | リードモディファイライトユニットを有するシステム |

| JP2008129771A (ja) * | 2006-11-20 | 2008-06-05 | Konica Minolta Business Technologies Inc | メモリシステムおよび情報処理装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5933651A (en) * | 1995-09-29 | 1999-08-03 | Matsushita Electric Works, Ltd. | Programmable controller |

| JPH0997180A (ja) * | 1995-09-29 | 1997-04-08 | Matsushita Electric Works Ltd | プログラマブルコントローラ |

| JP2001125770A (ja) * | 1999-10-29 | 2001-05-11 | Matsushita Electric Works Ltd | 演算方法及び演算装置 |

| JP2005242457A (ja) * | 2004-02-24 | 2005-09-08 | Matsushita Electric Works Ltd | プログラマブルコントローラ |

| EP2148272B1 (en) * | 2007-05-17 | 2012-08-08 | Fujitsu Limited | Calculation unit, processor, and processor architecture |

-

2010

- 2010-12-10 JP JP2010275719A patent/JP5480793B2/ja active Active

-

2011

- 2011-11-28 CN CN201180059507.9A patent/CN103262029B/zh active Active

- 2011-11-28 WO PCT/JP2011/077328 patent/WO2012077516A1/ja not_active Ceased

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05120135A (ja) * | 1991-10-25 | 1993-05-18 | Oki Electric Ind Co Ltd | キヤツシユ制御方式 |

| JPH0954694A (ja) * | 1995-08-16 | 1997-02-25 | Nec Corp | パイプラインプロセッサおよびその処理方法 |

| JPH11119995A (ja) * | 1997-10-09 | 1999-04-30 | Nec Corp | データ処理装置および方法 |

| JP2001290702A (ja) * | 2000-04-05 | 2001-10-19 | Nec Corp | 記憶装置 |

| JP2003044357A (ja) * | 2001-07-27 | 2003-02-14 | Nec Computertechno Ltd | キャッシュ先取り方式 |

| JP2003196084A (ja) * | 2001-12-25 | 2003-07-11 | Toshiba Corp | リードモディファイライトユニットを有するシステム |

| JP2008129771A (ja) * | 2006-11-20 | 2008-06-05 | Konica Minolta Business Technologies Inc | メモリシステムおよび情報処理装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2012077516A1 (ja) | 2012-06-14 |

| JP5480793B2 (ja) | 2014-04-23 |

| CN103262029B (zh) | 2015-10-14 |

| CN103262029A (zh) | 2013-08-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10901913B2 (en) | Two address translations from a single table look-aside buffer read | |

| US7434024B2 (en) | SIMD processor with register addressing, buffer stall and methods | |

| CN110806900B (zh) | 一种访存指令处理方法及处理器 | |

| KR101839479B1 (ko) | 더 넓은 레지스터에의 모드 의존형 부분 폭 로드 프로세서들, 방법들, 및 시스템들 | |

| JP2017538213A (ja) | アウトオブオーダーハードウェアソフトウェア協調設計プロセッサにおいてスタック同期命令を用いてプレディケート値のスタックを実装し維持する方法および装置 | |

| CN101432703B (zh) | 用于高速缓存可变长度指令的方法及设备 | |

| US7836253B2 (en) | Cache memory having pipeline structure and method for controlling the same | |

| US8145804B2 (en) | Systems and methods for transferring data to maintain preferred slot positions in a bi-endian processor | |

| JP7626527B2 (ja) | グラフアプリケーション内の圧縮されたリストに効率的にアクセスするための間接参照のロード及びストアへのisaサポートのシステム及び方法 | |

| CN101727406B (zh) | 组相联方式的高速缓存装置、高速缓存方法及处理器系统 | |

| JPH10228376A (ja) | 複数レジスタ命令を処理する方法及びプロセッサ | |

| JP5625809B2 (ja) | 演算処理装置、情報処理装置及び制御方法 | |

| US20100318766A1 (en) | Processor and information processing system | |

| JP2001195304A (ja) | キャッシュ記憶装置 | |

| WO1996008769A1 (en) | Computer instruction prefetch system | |

| US20100106910A1 (en) | Cache memory and method of controlling the same | |

| JP5480793B2 (ja) | プログラマブルコントローラ | |

| US7159078B2 (en) | Computer system embedding sequential buffers therein for performing a digital signal processing data access operation and a method thereof | |

| EP0706120A1 (en) | Method and system for memory addressing | |

| JP2008257508A (ja) | キャッシュ制御方法およびキャッシュ装置並びにマイクロコンピュータ | |

| US7290120B2 (en) | Microprocessor having a power-saving fetch and decoding unit for fetching and decoding compressed program instructions and having a program instruction sequencer | |

| JPH08249175A (ja) | スーパースカラ・プロセッサ装置内の非アーキテクト命令を選択的にサポートする方法及び装置 | |

| JPH07200406A (ja) | キャッシュシステム | |

| JP2877468B2 (ja) | 電子計算機 | |

| JP4553622B2 (ja) | データ処理装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20121129 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130604 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130802 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131119 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140120 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140204 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140214 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5480793 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |