JP2010187182A - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP2010187182A JP2010187182A JP2009029677A JP2009029677A JP2010187182A JP 2010187182 A JP2010187182 A JP 2010187182A JP 2009029677 A JP2009029677 A JP 2009029677A JP 2009029677 A JP2009029677 A JP 2009029677A JP 2010187182 A JP2010187182 A JP 2010187182A

- Authority

- JP

- Japan

- Prior art keywords

- chip

- lead frame

- lid

- semiconductor

- mold resin

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/146—Mixed devices

- H01L2924/1461—MEMS

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3025—Electromagnetic shielding

Landscapes

- Details Of Audible-Bandwidth Transducers (AREA)

- Lead Frames For Integrated Circuits (AREA)

Abstract

【課題】プリモールドタイプのパッケージにあってパッケージ本体の反り等の変形を防止する。

【解決手段】MEMSチップ2がモールド樹脂体6に形成された凹部9内に収容されるとともに、凹部9が蓋体8により閉塞され、MEMSチップ2以外の他の半導体チップ3がモールド樹脂体6内に埋設され、端子部は、他の半導体チップ3に接続されモールド樹脂体から一部が露出する外部接続用端子部と、MEMSチップ2及び他の半導体チップ3の両方に接続された中継端子部24とを有し、中継端子部24は、MEMSチップ2に接続された部分が凹部9内に露出され、他の半導体チップ3に接続された部分がモールド樹脂体6内に埋設されている。

【選択図】 図1

【解決手段】MEMSチップ2がモールド樹脂体6に形成された凹部9内に収容されるとともに、凹部9が蓋体8により閉塞され、MEMSチップ2以外の他の半導体チップ3がモールド樹脂体6内に埋設され、端子部は、他の半導体チップ3に接続されモールド樹脂体から一部が露出する外部接続用端子部と、MEMSチップ2及び他の半導体チップ3の両方に接続された中継端子部24とを有し、中継端子部24は、MEMSチップ2に接続された部分が凹部9内に露出され、他の半導体チップ3に接続された部分がモールド樹脂体6内に埋設されている。

【選択図】 図1

Description

本発明は、リードフレームの少なくとも一部をモールド樹脂体に埋設してなるパッケージ本体にMEMSチップを含む複数の半導体チップを収納して蓋体により覆ってなる半導体装置及びその製造方法に関する。

シリコンマイクや圧力センサ等の半導体装置は、中空のパッケージの中にマイクロフォンチップ等の半導体チップが収納されている。また、近年では、このマイクロフォンチップのような機械要素を有するセンサ等の半導体チップとして、マイクロマシニング技術を用いたMEMS(Micro Electro Mechanical Systems)構造の半導体チップが採用されている。

特許文献1に記載の半導体装置は、フラットの基板の上にMEMS構造のマイクロフォンチップを含む複数の半導体チップが搭載され、その上からキャップ状に絞り加工された蓋体が被せられ、その下端が基板の表面に固定されている。この場合、蓋体は金属等の導電性材料によって形成され、その下端が基板上の導体に導電性接着剤によって固定されており、蓋体と基板上の導体とによって半導体チップの電磁シールドがなされるようになっている。

特許文献1に記載の半導体装置は、フラットの基板の上にMEMS構造のマイクロフォンチップを含む複数の半導体チップが搭載され、その上からキャップ状に絞り加工された蓋体が被せられ、その下端が基板の表面に固定されている。この場合、蓋体は金属等の導電性材料によって形成され、その下端が基板上の導体に導電性接着剤によって固定されており、蓋体と基板上の導体とによって半導体チップの電磁シールドがなされるようになっている。

一方、この種の半導体装置として、リードフレームに樹脂をモールドして一体化したプリモールドタイプのパッケージを用いることにより、リードフレームを複数個マトリクス状に連続成形したリードフレーム連続成形体を形成して、パッケージ本体を複数個一括して製作することができ、材料コストの低減、生産性の向上を図ることができると考えられる。特許文献2及び3に記載の半導体装置は、このようなプリモールドタイプのパッケージを用いたものであり、半導体チップに接続されるリードフレームの一部がモールド樹脂に埋設状態とされるとともに、この半導体チップの回りを囲むように周壁部がモールド樹脂に一体に形成され、その周壁部の上に蓋体が固定されている。この場合、特許文献2記載のもののように、半導体チップはポッティング樹脂により封止される。

ところで、このようなプリモールドタイプのパッケージにおいて、特許文献1記載の半導体装置のように半導体チップの回りを電磁シールドした構造とする場合、リードフレームを半導体チップの下方に配置し、その一部に、半導体チップの上方の蓋体を接触させる必要がある。このような構造とする場合、リードフレームに樹脂をモールドすると、そのモールド時に例えば170℃の高温となるため、リードフレームとモールド樹脂との熱膨張係数の違いにより、特許文献3に記載されるように、プリモールドしたパッケージ本体に反りなどの変形が生じ易い。特に、リードフレームを複数個連続状態に形成して、複数のパッケージ本体を一括して製作する場合に、顕著になる。

本発明は、このような事情に鑑みてなされたもので、プリモールドタイプのパッケージにあってパッケージ本体の反り等の変形を防止することができる半導体装置及びその製造方法を提供することを目的とする。

本発明の半導体装置は、MEMSチップを含む複数の半導体チップを搭載したパッケージ本体が、リードフレームと該リードフレームの一部を埋設状態としたモールド樹脂体とからなり、前記リードフレームに、前記半導体チップの下方に配置されるステージ部と、該ステージ部と間隔を開けて配置され前記半導体チップに接続された複数の端子部と、前記ステージ部に接続状態とされ前記モールド樹脂体の表面に露出した導通フレーム部とが形成され、該導通フレーム部に前記パッケージ本体に固着された導電性材料からなる蓋体が接続された半導体装置であって、前記複数の半導体チップは、前記MEMSチップが前記モールド樹脂体に形成された凹部内に収容されるとともに、該凹部が前記蓋体により閉塞され、MEMSチップ以外の他の半導体チップが前記モールド樹脂体内に埋設され、前記端子部は、前記他の半導体チップに接続され前記モールド樹脂体から一部が露出する外部接続用端子部と、前記MEMSチップ及び前記他の半導体チップの両方に接続された中継端子部とを有し、該中継端子部は、前記MEMSチップに接続された部分が前記凹部内に露出され、前記他の半導体チップに接続された部分が前記モールド樹脂体内に埋設されていることを特徴とする。

この半導体装置は、リードフレームの導通フレーム部と蓋体とを電気的接続状態として、これらリードフレームと蓋体とにより半導体チップを囲った状態とすることができ、内部の半導体チップを有効に電磁シールドすることができる。

この場合、プリモールドタイプのパッケージであるから、リードフレームよりもモールド樹脂体の方が熱膨張係数が大きく、そのため、モールド樹脂体の大きな収縮によって反り等の変形が生じ易い。一方、半導体チップはモールド樹脂体よりも熱膨張係数が小さい。このため、この半導体装置においては、複数の半導体チップのうち、機械要素を有するMEMSチップは凹部に収容するが、MEMSチップ以外の他の半導体チップをモールド樹脂体に埋設状態とすることにより、モールド樹脂体の収縮を半導体チップによって拘束して、反り等の変形の発生を抑制するのである。この場合、モールド樹脂によって埋設したので、ポッティング工程を別途設ける必要がなく、作業性がよい。また、ポッティング樹脂に比べてモールド樹脂の方が硬質であるので、外力が作用したときの歪みの発生等も少なくなる。

この場合、プリモールドタイプのパッケージであるから、リードフレームよりもモールド樹脂体の方が熱膨張係数が大きく、そのため、モールド樹脂体の大きな収縮によって反り等の変形が生じ易い。一方、半導体チップはモールド樹脂体よりも熱膨張係数が小さい。このため、この半導体装置においては、複数の半導体チップのうち、機械要素を有するMEMSチップは凹部に収容するが、MEMSチップ以外の他の半導体チップをモールド樹脂体に埋設状態とすることにより、モールド樹脂体の収縮を半導体チップによって拘束して、反り等の変形の発生を抑制するのである。この場合、モールド樹脂によって埋設したので、ポッティング工程を別途設ける必要がなく、作業性がよい。また、ポッティング樹脂に比べてモールド樹脂の方が硬質であるので、外力が作用したときの歪みの発生等も少なくなる。

すなわち、本発明の半導体装置の製造方法は、前記半導体装置を製造する方法であって、前記リードフレームを形成するリードフレーム形成工程と、前記リードフレームのステージ部に前記他の半導体チップを固定して前記外部接続用端子部及び前記中継端子部に接続状態とする第1の半導体チップ搭載工程と、前記他の半導体チップを搭載した状態のリードフレームに樹脂をモールドすることにより前記凹部を有する前記モールド樹脂体を形成するモールド工程と、前記モールド樹脂体の凹部に前記MEMSチップを収容して該凹部内に露出している前記中継端子部に接続状態とする第2の半導体チップ搭載工程と、前記MEMSチップの上方から前記凹部を閉塞するように前記モールド樹脂体に前記蓋体を固着する蓋体固着工程とを有することを特徴とする。

MEMSチップ以外の他の半導体チップの搭載工程においては、樹脂のモールド前であるから、周囲が囲まれることなく広い空間で作業することができ、作業性がよい。この他の半導体チップも樹脂をモールドした後に搭載する場合であると、この半導体チップが搭載される部分のステージ部に樹脂のバリが生じるなどの問題があり、また、ダイボンド材が端子部の表面にまで流れ出して接触するおそれもあるが、リードフレームに半導体チップを搭載した後に樹脂をモールドするので、そのような不具合も解消できる。

また、本発明の半導体装置において、前記MEMSチップがマイクロフォンチップとされ、前記他の半導体チップが制御回路チップとされ、前記蓋体又はパッケージ本体のいずれかに、前記凹部に連通する音響孔が形成されているものとすることができる。

この半導体装置においては、制御回路チップをポッティング樹脂で覆うのではなく、モールド樹脂によって埋設状態としたことにより、その埋設部分の容積を金型により正確に設定することができる。言い換えれば、埋設部分により形成される凹部の容積を正確に設定することができ、マイクロフォンとしての所望の音響特性をばらつきなく得ることができる。

この半導体装置においては、制御回路チップをポッティング樹脂で覆うのではなく、モールド樹脂によって埋設状態としたことにより、その埋設部分の容積を金型により正確に設定することができる。言い換えれば、埋設部分により形成される凹部の容積を正確に設定することができ、マイクロフォンとしての所望の音響特性をばらつきなく得ることができる。

本発明によれば、導通フレーム部を蓋体に電気的接続状態として、内部に収納される半導体チップの電磁シールドをすることが可能になるとともに、MEMSチップ以外の他の半導体チップをモールド樹脂体に埋設状態としたことにより、モールド樹脂体の熱伸縮を半導体チップによって拘束して、反り等の変形の発生を抑制することができる。また、ポッティング樹脂でなくモールド樹脂によって埋設したので、ポッティング工程を別途設ける必要がなく、作業性がよいとともに、外力が作用したときの歪みの発生等も少なくなり、高い信頼性を維持することができる。

以下、本発明に係る半導体装置の一実施形態を図面を参照しながら説明する。

本実施形態の半導体装置1は、マイクロフォンパッケージであり、図1に蓋体を分離した状態の斜視図を示したように、半導体チップとしてMEMS構造のマイクロフォンチップ2と制御回路チップ3との二つのチップが収納されている。また、そのパッケージ4は、リードフレーム5に箱型のモールド樹脂体6を一体成形してなるパッケージ本体7と、このパッケージ本体7の上方を閉塞する蓋体8とを備える構成とされ、両半導体チップのうち、制御回路チップ3はモールド樹脂体6内に埋設状態とされ、マイクロフォンチップ2は、モールド樹脂体6に形成した凹部9内に収容されている。

この半導体装置1は、リードフレーム5が複数並べられた状態で形成され、後述のように加工され、それぞれに半導体チップ2,3が搭載されて組み立てられた後に、個々に分離されたものである。

本実施形態の半導体装置1は、マイクロフォンパッケージであり、図1に蓋体を分離した状態の斜視図を示したように、半導体チップとしてMEMS構造のマイクロフォンチップ2と制御回路チップ3との二つのチップが収納されている。また、そのパッケージ4は、リードフレーム5に箱型のモールド樹脂体6を一体成形してなるパッケージ本体7と、このパッケージ本体7の上方を閉塞する蓋体8とを備える構成とされ、両半導体チップのうち、制御回路チップ3はモールド樹脂体6内に埋設状態とされ、マイクロフォンチップ2は、モールド樹脂体6に形成した凹部9内に収容されている。

この半導体装置1は、リードフレーム5が複数並べられた状態で形成され、後述のように加工され、それぞれに半導体チップ2,3が搭載されて組み立てられた後に、個々に分離されたものである。

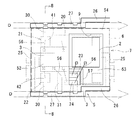

図4は外枠部11の中にリードフレーム5を一定のピッチで並べて形成したリードフレーム連続成形体12の展開状態を示しており、図5は、その裏面を示している。この展開状態のリードフレーム連続成形体についても、後述の折り曲げ加工後のリードフレーム連続成形体についても、各部の構成要素等には同一符号を付している。また、この明細書中では、1個単位のものをリードフレームと称しており、以下では図4の上下方向を縦方向、左右方向を横方向というものとする。また、図4中、符号13は、後述するように蓋体8を取り付ける際等に金型のガイドピンを挿入するためのガイド孔を示しており、図示例では、外枠部11の上下方向の両端部に一定のピッチで並んで配置されている(図には一方の端部におけるガイド孔のみ示している)。

各リードフレーム5は、図6に1個のリードフレームを示したように(この図6は展開状態のリードフレームを示している)、平板状のステージ部20と、入力用、出力用の2個の外部接続用端子部21,22と、2個の中継用端子部23,24とが相互に間隔をあけて配置され、そのステージ部20の両側部にそれぞれ連結フレーム部25が接続されている。これら連結フレーム部25は、ステージ部20の側縁に沿って(縦方向に沿って)延在し、ステージ部20の端部よりも外方に突出しており、両連結フレーム部25の先端部の間に、ステージ部20の外側に配置されるように横方向に沿う導通フレーム部26及び補助フレーム部27が相互に連結状態に形成されている。そして、これら導通フレーム部26、補助フレーム部27、ステージ部20、各外部接続用端子部21,22及び中継用端子部23,24が全体として横長の矩形状をなすように配置されている。

ステージ部20は、矩形状の一方の側部(図示例では右側部)は直線状に形成されるが、他方の側部(左側部)における両隅部の2箇所がそれぞれ矩形状に切り欠かれた形状とされている。この場合、その一方の切欠部28はほぼ正方形状に形成され、他方の切欠部29は横方向に長い長方形状に形成され、一方の切欠部28に一つの外部接続用端子部21が配置され、他方の切欠部29に他の外部接続用端子部22及び2個の中継用端子部23,24が配置されている。

これら端子部21〜24のうち、外部接続用端子部21,22は、ほぼ正方形状に形成され、中継用端子部23,24は、横方向に沿う短冊状に形成され、それぞれ切欠部28,29内でステージ部20との間に一定の間隔をあけて配置され、補助フレーム部27に、この補助フレーム部27と直交するアーム部30,31を介して接続されている。なお、両中継用端子部23,24は、切欠部29内に相互に平行に横方向に沿って配置され、それらの端部とアーム部31とが直交して形成されている。

ステージ部20は、矩形状の一方の側部(図示例では右側部)は直線状に形成されるが、他方の側部(左側部)における両隅部の2箇所がそれぞれ矩形状に切り欠かれた形状とされている。この場合、その一方の切欠部28はほぼ正方形状に形成され、他方の切欠部29は横方向に長い長方形状に形成され、一方の切欠部28に一つの外部接続用端子部21が配置され、他方の切欠部29に他の外部接続用端子部22及び2個の中継用端子部23,24が配置されている。

これら端子部21〜24のうち、外部接続用端子部21,22は、ほぼ正方形状に形成され、中継用端子部23,24は、横方向に沿う短冊状に形成され、それぞれ切欠部28,29内でステージ部20との間に一定の間隔をあけて配置され、補助フレーム部27に、この補助フレーム部27と直交するアーム部30,31を介して接続されている。なお、両中継用端子部23,24は、切欠部29内に相互に平行に横方向に沿って配置され、それらの端部とアーム部31とが直交して形成されている。

導通フレーム部26は、長方形状の切欠部29により残されたステージ部20の端部と間隔をあけてこの端部の辺に沿って配置されている。また、この導通フレーム部26の端部から屈曲部32を介して外方に張り出すように補助フレーム部27が連結され、この補助フレーム部27が長方形状の切欠部29に沿って横方向に延びて配置され、その端部に連結フレーム部25が連結されている。したがって、これら導通フレーム部26、屈曲部32、補助フレーム部27がステージ部20の一方の端部の外側に配置され、これらの両端から直交する連結フレーム部25がステージ部20の両側部に接続されていることにより、これら導通フレーム部26、屈曲部32、補助フレーム部27及び両連結フレーム部25が、ステージ部20のほぼ半分を囲むように構成されている。また、隣接するリードフレーム5においては、図4に示すように、連結フレーム部25の長さ方向の途中位置どうしが図示例では2本の短尺のブリッジ部(連結部)33によって連結状態とされている。

このように導通フレーム部26、屈曲部32、補助フレーム部27及び両連結フレーム部25が連結状態とされ、その両端部の連結フレーム部25が隣接状態の両リードフレーム5間で相互に連結状態とされていることにより、図4に示すように、各リードフレーム5の一端部側に配置される導通フレーム26、屈曲部32、補助フレーム部27及び連結フレーム部25が一列に連なった状態とされ、その両端が外枠部11に接続されている。そして、これら連結状態の導通フレーム26、屈曲部32、補助フレーム部27及び連結フレーム部25により、各リードフレーム5の一端部側を列に沿って連結状態として外枠部11に支持する支持フレーム部34が構成される。具体的には、この支持フレーム部34には、その片側に、各リードフレーム5のステージ部20が連結フレーム部25を介して接続されるとともに、2個の外部接続用端子部21,22のうちの1個の端子部22と両中継用端子部23,24とがそれぞれアーム部30,31を介して接続され、支持フレーム部34の反対側に、隣接する他の列のリードフレーム5に属する1個の端子部21がアーム部30を介して接続されている。

なお、各端子部21〜24のアーム部30,31の基端部においては、補助フレーム部27との接続部分の表面がハーフエッチングされ、補助フレーム部27等の他の表面よりも低い凹状部35とされている。

なお、各端子部21〜24のアーム部30,31の基端部においては、補助フレーム部27との接続部分の表面がハーフエッチングされ、補助フレーム部27等の他の表面よりも低い凹状部35とされている。

一方、このリードフレーム連続成形体12の裏面は、図5にハッチングでハーフエッチング領域を示したように、ステージ部20の大部分がハーフエッチングされている。すなわち、2個の外部接続用端子部21,22が配置されている側部(左側部)とは反対側のステージ部20の側部の両隅部が両端子部21,22に対応して矩形状に残された状態で、他の部分が板厚の半分程度までハーフエッチングされた凹状部36とされ、その残された両隅部が2個の端子部21,22とほぼ同じ形状の矩形状とされており、これら端子部21,22及びステージ部20の両隅部の表面が外部接続面37〜40とされ、これら4個の外部接続面37〜40がリードフレーム5全体の四隅付近に配置されるようになっている。なお、各外部接続端子部21,22の表面が制御回路チップ3に接続される内部接続面41,42とされている。

また、両中継用端子部23,24は、その下面の全面がハーフエッチングされている。

また、両中継用端子部23,24は、その下面の全面がハーフエッチングされている。

そして、このリードフレーム連続成形体12は、連結フレーム部25及びアーム部30,31が、その両端部で折り曲げ変形され、支持フレーム部34は外枠部11と同一平面上に配置されるが、連結フレーム部25及びアーム部30,31は、それぞれ導通フレーム部26側の基端から先端に向けて下り勾配に傾斜して配置され、これらの先端に接続状態のステージ部20と各端子部21〜24とは、支持フレーム部34よりも低い位置で同一平面上に配置される。

このように加工されたリードフレーム連続成形体12に対して、図4の二点鎖線で示すようにモールド樹脂体6を相互に連結状態とした一体構造のモールド樹脂成形体50が形成される。

また、このモールド樹脂成形体50には、両半導体チップのうち、制御回路チップ3が埋設状態とされ、マイクロフォンチップ2はモールド樹脂体6に形成した凹部9内に収容され、その凹部9を閉塞する蓋体8が固定されて、個々に分割されることにより、各リードフレーム5にモールド樹脂体6を一体化したパッケージ本体7と蓋体8とによりマイクロフォンチップ2及び制御回路チップ3を収納した半導体装置1が構成される。本発明では、このリードフレーム連続成形体12にモールド樹脂成形体50が一体に形成された状態のものをパッケージ本体連続成形体51と称しており、複数のパッケージ本体7が相互に連結状態に形成される。

また、このモールド樹脂成形体50には、両半導体チップのうち、制御回路チップ3が埋設状態とされ、マイクロフォンチップ2はモールド樹脂体6に形成した凹部9内に収容され、その凹部9を閉塞する蓋体8が固定されて、個々に分割されることにより、各リードフレーム5にモールド樹脂体6を一体化したパッケージ本体7と蓋体8とによりマイクロフォンチップ2及び制御回路チップ3を収納した半導体装置1が構成される。本発明では、このリードフレーム連続成形体12にモールド樹脂成形体50が一体に形成された状態のものをパッケージ本体連続成形体51と称しており、複数のパッケージ本体7が相互に連結状態に形成される。

その1個ずつのパッケージ本体7の部分についての構造を図9により説明すると、このパッケージ本体7のモールド樹脂体6は、制御回路チップ3を埋設状態とした埋設部52と、この埋設部52に隣接して上方を開放状態とした凹部9を形成する底板部53及び該底板部53の周縁部から立設した周壁部54とを備える構成とされ、その凹部9の底板部53上にマイクロフォンチップ2が搭載されている。

制御回路チップ3は、埋設部52の中で、ステージ部20の上にダイボンド材55によって固定され(図8参照)、両外部接続用端子部21,22の内部接続面41,42、ステージ部20及び中継用端子部23,24にそれぞれボンディングワイヤ56によって接続されている。

埋設部52は、両外部接続用端子部21,22の下面の外部接続面37,38を除き、この外部接続用端子部21,22、制御回路チップ3及びそのボンディングワイヤ56、ステージ部20の半分及び中継用端子部23,24の半分、さらに連結フレーム部25の一方(図9の左側部の連結フレーム部)を一括して埋設状態としており、その上端面は平坦面に形成されている。一方、凹部9には、その底板部53内にステージ部20の残りの半分が下面の外部接続面39,40を除き埋設状態とされるとともに、底板部53の上面に、両中継用端子部23,24の残り半分が露出している。また、この凹部9に露出している中継用端子部23,24の回りを囲むように立ち上げ壁57が底板部53上にリブ状に突出して形成されている。この立ち上げ壁57の高さは、凹部9に収容されるマイクロフォンチップ2の高さよりは低いが、マイクロフォンチップ2を固定するためのダイボンド材58の塗布厚さよりも大きく、マイクロフォンチップ2の下方からダイボンド材58がはみ出しても乗り越えられない程度の高さに設定される。

制御回路チップ3は、埋設部52の中で、ステージ部20の上にダイボンド材55によって固定され(図8参照)、両外部接続用端子部21,22の内部接続面41,42、ステージ部20及び中継用端子部23,24にそれぞれボンディングワイヤ56によって接続されている。

埋設部52は、両外部接続用端子部21,22の下面の外部接続面37,38を除き、この外部接続用端子部21,22、制御回路チップ3及びそのボンディングワイヤ56、ステージ部20の半分及び中継用端子部23,24の半分、さらに連結フレーム部25の一方(図9の左側部の連結フレーム部)を一括して埋設状態としており、その上端面は平坦面に形成されている。一方、凹部9には、その底板部53内にステージ部20の残りの半分が下面の外部接続面39,40を除き埋設状態とされるとともに、底板部53の上面に、両中継用端子部23,24の残り半分が露出している。また、この凹部9に露出している中継用端子部23,24の回りを囲むように立ち上げ壁57が底板部53上にリブ状に突出して形成されている。この立ち上げ壁57の高さは、凹部9に収容されるマイクロフォンチップ2の高さよりは低いが、マイクロフォンチップ2を固定するためのダイボンド材58の塗布厚さよりも大きく、マイクロフォンチップ2の下方からダイボンド材58がはみ出しても乗り越えられない程度の高さに設定される。

そして、この底板部53の上に、マイクロフォンチップ2がダイボンド材58によって固定され、底板部53に露出状態とされている中継用端子部23,24にボンディングワイヤ56によって接続される(図10参照)。マイクロフォンチップ2は、音響等の圧力変動に応じて振動するダイヤフラム電極と固定電極とが対向配置され、ダイヤフラム電極の振動に伴う静電容量変化を検出するものである。また、制御回路チップ3は、マイクロフォンチップ2への電源の供給回路、マイクロフォンチップ2からの出力信号の増幅器等を備える構成とされている。この場合、底板部53にマイクロフォンチップ2を固定するダイボンド材58は絶縁性樹脂によって構成されるが、ステージ部20に制御回路チップ3を固定するダイボンド材55は導電性樹脂によって構成される。

一方、周壁部54は、埋設部52から連続する底板部53の三辺に、埋設部52と同じ高さに垂直に立設されており、その内部に右側部の連結フレーム部25が埋設され、この連結フレーム部25に連続する導通フレーム部26の表面が周壁部54の上端面に露出している。

このように構成したパッケージ本体7に被せられる蓋体8も、リードフレーム5と同様に、銅材等の導電性金属材料からなる帯状金属板を加工することにより、複数個並べられた状態で形成され、後述するようにパッケージ本体7に組み合わせた後に、個々に分離されるものである。図12に蓋体8を一定のピッチで並べて形成した連続成形体61を示している。この連続成形体61では、各蓋体8は、外枠部62との間又は隣接する蓋体8相互の間が接続フレーム部63により接続され、リードフレーム5と同じピッチで縦横に並べられる。また、図4等のリードフレーム連続成形体12の場合と同様に、ガイドピンが挿入されるガイド孔13が外枠部62の両側部にリードフレーム連続成形体12と同じピッチで配列されている。

個々の蓋体8は、パッケージ本体7の埋設部52及び周壁部54の上端面を覆う矩形の平板状に形成されており、パッケージ本体7の凹部9に対応する位置のほぼ中央に音響孔64が貫通状態に形成されている。そして、この蓋体8をパッケージ本体7に重ねると、パッケージ本体7の埋設部52及び周壁部54の上端面に当接し、パッケージ本体7の凹部9においては底板部53と蓋体8とが対向し、凹部9がマイクロフォンチップ収納空間として閉塞され、その収納空間65(図2参照)が蓋体8の音響孔64によって外部に連通させた状態とされる構成である。

この場合、これらパッケージ本体7と蓋体8とは、パッケージ本体7の埋設部52及び周壁部54の上端面に蓋体8の下面が導電性接着剤66によって固着されるようになっており、パッケージ本体7の周壁部54の上端面に露出しているリードフレーム5の導通フレーム部26が導電性接着剤66を介して蓋体8と電気的接続状態とされる。したがって、これらパッケージ本体7に蓋体8を固着してなるパッケージ4は、蓋体8からリードフレーム5のステージ部20の間が電気的接続状態となってマイクロフォンチップ2及び制御回路チップ3を囲った状態とするのである。

この場合、これらパッケージ本体7と蓋体8とは、パッケージ本体7の埋設部52及び周壁部54の上端面に蓋体8の下面が導電性接着剤66によって固着されるようになっており、パッケージ本体7の周壁部54の上端面に露出しているリードフレーム5の導通フレーム部26が導電性接着剤66を介して蓋体8と電気的接続状態とされる。したがって、これらパッケージ本体7に蓋体8を固着してなるパッケージ4は、蓋体8からリードフレーム5のステージ部20の間が電気的接続状態となってマイクロフォンチップ2及び制御回路チップ3を囲った状態とするのである。

次に、このように構成される半導体装置1の製造方法について説明する。この製造方法は、リードフレーム形成工程、制御回路チップ搭載工程(第1の半導体チップ搭載工程)、モールド工程、マイクロフォンチップ搭載工程(第2の半導体チップ搭載工程)、及び蓋体形成工程、蓋体固着工程、切断工程から構成される。以下、その工程順に説明する。

(リードフレーム形成工程)

まず、リードフレーム連続成形体12となる帯状金属板の必要な個所にマスキングをしてエッチング処理することにより、図4に示す表面側のハッチング領域及び図5に示す裏面側のハッチング領域をそれぞれ板厚の半分程度までハーフエッチングする。そして、エッチング加工によって外形を成形し、外枠部11の内側に展開状態のリードフレーム5を形成する。この状態では、図4及び図5に示すように、外枠部11の内側に、導通フレーム部26、補助フレーム部27、連結フレーム部25が連続した支持フレーム部34が横一列状態に形成され、この支持フレーム部34により一端部が支持された状態に展開状態のリードフレーム5が形成される。また、このエッチング加工時に外枠部11のガイド孔13も成形しておく。

この後、連結フレーム部25及び各端子部21〜24のアーム部30,31をプレスによって曲げ変形させることにより、図7及び図8に示すように、支持フレーム部34に対してステージ部20及び端子部21〜24を押し下げた状態とする。

(リードフレーム形成工程)

まず、リードフレーム連続成形体12となる帯状金属板の必要な個所にマスキングをしてエッチング処理することにより、図4に示す表面側のハッチング領域及び図5に示す裏面側のハッチング領域をそれぞれ板厚の半分程度までハーフエッチングする。そして、エッチング加工によって外形を成形し、外枠部11の内側に展開状態のリードフレーム5を形成する。この状態では、図4及び図5に示すように、外枠部11の内側に、導通フレーム部26、補助フレーム部27、連結フレーム部25が連続した支持フレーム部34が横一列状態に形成され、この支持フレーム部34により一端部が支持された状態に展開状態のリードフレーム5が形成される。また、このエッチング加工時に外枠部11のガイド孔13も成形しておく。

この後、連結フレーム部25及び各端子部21〜24のアーム部30,31をプレスによって曲げ変形させることにより、図7及び図8に示すように、支持フレーム部34に対してステージ部20及び端子部21〜24を押し下げた状態とする。

(制御回路チップ搭載工程)

次いで、このように成形したリードフレーム5の連続成形体12に両半導体チップのうちの制御回路チップ3を搭載する。この制御回路チップ3は、導電性のダイボンド材55によってステージ部20に固着され、二つの外部接続用端子部21,22の内部接続面41,42及び中継用端子部23,24にそれぞれボンディングワイヤ56によって接続される。このチップ搭載作業は、リードフレーム5に樹脂をモールドする前の作業であり、搭載領域の周囲が開放状態とされているため、ダイボンド作業、ワイヤボンド作業とも容易に実施することができる。

(モールド工程)

そして、この制御回路チップ3を搭載したリードフレーム連続成形体12を射出成形金型内に配置し、制御回路チップ3とともに各リードフレーム5を埋設するように樹脂を射出成形してモールド樹脂体6を成形する。

この場合、図8に示すように、射出成形金型は、その上型と71下型72とによりリードフレーム連続成形体12の外枠部11を隙間なく挟持し、その内側の各リードフレーム5全体を一括して覆うように広いキャビティ73が形成され、各支持フレーム部34の上面と凹部9に配置されるべき両中継用端子部23,24の半分とが上型71に接触し、各リードフレーム5の裏面の4箇所の外部接続面37〜40が下型72に接触した状態となる。また、両中継用端子部23,24は、裏面がハーフエッチングされていて薄肉になっているので、下型72に突出させた小径のピン74の先端で裏面が支持され、このピン74と上型71のキャビティ面との間で挟持される。

次いで、このように成形したリードフレーム5の連続成形体12に両半導体チップのうちの制御回路チップ3を搭載する。この制御回路チップ3は、導電性のダイボンド材55によってステージ部20に固着され、二つの外部接続用端子部21,22の内部接続面41,42及び中継用端子部23,24にそれぞれボンディングワイヤ56によって接続される。このチップ搭載作業は、リードフレーム5に樹脂をモールドする前の作業であり、搭載領域の周囲が開放状態とされているため、ダイボンド作業、ワイヤボンド作業とも容易に実施することができる。

(モールド工程)

そして、この制御回路チップ3を搭載したリードフレーム連続成形体12を射出成形金型内に配置し、制御回路チップ3とともに各リードフレーム5を埋設するように樹脂を射出成形してモールド樹脂体6を成形する。

この場合、図8に示すように、射出成形金型は、その上型と71下型72とによりリードフレーム連続成形体12の外枠部11を隙間なく挟持し、その内側の各リードフレーム5全体を一括して覆うように広いキャビティ73が形成され、各支持フレーム部34の上面と凹部9に配置されるべき両中継用端子部23,24の半分とが上型71に接触し、各リードフレーム5の裏面の4箇所の外部接続面37〜40が下型72に接触した状態となる。また、両中継用端子部23,24は、裏面がハーフエッチングされていて薄肉になっているので、下型72に突出させた小径のピン74の先端で裏面が支持され、このピン74と上型71のキャビティ面との間で挟持される。

このようにして各リードフレーム5に樹脂をモールドすると、図9に示すように、制御回路チップ3及びそのボンディングワイヤ55が接続されている両外部接続用端子部21,22、中継用端子部23,24の半分が埋設部52内に埋設状態とされるとともに、この埋設部52及び周壁部54の部分を連続状態としたモールド樹脂成形体50が各リードフレーム5に一体に成形された状態となる。

(マイクロフォンチップ搭載工程)

その後、このモールド樹脂成形体50の各モールド樹脂体6における凹部9の底板部53の上に、図10に示すようにマイクロフォンチップ2を絶縁性のダイボンド材58により固着し、底板部53に露出している両中継用端子部23,24にボンディングワイヤ56によって接続状態とすると、マイクロフォンチップ2と制御回路チップ3とが中継用端子部23,24を介して相互に接続状態となる。

(蓋体形成工程)

一方、蓋体8についても、帯状金属板をエッチング加工して外形を成形することにより、図12に示すように、外枠部62の中で接続フレーム部63により相互に接続状態とされた蓋体8の連続成形体61を形成しておく。また、このときのエッチング加工によって外枠部62のガイド孔13も成形される。このガイド孔13はリードフレーム5のガイド孔13と同じ位置に、同じピッチで形成される。

(マイクロフォンチップ搭載工程)

その後、このモールド樹脂成形体50の各モールド樹脂体6における凹部9の底板部53の上に、図10に示すようにマイクロフォンチップ2を絶縁性のダイボンド材58により固着し、底板部53に露出している両中継用端子部23,24にボンディングワイヤ56によって接続状態とすると、マイクロフォンチップ2と制御回路チップ3とが中継用端子部23,24を介して相互に接続状態となる。

(蓋体形成工程)

一方、蓋体8についても、帯状金属板をエッチング加工して外形を成形することにより、図12に示すように、外枠部62の中で接続フレーム部63により相互に接続状態とされた蓋体8の連続成形体61を形成しておく。また、このときのエッチング加工によって外枠部62のガイド孔13も成形される。このガイド孔13はリードフレーム5のガイド孔13と同じ位置に、同じピッチで形成される。

(蓋体固着工程)

このようにしてリードフレーム5にモールド樹脂成形体50を一体化させたパッケージ本体連続成形体51及び蓋体連続成形体61をそれぞれ製作した後、各蓋体8をモールド樹脂成形体50の埋設部52及び周壁部54の上端面に導電性接着剤66を介して固着する。このとき、蓋体連続成形体61及びリードフレーム連続成形体12の各外枠部11,62のガイド孔13にピンを挿入した状態とすることにより、両者が位置合わせされる。この状態では、各リードフレーム5は、隣接するリードフレーム5に支持フレーム部34によって列毎に連結状態とされているとともに、これらを一括してモールド樹脂成形体50が覆っていることにより、パッケージ本体7としては複数個が縦横に連なった状態となっており、蓋体8もリードフレーム5と同様に接続フレーム部63によりリードフレーム5と同じピッチで複数個が連結状態とされている。

このようにしてリードフレーム5にモールド樹脂成形体50を一体化させたパッケージ本体連続成形体51及び蓋体連続成形体61をそれぞれ製作した後、各蓋体8をモールド樹脂成形体50の埋設部52及び周壁部54の上端面に導電性接着剤66を介して固着する。このとき、蓋体連続成形体61及びリードフレーム連続成形体12の各外枠部11,62のガイド孔13にピンを挿入した状態とすることにより、両者が位置合わせされる。この状態では、各リードフレーム5は、隣接するリードフレーム5に支持フレーム部34によって列毎に連結状態とされているとともに、これらを一括してモールド樹脂成形体50が覆っていることにより、パッケージ本体7としては複数個が縦横に連なった状態となっており、蓋体8もリードフレーム5と同様に接続フレーム部63によりリードフレーム5と同じピッチで複数個が連結状態とされている。

(切断工程)

次に、これらリードフレーム連続成形体12、モールド樹脂成形体50、及び蓋体連続成形体61をダイシング加工によって同時に切断しながら個々の半導体装置1に切り離す。

このダイシング加工は、図4に一点鎖線の矢印で示したように、一定幅の切断ラインに沿って行われる。この切断ラインの幅はダイシング刃の厚さを示している。

この切断ラインのうち、リードフレーム5の列に沿う方向においては、図10に示したように、横一列に配置される支持フレーム部34における導通フレーム部26の外側に切断ラインDが配置され、その幅が補助フレーム部27の幅より広く形成されており、補助フレーム部27を削除するように切断することになる。この切断により、補助フレーム部27に接続されていた各アーム部30,31が切り離され、このアーム部30,31に接続状態の外部接続用端子部21,22及び中継用端子部23,24が導通フレーム部26から分離して独立状態とされる。

次に、これらリードフレーム連続成形体12、モールド樹脂成形体50、及び蓋体連続成形体61をダイシング加工によって同時に切断しながら個々の半導体装置1に切り離す。

このダイシング加工は、図4に一点鎖線の矢印で示したように、一定幅の切断ラインに沿って行われる。この切断ラインの幅はダイシング刃の厚さを示している。

この切断ラインのうち、リードフレーム5の列に沿う方向においては、図10に示したように、横一列に配置される支持フレーム部34における導通フレーム部26の外側に切断ラインDが配置され、その幅が補助フレーム部27の幅より広く形成されており、補助フレーム部27を削除するように切断することになる。この切断により、補助フレーム部27に接続されていた各アーム部30,31が切り離され、このアーム部30,31に接続状態の外部接続用端子部21,22及び中継用端子部23,24が導通フレーム部26から分離して独立状態とされる。

一方、リードフレーム5の列に直交する方向のダイシング加工においては、隣接するリードフレーム5で連結状態となっている両連結フレーム部25の間で切断され、これら連結フレーム部25が分離されて、個々のパッケージ4に形成される。

そして、この列方向及びその直交方向に沿う両ダイシング加工により、パッケージ4の周壁部54の外縁が形成され、平面視矩形状のパッケージ4にマイクロフォンチップ2及び制御回路リップ3を搭載した状態の半導体装置1を得ることができる。

そして、この列方向及びその直交方向に沿う両ダイシング加工により、パッケージ4の周壁部54の外縁が形成され、平面視矩形状のパッケージ4にマイクロフォンチップ2及び制御回路リップ3を搭載した状態の半導体装置1を得ることができる。

このようにして製造した半導体装置1は、その裏面に露出している両端子部21,22の外部接続面37,38及びステージ部20と一体の接地用の2個の外部接続面39,40をそれぞれ基板にはんだ付けすることにより実装される。この場合、半導体装置1は、図2に示すように、底板部53内に埋設されているステージ部20がマイクロフォンチップ2及び制御回路チップ3の下方に配置され、このステージ部20に制御回路チップ3が接続され、ステージ部20に連結フレーム部25を介して一体の導通フレーム部26が周壁部54の上端面で導電性接着剤66を介して蓋体8に接続され、その蓋体8がマイクロフォンチップ2及び制御回路チップ3の上方を覆った状態としている。したがって、マイクロフォンチップ2及び制御回路チップ3は、その周囲をステージ部20及び蓋体8によって囲まれた状態となり、このステージ部20の外部接続面39,40が基板を介して接地状態とされることにより、マイクロフォンチップ2及び制御回路チップ3を外部磁界からシールドすることができる。

この半導体装置1においては、リードフレーム5に樹脂をモールドする前に、そのステージ部20のほぼ半分に制御回路チップ3を固定し、その状態でモールド樹脂体6を成形するようにしたから、樹脂モールド時のリードフレーム5の熱伸縮をこのリードフレーム5より熱膨張係数が小さい制御回路チップ3により拘束して、反り等の変形の発生を防止することができる。また、樹脂をモールドした後に制御回路チップ3を搭載する場合に生じる可能性のある不具合も解消できる。

例えば、リードフレーム5に樹脂をモールドした後に制御回路チップ3を搭載する場合、制御回路チップ3を搭載する領域では、リードフレーム5のステージ部20及び端子部21,22をモールド樹脂体6から露出させておく必要があるが、射出成形金型のキャビティ面との接触が不十分であると、ステージ部20の表面に樹脂が薄膜状に生じ易く、導電性のダイボンド材55による接着を損なうことになる。また、ステージ部20と端子部21,22とがモールド樹脂体を介して面一に形成される場合、導電性のダイボンド材55が端子部21,22に流れて接触するおそれもある。本実施形態の場合は、樹脂のモールド前に制御回路チップ3をリードフレーム5のステージ部20に直接搭載するのであり、また、ステージ部20と端子部21,22とは分離されているため、そのような問題は生じない。

また、リードフレーム5に樹脂をモールドした後に制御回路チップ3を搭載する場合、従来では制御回路チップ3及びボンディングワイヤ56をポッティング樹脂によって封止することが行われるが、その樹脂量にばらつきが生じ易く、それによって残る空間部の容積が不均一になることから、マイクロフォンとしての音響特性にばらつきが生じる。本実施形態のように射出成形のモールド樹脂によって封止すれば、金型によって容積が規制され、凹部9を正確にかつ均一な容積に形成することができ、音響特性のばらつきを小さくすることができる。

また、ポッティング樹脂よりもモールド樹脂の方が硬質であるので、振動等の外力が作用した場合でも、歪みの発生等も少なくなり、機械的強度に優れる半導体装置とすることができる。

例えば、リードフレーム5に樹脂をモールドした後に制御回路チップ3を搭載する場合、制御回路チップ3を搭載する領域では、リードフレーム5のステージ部20及び端子部21,22をモールド樹脂体6から露出させておく必要があるが、射出成形金型のキャビティ面との接触が不十分であると、ステージ部20の表面に樹脂が薄膜状に生じ易く、導電性のダイボンド材55による接着を損なうことになる。また、ステージ部20と端子部21,22とがモールド樹脂体を介して面一に形成される場合、導電性のダイボンド材55が端子部21,22に流れて接触するおそれもある。本実施形態の場合は、樹脂のモールド前に制御回路チップ3をリードフレーム5のステージ部20に直接搭載するのであり、また、ステージ部20と端子部21,22とは分離されているため、そのような問題は生じない。

また、リードフレーム5に樹脂をモールドした後に制御回路チップ3を搭載する場合、従来では制御回路チップ3及びボンディングワイヤ56をポッティング樹脂によって封止することが行われるが、その樹脂量にばらつきが生じ易く、それによって残る空間部の容積が不均一になることから、マイクロフォンとしての音響特性にばらつきが生じる。本実施形態のように射出成形のモールド樹脂によって封止すれば、金型によって容積が規制され、凹部9を正確にかつ均一な容積に形成することができ、音響特性のばらつきを小さくすることができる。

また、ポッティング樹脂よりもモールド樹脂の方が硬質であるので、振動等の外力が作用した場合でも、歪みの発生等も少なくなり、機械的強度に優れる半導体装置とすることができる。

図13は、他の実施形態を示しており、この実施形態の半導体装置81では、マイクロフォンチップ82に貫通電極83が形成され、その一端がマイクロフォンチップ82の裏面に到達している。そして、パッケージ本体7の中継用端子部23,24の上に貫通電極83が重ねられ、これらをはんだ84により接続した状態として搭載されている。

したがって、このマイクロフォンチップ82の搭載作業としては、マイクロフォンチップ82の貫通電極83を中継用端子部23,24に位置合わせした状態で固定するだけでよく、ワイヤボンディング作業を省略することができ、限られた空間内での搭載作業を効率的に行うことができる。

したがって、このマイクロフォンチップ82の搭載作業としては、マイクロフォンチップ82の貫通電極83を中継用端子部23,24に位置合わせした状態で固定するだけでよく、ワイヤボンディング作業を省略することができ、限られた空間内での搭載作業を効率的に行うことができる。

なお、本発明は上記実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の変更を加えることが可能である。

例えば、上記実施形態では、蓋体を平板状に形成したが、若干の絞り加工を施すようにしてもよい。また、蓋体をリードフレームと同じ金属材で形成したが、非導電性の基板の少なくともパッケージ本体への固着面に導電性フィルムや金属メッキ等の導電層を形成した構成としてもよい。

また、上記実施形態では半導体装置としてマイクロフォンパッケージに適用した例を示したが、マイクロフォン以外にも、圧力センサ、加速度センサ、磁気センサ、流量センサ、風圧センサ、超音波センサ等にも適用することが可能である。この場合、上記実施形態のマイクロフォンにおいては、音響孔のような内部空間と外部とを連通させる連通孔が必要であったが、センサの種類によっては連通孔が不要になる場合や、流量センサのように二つの連通孔が必要になる場合がある。

また、マイクロフォンパッケージに適用する場合でも、各パッケージとも同じ仕様にして一つずつ分割したが、例えば隣接する4個のパッケージ本体について、内部に収納するマイクロフォンチップの感度を異なるものとし、これら4個を連結状態として一つのユニットとして分割形成することにより、指向性を有するマイクロフォンとすることもできる。

さらに、音響孔等の貫通孔を形成する場合、実施形態では蓋体に形成したが、パッケージ本体の底板部に形成するようにしてもよく、その場合、モールド樹脂によって貫通孔の周囲を囲むように筒状に壁を設けることにより、ダイボンド材が貫通孔に流れ込まないようにするとよい。

例えば、上記実施形態では、蓋体を平板状に形成したが、若干の絞り加工を施すようにしてもよい。また、蓋体をリードフレームと同じ金属材で形成したが、非導電性の基板の少なくともパッケージ本体への固着面に導電性フィルムや金属メッキ等の導電層を形成した構成としてもよい。

また、上記実施形態では半導体装置としてマイクロフォンパッケージに適用した例を示したが、マイクロフォン以外にも、圧力センサ、加速度センサ、磁気センサ、流量センサ、風圧センサ、超音波センサ等にも適用することが可能である。この場合、上記実施形態のマイクロフォンにおいては、音響孔のような内部空間と外部とを連通させる連通孔が必要であったが、センサの種類によっては連通孔が不要になる場合や、流量センサのように二つの連通孔が必要になる場合がある。

また、マイクロフォンパッケージに適用する場合でも、各パッケージとも同じ仕様にして一つずつ分割したが、例えば隣接する4個のパッケージ本体について、内部に収納するマイクロフォンチップの感度を異なるものとし、これら4個を連結状態として一つのユニットとして分割形成することにより、指向性を有するマイクロフォンとすることもできる。

さらに、音響孔等の貫通孔を形成する場合、実施形態では蓋体に形成したが、パッケージ本体の底板部に形成するようにしてもよく、その場合、モールド樹脂によって貫通孔の周囲を囲むように筒状に壁を設けることにより、ダイボンド材が貫通孔に流れ込まないようにするとよい。

また、リードフレームの外形の成形をエッチング加工によって行うようにしているが、プレスによって打ち抜き成形してもよい。

さらに、パッケージ本体連続成形体に蓋体連続成形体を導電性接着剤を介して固着する場合、パッケージ本体連続成形体の周壁部を上方に向け、その上端面に導電性接着剤を塗布して蓋体連続成形体を重ねる方法としてもよいし、逆に、蓋体連続成形体を裏返し状態で配置し、各蓋体の周縁部に導電性接着剤を塗布して、その上に裏返し状態のパッケージ本体連続成形体を重ねる方法としてもよい。後者の場合、導電性接着剤が周壁部から底板部に垂れることを確実に防止できる。

さらに、パッケージ本体連続成形体に蓋体連続成形体を導電性接着剤を介して固着する場合、パッケージ本体連続成形体の周壁部を上方に向け、その上端面に導電性接着剤を塗布して蓋体連続成形体を重ねる方法としてもよいし、逆に、蓋体連続成形体を裏返し状態で配置し、各蓋体の周縁部に導電性接着剤を塗布して、その上に裏返し状態のパッケージ本体連続成形体を重ねる方法としてもよい。後者の場合、導電性接着剤が周壁部から底板部に垂れることを確実に防止できる。

1…半導体装置、2…マイクロフォンチップ(MEMSチップ、半導体チップ)、3…制御回路チップ(半導体チップ)、4…パッケージ、5…リードフレーム、6…モールド樹脂体、7…パッケージ本体、8…蓋体、11…外枠部、12…リードフレーム連続成形体、13…ガイド孔、20…ステージ部、21,22…外部接続用端子部、23,24…中継用端子部、25…連結フレーム部、26…導通フレーム部、27…補助フレーム部、28,29…切欠部、30,31…アーム部、32…屈曲部、33…ブリッジ部、34…支持フレーム部、35,36…凹状部、37〜40…外部接続面、41,42…内部接続面、50…モールド樹脂成形体、51…パッケージ本体連続成形体、52…埋設部、53…底板部、54…周壁部、55…ダイボンド材、56…ボンディングワイヤ、57…立ち上げ壁、58…ダイボンド材、61…蓋体連続成形体、62…外枠部、63…接続フレーム部、64…音響孔、65…内部空間、66…導電性接着剤、71…上型、72…下型、73…キャビティ、81…半導体装置、82…マイクロフォンチップ(MEMSチップ、半導体チップ)、83…貫通電極、84…はんだ、D…切断ライン

Claims (3)

- MEMSチップを含む複数の半導体チップを搭載したパッケージ本体が、リードフレームと該リードフレームの一部を埋設状態としたモールド樹脂体とからなり、前記リードフレームに、前記半導体チップの下方に配置されるステージ部と、該ステージ部と間隔を開けて配置され前記半導体チップに接続された複数の端子部と、前記ステージ部に接続状態とされ前記モールド樹脂体の表面に露出した導通フレーム部とが形成され、該導通フレーム部に前記パッケージ本体に固着された導電性材料からなる蓋体が接続された半導体装置であって、

前記複数の半導体チップは、前記MEMSチップが前記モールド樹脂体に形成された凹部内に収容されるとともに、該凹部が前記蓋体により閉塞され、MEMSチップ以外の他の半導体チップが前記モールド樹脂体内に埋設され、

前記端子部は、前記他の半導体チップに接続され前記モールド樹脂体から一部が露出する外部接続用端子部と、前記MEMSチップ及び前記他の半導体チップの両方に接続された中継端子部とを有し、該中継端子部は、前記MEMSチップに接続された部分が前記凹部内に露出され、前記他の半導体チップに接続された部分が前記モールド樹脂体内に埋設されていることを特徴とする半導体装置。 - 前記MEMSチップがマイクロフォンチップとされ、前記他の半導体チップが制御回路チップとされ、前記蓋体又はパッケージ本体のいずれかに、前記凹部に連通する音響孔が形成されていることを特徴とする請求項1記載の半導体装置。

- 請求項1又は2記載の半導体装置を製造する方法であって、

前記リードフレームを形成するリードフレーム形成工程と、

前記リードフレームのステージ部に前記他の半導体チップを搭載して前記外部接続用端子部及び前記中継端子部に接続状態とする第1の半導体チップ搭載工程と、

前記他の半導体チップを搭載した状態のリードフレームに樹脂をモールドすることにより前記凹部を有する前記モールド樹脂体を形成するモールド工程と、

前記モールド樹脂体の凹部に前記MEMSチップを収容して該凹部内の前記中継端子部に接続状態とする第2の半導体チップ搭載工程と、

前記MEMSチップの上方から前記凹部を閉塞するように前記モールド樹脂体に前記蓋体を固着する蓋体固着工程とを有することを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009029677A JP2010187182A (ja) | 2009-02-12 | 2009-02-12 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009029677A JP2010187182A (ja) | 2009-02-12 | 2009-02-12 | 半導体装置及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010187182A true JP2010187182A (ja) | 2010-08-26 |

Family

ID=42767565

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009029677A Withdrawn JP2010187182A (ja) | 2009-02-12 | 2009-02-12 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2010187182A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014216557A (ja) * | 2013-04-26 | 2014-11-17 | アオイ電子株式会社 | 半導体装置およびその製造方法 |

-

2009

- 2009-02-12 JP JP2009029677A patent/JP2010187182A/ja not_active Withdrawn

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014216557A (ja) * | 2013-04-26 | 2014-11-17 | アオイ電子株式会社 | 半導体装置およびその製造方法 |

| US9570407B2 (en) | 2013-04-26 | 2017-02-14 | Aoi Electronics Co., Ltd. | Method for manufacturing semiconductor device and semiconductor device |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20090072334A1 (en) | Semiconductor device, pre-mold package, and manufacturing method therefor | |

| JP4380748B2 (ja) | 半導体装置、及び、マイクロフォンパッケージ | |

| JP4779614B2 (ja) | 半導体装置 | |

| JP2009246116A (ja) | リードフレーム及びパッケージ本体、パッケージ、半導体装置、並びにマイクロフォンパッケージ | |

| CN101359645B (zh) | 半导体装置、预模制封装结构及其制造方法 | |

| JP2009164475A (ja) | マイクロフォンパッケージ、リードフレーム、モールド基板及びマイクロフォンパッケージの実装構造 | |

| JP2007258670A (ja) | 半導体装置 | |

| JP2009038053A (ja) | 半導体センサ装置 | |

| US8218796B2 (en) | Microphone unit and method of manufacturing the same | |

| JP2010153519A (ja) | 半導体装置用パッケージ本体及びその製造方法、半導体装置、マイクロフォンパッケージ | |

| JP4742706B2 (ja) | 半導体装置及びその製造方法 | |

| JP2009302311A (ja) | 半導体装置用パッケージ、半導体装置、並びにマイクロフォンパッケージ | |

| JP2010187182A (ja) | 半導体装置及びその製造方法 | |

| JP2010040656A (ja) | 半導体パッケージ、半導体装置及びその製造方法、並びにマイクロフォンパッケージ | |

| JP2007199049A (ja) | 半導体装置 | |

| JP4049176B2 (ja) | 半導体装置及びその製造方法 | |

| JP2009289924A (ja) | 半導体装置用パッケージ本体及びその製造方法、パッケージ、半導体装置、並びにマイクロフォンパッケージ | |

| JP2010153517A (ja) | リードフレーム連続成形体、パッケージ本体連続成形体及び半導体装置の製造方法 | |

| JP4609477B2 (ja) | 半導体装置 | |

| JP2009302350A (ja) | 半導体装置の製造方法及び半導体装置 | |

| JP2014236125A (ja) | 半導体装置の製造方法 | |

| JP2010021519A (ja) | リードフレーム用平フレーム部材、リードフレーム及びその製造方法、パッケージ本体、パッケージ、半導体装置、並びにマイクロフォンパッケージ | |

| JPH1062282A (ja) | 圧力センサ | |

| JP4609476B2 (ja) | 半導体装置の封止樹脂層及び半導体装置の封止樹脂層の形成方法 | |

| JP2010098227A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A300 | Withdrawal of application because of no request for examination |

Free format text: JAPANESE INTERMEDIATE CODE: A300 Effective date: 20120501 |