JP2010141099A - Method of manufacturing silicon epitaxial wafer - Google Patents

Method of manufacturing silicon epitaxial wafer Download PDFInfo

- Publication number

- JP2010141099A JP2010141099A JP2008315519A JP2008315519A JP2010141099A JP 2010141099 A JP2010141099 A JP 2010141099A JP 2008315519 A JP2008315519 A JP 2008315519A JP 2008315519 A JP2008315519 A JP 2008315519A JP 2010141099 A JP2010141099 A JP 2010141099A

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- silicon

- silicon single

- crystal substrate

- single crystal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 title claims abstract description 51

- 229910052710 silicon Inorganic materials 0.000 title claims abstract description 51

- 239000010703 silicon Substances 0.000 title claims abstract description 51

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 28

- 239000000758 substrate Substances 0.000 claims abstract description 100

- 238000009792 diffusion process Methods 0.000 claims abstract description 46

- 239000013078 crystal Substances 0.000 claims abstract description 35

- 238000010438 heat treatment Methods 0.000 claims description 29

- 238000005530 etching Methods 0.000 claims description 10

- 238000000034 method Methods 0.000 abstract description 27

- 238000007669 thermal treatment Methods 0.000 abstract 3

- 235000012431 wafers Nutrition 0.000 description 36

- 239000010410 layer Substances 0.000 description 25

- 238000004140 cleaning Methods 0.000 description 17

- 239000000243 solution Substances 0.000 description 13

- 239000002245 particle Substances 0.000 description 10

- 239000002344 surface layer Substances 0.000 description 10

- 238000011109 contamination Methods 0.000 description 9

- 230000000052 comparative effect Effects 0.000 description 8

- 230000007547 defect Effects 0.000 description 8

- 239000012535 impurity Substances 0.000 description 7

- 239000002019 doping agent Substances 0.000 description 6

- 238000000624 total reflection X-ray fluorescence spectroscopy Methods 0.000 description 6

- 229910052751 metal Inorganic materials 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 239000011248 coating agent Substances 0.000 description 4

- 238000000576 coating method Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 238000005259 measurement Methods 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- 239000004743 Polypropylene Substances 0.000 description 3

- 238000004458 analytical method Methods 0.000 description 3

- 229910052787 antimony Inorganic materials 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- -1 polypropylene Polymers 0.000 description 3

- 229920001155 polypropylene Polymers 0.000 description 3

- 238000005406 washing Methods 0.000 description 3

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 2

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- 238000009614 chemical analysis method Methods 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000010408 film Substances 0.000 description 2

- 229920006395 saturated elastomer Polymers 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 239000012808 vapor phase Substances 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 238000003912 environmental pollution Methods 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 229910001385 heavy metal Inorganic materials 0.000 description 1

- 238000011835 investigation Methods 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 235000012771 pancakes Nutrition 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 239000002244 precipitate Substances 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 238000002791 soaking Methods 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000005979 thermal decomposition reaction Methods 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

Images

Landscapes

- Crystals, And After-Treatments Of Crystals (AREA)

Abstract

Description

本発明は、拡散熱処理されたシリコン単結晶基板上にエピタキシャル層を成長させるシリコンエピタキシャルウェーハの製造方法に関する。 The present invention relates to a method for manufacturing a silicon epitaxial wafer in which an epitaxial layer is grown on a diffusion-heat treated silicon single crystal substrate.

半導体素子を形成するための半導体基板として、CZ(Czochralski)法やMCZ(Magnetic Czochralski)法で成長させたシリコン単結晶基板や、シリコン単結晶基板表面に不純物(ドーパント)を拡散し、その後エピタキシャル層を形成したシリコンエピタキシャルウェーハ等が従来から用いられている。 As a semiconductor substrate for forming a semiconductor device, a silicon single crystal substrate grown by a CZ (Czochralski) method or an MCZ (Magnetic Czochralski) method, or an impurity (dopant) is diffused on the surface of the silicon single crystal substrate, and then an epitaxial layer A silicon epitaxial wafer or the like on which is formed has been conventionally used.

気相エピタキシャル成長技術は、バイポーラトランジスタやMOSLSI等の集積回路の製造に用いられる単結晶薄膜技術であり、清浄な半導体単結晶基板上に基板の結晶方位に合わせて均一な単結晶薄膜を成長させたり、ドーパント濃度差が大きい接合の急峻な不純物濃度勾配を形成することができるため、きわめて重要な技術である。気相エピタキシャル成長に用いる装置としては、一般的には枚葉型、縦型(パンケーキ型)、バレル型(シリンダー型)の3種類があり、これらの成長装置の原理は共通している。 Vapor phase epitaxial growth technology is a single crystal thin film technology used in the manufacture of integrated circuits such as bipolar transistors and MOSLSIs. A uniform single crystal thin film is grown on a clean semiconductor single crystal substrate in accordance with the crystal orientation of the substrate. This is an extremely important technique because a steep impurity concentration gradient of a junction having a large dopant concentration difference can be formed. There are generally three types of apparatuses used for vapor phase epitaxial growth: a single wafer type, a vertical type (pancake type), and a barrel type (cylinder type), and the principles of these growth apparatuses are common.

一方、基板としてはシリコン単結晶基板をそのまま用いる場合と、埋め込み拡散を行ったシリコン単結晶基板を用いる場合がある。後者は、主にバイポーラデバイス用として用いられることがしばしばある。このときの拡散物質としては、N型として、Sb(アンチモン)、P(リン)、As(ヒ素)などが用いられ、P型としては、B(ボロン)が用いられるのが一般的である。また、拡散方法として、イオン注入法、塗布拡散法、熱拡散法がよく用いられる。 On the other hand, a silicon single crystal substrate may be used as it is, or a silicon single crystal substrate subjected to buried diffusion may be used. The latter is often used primarily for bipolar devices. As the diffusing material at this time, Sb (antimony), P (phosphorus), As (arsenic), or the like is used as the N type, and B (boron) is generally used as the P type. As the diffusion method, an ion implantation method, a coating diffusion method, or a thermal diffusion method is often used.

エピタキシャル成長のプロセスの一例としては、上記のような単結晶基板を成長装置内のサセプターと呼ばれる載置台の上に載置し、同基板を所定の反応温度に加熱して、Siを含んだ原料ガスの熱分解によってエピタキシャル層を成長させ、シリコンエピタキシャルウェーハを得る。 As an example of the epitaxial growth process, a single crystal substrate as described above is mounted on a mounting table called a susceptor in a growth apparatus, the substrate is heated to a predetermined reaction temperature, and a source gas containing Si is contained. An epitaxial layer is grown by thermal decomposition of to obtain a silicon epitaxial wafer.

ところで、シリコン単結晶基板上にエピタキシャル層を形成する場合、スタッキングフォルト(SF)が発生することがあるという問題が生じる。このようなSFが発生した基板を使用して、半導体素子を製造した場合、著しい歩留まりの低下が認められることが知られている。 By the way, when an epitaxial layer is formed on a silicon single crystal substrate, there arises a problem that a stacking fault (SF) may occur. It is known that when a semiconductor element is manufactured using a substrate in which such SF is generated, a significant decrease in yield is recognized.

このSFの発生原因として主なものには、基板表面のパーティクルと呼ばれるいわゆる粒子状のごみ、基板表面のダメージ、基板表面の金属不純物等があげられる。SFは上述の原因物質を核として、逆四角錐、または逆三角錐に成長することから、基板の結晶方位により見え方が異なり、(100)の基板の場合は正方形、(111)の基板の場合は三角形の形状で観察される。(111)の基板にエピタキシャル層を成長させた場合のSFを観察した図を図4に示す。 The main causes of this SF are so-called particulate dust called particles on the substrate surface, damage on the substrate surface, metal impurities on the substrate surface, and the like. SF grows into an inverted quadrangular pyramid or an inverted triangular pyramid with the above causative substance as a nucleus, so that the appearance differs depending on the crystal orientation of the substrate. In the case of the (100) substrate, the SF is square, and the (111) substrate The case is observed in a triangular shape. FIG. 4 shows a view of SF observed when an epitaxial layer is grown on the (111) substrate.

従来、これらの原因を取り除く為に基板を洗浄することがある。この洗浄方法としては、NH4OH及びH2O2を成分とするSC−1溶液による洗浄、HCl及びH2O2を成分とするSC−2溶液による洗浄を行う場合が多い。このような技術については、特許文献1に記載されている。 Conventionally, a substrate may be cleaned to remove these causes. As this cleaning method, cleaning with an SC-1 solution containing NH 4 OH and H 2 O 2 as components and cleaning with an SC-2 solution containing HCl and H 2 O 2 as components are often performed. Such a technique is described in Patent Document 1.

しかし、特にボロン等のドーパント拡散のための熱処理を行った基板にエピタキシャル層を成長させる際には、上記のような洗浄を行った場合でもSFが生じてしまうという問題があった。

また、拡散工程で使用される炉や、環境から、基板がCuに汚染されることがある。一般にCuの汚染源は、炉の部材であるチューブ本体、ボート、均熱管等のSiCに含まれるCuが汚染源になる場合が多く、基板内部に拡散したCuはデバイス不良等の原因となっていた。

However, when growing an epitaxial layer on a substrate that has been subjected to a heat treatment for dopant diffusion such as boron, there is a problem that SF occurs even when the above cleaning is performed.

In addition, the substrate may be contaminated with Cu from the furnace used in the diffusion process or the environment. In general, Cu contained in SiC such as a tube body, a boat, and a soaking tube, which are members of a furnace, is often a contamination source of Cu, and Cu diffused inside the substrate causes a device defect or the like.

本発明は、上記問題点に鑑みてなされたものであって、エピタキシャル層に発生するSFを防止するとともに、基板内部のCu濃度を効果的に低減することによって、後工程での歩留まりを向上することができるシリコンエピタキシャルウェーハの製造方法を提供することを目的とする。 The present invention has been made in view of the above-described problems, and prevents the SF generated in the epitaxial layer and effectively reduces the Cu concentration inside the substrate, thereby improving the yield in the subsequent process. An object of the present invention is to provide a method for manufacturing a silicon epitaxial wafer.

上記目的を達成するために、本発明は、少なくとも、シリコン単結晶基板に拡散熱処理を行い、該拡散熱処理を行ったシリコン単結晶基板の表面上にエピタキシャル層を成長させるシリコンエピタキシャルウェーハの製造方法であって、前記拡散熱処理を行ったシリコン単結晶基板を常温で7日間以上保持した後に、前記シリコン単結晶基板の表面をエッチングし、その後前記エピタキシャル層を成長させることを特徴とするシリコンエピタキシャルウェーハの製造方法を提供する(請求項1)。 In order to achieve the above object, the present invention provides a silicon epitaxial wafer manufacturing method in which at least a silicon single crystal substrate is subjected to a diffusion heat treatment, and an epitaxial layer is grown on the surface of the silicon single crystal substrate subjected to the diffusion heat treatment. The silicon single crystal substrate subjected to the diffusion heat treatment is held at room temperature for 7 days or more, and then the surface of the silicon single crystal substrate is etched, and then the epitaxial layer is grown. A manufacturing method is provided (claim 1).

このように、拡散熱処理後に常温で7日間以上保持することにより、拡散熱処理等の前工程で基板内部に拡散した金属不純物であるCuを、基板の表層に十分に集結させることができる。そしてこの保持後の基板表面をエッチングすることにより、表面のパーティクル等と共に、表層に集結したCuも効果的に除去することができるため、基板のCu汚染濃度を効率的に低減することができる。さらに、このようにエピタキシャル層成長前に基板のパーティクル等と共にCuも除去することができるため、エピタキシャル層成長時に生じるSFを効果的に防止することができる。

これにより、SF等の欠陥がほとんどないエピタキシャル層を有し、基板内部のCu濃度も低いシリコンエピタキシャルウェーハを製造することができるため、後工程のデバイス作製工程等での歩留まりが向上する。

Thus, by holding for 7 days or more at room temperature after the diffusion heat treatment, Cu, which is a metal impurity diffused into the substrate in the previous process such as diffusion heat treatment, can be sufficiently concentrated on the surface layer of the substrate. Then, by etching the substrate surface after the holding, Cu concentrated on the surface layer can be effectively removed together with the surface particles and the like, so that the Cu contamination concentration of the substrate can be efficiently reduced. Furthermore, since Cu can be removed together with the substrate particles and the like before the epitaxial layer growth in this way, SF generated during the epitaxial layer growth can be effectively prevented.

Thereby, a silicon epitaxial wafer having an epitaxial layer having almost no defects such as SF and having a low Cu concentration inside the substrate can be manufactured, so that the yield in a device manufacturing process or the like in the subsequent process is improved.

このとき、前記拡散熱処理を行ったシリコン単結晶基板を常温で14日間以上保持することが好ましい(請求項2)。

このように、常温で保持する期間が14日間以上であれば、基板表層での集結するCuが飽和状態に達して、後のエッチングによって、基板内部のCuをより多く除去することができる。

At this time, it is preferable to hold the silicon single crystal substrate subjected to the diffusion heat treatment at room temperature for 14 days or more.

Thus, if the period of holding at room temperature is 14 days or more, Cu that collects on the substrate surface layer reaches a saturated state, and more Cu inside the substrate can be removed by subsequent etching.

このとき、前記シリコン単結晶基板の表面のエッチングを、SC−1溶液により行うことが好ましい(請求項3)。

このようにSC−1溶液であれば、容易に表層のみをエッチングすることができ、また、基板表面への洗浄効果も高いため、より欠陥の少ないエピタキシャル層を成長させることができる。

At this time, it is preferable that the surface of the silicon single crystal substrate is etched with an SC-1 solution.

Thus, with the SC-1 solution, only the surface layer can be easily etched, and since the cleaning effect on the substrate surface is high, an epitaxial layer with fewer defects can be grown.

このとき、前記拡散熱処理を行ったシリコン単結晶基板を、洗浄した後に常温で保持することが好ましい(請求項4)。

このように、洗浄によって不純物等を除去する等して基板表面を清浄にしてから保持することにより、保持している間に基板が汚染されることを防止することができるため、より汚染の少ないエピタキシャルシリコンウェーハを製造することができる。

At this time, the silicon single crystal substrate subjected to the diffusion heat treatment is preferably held at room temperature after being washed.

In this way, the substrate surface can be prevented from being polluted while being held by cleaning the substrate surface by removing impurities or the like by washing, and therefore less contaminated. An epitaxial silicon wafer can be manufactured.

以上のように、本発明のシリコンエピタキシャルウェーハの製造方法によれば、SF等の欠陥がほとんどないエピタキシャル層を有し、基板内部のCu濃度も低いシリコンエピタキシャルウェーハを製造することができるため、後工程のデバイス作製工程等での歩留まりが向上する。 As described above, according to the method for producing a silicon epitaxial wafer of the present invention, a silicon epitaxial wafer having an epitaxial layer having almost no defects such as SF and having a low Cu concentration inside the substrate can be produced. The yield in the device manufacturing process of the process is improved.

エピタキシャル層を成長させる際に生じるSF等の欠陥や、その前工程でのCu汚染によって、デバイス作製工程での歩留まりが低下してしまうという問題があった。

本発明者はこのような問題に対して鋭意検討を行った。

There was a problem that the yield in the device manufacturing process was lowered due to defects such as SF generated when growing the epitaxial layer and Cu contamination in the previous process.

The present inventor has intensively studied such problems.

図2に、TXRF法(全反射蛍光X線法)により測定したエピタキシャル成長前の拡散熱処理を施した基板表面のCu濃度と、その基板にエピタキシャル成長させた後のSF発生マップを示す。

この結果から、Cuの基板表層の濃度分布と、エピタキシャル層成長時に発生するSFには相関関係があることを見出した。これは、拡散熱処理の際の降温時に表面付近に集まってきたCuが、洗浄を行っても十分には除去されず、エピタキシャル成長時にSFの核となるためであると考えられる。なお、図中のDLとは測定限界以下であることを示す。

FIG. 2 shows the Cu concentration on the surface of the substrate subjected to diffusion heat treatment before epitaxial growth measured by the TXRF method (total reflection fluorescent X-ray method), and the SF generation map after epitaxial growth on the substrate.

From this result, it was found that there is a correlation between the concentration distribution of the Cu substrate surface layer and the SF generated during the growth of the epitaxial layer. This is considered to be because Cu that has gathered near the surface when the temperature is lowered during diffusion heat treatment is not sufficiently removed even after cleaning, and becomes a nucleus of SF during epitaxial growth. In addition, DL in a figure shows that it is below a measurement limit.

そして、本発明者は、このSF発生の要因となる基板表面のCu濃度について検討した結果、以下のことを見出した。

図3は、ボロン拡散熱処理を行ったシリコン単結晶基板を常温で保持した場合の、基板表面のCu濃度と経過日数の関係を示すグラフである。

Cuは常温でも基板表面に集まりやすい性質があり、発明者が調査したところによると、図3に示すように、一度基板内部に拡散したCuは、7日以上経過すると表面のCu濃度が高くなるほど基板表層に集まり、14日以上経過すると表面Cu濃度は飽和状態に達する。

As a result of studying the Cu concentration on the substrate surface that causes the occurrence of SF, the present inventor has found the following.

FIG. 3 is a graph showing the relationship between the Cu concentration on the substrate surface and the elapsed days when a silicon single crystal substrate subjected to boron diffusion heat treatment is held at room temperature.

Cu has the property of being easily collected on the substrate surface even at room temperature. According to an investigation by the inventor, as shown in FIG. 3, the Cu once diffused inside the substrate increases as the surface Cu concentration increases after 7 days or more. The surface Cu concentration reaches the saturation state after 14 days or more after gathering on the substrate surface layer.

以上より、本発明者は、Cu汚染が発生しやすい拡散熱処理後に、常温で7日間以上保持して表面をエッチングすることにより基板内部のCuを効果的に除去でき、その後にエピタキシャル層を成長させることで、Cu起因のSFを防止することができることを見出して、本発明を完成させた。 As described above, the present inventor can effectively remove Cu inside the substrate by etching the surface while holding at room temperature for 7 days or more after diffusion heat treatment that is likely to cause Cu contamination, and then grow an epitaxial layer. Thus, it was found that SF caused by Cu could be prevented, and the present invention was completed.

以下、本発明のシリコンエピタキシャルウェーハの製造方法について、実施態様の一例として、図を参照しながら詳細に説明するが、本発明はこれに限定されるものではない。

図1は、本発明のシリコンエピタキシャルウェーハの製造方法の実施態様の一例を示すフロー図である。

Hereinafter, although the manufacturing method of the silicon epitaxial wafer of this invention is demonstrated in detail, referring to a figure as an example of an embodiment, this invention is not limited to this.

FIG. 1 is a flowchart showing an example of an embodiment of a method for producing a silicon epitaxial wafer of the present invention.

本発明の製造方法では、パターン付き又はパターン無しシリコン単結晶基板に拡散熱処理を行う。

この拡散熱処理は、図1A、Bに示すように、Sb、P、As等のドーパントを拡散する工程の後にB等のドーパントを拡散する工程を行うこともできるし、同時でも、順序逆でも、一方の工程のみ行うこともできる。また、拡散させる方法としては、特に限定されず、塗布拡散法やイオン注入後に熱処理を行う方法等がある。なお、本発明の拡散熱処理としては、上記のイオン注入後の熱処理や、一度基板内部に拡散したドーパントをさらに内部に拡散させる熱処理のような、拡散工程において熱処理を伴うものが含まれる。

In the manufacturing method of the present invention, diffusion heat treatment is performed on a patterned or non-patterned silicon single crystal substrate.

In this diffusion heat treatment, as shown in FIGS. 1A and 1B, a step of diffusing a dopant such as B can be performed after a step of diffusing a dopant such as Sb, P, As, etc. Only one step can be performed. Further, the diffusion method is not particularly limited, and examples thereof include a coating diffusion method and a method of performing a heat treatment after ion implantation. The diffusion heat treatment of the present invention includes a heat treatment in the diffusion process, such as the heat treatment after the ion implantation described above, or the heat treatment for further diffusing the dopant once diffused inside the substrate.

次に、図1Cに示すように、拡散熱処理を行ったシリコン単結晶基板を洗浄することが好ましい。

例えば、前工程で基板表面に形成された酸化膜をHF水溶液で除去し、その後基板表面を保護する目的でSC−1溶液により洗浄を行ったり、SC−1溶液による洗浄の後にSC−2溶液により洗浄することもできる。SC−1溶液中においては、アルカリ性を示すため、Cuを除く、Fe、Cr、Niなどの重金属やNa、Zn、Kなどの軽金属類などの汚染を受ける可能性がある。これらの汚染を防ぐため、SC−1洗浄の後にSC−2洗浄を実施することも好ましい。

このように、洗浄によって金属不純物等を除去する等して基板表面を清浄にしてから保持することにより、保持している間に基板が汚染されることを防止することができるため、より汚染の少ないエピタキシャルシリコンウェーハを製造することができる。

Next, as shown in FIG. 1C, it is preferable to clean the silicon single crystal substrate subjected to the diffusion heat treatment.

For example, the oxide film formed on the substrate surface in the previous step is removed with an HF aqueous solution, and then the substrate is cleaned with an SC-1 solution for the purpose of protecting the substrate surface. Can also be washed. In SC-1 solution, since it shows alkalinity, there is a possibility of contamination with heavy metals such as Fe, Cr and Ni, and light metals such as Na, Zn and K, excluding Cu. In order to prevent such contamination, it is also preferable to perform SC-2 cleaning after SC-1 cleaning.

In this way, the substrate surface can be prevented from being contaminated while being held by cleaning the substrate surface by removing metal impurities, etc. by washing, etc. A small number of epitaxial silicon wafers can be manufactured.

次に、図1Dに示すように、本発明の製造方法では、拡散熱処理を行ったシリコン単結晶基板を常温で7日間以上保持する。

このように、拡散熱処理後に常温で7日間以上保持することにより、拡散熱処理等の前工程で基板内部に拡散した金属不純物であるCuを、基板の表層に十分に集結させることができる。尚、図3からすると、7日ではCuが最表面まで拡散していないものもあり得るが、本発明では、後工程でエッチングにより基板表面の一部を溶解除去するので、7日の保持でも効果がある。

また、この保持する期間は、拡散熱処理を行って、基板が常温(25℃程度)に戻ってからの期間をいう。また、保持方法としては、ポリプロピレン製BOX内等の基板が清浄に保たれるような場所に保管することが好ましい。

Next, as shown in FIG. 1D, in the manufacturing method of the present invention, the silicon single crystal substrate subjected to the diffusion heat treatment is held at room temperature for 7 days or more.

Thus, by holding for 7 days or more at room temperature after the diffusion heat treatment, Cu, which is a metal impurity diffused into the substrate in the previous process such as diffusion heat treatment, can be sufficiently concentrated on the surface layer of the substrate. According to FIG. 3, Cu may not have diffused to the outermost surface on the 7th, but in the present invention, a part of the substrate surface is dissolved and removed by etching in the subsequent process. effective.

Further, this holding period refers to a period after the diffusion heat treatment is performed and the substrate returns to room temperature (about 25 ° C.). Further, as a holding method, it is preferable to store the substrate in a place such as a polypropylene BOX where the substrate is kept clean.

このとき、常温で14日間以上保持することが好ましい。

このように、常温で保持する期間が14日間以上であれば、基板表層での集結するCuが飽和状態に達して、後のエッチングによって、より多くのCuを除去することができる。

At this time, it is preferable to hold | maintain at normal temperature for 14 days or more.

Thus, if the period of holding at room temperature is 14 days or more, Cu that collects on the surface layer of the substrate reaches a saturated state, and more Cu can be removed by subsequent etching.

次に、図1Eに示すように、上記のように常温で保持した基板の表面をエッチングする。

保持後の基板表面をエッチングすることにより、表面のパーティクル等と共に、表層に集結したCuも効果的に除去することができるため、基板のCu汚染濃度を効率的に低減することができる。

Next, as shown in FIG. 1E, the surface of the substrate held at room temperature as described above is etched.

By etching the substrate surface after holding, Cu concentrated on the surface layer can be effectively removed together with the surface particles and the like, so that the Cu contamination concentration of the substrate can be efficiently reduced.

このエッチングする方法としては、特に限定されず、例えばSC−1溶液(アンモニア:過酸化水素:水=1:1〜2:5〜7)を用いたり、SC−1溶液を用いた後にSC−2溶液を用いることが好ましい。

このようにSC−1溶液であれば、容易に表層のみをエッチングすることができ、また、基板表面への洗浄効果も高いため、より欠陥の少ないエピタキシャル層を成長させることができる。また、SC−1溶液の後にSC−2溶液を用いるとより洗浄効果が高い。

The etching method is not particularly limited. For example, SC-1 solution (ammonia: hydrogen peroxide: water = 1: 1 to 2: 5-7) is used, or SC-solution is used after SC-1 solution is used. Two solutions are preferably used.

Thus, with the SC-1 solution, only the surface layer can be easily etched, and since the cleaning effect on the substrate surface is high, an epitaxial layer with fewer defects can be grown. Further, when the SC-2 solution is used after the SC-1 solution, the cleaning effect is higher.

次に、図1Fに示すように、シリコン単結晶基板の表面にエピタキシャル層を成長させる。

このようにエピタキシャル層成長前に基板のCu、パーティクル等が除去されているため、エピタキシャル層成長時に生じる基板のCu起因のSFや、その他の欠陥を効果的に防止することができる。

Next, as shown in FIG. 1F, an epitaxial layer is grown on the surface of the silicon single crystal substrate.

As described above, Cu, particles, and the like of the substrate are removed before the epitaxial layer is grown, so that it is possible to effectively prevent SF and other defects caused by Cu of the substrate that are generated during the growth of the epitaxial layer.

以上の本発明の製造方法によれば、SF等の欠陥がほとんどないエピタキシャル層を有し、基板内部のCu濃度も低いシリコンエピタキシャルウェーハを製造することができるため、後工程のデバイス作製工程等での歩留まりが向上する。 According to the above manufacturing method of the present invention, a silicon epitaxial wafer having an epitaxial layer with almost no defects such as SF and having a low Cu concentration inside the substrate can be manufactured. The yield is improved.

以下、実施例及び比較例を示して本発明をより具体的に説明するが、本発明はこれらに限定されるものではない。

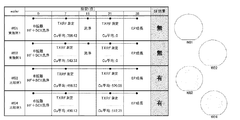

(実施例1、比較例1)

まず、4枚のパターン付きウェーハ(W01〜04)に塗布拡散法を用いてB拡散を行った。このウェーハにはB拡散前にSb及びPが前もって拡散してある。B拡散時に基板が炉からCu汚染されているのを確認した。

EXAMPLES Hereinafter, although an Example and a comparative example are shown and this invention is demonstrated more concretely, this invention is not limited to these.

(Example 1, Comparative Example 1)

First, B diffusion was performed on four patterned wafers (W01 to 04) using a coating diffusion method. In this wafer, Sb and P are diffused before B diffusion. It was confirmed that the substrate was contaminated with Cu from the furnace during B diffusion.

B拡散工程で基板表面に成長した酸化膜をHFで除去し、表面洗浄及び表面保護の為、同ウェーハにSC−1洗浄を行った。なお、HF処理とSC−1処理は同一ライン上に設けられた槽で実施した。 The oxide film grown on the substrate surface in the B diffusion step was removed with HF, and SC-1 cleaning was performed on the wafer for surface cleaning and surface protection. Note that the HF treatment and the SC-1 treatment were performed in a tank provided on the same line.

その後ポリプロピレン製BOX内で7日間保管し、表面のCu濃度を測定した。測定はTXRF法(全反射蛍光X線法)を用いて行った。Cu濃度は455×1010〜766×1010atoms/cm2であった。 Thereafter, it was stored in a polypropylene BOX for 7 days, and the Cu concentration on the surface was measured. The measurement was performed using the TXRF method (total reflection fluorescent X-ray method). The Cu concentration was 455 × 10 10 to 766 × 10 10 atoms / cm 2 .

同条件で処理した4枚のウェーハのうち2枚(W01、W02)について、保管18日目にSC−1洗浄を行った。洗浄後の21日目に再度TXRF測定を実施したところ、洗浄を実施したウェーハ(W01、W02)についてはCuを検出しなかった。洗浄を実施しなかったウェーハ(W03、W04)については、21日目に520×1010、512×1010atoms/cm2の濃度のCuを検出した。 Of the four wafers processed under the same conditions, two wafers (W01, W02) were subjected to SC-1 cleaning on the 18th day of storage. When TXRF measurement was performed again on the 21st day after cleaning, Cu was not detected in the cleaned wafers (W01, W02). For the wafers (W03, W04) that were not cleaned, Cu having a concentration of 520 × 10 10 , 512 × 10 10 atoms / cm 2 was detected on the 21st day.

これらのウェーハに、38日目に同一エピバッチでエピタキシャル成長を実施した。エピタキシャル成長にはシリンダー型リアクターを使用した。エピタキシャル成長後にSF発生の有無を確認したところ、表面にCuを検出したウェーハ(W03、W04)のみに発生したことを確認した。 These wafers were epitaxially grown in the same epibatch on the 38th day. A cylinder reactor was used for epitaxial growth. When the presence or absence of SF was confirmed after the epitaxial growth, it was confirmed that it was generated only on the wafers (W03, W04) in which Cu was detected on the surface.

上述の製造は、環境からの汚染を考慮して、クラス100のクリーンルーム内で実施し、洗浄機上部には更にクリーンユニットを設置した。ウェーハの保管はポリプロピレン製の洗浄済みBOX内に密閉保管した。

図5に実施例1、比較例1の製造過程の一覧と、製造されたシリコンピタキシャルウェーハのSFを観察した図を示す。

The above-mentioned production was carried out in a

FIG. 5 shows a list of the manufacturing processes of Example 1 and Comparative Example 1, and a diagram in which the SF of the manufactured silicon epitaxial wafer is observed.

(実施例2、比較例2)

パターン無しウェーハ2枚に塗布拡散法を用いてB拡散を行った。B拡散時に基板が炉からCu汚染されているのを確認した。

(Example 2, comparative example 2)

B diffusion was performed on two unpatterned wafers using the coating diffusion method. It was confirmed that the substrate was contaminated with Cu from the furnace during B diffusion.

同ウェーハを常温で7日間放置した。レーザー式パーティクルカウンターにてウェーハ上のパーティクルマップを測定した結果を図6に示す。図6に示すように、基板周縁部分にCuの析出物を検出した。基板表面に集結したCuはレーザー式パーティクル測定器で検出することができる。サイズとしては概ね0.12〜0.16umである。

また、化学分析法にてCuレベルを分析したところ、どちらのウェーハも約20×1010atoms/cm2検出した。なお、TXRF測定に比べてレベルが低いのは、ウェーハ全面として換算するためであり、局所的な分析はできない。今回マップで示しているように、汚染位置がウェーハのエッジの極めて近くであり、この付近の汚染濃度分析はTXRF分析に適合できなかった。

The wafer was left at room temperature for 7 days. The result of measuring the particle map on the wafer with a laser particle counter is shown in FIG. As shown in FIG. 6, Cu precipitates were detected at the periphery of the substrate. Cu collected on the substrate surface can be detected by a laser particle measuring instrument. The size is approximately 0.12 to 0.16 um.

Further, when the Cu level was analyzed by a chemical analysis method, about 20 × 10 10 atoms / cm 2 of both wafers were detected. The reason why the level is lower than that of TXRF measurement is to convert the entire wafer surface, and local analysis is not possible. As shown in the map this time, the contamination location was very close to the edge of the wafer, and the contamination concentration analysis in this vicinity could not be adapted to the TXRF analysis.

一方のウェーハをSC−1洗浄し、再び化学分析法を実施したところ、Cuレベルが0.05×1010atoms/cm2であった。

2枚のウェーハにエピタキシャル成長させたところ、洗浄しなかったウェーハについては、図6のマップのCuを検出した位置に多くのSFが発生した。洗浄したウェーハについてはSFの発生は無かった。

When one wafer was SC-1 cleaned and the chemical analysis method was performed again, the Cu level was 0.05 × 10 10 atoms / cm 2 .

When epitaxial growth was performed on two wafers, a lot of SF was generated at the position where Cu was detected in the map of FIG. There was no SF on the cleaned wafer.

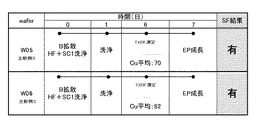

(比較例3)

実施例1と同様に拡散工程を行った後、HF処理、SC−1洗浄を順次6日以内に実施し、7日目にエピタキシャル成長を実施した。6日目に実施例1と同様に表面のCu濃度を測定したところ、Cu濃度は70×1010〜82×1010atoms/cm2であった。

この場合は、エピタキシャル層にSFが発生してしまい、また、基板内に拡散しているCuにより後工程での歩留まりも悪化した。

図7に比較例3の製造過程の一覧を示す。

(Comparative Example 3)

After performing the diffusion step in the same manner as in Example 1, HF treatment and SC-1 cleaning were sequentially performed within 6 days, and epitaxial growth was performed on the 7th day. On the 6th day, when the surface Cu concentration was measured in the same manner as in Example 1, the Cu concentration was 70 × 10 10 to 82 × 10 10 atoms / cm 2 .

In this case, SF was generated in the epitaxial layer, and the yield in the subsequent process was also deteriorated by Cu diffused in the substrate.

FIG. 7 shows a list of manufacturing processes of Comparative Example 3.

以上より、7日間以上常温で保持してエッチングを行うことにより、基板のCu濃度低減と、エピタキシャル層のSF発生防止を同時に達成できることがわかった。 From the above, it was found that by performing etching while holding at room temperature for 7 days or more, reduction of the Cu concentration of the substrate and prevention of SF generation of the epitaxial layer can be achieved simultaneously.

なお、本発明は、上記実施形態に限定されるものではない。上記実施形態は、例示であり、本発明の特許請求の範囲に記載された技術的思想と実質的に同一な構成を有し、同様な作用効果を奏するものは、いかなるものであっても本発明の技術的範囲に包含される。 The present invention is not limited to the above embodiment. The above-described embodiment is an exemplification, and the present invention has substantially the same configuration as the technical idea described in the claims of the present invention, and any device that exhibits the same function and effect is the present invention. It is included in the technical scope of the invention.

Claims (4)

前記拡散熱処理を行ったシリコン単結晶基板を常温で7日間以上保持した後に、前記シリコン単結晶基板の表面をエッチングし、その後前記エピタキシャル層を成長させることを特徴とするシリコンエピタキシャルウェーハの製造方法。 At least a method for producing a silicon epitaxial wafer in which a diffusion heat treatment is performed on a silicon single crystal substrate, and an epitaxial layer is grown on the surface of the silicon single crystal substrate subjected to the diffusion heat treatment,

A method for producing a silicon epitaxial wafer, comprising: holding a silicon single crystal substrate subjected to the diffusion heat treatment at room temperature for 7 days or more, etching the surface of the silicon single crystal substrate, and then growing the epitaxial layer.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008315519A JP5168117B2 (en) | 2008-12-11 | 2008-12-11 | Manufacturing method of silicon epitaxial wafer |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008315519A JP5168117B2 (en) | 2008-12-11 | 2008-12-11 | Manufacturing method of silicon epitaxial wafer |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010141099A true JP2010141099A (en) | 2010-06-24 |

| JP5168117B2 JP5168117B2 (en) | 2013-03-21 |

Family

ID=42350979

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008315519A Active JP5168117B2 (en) | 2008-12-11 | 2008-12-11 | Manufacturing method of silicon epitaxial wafer |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5168117B2 (en) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012144188A1 (en) | 2011-04-19 | 2012-10-26 | 株式会社ブリヂストン | Method for producing carbide for reinforcing rubber article |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5935421A (en) * | 1982-08-24 | 1984-02-27 | Toshiba Corp | Manufacture of semiconductor device |

| JPH03254125A (en) * | 1990-03-02 | 1991-11-13 | Mitsubishi Materials Corp | Method of washing semiconductor wafer |

| JPH05275416A (en) * | 1992-03-27 | 1993-10-22 | Mitsubishi Materials Corp | Cleaning solvent of silicon wafer |

-

2008

- 2008-12-11 JP JP2008315519A patent/JP5168117B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5935421A (en) * | 1982-08-24 | 1984-02-27 | Toshiba Corp | Manufacture of semiconductor device |

| JPH03254125A (en) * | 1990-03-02 | 1991-11-13 | Mitsubishi Materials Corp | Method of washing semiconductor wafer |

| JPH05275416A (en) * | 1992-03-27 | 1993-10-22 | Mitsubishi Materials Corp | Cleaning solvent of silicon wafer |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012144188A1 (en) | 2011-04-19 | 2012-10-26 | 株式会社ブリヂストン | Method for producing carbide for reinforcing rubber article |

| US9358549B2 (en) | 2011-04-19 | 2016-06-07 | Bridgestone Corporation | Method for manufacturing carbide for reinforcing rubber articles |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5168117B2 (en) | 2013-03-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100278210B1 (en) | Semiconductor surface treatment agent and treatment method | |

| JP4240403B2 (en) | Epitaxial wafer manufacturing method | |

| US20120051872A1 (en) | Integrated apparatus to assure wafer quality and manufacturability | |

| US6514886B1 (en) | Method for elimination of contaminants prior to epitaxy | |

| JPH0817163B2 (en) | Epitaxial wafer manufacturing method | |

| JP4164816B2 (en) | Epitaxial wafer manufacturing method | |

| JP5168117B2 (en) | Manufacturing method of silicon epitaxial wafer | |

| JP3298467B2 (en) | Manufacturing method of epitaxial wafer | |

| JP6376072B2 (en) | Epitaxial wafer manufacturing method | |

| EP2417241A2 (en) | Process and apparatus for removal of contaminating material from substrates | |

| JP3116487B2 (en) | Method for manufacturing semiconductor epitaxial substrate | |

| KR102585395B1 (en) | Method for manufacturing epitaxial wafers | |

| JP4573282B2 (en) | Epitaxial silicon wafer manufacturing method | |

| JPH0795546B2 (en) | Silicon surface treatment method | |

| JP3076202B2 (en) | Method of depositing polysilicon film for EG | |

| JP2004165489A (en) | Epitaxial silicon wafer, its manufacturing method and semiconductor device | |

| JP2010109141A (en) | Manufacturing method of semiconductor substrate | |

| JP3274810B2 (en) | Method for cleaning sand-blasted semiconductor wafer and semiconductor wafer cleaned by this method | |

| JP6569640B2 (en) | Box management method and epitaxial wafer manufacturing method | |

| WO2003052811A1 (en) | Silicon wafer and method for production of silicon wafer | |

| JP6575931B2 (en) | Epitaxial wafer manufacturing method | |

| JPH09298180A (en) | Silicon wafer washing method | |

| JP2019149416A (en) | Epitaxial silicon wafer manufacturing method and epitaxial silicon wafer | |

| JP4826993B2 (en) | Method for producing p-type silicon single crystal wafer | |

| JP2003197547A (en) | Method of manufacturing silicon epitaxial wafer |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110214 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111220 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121127 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121210 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5168117 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |