JP2010093658A - 信号送信装置及び信号送信方法 - Google Patents

信号送信装置及び信号送信方法 Download PDFInfo

- Publication number

- JP2010093658A JP2010093658A JP2008263243A JP2008263243A JP2010093658A JP 2010093658 A JP2010093658 A JP 2010093658A JP 2008263243 A JP2008263243 A JP 2008263243A JP 2008263243 A JP2008263243 A JP 2008263243A JP 2010093658 A JP2010093658 A JP 2010093658A

- Authority

- JP

- Japan

- Prior art keywords

- data

- reference signal

- timing reference

- bits

- bit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/222—Studio circuitry; Studio devices; Studio equipment

- H04N5/262—Studio circuits, e.g. for mixing, switching-over, change of character of image, other special effects ; Cameras specially adapted for the electronic generation of special effects

- H04N5/268—Signal distribution or switching

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N21/00—Selective content distribution, e.g. interactive television or video on demand [VOD]

- H04N21/20—Servers specifically adapted for the distribution of content, e.g. VOD servers; Operations thereof

- H04N21/23—Processing of content or additional data; Elementary server operations; Server middleware

- H04N21/236—Assembling of a multiplex stream, e.g. transport stream, by combining a video stream with other content or additional data, e.g. inserting a URL [Uniform Resource Locator] into a video stream, multiplexing software data into a video stream; Remultiplexing of multiplex streams; Insertion of stuffing bits into the multiplex stream, e.g. to obtain a constant bit-rate; Assembling of a packetised elementary stream

- H04N21/23602—Multiplexing isochronously with the video sync, e.g. according to bit-parallel or bit-serial interface formats, as SDI

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N21/00—Selective content distribution, e.g. interactive television or video on demand [VOD]

- H04N21/40—Client devices specifically adapted for the reception of or interaction with content, e.g. set-top-box [STB]; Operations thereof

- H04N21/43—Processing of content or additional data, e.g. demultiplexing additional data from a digital video stream; Elementary client operations, e.g. monitoring of home network or synchronising decoder's clock; Client middleware

- H04N21/434—Disassembling of a multiplex stream, e.g. demultiplexing audio and video streams, extraction of additional data from a video stream; Remultiplexing of multiplex streams; Extraction or processing of SI; Disassembling of packetised elementary stream

- H04N21/4342—Demultiplexing isochronously with video sync, e.g. according to bit-parallel or bit-serial interface formats, as SDI

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N7/00—Television systems

- H04N7/015—High-definition television systems

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N7/00—Television systems

- H04N7/12—Systems in which the television signal is transmitted via one channel or a plurality of parallel channels, the bandwidth of each channel being less than the bandwidth of the television signal

Abstract

【解決手段】所定の伝送規格に従ってLinkA及びBのHD−SDI信号にマッピングし、LinkAについては、各水平ラインのデータのうち、000h,000h,000h,000hで規定されるタイミング基準信号SAVを所定の値に書き換える。そして、水平ブランキング期間以外のデータに自己同期型スクランブルを掛ける。そして、SAVの直前でスクランブラ内のレジスタの値を全て0にセットしてエンコードし、誤り検出符号CRCに続く少なくとも数ビットまでのデータを出力する。一方、LinkBのRGBのビットを8B/10Bエンコーディングしたデータと多重して、10.692Gbpsのシリアル・デジタルデータを生成する。

【選択図】図11

Description

図20Aは、ベーシックストリームCH1,3,5,7を伝送する場合におけるデータ構造の例を示す。

従来、ベーシックストリームCH1,3,5,7のEAVに続くフィールド101には、(LN0,LN0,LN1,LN1)が含まれる。CH1,3,5,7のSAV内における(3FFh,3FFh,000h,000h,000h,000h,XYZ,ZYZh)のフィールド102で示される(000h,000h,000h,000h)はそのままスクランブルが掛けられる。このとき、CXYZhの下位2ビットを、CH1,3,5,7でそれぞれ、(0,0),(0,1),(1,0),(1,1)に書き換える。

ベーシックストリームCH2,4,6,8は、それぞれSAVとアクティブビデオとEAVによって構成される映像信号に変換される。ただし、この映像信号は、8B/10B変換される。

図20Aにおけるフィールド103と、図20Bにおけるフィールド104は、それぞれ、10ビット8ワードのデータに挿入される。

次に、シリアル/パラレル変換されたLinkAの各水平ラインのデータのうち、000h,000h,000h,000hで規定されるタイミング基準信号SAVを所定の値に書き換える。

次に、スクランブラによって、タイミング基準信号SAV,アクティブライン,タイミング基準信号EAV,ライン番号LN及び誤り検出符号CRCのデータのみに自己同期型スクランブルを掛ける。

次に、タイミング基準信号SAVの直前でスクランブラ内のレジスタの値を全て0にセットしてエンコードし、誤り検出符号CRCに続く少なくとも数ビットまでのデータを出力する。

次に、シリアル/パラレル変換されたLinkBの各水平ラインのデータのうち、タイミング基準信号SAV,アクティブライン,タイミング基準信号EAV,ライン番号LN及び誤り検出符号CRCのデータのみからRGBのビットを抜き出す。

次に、抜き出されたLinkBのRGBのビットを8ビット/10ビットエンコーディングする。

次に、自己同期型スクランブルを掛けられたLinkAのパラレル・デジタルデータと、8ビット/10ビットエンコーディングされたLinkBのパラレル・デジタルデータとを多重する。

そして、多重されたパラレル・デジタルデータから、所定のビットレートのシリアル・デジタルデータを生成する。

1.第1の実施の形態(スクランブル制御:SAVへのデータ書換え処理の例)

2.変形例

[伝送システムの例]

図1は、本発明を適用したテレビジョン放送局用のカメラ伝送システムの全体構成を示す図である。このカメラ伝送システムは、複数台の放送用カメラ1とCCU(カメラコントロールユニット)2とで構成されており各放送用カメラ1が光ファイバーケーブル3でCCU2に接続されている。

図2は、放送用カメラ1の回路構成のうち、本発明に関連する部分を示すブロック図である。放送用カメラ1内の撮像部及び映像信号処理部(図示略)によって生成された3840×2160/24P,25P,30P/4:4:4/12ビット信号が、マッピング部11に送られる。

図6は、S/P・スクランブル・8B/10B部12の構成を示すブロック図である。S/P・スクランブル・8B/10B部12は、各CH1〜CH8に一対一に対応した8個のブロック12−1〜12−8から成っている。

X9+X4+1

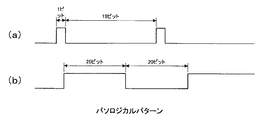

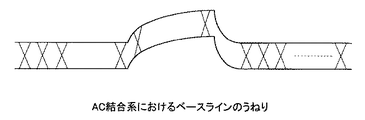

で順次割り算する。そして、割り算した結果である商を伝送することにより、統計的に伝送データのマーク率(1と0の割合)を平均1/2にする。このスクランブルは、原始多項式による信号の暗号化という意味も併せ持っている。この商をさらにX+1で割ることによって極性フリー(データとその反転データで同じ情報を持つこと)のデータにして送信する。受信側では、受信したシリアル信号にX+1を掛け、さらに上記原始多項式X9+X4+1を掛ける処理(デスクランブル)により、元のシリアル信号を再生する。

図11Aは、ベーシックストリームCH1,3,5,7を伝送する場合におけるデータ構造の例を示す。

フラットフィールドに対する安定性を向上させるために以下の処理を行う。すなわち、スクランブラ24は、スクランブルを掛ける前に、CH1,3,5,7のSAV(3FFh,3FFh,000h,000h,000h,000h,XYZh,XYZh)の(000h,000h,000h,000h)を、所定の値に書き換える。本例において、スクランブラ24は、フィールド51に含まれるライン番号(LN0,LN0,LN1,LN1)の内容を、フィールド52に含まれるSAV(000h,000h,000h,000h)の内容と書き換える処理を行う。つまり、CH1,3,5,7のSAVが多重してある同じラインのEAVに続く(LN0,LN0,LN1,LN1)に書き換えた後、スクランブルを掛ける。この処理によって、ベーシックストリームCH1,3,5,7は、それぞれSAVとアクティブビデオとEAVによって構成される映像信号に変換される。このとき、CXYZhの下位2ビットを、CH1,3,5,7でそれぞれ、(0,0),(0,1),(1,0),(1,1)に書き換える。

ベーシックストリームCH2,4,6,8は、それぞれSAVとアクティブビデオとEAVによって構成されるHD−SDIフォーマット信号に変換される。ただし、このHD−SDIフォーマット信号は、8B/10B変換される。

図11Aにおけるフィールド53と、図11Bにおけるフィールド54は、それぞれ、10ビット8ワードのデータに挿入される。

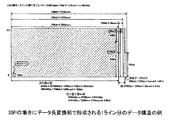

図12は30Pの場合の1ライン分のデータ構造を示す。

図13は25Pの場合の1ライン分のデータ構造を示す。

図14は24Pの場合の4ライン分のデータ構造を示す。

ただし、24Pの場合には、4ライン周期で最後のワードのビット数が128ビットになるので、4ライン分を描いている。

SMPTE435Mでは、フレームレート及びライン数が、CH1のHD−SDI信号と同じにされる。そして、S/P・スクランブル・8B/10B部12では、スクランブルと8B/10Bエンコーディングとを併用しているが、CH1にはスクランブル(SMPTE292Mで採用されているもの)を掛けている。したがって、図12〜図14に示したデータ構造は、基本的にはHD−SDI信号と同じになっている。

・斜線を付した領域:CH2,CH1,CH4,CH3,CH6,CH5,CH8,CH7の順に40ビット単位で多重された各CH1〜CH8のタイミング基準信号SAV,アクティブライン,タイミング基準信号EAV,ライン番号LN及び誤り検出符号CRCのデータの領域

・ 白地の領域:8B/10BエンコーディングされたCH1の50ビットずつの水平ブランキング期間のデータの領域

・ ドット模様を付した領域:データ量調整のための付加データの領域

10.692Gbps÷24フレーム/秒÷1125ライン/フレーム=396000ビット

10.692Gbps÷25フレーム/秒÷1125ライン/フレーム=380160ビット

10.692Gbps÷30フレーム/秒÷1125ライン/フレーム=316800ビット

(1920T+12T)×36ビット×4ch×40/36=309120ビット

(1)24Pの場合:396000ビット−309120ビット=86880ビット

(2750T−1920T−12T(SAV+EAV+LN+CRC))×20ビット×10/8=20450ビット

86880ビット>20450ビット

(2)25Pの場合:380160ビット−309120ビット=71040ビット

(2640T−1920T−12T(SAV+EAV+LN+CRC))×20ビット×10/8=17700ビット

71040ビット>17700ビット

(3)30Pの場合:316800ビット−309120ビット=7680ビット

(22T−1920T−12T(SAV+EAV+LN+CRC))×20ビット×10/8=6700ビット

7680ビット>6700ビット

24Pの場合、SMPTE435Mによる水平ブランキング期間のビット数である86880ビットの方が、20450ビットより大きい。

25Pの場合、SMPTE435Mによる水平ブランキング期間のビット数である71040ビットの方が、17700ビットより大きい。

30Pの場合、SMPTE435Mによる水平ブランキング期間のビット数である7680ビットの方が、6700ビットより大きい。

ここで、24Pの場合における20450ビットは、CH1の{水平ブランキング期間のデータ−(タイミング基準信号SAV,タイミング基準信号EAV,ライン番号LN及び誤り検出符号CRCのデータ)}のビット数である。以下、25Pの場合における17700ビット、30Pの場合における6700ビットも同様である。

このため、CH1の水平ブランキング期間のデータを多重することが可能である。

図16は、CCU2の回路構成のうち、本発明に関連する部分を示すブロック図である。CCU2には、図16に示すような回路が、各放送用カメラ1に一対一に対応して複数組設けられている。

図17は、デスクランブル・8B/10B・P/S部38の構成を示すブロック図である。デスクランブル・8B/10B・P/S部38は、各CH1〜CH8に一対一に対応した8個のブロック38−1〜38−8から成っている。

図18に示すように、放送用カメラ1では、3840×2160/24P,25P,30P/4:4:4/12ビット信号が、CH1〜CH8のHD−SDI信号にマッピングされる(ステップS1)。CH1〜CH8は、LinkAであるCH1,CH3,CH5,CH7及びLinkBであるCH2,CH4,CH6,CH8である。放送用カメラ1のマッピングは、SMPTE 435MPart1の5.4 Octa Link 1.5 GbpsClassに従って行われる。このステップS1は、図2のマッピング部11の処理である。

図19に示すように、CCU2では、ビットレート10.692Gbpsのシリアル・デジタルデータからパラレル・デジタルデータを生成する。(ステップS11)。そして、このパラレル・デジタルデータをLinkA,LinkBの各チャンネルのデータに分離する(ステップS12)。このステップS11は、図16のS/P変換・多チャンネルデータ形成部32〜データ長変換部36の処理であり、このステップS12は、図16の分離部37の処理である。

なお、以上の例ではカメラ伝送システムに本発明を適用しているが、本発明は、3840×2160/24P,25P,30P/4:4:4/12ビット信号を伝送するあらゆるシステムに適用してよい。

Claims (7)

- 所定の伝送規格に従ってマッピングされたLinkAであるCH1,CH3,CH5,CH7及びLinkBであるCH2,CH4,CH6,CH8のHD−SDIフォーマットのシリアル・デジタルビデオ信号を、それぞれシリアル/パラレル変換するシリアル/パラレル変換部と、

前記シリアル/パラレル変換部によってシリアル/パラレル変換されたLinkAの各水平ラインのデータのうち、000h,000h,000h,000hで規定されるタイミング基準信号SAVを所定の値に書き換えて、タイミング基準信号SAV,アクティブライン,タイミング基準信号EAV,ライン番号LN及び誤り検出符号CRCのデータのみに自己同期型スクランブルを掛け、タイミング基準信号SAVの直前でスクランブラ内のレジスタの値を全て0にセットしてエンコードし、誤り検出符号CRCに続く少なくとも数ビットまでのデータを出力するスクランブラと、

前記シリアル/パラレル変換部によってシリアル/パラレル変換されたLinkBの各水平ラインのデータのうち、タイミング基準信号SAV,アクティブライン,タイミング基準信号EAV,ライン番号LN及び誤り検出符号CRCのデータのみからRGBのビットを抜き出す抜き出し部と、

前記抜き出し部によって抜き出されたLinkBのRGBのビットを8ビット/10ビットエンコーディングする8ビット/10ビットエンコーダと、

前記スクランブラによって自己同期型スクランブルを掛けられたLinkAのパラレル・デジタルデータと、前記8ビット/10ビットエンコーダによって8ビット/10ビットエンコーディングされたLinkBのパラレル・デジタルデータとを多重する多重部と、

前記多重部によって多重されたパラレル・デジタルデータから、所定のビットレートのシリアル・デジタルデータを生成するシリアル・デジタルデータ生成部と

を備える信号送信装置。 - 請求項1に記載の信号送信装置において、

前記000h,000h,000h,000hで規定されるタイミング基準信号SAVを、LinkAに含まれるタイミング基準信号EAVに続く、ライン番号LN0,LN0,LN1,LN1の順に書き換える

信号送信装置。 - 請求項1に記載の信号送信装置において、

前記000h,000h,000h,000hで規定されるタイミング基準信号SAVをランダムな数値に書き換える

信号送信装置。 - 請求項1に記載の信号送信装置において、

前記000h,000h,000h,000hで規定されるタイミング基準信号SAVを、LinkAに含まれるタイミング基準信号EAVに続く、ライン番号LN0,LN0,LN1,LN1の順に書き換える

信号送信装置。 - 請求項1に記載の信号送信装置において、

前記000h,000h,000h,000hで規定されるタイミング基準信号SAVを、000h,000h及びLinkAに含まれるタイミング基準信号EAVに続く、ライン番号LN0,LN1の順に書き換える

信号送信装置。 - 請求項1に記載の信号送信装置において、

前記000h,000h,000h,000hで規定されるタイミング基準信号SAVを、LinkAに含まれるタイミング基準信号EAVに続く、ライン番号LN0,LN1及び000h,000hの順に書き換える

信号送信装置。 - 所定の伝送規格に従ってマッピングされたLinkAであるCH1,CH3,CH5,CH7及びLinkBであるCH2,CH4,CH6,CH8のHD−SDIフォーマットのシリアル・デジタルビデオ信号を、それぞれシリアル/パラレル変換する第1のステップと、

前記第1のステップでシリアル/パラレル変換したLinkAの各水平ラインのデータのうち、000h,000h,000h,000hで規定されるタイミング基準信号SAVを所定の値に書き換えて、タイミング基準信号SAV,アクティブライン,タイミング基準信号EAV,ライン番号LN及び誤り検出符号CRCのデータのみに自己同期型スクランブルを掛けるステップであって、タイミング基準信号SAVの直前でスクランブラ内のレジスタの値を全て0にセットしてエンコードし、誤り検出符号CRCに続く少なくとも数ビットまでのデータを出力する第2のステップと、

前記第1のステップでシリアル/パラレル変換したLinkBの各水平ラインのデータのうち、タイミング基準信号SAV,アクティブライン,タイミング基準信号EAV,ライン番号LN及び誤り検出符号CRCのデータのみからRGBのビットを抜き出す第3のステップと、

前記第3のステップで抜き出したLinkBのRGBのビットを8ビット/10ビットエンコーディングする第4のステップと、

前記第2のステップで自己同期型スクランブルを掛けたLinkAのパラレル・デジタルデータと、前記第4のステップで8ビット/10ビットエンコーディングしたLinkBのパラレル・デジタルデータとを多重する第5のステップと、

前記第5のステップで多重したパラレル・デジタルデータから、所定のビットレートのシリアル・デジタルデータを生成する第7のステップと、を有する

信号送信方法。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008263243A JP4702425B2 (ja) | 2008-10-09 | 2008-10-09 | 信号送信装置及び信号送信方法 |

| AT09252322T ATE493843T1 (de) | 2008-10-09 | 2009-09-30 | Signalübertragungsvorrichtung und signalübertragungsverfahren |

| BRPI0903985-6A BRPI0903985A2 (pt) | 2008-10-09 | 2009-09-30 | aparelho e método de transmissão de sinal |

| DE200960000497 DE602009000497D1 (de) | 2008-10-09 | 2009-09-30 | Signalübertragungsvorrichtung und Signalübertragungsverfahren |

| EP20090252322 EP2175637B1 (en) | 2008-10-09 | 2009-09-30 | Signal transmission apparatus and signal transmission method |

| US12/574,743 US8396215B2 (en) | 2008-10-09 | 2009-10-07 | Signal transmission apparatus and signal transmission method |

| CN200910179402A CN101719807A (zh) | 2008-10-09 | 2009-10-09 | 信号发送装置和信号发送方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008263243A JP4702425B2 (ja) | 2008-10-09 | 2008-10-09 | 信号送信装置及び信号送信方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010093658A true JP2010093658A (ja) | 2010-04-22 |

| JP4702425B2 JP4702425B2 (ja) | 2011-06-15 |

Family

ID=41441502

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008263243A Active JP4702425B2 (ja) | 2008-10-09 | 2008-10-09 | 信号送信装置及び信号送信方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US8396215B2 (ja) |

| EP (1) | EP2175637B1 (ja) |

| JP (1) | JP4702425B2 (ja) |

| CN (1) | CN101719807A (ja) |

| AT (1) | ATE493843T1 (ja) |

| BR (1) | BRPI0903985A2 (ja) |

| DE (1) | DE602009000497D1 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012244419A (ja) * | 2011-05-19 | 2012-12-10 | Sony Corp | 信号送信装置、信号送信方法、信号受信装置、信号受信方法及び信号伝送システム |

| US8903000B2 (en) | 2010-10-12 | 2014-12-02 | Panasonic Corporation | Transmission circuit, reception circuit, transmission method, reception method, communication system and communication method therefor |

| US8913196B2 (en) | 2011-09-22 | 2014-12-16 | Nec Display Solutions, Ltd. | Video processing device and video processing method including deserializer |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102065208B (zh) * | 2010-12-08 | 2013-03-13 | 南开大学 | 一种数字音视频信号串行解串器的实现方法 |

| JP2012253689A (ja) * | 2011-06-06 | 2012-12-20 | Sony Corp | 信号送信装置、信号送信方法、信号受信装置、信号受信方法及び信号伝送システム |

| CN103402068B (zh) * | 2013-08-09 | 2016-08-17 | 西安电子科技大学 | 非压缩式视频播放系统及播放方法 |

| CN104699219B (zh) * | 2013-12-10 | 2020-06-23 | 联想(北京)有限公司 | 一种电子设备及信息处理方法 |

| JP6220258B2 (ja) * | 2013-12-18 | 2017-10-25 | 日本放送協会 | 映像データの伝送装置及び伝送方法 |

| US20160112723A1 (en) * | 2014-10-17 | 2016-04-21 | Ross Video Limited | Transfer of video and related data over serial data interface (sdi) links |

| US9967476B2 (en) | 2014-10-17 | 2018-05-08 | Ross Video Limited | Parallel video effects, mix trees, and related methods |

| CN105680871B (zh) * | 2016-04-07 | 2018-09-28 | 武汉芯泰科技有限公司 | 用于数据串行传输的并串、串并转换装置 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008028651A (ja) * | 2006-07-20 | 2008-02-07 | Sony Corp | 信号処理装置及び信号処理方法 |

| JP2008042408A (ja) * | 2006-08-03 | 2008-02-21 | Sony Corp | 信号処理装置及び信号処理方法 |

| JP2008099189A (ja) * | 2006-10-16 | 2008-04-24 | Sony Corp | 信号処理装置及び信号処理方法 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4645638B2 (ja) * | 2007-11-22 | 2011-03-09 | ソニー株式会社 | 信号送信装置、信号送信方法、信号受信装置及び信号受信方法 |

-

2008

- 2008-10-09 JP JP2008263243A patent/JP4702425B2/ja active Active

-

2009

- 2009-09-30 EP EP20090252322 patent/EP2175637B1/en active Active

- 2009-09-30 AT AT09252322T patent/ATE493843T1/de not_active IP Right Cessation

- 2009-09-30 DE DE200960000497 patent/DE602009000497D1/de active Active

- 2009-09-30 BR BRPI0903985-6A patent/BRPI0903985A2/pt not_active IP Right Cessation

- 2009-10-07 US US12/574,743 patent/US8396215B2/en active Active

- 2009-10-09 CN CN200910179402A patent/CN101719807A/zh active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008028651A (ja) * | 2006-07-20 | 2008-02-07 | Sony Corp | 信号処理装置及び信号処理方法 |

| JP2008042408A (ja) * | 2006-08-03 | 2008-02-21 | Sony Corp | 信号処理装置及び信号処理方法 |

| JP2008099189A (ja) * | 2006-10-16 | 2008-04-24 | Sony Corp | 信号処理装置及び信号処理方法 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8903000B2 (en) | 2010-10-12 | 2014-12-02 | Panasonic Corporation | Transmission circuit, reception circuit, transmission method, reception method, communication system and communication method therefor |

| JP2012244419A (ja) * | 2011-05-19 | 2012-12-10 | Sony Corp | 信号送信装置、信号送信方法、信号受信装置、信号受信方法及び信号伝送システム |

| US8913196B2 (en) | 2011-09-22 | 2014-12-16 | Nec Display Solutions, Ltd. | Video processing device and video processing method including deserializer |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2175637B1 (en) | 2010-12-29 |

| ATE493843T1 (de) | 2011-01-15 |

| CN101719807A (zh) | 2010-06-02 |

| JP4702425B2 (ja) | 2011-06-15 |

| EP2175637A1 (en) | 2010-04-14 |

| US8396215B2 (en) | 2013-03-12 |

| DE602009000497D1 (de) | 2011-02-10 |

| US20100091989A1 (en) | 2010-04-15 |

| BRPI0903985A2 (pt) | 2011-02-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4702425B2 (ja) | 信号送信装置及び信号送信方法 | |

| JP4645638B2 (ja) | 信号送信装置、信号送信方法、信号受信装置及び信号受信方法 | |

| JP4557016B2 (ja) | 信号送信装置 | |

| JP4506852B2 (ja) | 信号入力装置及び信号入力方法 | |

| JP4165587B2 (ja) | 信号処理装置及び信号処理方法 | |

| JP4692576B2 (ja) | 信号送信装置及び信号送信方法 | |

| US8854540B2 (en) | Signal transmission apparatus, signal transmission method, signal reception apparatus, signal reception method, and signal transmission system | |

| JP6221606B2 (ja) | 信号処理装置、信号処理方法、プログラム、及び、信号伝送システム | |

| US8982959B2 (en) | Signal transmission apparatus, signal transmission method, signal reception apparatus, signal reception method, and signal transmission system | |

| US9071375B2 (en) | Signal transmitting apparatus, signal transmitting method, signal receiving apparatus, signal receiving method, and signal transmission system | |

| US8902993B2 (en) | Signal transmission apparatus and signal transmission method | |

| US11044439B2 (en) | Signal processing apparatus, signal processing method, program, and signal transmission system | |

| JP4910621B2 (ja) | 信号処理装置及び信号処理方法 | |

| US20070194954A1 (en) | Apparatus for and method of processing data | |

| JP2007274533A (ja) | シリアル伝送用の送信装置,スクランブル処理方法,受信装置及びシステム | |

| JP2014168152A (ja) | 信号送信装置、信号受信装置及び信号伝送システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100629 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100820 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110208 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110221 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4702425 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |