[第1の実施の形態]

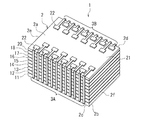

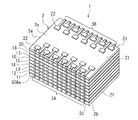

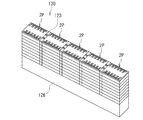

以下、本発明の実施の形態について図面を参照して詳細に説明する。始めに、図1および図2を参照して、本発明の第1の実施の形態に係る積層チップパッケージの構成について説明する。図1は、本実施の形態に係る積層チップパッケージの斜視図である。図1に示したように、本実施の形態に係る積層チップパッケージ1は、直方体形状の本体2を備えている。本体2は、上面2a、下面2b、互いに反対側を向いた第1の側面2cおよび第2の側面2d、ならびに互いに反対側を向いた第3の側面2eおよび第4の側面2fを有している。

積層チップパッケージ1は、更に、本体2の少なくとも1つの側面に配置された配線を備えている。図1に示した例では、積層チップパッケージ1は、本体2の第1の側面2cに配置された第1の配線3Aと、本体2の第2の側面2dに配置された第2の配線3Bとを備えている。以下、任意の配線に関しては符号3を付して表す。図2は、図1に示した積層チップパッケージ1において、第1の配線3Aを破線で示し、本体2の第1の側面2cを表したものである。

本体2は、積層された複数の階層部分を含んでいる。図1および図2には、一例として、本体2が、下から順に配置された8つの階層部分11,12,13,14,15,16,17,18を含んでいる例を示している。しかし、本体2に含まれる階層部分の数は8つに限らず、複数であればよい。以下の説明では、任意の階層部分に関しては、符号10を付して表す。

本体2は、更に、最も上に配置された階層部分18の上に積層された端子層20を含んでいる。上下に隣接する2つの階層部分の間、および階層部分18と端子層20の間は、それぞれ、接着剤によって接合されている。階層部分11〜18と端子層20は、いずれも、上面と、下面と、4つの側面とを有している。端子層20は、上面と下面を有する端子層本体21と、この端子層本体21の上面に配置された複数のパッド状端子22とを含んでいる。複数のパッド状端子22は、積層チップパッケージ1における外部接続端子として機能する。複数のパッド状端子22のうちのいくつかは、本体2の側面2cに配置された端面を有し、この端面に第1の配線3Aが接続されている。複数のパッド状端子22のうちの他のいくつかは、本体2の側面2dに配置された端面を有し、この端面に第2の配線3Bが接続されている。

複数の階層部分10は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含んでいる。図2には、階層部分17が第2の種類の階層部分で、他の階層部分11〜16,18が第1の種類の階層部分である例を示している。第1の種類の階層部分と第2の種類の階層部分の違いは、後で詳しく説明する。

図3は、図1に示した積層チップパッケージ1に含まれる一対の階層部分を分解して示す斜視図である。図3に示したように、階層部分11,12は、それぞれ半導体チップ30を含んでいる。半導体チップ30は、デバイスが形成された第1の面30aと、その反対側の第2の面30bと、互いに反対側を向いた第1の側面30cおよび第2の側面30d、ならびに互いに反対側を向いた第3の側面30eおよび第4の側面30fを有している。側面30c,30d,30e,30fは、それぞれ、本体2の側面2c,2d,2e,2fに向いている。階層部分11,12は、それぞれに含まれる半導体チップ30の第1の面30a同士が対向するように配置されている。図1および図2に示した積層チップパッケージ1は、半導体チップ30の第1の面30a同士が対向するように配置された対の階層部分10を、4対含んでいる。

階層部分11,12は、それぞれ、更に、半導体チップ30の4つの側面のうちの少なくとも1つの側面を覆う絶縁部31と、半導体チップ30に接続された複数の電極32とを含んでいる。絶縁部31は、配線が配置された本体2の少なくとも1つの側面に配置された少なくとも1つの端面31aを有している。図3に示した例では、絶縁部31は、半導体チップ30の4つの側面の全てを覆い、絶縁部31は、本体2の4つの側面に配置された4つの端面31aを有している。また、この例では、絶縁部31は、半導体チップ30の第1の面30aも覆っている。

また、図3に示した例では、複数の電極32は、複数の第1の電極32Aと、複数の第2の電極32Bとを含んでいる。複数の第1の電極32Aの各々は、本体2の第1の側面2cに配置され且つ絶縁部31によって囲まれた端面32Aaを有している。複数の第2の電極32Bの各々は、本体2の第2の側面2dに配置され且つ絶縁部31によって囲まれた端面32Baを有している。本体2の第1の側面2cに配置された第1の配線3Aは、複数の階層部分10における複数の第1の電極32Aの端面32Aaに接続されている。本体2の第2の側面2dに配置された第2の配線3Bは、複数の階層部分10における複数の第2の電極32Bの端面32Baに接続されている。以下、任意の電極に関しては符号32を付して表し、任意の電極32の端面に関しては符号32aを付して表す。

階層部分13,14、階層部分15,16の各対も、図3に示した階層部分11,12の対と同様の構成である。階層部分18は、図3に示した階層部分12と同様の構成である。第2の種類の階層部分である階層部分17は、半導体チップ30に接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有する電極を含んでいない。従って、図2に示したように、階層部分17の側面には、電極の端面は存在しない。階層部分17のその他の構成は、図3に示した階層部分11と同様である。第1の種類の階層部分である階層部分11〜16,18における半導体チップ30は正常に動作するものであり、第2の種類の階層部分である階層部分17における半導体チップ30は正常に動作しないものである。以下、正常に動作する半導体チップ30を良品の半導体チップ30と言い、正常に動作しない半導体チップ30を不良の半導体チップ30と言う。なお、第2の種類の階層部分10は、半導体チップ30に接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有するような形態の電極ではなければ、他の形態の電極や配線を含んでいてもよい。例えば、第2の種類の階層部分10は、半導体チップ30には接続されているが、配線3が配置された本体2の少なくとも1つの側面に配置される端面を有していない電極や、半導体チップ30の端子同士を接続する配線を含んでいてもよい。

半導体チップ30は、フラッシュメモリ、DRAM、SRAM、MRAM、PROM、FeRAM等のメモリを構成するメモリチップであってもよい。この場合には、複数の半導体チップ30を含む積層チップパッケージ1によって、大容量のメモリを実現することができる。また、本実施の形態に係る積層チップパッケージ1によれば、積層チップパッケージ1に含まれる半導体チップ30の数を変えることにより、64GB(ギガバイト)、128GB、256GB等の種々の容量のメモリを容易に実現することができる。

また、積層チップパッケージ1は、互いに異なる種類のメモリを構成するメモリチップとしての複数の半導体チップ30を含んでいてもよい。また、積層チップパッケージ1は、メモリチップとしての半導体チップ30と、メモリチップを制御するコントローラとしての半導体チップ30とを含んでいてもよい。

半導体チップ30が複数のメモリセルを有する場合、半導体チップ30が1つ以上の欠陥のあるメモリセルを含んでいても、冗長技術によって正常に動作させることができる場合には、その半導体チップ30は、良品の半導体チップである。

半導体チップ30は、メモリチップに限らず、CPU、センサ、センサの駆動回路等の他のデバイスを実現するものであってもよい。本実施の形態に係る積層チップパッケージ1は、特にSiPを実現するのに適している。

次に、本実施の形態に係る積層チップパッケージ1の製造方法について説明する。本実施の形態に係る積層チップパッケージ1の製造方法は、積層チップパッケージ1の複数の階層部分10にそれぞれ対応する複数の基礎構造物であって、各々が対応する階層部分10を複数含み、後にそれら対応する階層部分10のうちの隣接するもの同士の境界位置で切断される複数の基礎構造物を作製する工程と、複数の基礎構造物を用いて本体2を作製すると共に、本体2に対して配線3A,3Bを形成して、積層チップパッケージ1を完成させる工程とを備えている。

積層チップパッケージ1を完成させる工程は、複数の基礎構造物を、積層チップパッケージ1の複数の階層部分10の積層の順序に対応させて積層して、積層基礎構造物を作製する工程と、積層基礎構造物を切断することによって、複数の階層部分10の積層方向と直交する一方向に配列され、それぞれ後に本体2となる複数の本体予定部を含む本体集合体を作製する工程と、本体集合体における各本体予定部に対してそれぞれ配線3A,3Bを形成する工程と、配線3A,3Bの形成後、複数の本体予定部が互いに分離されてそれぞれ本体2となることによって複数の積層チップパッケージ1が形成されるように、本体集合体を切断する工程とを含んでいる。複数の基礎構造物の各々は、同種の階層部分10を複数含んでいてもよい。

以下、図4ないし図23を参照して、本実施の形態に係る積層チップパッケージ1の製造方法における複数の基礎構造物を作製する工程について詳しく説明する。複数の基礎構造物を作製する工程では、まず、積層チップパッケージ1の複数の階層部分10にそれぞれ対応する複数の基礎構造物前ウェハを作製する。

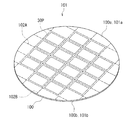

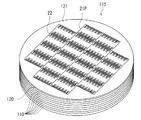

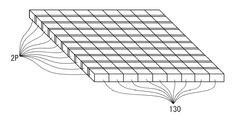

図4は、1つの基礎構造物前ウェハを作製する工程を示している。この工程では、互いに反対側を向いた第1の面100aおよび第2の面100bを有する1つの半導体ウェハ100における第1の面100aに処理、例えばウェハプロセスを施すことによって、それぞれデバイスを含み、後に複数の半導体チップ30となる複数の半導体チップ予定部30Pが配列された基礎構造物前ウェハ101を作製する。基礎構造物前ウェハ101における複数の半導体チップ予定部30Pは、後に同種の複数の半導体チップ30となるものであってもよい。基礎構造物前ウェハ101は、半導体ウェハ100の第1の面100aに対応する第1の面101aと、半導体ウェハ100の第2の面100bに対応する第2の面101bとを有している。基礎構造物前ウェハ101において、複数の半導体チップ予定部30Pは一列に配列されていてもよいし、縦方向と横方向にそれぞれ複数個並ぶように、複数列に配列されていてもよい。以下の説明では、基礎構造物前ウェハ101において、複数の半導体チップ予定部30Pは、縦方向と横方向にそれぞれ複数個並ぶように、複数列に配列されているものとする。

半導体ウェハ100としては、例えばシリコンウェハが用いられる。ウェハプロセスとは、ウェハを加工して、複数のチップに分割される前の複数のデバイスを作製するプロセスである。基礎構造物前ウェハ101において、第1の面101aは、デバイスが形成されているデバイス形成面である。複数の半導体チップ予定部30Pの各々は、基礎構造物前ウェハ101の第1の面101aに配置された複数のパッド状の端子34を有している。

図9は、基礎構造物前ウェハ101を示す斜視図である。図9に示したように、基礎構造物前ウェハ101には、縦方向に隣接する2つの半導体チップ予定部30Pの境界を通るように横方向に延びる複数のスクライブライン102Aと、横方向に隣接する2つの半導体チップ予定部30Pの境界を通るように縦方向に延びる複数のスクライブライン102Bとが形成されている。なお、図9は、理解を容易にするために、半導体ウェハ100に比べて半導体チップ予定部30Pを大きく描いている。例えば、半導体ウェハ100が12インチウェハで、半導体チップ予定部30Pの上面の一辺の長さが8〜10mmとすると、1枚の半導体ウェハ100を用いて、700〜900個の半導体チップ予定部30Pを形成することが可能である。

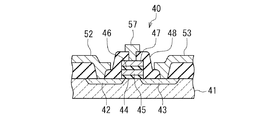

図10は、図9に示した基礎構造物前ウェハ101における半導体チップ予定部30Pの内部の構造の一例を示す断面図である。ここでは、半導体チップ予定部30Pに、デバイスとして、フラッシュメモリにおける複数のメモリセルが形成されている例を示す。図10は、半導体チップ予定部30Pに形成されたデバイスとしての複数のメモリセルのうちの1つを示している。このメモリセル40は、半導体ウェハ100よりなるP型シリコン基板41の表面(半導体ウェハ100の第1の面100a)の近傍に形成されたソース42およびドレイン43を備えている。ソース42およびドレイン43は、共にN型の領域である。ソース42とドレイン43は、これらの間にP型シリコン基板41の一部よりなるチャネルが形成されるように、所定の間隔を開けて配置されている。メモリセル40は、更に、ソース42とドレイン43の間において基板41の表面上に順に積層された絶縁膜44、浮遊ゲート45、絶縁膜46および制御ゲート47を備えている。メモリセル40は、更に、ソース42、ドレイン43、絶縁膜44、浮遊ゲート45、絶縁膜46および制御ゲート47を覆う絶縁層48を備えている。この絶縁層48には、ソース42、ドレイン43、制御ゲート47のそれぞれの上で開口するコンタクトホールが形成されている。メモリセル40は、それぞれ、ソース42、ドレイン43、制御ゲート47の上方の位置で絶縁層48上に形成されたソース電極52、ドレイン電極53、制御ゲート電極57を備えている。ソース電極52、ドレイン電極53、制御ゲート電極57は、それぞれ、対応するコンタクトホールを通して、ソース42、ドレイン43、制御ゲート47に接続されている。

積層チップパッケージ1の複数の階層部分10にそれぞれ対応する複数の基礎構造物前ウェハ101は、いずれも、図4を参照して説明した工程によって作製される。

次に、複数の基礎構造物前ウェハ101の各々に対してウェハソートテストを行って、各基礎構造物前ウェハ101に含まれる複数の半導体チップ予定部30Pについて、正常に動作する半導体チップ予定部30Pと正常に動作しない半導体チップ予定部30Pとを判別する。ウェハソートテストでは、各半導体チップ予定部30Pの複数の端子34に試験装置のプローブを接触させて、試験装置によって、半導体チップ予定部30Pが正常に動作するか否かをテストする。

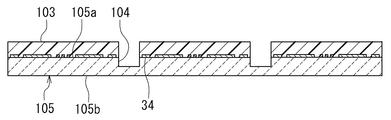

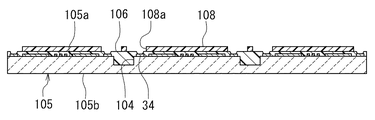

図5は、次の工程を示している。この工程では、まず、基礎構造物前ウェハ101の第1の面101aの全体を覆うように、フォトレジスト等よりなる保護膜103を形成する。次に、基礎構造物前ウェハ101に対して、少なくとも1つの半導体チップ予定部30Pに隣接するように延び、且つ基礎構造物前ウェハ101の第1の面101aにおいて開口する1以上の溝104を形成する。ここでは、図5に示したように、複数の溝104を形成するものとする。隣接する2つの半導体チップ予定部30Pの境界の位置では、隣接する2つの半導体チップ予定部30Pの境界を通るように溝104が形成される。このようにして、複数の溝104が形成された後の基礎構造物前ウェハ101よりなる研磨前基礎構造物本体105が作製される。研磨前基礎構造物本体105は、複数の半導体チップ予定部30Pを含んでいる。また、研磨前基礎構造物本体105は、半導体ウェハ100の第1の面100aおよび基礎構造物前ウェハ101の第1の面101aに対応する第1の面105aと、半導体ウェハ100の第2の面100bおよび基礎構造物前ウェハ101の第2の面101bに対応する第2の面105bと、第1の面105aにおいて開口する複数の溝104とを有している。研磨前基礎構造物本体105において、第1の面105aは、デバイスが形成されているデバイス形成面である。

複数の溝104は、図9に示したスクライブライン102A,102Bに沿って形成される。また、溝104は、その底部が基礎構造物前ウェハ101の第2の面101bに達しないように形成される。溝104の幅は、例えば10〜150μmの範囲内である。溝104の深さは、例えば30〜150μmの範囲内である。溝104は、例えば、ダイシングソーによって形成してもよいし、反応性イオンエッチング等のエッチングによって形成してもよい。

図11は、図5に示した工程で作製される研磨前基礎構造物本体105の一部を示している。本実施の形態では、複数の溝104は、複数の第1の溝104Aと複数の第2の溝104Bとを含んでいる。複数の第1の溝104Aと複数の第2の溝104Bは、互いに直交する方向に延びている。なお、図11には、1つの第1の溝104Aと1つの第2の溝104Bのみを示している。第1の溝104Aは、図9に示したスクライブライン102Aに沿って形成され、第2の溝104Bは、図9に示したスクライブライン102Bに沿って形成されている。

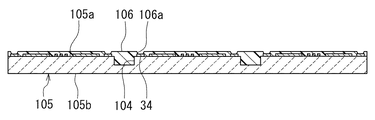

図6は、図5に示した工程に続く工程を示している。この工程では、まず、研磨前基礎構造物本体105の複数の溝104を埋め、且つ複数の端子34を覆うように、絶縁層106を形成する。この絶縁層106は、後に絶縁部31の一部となるものである。次に、絶縁層106に、複数の端子34を露出させるための複数の開口部106aを形成する。

絶縁層106は、エポキシ樹脂、ポリイミド樹脂等の樹脂によって形成されてもよい。また、絶縁層106は、感光剤を含んだポリイミド樹脂等の感光性を有する材料によって形成されてもよい。絶縁層106が感光性を有する材料によって形成されている場合には、フォトリソグラフィによって絶縁層106に開口部106aを形成することができる。絶縁層106が感光性を有しない材料によって形成されている場合には、絶縁層106を選択的にエッチングすることによって、絶縁層106に開口部106aを形成することができる。

また、絶縁層106は、複数の溝104を埋める第1層と、この第1層および複数の端子34を覆う第2層とを含んでいてもよい。この場合には、開口部106aは、第2層に形成される。第1層と第2層は、共に、エポキシ樹脂、ポリイミド樹脂等の樹脂によって形成されてもよい。また、第2層は、感光剤を含んだポリイミド樹脂等の感光性を有する材料によって形成されてもよい。第2層が感光性を有する材料によって形成されている場合には、フォトリソグラフィによって第2層に開口部106aを形成することができる。第2層が感光性を有しない材料によって形成されている場合には、第2層を選択的にエッチングすることによって、第2層に開口部106aを形成することができる。

また、絶縁層106は、熱膨張係数の小さな樹脂によって形成することが好ましい。熱膨張係数の小さな樹脂によって絶縁層106を形成することにより、後にダイシングソーによって絶縁層106を切断する場合に、絶縁層106の切断が容易になる。

また、絶縁層106は、透明であることが好ましい。絶縁層106が透明であることにより、後に絶縁層106の上に形成されるアライメントマークを、絶縁層106を通して容易に認識することが可能になる。

図7は、図6に示した工程に続く工程を示している。この工程では、まず、複数の半導体チップ予定部30Pを覆うように、絶縁層106の上にフォトレジスト層を形成する。このフォトレジスト層は、複数の電極32を形成するために用いられるものである。また、フォトレジスト層は、全ての半導体チップ予定部30Pに対応する複数の部分を含んでいる。フォトレジスト層において、1つの半導体チップ予定部30Pに対応する部分とは、1つの半導体チップ予定部30Pとそれに接続される電極32が配置される領域とを覆う部分である。次に、フォトリソグラフィによりフォトレジスト層をパターニングすることによって、後に複数の電極32が収容される複数の溝部108aを有するフレーム108を形成する。フレーム108において、正常に動作しない半導体チップ予定部30Pに対応する部分には、溝部108aは形成されない。なお、フレーム108を形成する工程については、後で詳しく説明する。

図8は、図7に示した工程に続く工程を示している。この工程では、例えばめっき法によって、フレーム108の複数の溝部108a内に複数の電極32を形成する。複数の電極32は、各電極32の一部が絶縁層106の上に配置されるように形成される。各電極32は、開口部106aを通して端子34に接続される。図12は、図8に示した工程で作製される構造物の一部を示している。

電極32は、Cu等の導電性材料によって形成される。また、電極32をめっき法によって形成する場合には、フォトレジスト層を形成する前に、絶縁層106の上に、めっき用のシード層を形成する。次に、シード層の上に、フォトレジスト層を形成し、フォトリソグラフィによりフォトレジスト層をパターニングすることによってフレーム108を形成する。フォトレジスト層の厚みは、例えば10〜20μmの範囲内である。次に、めっき法によって、フレーム108の溝部内であってシード層の上に、電極32の一部となるめっき層を形成する。めっき層の厚みは、例えば5〜15μmの範囲内である。次に、フレーム108を除去し、更に、シード層のうち、めっき層の下に存在する部分以外の部分をエッチングによって除去する。これにより、めっき層およびその下に残ったシード層によって電極32が形成される。

図12に示したように、複数の電極32を形成する工程では、複数の電極32の形成と同時に、絶縁層106の上に複数のアライメントマーク107を形成する。アライメントマーク107は、溝104の上方の位置に配置される。アライメントマーク107の材料および形成方法は、電極32と同様である。

このようにして、図8および図12に示す研磨前基礎構造物109が作製される。研磨前基礎構造物109は、研磨前基礎構造物本体105と、研磨前基礎構造物本体105の複数の溝104を埋め、後に絶縁部31の一部となる絶縁層106と、一部が絶縁層106の上に配置された複数の電極32と、絶縁層106の上に配置された複数のアライメントマーク107とを備えている。また、研磨前基礎構造物109は、半導体ウェハ100の第1の面100aおよび基礎構造物前ウェハ101の第1の面101aに対応する第1の面109aと、半導体ウェハ100の第2の面100bおよび基礎構造物前ウェハ101の第2の面101bに対応する第2の面109bとを有している。

積層チップパッケージ1の複数の階層部分10にそれぞれ対応する複数の研磨前基礎構造物109は、いずれも、図5ないし図8を参照して説明した工程によって作製される。

ここで、図13ないし図18を参照して、フレーム108を形成する工程と複数の電極32を形成する工程について詳しく説明する。図13は、積層チップパッケージ1の複数の階層部分10にそれぞれ対応する複数の基礎構造物前ウェハ101を示している。前述のように、各基礎構造物前ウェハ101に含まれる複数の半導体チップ予定部30Pについては、ウェハソートテストによって、正常に動作する半導体チップ予定部30Pと正常に動作しない半導体チップ予定部30Pとが判別されている。図13において、記号“X”を付した四角は、正常に動作しない半導体チップ予定部30Pを表し、他の四角は、正常に動作する半導体チップ予定部30Pを表している。ウェハソートテストによって、基礎構造物前ウェハ101毎に、正常に動作する半導体チップ予定部30Pと正常に動作しない半導体チップ予定部30Pの位置情報が得られる。この位置情報は、後に、フレーム108を形成するための露光工程において使用される。

図14は、本実施の形態に係る積層チップパッケージ1の製造方法において使用される露光装置の構成の一例を示す説明図である。図14に示した露光装置は、ステップ式投影露光装置、いわゆるステッパーである。この露光装置は、マスク201を保持するマスクステージ210と、マスク201を移動または交換するためにマスクステージ210を駆動する駆動装置211と、ウェハ202を保持するウェハステージ220と、このウェハステージ220を移動させる移動機構221と、移動機構221を駆動する駆動装置222と、縮小投影光学系203と、照明装置204と、ウェハ202の位置を検出する検出装置240と、照明装置204、駆動装置211,222および検出装置240を制御する制御装置250とを備えている。

マスクステージ210は、ウェハステージ220の上方に配置されている。縮小投影光学系203は、マスクステージ210とウェハステージ220との間に配置されている。照明装置204は、マスクステージ210の上方に配置され、マスク201に対して、露光用の光を照射する。

移動機構221は、ウェハステージ220を、図14に示したX,Y,Zの各方向に移動可能であると共に、XY平面に対するウェハステージ220の傾斜角度を変えることができるようになっている。なお、X方向とY方向は、いずれも縮小投影光学系203の光軸方向に対して直交する方向であって、互いに直交する方向である。Z方向は、縮小投影光学系203の光軸方向に平行な方向である。検出装置240は、ウェハ202の表面の位置およびXY平面に対するウェハ202の表面の傾斜角度を検出する。

制御装置250は、マイクロプロセッサユニット(MPU)と、リード・オンリ・メモリ(ROM)と、ランダム・アクセス・メモリ(RAM)とを有している。

この露光装置を用いて、ウェハ202の露光を行う際には、ウェハ202の表面に、複数のパターン投影領域が設定される。照明装置204より出射された光束は、マスク201を通過し、縮小投影光学系203によって1つのパターン投影領域に照射される。これにより、マスク201が有するマスクパターンが、縮小投影光学系203を介して1つのパターン投影領域に投影され、1つのパターン投影領域を露光する処理が行われる。この露光装置では、マスクパターンに基づいて1つのパターン投影領域を露光する処理を行なった後、ウェハ202をX方向またはY方向に移動させ、次のパターン投影領域において、同様の露光処理を行なう。

本実施の形態において、フレーム108を形成する工程では、まず、図6に示した構造物において、複数の半導体チップ予定部30Pを覆うように、絶縁層106の上にフォトレジスト層を形成する。本実施の形態では、フォトレジスト層はネガ型である。このネガ型のフォトレジスト層では、光が照射されなかった部分は現像液に対して可溶性であり、光が照射された部分は現像液に対して不溶性になる。次に、フォトリソグラフィによりフォトレジスト層をパターニングすることによってフレーム108を形成する。このフレーム108を形成する際に、フォトレジスト層を露光するために、図14に示した露光装置が使用される。この場合、図6に示した構造物の上にフォトレジスト層が形成されたものが、図14におけるウェハ202となる。また、複数のパターン投影領域は、フォトレジスト層の表面において、複数の半導体チップ予定部30Pに対応する部分に設定される。パターン投影領域の大きさは、半導体チップ予定部30Pの上面よりわずかに大きく、複数の電極32が形成される予定の部分を含む大きさに設定される。ウェハソートテストによって得られた基礎構造物前ウェハ101毎の、正常に動作する半導体チップ予定部30Pと正常に動作しない半導体チップ予定部30Pの位置情報は、基礎構造物前ウェハ101に対応するウェハ202におけるフォトレジスト層を露光する際に、制御装置250に入力され、制御装置250によって保持される。制御装置250は、その位置情報に基づいて、マスク201を交換することができる。

次に、図15のフローチャートを参照して、本実施の形態におけるフレーム108を形成するためのフォトレジスト層の露光工程について説明する。この露光工程では、フォトレジスト層のうち、正常に動作しない半導体チップ予定部30Pに対応する部分には、正常に動作しない半導体チップ予定部30Pに接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有する電極に対応する潜像が形成されず、フォトレジスト層のうち、正常に動作する半導体チップ予定部30Pに対応する部分には、複数の電極32に対応した潜像が形成されるように、フォトレジスト層の露光を行う。この露光工程では、まず、図14に示した露光装置において、複数の半導体チップ予定部30Pに対応する複数のパターン投影領域のうち、最初の半導体チップ予定部30Pに対応するパターン投影領域が露光される状態に設定される(ステップS101)。次に、設定されたパターン投影領域に対応する半導体チップ予定部30Pが正常に動作する半導体チップ予定部30Pか否かが、制御装置250によって判断される(ステップS102)。

ステップS102において、正常に動作する半導体チップ予定部30Pであると判断された場合(Y)には、複数の電極32に対応したパターン(以下、電極パターンと記す。)を有するマスク201を用いて、フォトレジスト層のうち、正常に動作する半導体チップ予定部30Pに対応する部分に対して、電極パターンによる露光を行う(ステップS103)。電極パターンは、具体的には、パターン投影領域のうち、後に電極32を収容する溝部108aが形成される部分に対しては光が照射されず、他の部分に対しては光が照射されるようにするパターンである。この露光により、フォトレジスト層のうち、正常に動作する半導体チップ予定部30Pに対応する部分には、複数の電極32に対応した潜像が形成される。具体的には、この露光が行われた後、フォトレジスト層のうち、正常に動作する半導体チップ予定部30Pに対応する部分では、後に電極32を収容する溝部108aが形成される部分は現像液に対して可溶性であり、他の部分は現像液に対して不溶性になる。

ステップS102において、正常に動作しない半導体チップ予定部30Pであると判断された場合(N)には、全面的に光を透過するマスク201を用いて、あるいはマスク201を用いずに、フォトレジスト層のうち、正常に動作しない半導体チップ予定部30Pに対応する部分に対して、全面的に露光を行う(ステップS104)。これにより、フォトレジスト層のうち、正常に動作しない半導体チップ予定部30Pに対応する部分には、正常に動作しない半導体チップ予定部30Pに接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有する電極に対応する潜像は形成されない。具体的には、フォトレジスト層のうち、正常に動作しない半導体チップ予定部30Pに対応する部分の全体が、現像液に対して不溶性になる。なお、第2の種類の階層部分10が、正常に動作しない半導体チップ30に接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有するような形態の電極ではない、他の形態の電極や配線を含んでいる場合には、ステップS104において、全面的に露光を行う代りに、他の形態の電極や配線に対応する潜像が形成されるように露光を行う。この場合にも、フォトレジスト層のうち、正常に動作しない半導体チップ予定部30Pに対応する部分には、正常に動作しない半導体チップ予定部30Pに接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有する電極に対応する潜像は形成されない。

ステップS103またはステップS104の実行後は、ステップS103またはステップS104を実行した露光したパターン投影領域が、最後の半導体チップ予定部30Pに対応するパターン投影領域であったか否かが、制御装置250によって判断される(ステップS105)。最後の半導体チップ予定部30Pに対応するパターン投影領域であった場合(Y)には、露光工程を終了する。最後の半導体チップ予定部30Pに対応するパターン投影領域ではなかった場合(N)には、次の半導体チップ予定部30Pに対応するパターン投影領域が露光される状態に設定されて(ステップS106)、ステップS102以降の処理が繰り返される。

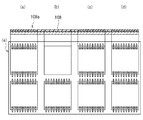

図16は、図15に示した露光工程を示す説明図である。図16において、符号108Pは、フレーム108を形成するために用いられるフォトレジスト層を示している。図16において、(a)、(b)、(c)、(d)は、ステップS103またはステップS104が実行される領域を表している。図16に示した例では、領域(a)、(b)、(c)、(d)の順に、ステップS103またはステップS104が実行されている。また、領域(a)、(c)、(d)では、ステップS102において、正常に動作する半導体チップ予定部30Pであると判断され、電極パターンを有するマスク201Aを用いて、フォトレジスト層108Pのうち、正常に動作する半導体チップ予定部30Pに対応する部分に対して、電極パターンによる露光が行われている。領域(b)では、ステップS102において、正常に動作しない半導体チップ予定部30Pであると判断され、全面的に光を透過するマスク201Bを用いて(あるいはマスク201を用いずに)、フォトレジスト層108Pのうち、正常に動作しない半導体チップ予定部30Pに対応する部分に対して、全面的に露光が行われている。図16において、(e)は、露光によってフォトレジスト層108Pに形成された潜像の平面形状を表している。

上記の露光工程の後、フォトレジスト層108Pは、現像液によって現像され、これにより、フレーム108が形成される。図17は、この現像により形成されたフレーム108を表している。図17における領域(a)、(b)、(c)、(d)は、図16における領域(a)、(b)、(c)、(d)に対応している。図17において、領域(a)、(c)、(d)ではフレーム108に溝部108aが形成されているが、領域(b)ではフレーム108に溝部108aは形成されていない。図17において、(e)は、溝部108aの平面形状を表している。

次に、例えばめっき法によって、フレーム108の複数の溝部108a内に複数の電極32を形成し、フレーム108を除去する。図18は、このようにして形成された複数の電極32を表している。図18における領域(a)、(b)、(c)、(d)は、図16における領域(a)、(b)、(c)、(d)に対応している。図18において、領域(a)、(c)、(d)では複数の電極32が形成されているが、領域(b)では、半導体チップ予定部30Pに接続される電極は形成されていない。図18において、(e)は、複数の電極32の平面形状を表している。

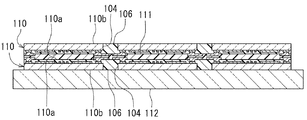

次に、複数の電極32の形成後の工程について説明する。図19は、図8に示した工程に続く工程を示している。この工程では、2つの研磨前基礎構造物109を、それらの第1の面109a同士が対向するように、絶縁性の接着剤によって張り合わせて、2つの研磨前基礎構造物109を含む積層体を作製する。接着剤によって形成される絶縁層111は、電極32を覆い、絶縁部31の一部となる。絶縁層111は、透明であることが好ましい。以下、図19に示した2つの研磨前基礎構造物109のうちの下側の研磨前基礎構造物109を、第1の研磨前基礎構造物109と呼ぶ。また、第1の研磨前基礎構造物109を作製する基となる基礎構造物前ウェハ101を第1の基礎構造物前ウェハ101と呼ぶ。また、図19に示した2つの研磨前基礎構造物109のうちの上側の研磨前基礎構造物109を、第2の研磨前基礎構造物109と呼ぶ。また、第2の研磨前基礎構造物109を作製する基となる基礎構造物前ウェハ101を第2の基礎構造物前ウェハ101と呼ぶ。

次に、図19に示した積層体における両面、すなわち第1の研磨前基礎構造物109の第2の面109bおよび第2の研磨前基礎構造物109の第2の面109bを研磨する。この研磨は、複数の溝104が露出するまで行う。図19において、破線は、研磨後の第2の面109bの位置を示している。

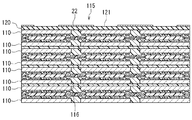

図20は、上述のようにして両面が研磨された後の積層体を示している。第1の研磨前基礎構造物109の第2の面109bを研磨することにより、第1の研磨前基礎構造物109が研磨により薄くされることによって、基礎構造物110が形成される。以下、この基礎構造物110を第1の基礎構造物110と呼ぶ。同様に、第2の研磨前基礎構造物109の第2の面109bを研磨することにより、第2の研磨前基礎構造物109が研磨により薄くされることによって、基礎構造物110が形成される。以下、この基礎構造物110を第2の基礎構造物110と呼ぶ。第1および第2の基礎構造物110の厚みは、それぞれ、例えば30〜100μmである。各基礎構造物110は、研磨前基礎構造物109の第1の面109aに対応する第1の面110aと、その反対側の第2の面110bとを有している。第2の面110bは、研磨された面である。

上述のように2つの研磨前基礎構造物109を含む積層体の両面を研磨する工程では、積層体の一方の面を研磨した後、この研磨された面に、図20に示した板状の治具112を張り付けた後、他方の面の研磨を行う。このように積層体の研磨後の面に治具112を張り付けることにより、その後の工程において、積層体の取り扱いが容易になると共に積層体が損傷を受けることを防止することができる。また、絶縁層106,111が透明である場合には、治具112としてアクリル板、ガラス板等の透明なものを用いることにより、いずれも透明な治具112および絶縁層106,111を通して、積層体に含まれる2つの基礎構造物110におけるアライメントマーク107を見ることが可能になる。これにより、後で説明するように、図20に示した積層体を2つ以上積層する際に、アライメントマーク107を利用して、積層体同士の位置合わせを行うことが可能になる。

図21は、図20に示した工程で作製される基礎構造物110の一部を示している。前述のように、複数の溝104が露出するまで、研磨前基礎構造物109の第2の面109bを研磨することにより、複数の半導体チップ予定部30Pは、互いに分離されて、それぞれ半導体チップ30となる。半導体チップ30の第1の面30aは半導体ウェハ100の第1の面100aに対応し、半導体チップ30の第2の面30bは半導体ウェハ100の第2の面100bに対応する。半導体チップ30の複数の端子34は、第1の面30aに配置されている。

ここで、図22および図23を参照して、第1の基礎構造物110における複数の端子34および複数の電極32の配置と、第2の基礎構造物110における複数の端子34および複数の電極32の配置の一例について説明する。図22は、第1の基礎構造物110の第1の面110a側から見たときの、第1の基礎構造物110の複数の端子34および複数の電極32を示している。図23は、第2の基礎構造物110の第2の面110b側から見たときの第2の基礎構造物110の複数の端子34および複数の電極32を示している。後に、図22および図23に示したスクライブライン102Aに沿って基礎構造物110が切断されることにより、本体2の1つの側面に配置される複数の電極32の端面が露出する。

ここで、図22に示した第1の基礎構造物110に含まれる半導体チップ30を第1の半導体チップ30と呼び、図23に示した第2の基礎構造物110に含まれる半導体チップ30を第2の半導体チップ30と呼ぶ。

図22に示したように、第1の半導体チップ30は、所定の順序で配列された複数の第1の端子34を有している。ここで、図22に示したように、複数の第1の端子34のうち、半導体チップ30の第1の面30aの1つの辺に沿って配列された9つの端子に着目する。図22では、この9つの端子を、記号A〜Iを付して示している。第1の半導体チップ30において、端子A〜Iは、図22における左側から右側へ向かう方向にA〜Iの順に1列に配列されている。

図23に示した第2の半導体チップ30は、図22に示した第1の半導体チップ30の第1の端子34に対応して所定の順序で配列された複数の第2の端子34を有している。特に、第2の半導体チップ30は、第1の半導体チップ30の端子A〜Iに対応し、これと同様に配列された端子A〜Iを有している。半導体チップ30の第1の面30aから見た場合には、第1の半導体チップ30の端子A〜Iの配列の順序と第2の半導体チップ30の端子A〜Iの配列の順序は同じである。しかし、第1の半導体チップ30と第2の半導体チップ30が、第1の面30a同士が対向するように配置された状態では、図22および図23に示したように、同一方向例えば第2の半導体チップ30の第2の面30b側から見たときに、第2の半導体チップ30の端子A〜Iの配列の順序は、第1の半導体チップ30の端子A〜Iの配列の順序とは逆になる。

ここで、後に図22および図23に示したスクライブライン102Aの位置に形成されることになる複数の電極32の端面についても、半導体チップ30の端子A〜Iに対応するものを記号A〜Iで表す。図22に示したように、第1の基礎構造物110では、同一方向から見たときに、スクライブライン102Aの位置に形成されることになる複数の電極32の端面A〜Iは、対応する複数の端子A〜Iの配列と同じ順序で配列されている。言い換えると、第1の基礎構造物110における複数の電極32は、複数の電極32の端面A〜Iの配列が、対応する複数の端子A〜Iの配列と同じ順序になるようなパターンで形成されている。

これに対し、図23に示したように、第2の基礎構造物110では、同一方向から見たときに、スクライブライン102Aの位置に形成されることになる複数の電極32の端面A〜Iは、対応する複数の端子A〜Iの配列とは逆の順序で配列されている。言い換えると、第2の基礎構造物110における複数の電極32は、複数の電極32の端面A〜Iの配列が、対応する複数の端子A〜Iの配列とは逆の順序になるようなパターンで形成されている。

図22および図23に示した第1および第2の基礎構造物110を含む積層基礎構造物を用いて作製された積層チップパッケージ1では、同一方向から見たときに、第2の半導体チップ30の端子A〜Iの配列の順序は、第1の半導体チップ30の端子A〜Iの配列の順序とは逆であり、本体2の1つの側面に配置され、第1の半導体チップ30の端子A〜Iに接続された複数の電極32の端面は、対応する端子A〜Iの配列と同じ順序で配列され、本体2の1つの側面に配置され、第2の半導体チップ30の端子A〜Iに接続された複数の電極32の端面は、対応する端子A〜Iの配列とは逆の順序で配列される。その結果、本体2の1つの側面において、第1の半導体チップ30の端子A〜Iに接続された複数の電極32の端面と、第2の半導体チップ30の端子A〜Iに接続された複数の電極32の端面は、同じ順序で配列される。

ここで、積層チップパッケージ1に含まれる一対の階層部分において、同様に配列された複数の端子34を有する第1および第2の半導体チップ30を、第1の面30a同士が対向するように配置し、第1および第2の半導体チップ30における対応する端子34同士を接続する場合について考える。この場合、図22および図23に示した第1および第2の基礎構造物110における複数の端子34および複数の電極32の配置の例によれば、本体2の1つの側面において、第1の半導体チップ30の複数の端子34に接続された複数の電極32の端面と、第2の半導体チップ30の複数の端子34に接続された複数の電極32の端面とが同じ順序で配列される。これにより、第1および第2の半導体チップ30における対応する端子34同士を配線3によって容易に接続することが可能になる。

なお、ここまで、図22および図23に示した半導体チップ30の第1の面30aの1つの辺に沿って配列された複数の端子34とそれに接続された複数の電極32について説明してきたが、この説明は、上記の辺とは反対側の辺に沿って配列された複数の端子34とそれに接続された複数の電極32についても当てはまる。

図24は、図20に示した工程に続く工程を示している。この工程では、図20に示したように、2つの基礎構造物110を含み、治具112に張り付けられた積層体を2つ用意し、これらを接着剤によって接合して、4つの基礎構造物110を含む新たな積層体を作製する。図24において、符号116は、接着剤によって形成された接着層を示している。ここで、前述のように、絶縁層106,111が透明である場合には、治具112としてアクリル板、ガラス板等の透明なものを用いることにより、いずれも透明な治具112および絶縁層106,111を通して、積層体に含まれる2つの基礎構造物110におけるアライメントマーク107を見ることが可能になる。これにより、後で説明するように、それぞれ2つの基礎構造物110を含む2つの積層体を接合する際に、アライメントマーク107を利用して、積層体同士の位置合わせを行うことが可能になる。

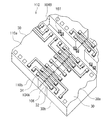

図25は、図24に示した工程に続く工程を示している。この工程では、図24に示したように4つの基礎構造物110を含む積層体を2つ用意し、これらを接着剤によって接合して、8つの基礎構造物110を含む新たな積層体を作製する。

図26および図27は、図25に示した工程に続く工程を示す。この工程では、図25に示した工程で作製された8つの基礎構造物110を含む積層体における最も上に配置された基礎構造物110の上に、更に端子用ウェハ120を積層して、積層基礎構造物115を作製する。端子用ウェハ120は、樹脂、セラミック等の絶縁材料によって形成された板状のウェハ本体121を有している。ウェハ本体121は、後に互いに分離されてそれぞれ端子層本体21となる複数の端子層本体予定部21Pを含んでいる。端子用ウェハ120は、更に、ウェハ本体121の上面に配置された複数組のパッド状端子22を有している。1組のパッド状端子22は、1つの端子層本体予定部21Pに配置されている。なお、図26および図27には、隣接する2つの端子層本体予定部21Pの境界において、2つの端子層本体予定部21Pの各々に配置された複数のパッド状端子22同士が連結されている例を示している。しかし、隣接する2つの端子層本体予定部21Pの各々に配置された複数のパッド状端子22は連結されていなくてもよい。ウェハ本体121は透明であってもよい。この場合、ウェハ本体121の上面において、隣接する2つの端子層本体予定部21Pの境界の位置にアライメントマークを設けてもよい。

本実施の形態において、積層基礎構造物115を作製する工程は、第1の基礎構造物前ウェハ101を作製する工程と、第2の基礎構造物前ウェハ101を作製する工程と、第1の基礎構造物前ウェハ101を用いて第1の研磨前基礎構造物109を作製する工程と、第2の基礎構造物前ウェハ101を用いて第2の研磨前基礎構造物109を作製する工程と、第1の研磨前基礎構造物109と第2の研磨前基礎構造物109の第1の面109a同士が対向するように、第1の研磨前基礎構造物109と第2の研磨前基礎構造物109とを張り合わせる工程と、張り合わされた状態の第1の研磨前基礎構造物109と第2の研磨前基礎構造物109のそれぞれの第2の面109bを研磨する工程とを含んでいる。

第1および第2の基礎構造物前ウェハ101は、いずれも、図4を参照して説明した工程によって作製される。第1および第2の研磨前基礎構造物109は、いずれも、図5ないし図8を参照して説明した工程によって作製される。張り合わされた状態の第1の研磨前基礎構造物109と第2の研磨前基礎構造物109のそれぞれの第2の面109bを研磨する工程によって、第1の研磨前基礎構造物109が研磨により薄くされることによって形成された第1の基礎構造物110と第2の研磨前基礎構造物109が研磨により薄くされることによって形成された第2の基礎構造物110との積層体が得られる。

単独の状態の研磨前基礎構造物109に対して研磨を行って基礎構造物110を作製すると、基礎構造物110が例えば30〜100μmのように薄くなるために、基礎構造物110の取り扱いが難しくなると共に、基礎構造物110が損傷を受け易くなる。また、基礎構造物110において半導体チップ30と絶縁層106の熱膨張係数が異なることから、基礎構造物110が薄くなると、基礎構造物110が丸まってしまい、この点からも、基礎構造物110の取り扱いが難しくなると共に、基礎構造物110が損傷を受け易くなる。

本実施の形態では、第1の面109a同士が対向するように第1の研磨前基礎構造物109と第2の研磨前基礎構造物109とを張り合わせ、この張り合わされた状態の第1の研磨前基礎構造物109と第2の研磨前基礎構造物109のそれぞれの第2の面109bを研磨する。これにより、第1の研磨前基礎構造物109が研磨により薄くされることによって形成された第1の基礎構造物110と第2の研磨前基礎構造物109が研磨により薄くされることによって形成された第2の基礎構造物110との積層体が得られる。この第1および第2の基礎構造物110を含む積層体の強度は、単独の状態の基礎構造物110に比べて大きい。そのため、本実施の形態によれば、第1および第2の基礎構造物110の取り扱いが容易になると共に、第1および第2の基礎構造物110が損傷を受け難くなる。

また、本実施の形態では、第1の面110a同士が対向するように張り合わされた第1および第2の基礎構造物110を含む積層体が得られる。第1および第2の基礎構造物110に、それぞれ、単独の状態では基礎構造物110を丸めるように作用する応力が存在する場合、本実施の形態によれば、第1および第2の基礎構造物110の応力を相殺することができる。そのため、本実施の形態によれば、第1および第2の基礎構造物110の平坦性を維持することができる。

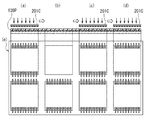

以下、積層基礎構造物115を用いて、複数の積層チップパッケージ1を作製する工程について説明する。この工程では、まず、図28に示したように、ダイシングソーによって、図21における第1の溝104Aに沿って、積層基礎構造物115を切断して、複数の本体集合体130を作製する。図29は本体集合体130の一例を示し、図30は本体集合体130の他の例を示している。図29および図30に示したように、本体集合体130は、積層チップパッケージ1の複数の階層部分10の積層方向と直交する一方向に配列され、それぞれ後に本体2となる複数の本体予定部2Pを含んでいる。図29に示した本体集合体130は、端子用ウェハ120のウェハ本体121が透明で、ウェハ本体121の上面において、隣接する2つの端子層本体予定部21Pの境界の位置に、アライメントマーク123が設けられた積層基礎構造物115を切断して得られたものである。図30に示した本体集合体130は、ウェハ本体121の上面にアライメントマーク123が設けられていない積層基礎構造物115を切断して得られたものである。なお、図29および図30には、本体集合体130が5つの本体予定部2Pを含む例を示したが、本体集合体130に含まれる本体予定部2Pの数は複数であればよい。

積層基礎構造物115の切断は、積層基礎構造物115を板状の治具または一般的にウェハのダイシングの際に使用されるウェハシートに張り付けた状態で行ってもよい。図28は、積層基礎構造物115を板状の治具125に張り付けた状態で、積層基礎構造物115の切断を行った例を示している。また、図28では、治具125は切断されていないが、積層基礎構造物115と共に治具125も切断してもよい。

図29および図30に示したように、本体集合体130は、上面と、下面と、4つの側面を有している。本体集合体130の下面には、治具126を張り付けてもよい。この治具126は、積層基礎構造物115を切断する際に積層基礎構造物115に張り付けた治具125が切断されて形成されたものであってもよい。

積層基礎構造物115を切断する工程では、図21における第1の溝104Aが延びる方向に沿って切断面が形成されるように絶縁層106が切断される。図31は、積層基礎構造物115を切断することによって作製された本体集合体130の一部を示している。図31に示したように、絶縁層106は、切断されることにより、絶縁部31の一部である絶縁層31Aとなる。また、絶縁層106の切断面、すなわち絶縁層31Aの切断面31Aaによって、絶縁部31の端面31aの一部が形成される。

積層基礎構造物115を切断する工程では、絶縁層106が切断される際に、電極32を覆う絶縁層113も切断される。絶縁層113は、切断されることにより、絶縁部31の他の一部である絶縁層31Bとなる。また、絶縁層113の切断面、すなわち絶縁層31Bの切断面31Baによって、絶縁部31の端面31aの他の一部が形成される。

また、積層基礎構造物115を切断する工程では、絶縁層106が切断されることによって、絶縁部31の端面31aから複数の電極32の端面32aが露出する。端面32aは、絶縁部31によって囲まれている。

積層基礎構造物115を切断することにより、本体集合体130の4つの側面のうち、複数の本体予定部2Pが並ぶ方向に平行な2つの側面に、それぞれ、複数の電極32の端面32aが現れる。より詳しく説明すると、本体集合体130の1つの側面には、本体集合体130に含まれる全ての階層部分10における複数の電極32Aの端面32Aaが現れ、この側面とは反対側の本体集合体130の側面には、本体集合体130に含まれる全ての階層部分10における複数の電極32Bの端面32Baが現れる。

複数の積層チップパッケージ1を作製する工程では、積層基礎構造物115を切断した後、複数の電極32の端面32aが現れる本体集合体130の2つの側面を研磨する。次に、本体集合体130における各本体予定部2Pに対してそれぞれ配線3A,3Bを形成する。この配線3A,3Bを形成する工程では、複数の本体集合体130を、複数の階層部分10の積層方向に並べた後、この複数の本体集合体130における各本体予定部2Pに対して同時に配線3A,3Bを形成してもよい。これにより、短時間で、多数の本体予定部2Pに対して配線3A,3Bを形成することが可能になる。

図32は、複数の本体集合体130を並べる方法の一例を示している。この例では、チップの位置の認識および制御が可能なチップボンディング装置を利用して、テーブル142上において、それぞれ治具126が張り付けられた複数の本体集合体130を、位置合わせを行いながら複数の階層部分10の積層方向に並べている。図32において、符号141は、チップを保持するためのヘッドを示している。この例では、治具126が張り付けられた状態の本体集合体130をヘッド141によって保持し、本体集合体130の位置の認識および制御を行いながら、本体集合体130をテーブル142上の所望の位置に配置している。図33は、それぞれ治具126が張り付けられた複数の本体集合体130が、複数の階層部分10の積層方向に並べられた状態を表している。なお、並べられた複数の本体集合体130を、容易に分離可能に接着して固定してもよい。

複数の本体集合体130を並べる際には、チップボンディング装置が備えている画像認識装置によって、本体集合体130の外縁の位置や、本体集合体130の側面に現れている電極32の端面32aの位置を認識することにより、本体集合体130の位置の認識および制御を行うことが可能になる。

また、それぞれ治具126が張り付けられていない複数の本体集合体130を、位置合わせを行いながら、複数の階層部分10の積層方向に並べてもよい。図34は、このようにして並べられた複数の本体集合体130を表している。この場合も、並べられた複数の本体集合体130を、容易に分離可能に接着して固定してもよい。

それぞれ治具126が張り付けられていない複数の本体集合体130を並べる場合において、絶縁部31および端子層本体21となる部分が透明で、アライメントマーク107,123の少なくとも一方を観察可能な場合には、チップボンディング装置が備えている画像認識装置によって、アライメントマーク107,123の少なくとも一方を認識することにより、本体集合体130の位置の認識および制御を行ってもよい。この場合には、画像認識装置によって、図32において符号143で示す矢印方向からアライメントマークを観察する。

次に、図35を参照して、配線3A,3Bを形成する工程について説明する。この工程では、本体集合体130における各本体予定部2Pに対してそれぞれ配線3A,3Bを形成する。配線3A,3Bは、例えばフレームめっき法によって形成される。この場合には、まず、配線3Aを形成すべき本体集合体130の側面上に、めっき用のシード層を形成する。次に、シード層の上に、溝部を有するフレームを形成する。このフレームは、例えば、フォトレジストフィルムをフォトリソグラフィによりパターニングすることによって形成される。次に、めっき法によって、フレームの溝部内であってシード層の上に、配線3Aの一部となるめっき層を形成する。次に、フレームを除去し、更に、シード層のうち、めっき層の下に存在する部分以外の部分をエッチングによって除去する。これにより、めっき層およびその下に残ったシード層によって配線3Aが形成される。次に、配線3Bを形成すべき本体集合体130の側面上に、配線3Aの形成方法と同様の方法によって配線3Bを形成する。図35は、配線3A,3Bが形成された後の本体集合体130の一部を示している。

次に、図36を参照して、本体集合体130を切断する工程について説明する。この工程では、本体集合体130に含まれる複数の本体予定部2Pが互いに分離されてそれぞれ本体2となることによって複数の積層チップパッケージ1が形成されるように、本体集合体130を切断する。このようにして、図36に示したように、積層チップパッケージ1が複数個同時に製造される。

本実施の形態に係る積層チップパッケージ1は、そのままの状態で、1つの電子部品として使用することが可能である。例えば、積層チップパッケージ1は、複数の複数のパッド状端子22が下を向くように配線基板上に配置することにより、フリップチップ法によって配線基板に実装することができる。

また、例えば、積層チップパッケージ1を使用する装置に、積層チップパッケージ1を収容する凹部が設けられている場合には、複数のパッド状端子22が上を向くようにして、凹部内に積層チップパッケージ1を挿入し、複数のパッド状端子22を装置内の回路に接続することができる。

図37は、積層チップパッケージ1の使用例を示している。この例では、積層チップパッケージ1の複数のパッド状端子22にそれぞれボンディングワイヤ160の一端を接続している。ボンディングワイヤ160の他端は、積層チップパッケージ1を使用する装置における端子に接続される。

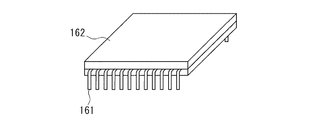

図38および図39は、積層チップパッケージ1の他の使用例を示している。この例では、複数のピン161を有するリードフレームに積層チップパッケージ1を取り付け、積層チップパッケージ1をモールド樹脂によって封止している。積層チップパッケージ1の複数のパッド状端子22は、複数のピン161に接続されている。モールド樹脂は、積層チップパッケージ1を保護する保護層162となる。図38は、複数のピン161が水平方向に延びている例を示している。図39は、複数のピン161が下方に向けて折り曲げられた例を示している。

以上説明したように、本実施の形態によれば、積層された複数のチップ30を含み、高集積化の可能な積層チップパッケージ1を実現することができる。本実施の形態に係る積層チップパッケージ1は、上面、下面および4つの側面を有する本体2と、この本体2の少なくとも1つの側面に配置された配線3とを備えている。本体2は、積層された複数の階層部分10を含んでいる。複数の階層部分10は、1つ以上の第1の種類の階層部分10と、1つ以上の第2の種類の階層部分10とを含んでいる。第1の種類の階層部分10と第2の種類の階層部分10は、いずれも、半導体チップ30と、半導体チップ30の4つの側面のうちの少なくとも1つの側面を覆う絶縁部31とを含んでいる。絶縁部31は、配線3が配置された本体2の少なくとも1つの側面に配置された少なくとも1つの端面31aを有している。

第1の種類の階層部分10における半導体チップ30は良品の半導体チップ30であり、第2の種類の階層部分10における半導体チップ30は不良の半導体チップ30である。第1の種類の階層部分10は、更に、それぞれ半導体チップ30に接続され、配線3が配置された本体2の少なくとも1つの側面に配置された端面32aを有する複数の電極32を含むが、第2の種類の階層部分10は、半導体チップ30に接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有する電極を含んでいない。複数の電極32の端面32aは、それぞれ絶縁部31によって囲まれている。配線3は、複数の電極32の端面32aに接続されている。

本実施の形態に係る積層チップパッケージ1の製造方法は、積層チップパッケージ1の複数の階層部分10にそれぞれ対応する複数の基礎構造物110であって、各々が対応する階層部分10を複数含み、後にそれら対応する階層部分10のうちの隣接するもの同士の境界位置で切断される複数の基礎構造物110を作製する工程と、複数の基礎構造物110を用いて本体2を作製すると共に、本体2に対して配線3を形成して、積層チップパッケージ1を完成させる工程とを備えている。

複数の基礎構造物110を作製する工程は、各基礎構造物110を作製するための一連の工程として、配列された複数の半導体チップ予定部30Pを含む基礎構造物前ウェハ101を作製する工程と、基礎構造物前ウェハ101に含まれる複数の半導体チップ予定部30Pについて、正常に動作する半導体チップ予定部30Pと正常に動作しない半導体チップ予定部30Pとを判別する工程と、正常に動作しない半導体チップ予定部30Pに接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有する電極を形成することなく、正常に動作する半導体チップ予定部30Pに接続されるように複数の電極32を形成する工程とを含んでいる。

本実施の形態に係る積層チップパッケージ1では、不良の半導体チップ30を含む第2の種類の階層部分10では、半導体チップ30に接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有する電極が設けられないことから、不良の半導体チップ30は使用不能にされる。

もし、不良の半導体チップ30を含む階層部分10においても、半導体チップ30に接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有する電極が設けられていると、この電極は配線3に接続される。この場合、不良の半導体チップ30に接続された電極は、メモリデバイス等、積層チップパッケージ1によって実現するデバイスにとって不要なキャパシタンスや不要なインダクタンスを発生させたり、良品の半導体チップ30に接続された電極32等との間に浮遊容量を発生させたりする。このことは、メモリデバイス等のデバイスの動作の高速化の妨げとなる。

これに対し、本実施の形態では、前述のように、不良の半導体チップ30を含む第2の種類の階層部分10では、半導体チップ30に接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有する電極が設けられない。そのため、積層チップパッケージ1において、不良の半導体チップ30を含む第2の種類の階層部分10は、単なる絶縁層とみなすことができる。従って、本実施の形態によれば、不良の半導体チップ30に接続された配線に起因する問題を低減しながら、不良の半導体チップ30を使用不能にすることができる。

積層チップパッケージ1が、メモリチップとしての複数の半導体チップ30を含んでいる場合には、1つ以上の不良の半導体チップ30を含んでいても、1つ以上の良品の半導体チップ30を含んでいれば、全ての半導体チップ30が良品である場合に比べるメモリ容量は減るが、メモリ容量の少ない製品として成り立つ。この場合、積層チップパッケージ1に含まれる不良の半導体チップ30の数によって、積層チップパッケージ1のメモリ容量が異なることになるが、メモリ容量毎に積層チップパッケージ1を分類すれば、メモリ容量が異なる複数種類の製品を実現することができる。

なお、積層チップパッケージ1に含まれる半導体チップ30の数を必要最小限の数とすると、不良の半導体チップ30の発生によって、積層チップパッケージ1のメモリ容量が所望のメモリ容量よりも少なくなるような場合には、冗長性を持たせて、必要最小限の数よりも多い数の半導体チップ30を含むように積層チップパッケージ1を構成してもよい。どの程度の冗長性を積層チップパッケージ1に持たせるかは、不良の半導体チップ30の発生率等に応じて任意に決めることができる。

なお、本実施の形態に係る積層チップパッケージ1の製造方法によれば、1つ以上の良品の半導体チップ30と1つ以上の不良の半導体チップ30とを含む積層チップパッケージ1のみならず、複数の良品の半導体チップ30のみを含む積層チップパッケージ1や、複数の不良の半導体チップ30のみを含む積層チップパッケージ1も製造され得る。複数の良品の半導体チップ30のみを含む積層チップパッケージ1は、当然、製品として成り立つ。複数の不良の半導体チップ30のみを含む積層チップパッケージ1は、破棄すればよい。

また、本実施の形態では、積層された複数の半導体チップ30は、本体2の少なくとも1つの側面に配置された配線3によって電気的に接続される。そのため、本実施の形態では、ワイヤボンディング方式における問題点、すなわちワイヤ同士の接触を避けるために電極の間隔を小さくすることが難しいという問題点や、ワイヤの高い抵抗値が回路の高速動作の妨げになるという問題点は生じない。

また、本実施の形態では、貫通電極方式に比べて以下の利点がある。まず、本実施の形態では、チップに貫通電極を形成する必要がないので、チップに貫通電極を形成するための多くの工程は不要である。

また、本実施の形態では、複数の半導体チップ30間の電気的接続を、本体2の少なくとも1つの側面に配置された配線3によって行う。そのため、本実施の形態によれば、複数のチップ間の電気的接続を貫通電極によって行う場合に比べて、チップ間の電気的接続の信頼性を向上させることができる。

また、本実施の形態では、配線3の線幅や厚みを容易に変更することができる。そのため、本実施の形態によれば、将来における配線3の微細化の要望にも容易に対応することができる。

また、貫通電極方式では、上下のチップの貫通電極同士を、例えば、高温下で半田によって接続する必要がある。これに対し、本実施の形態では、配線3は例えばめっき法によって形成することができるため、より低温下で、配線3を形成することが可能である。また、本実施の形態では、複数の階層部分10の接合も低温下で行うことができる。そのため、チップ30が熱によって損傷を受けることを防止することができる。

また、貫通電極方式では、上下のチップの貫通電極同士を接続するため、上下のチップを正確に位置合わせする必要がある。これに対し、本実施の形態では、複数の半導体チップ30間の電気的接続を、上下に隣接する2つの階層部分10の界面では行わず、本体2の少なくとも1つの側面に配置された配線3によって行うため、複数の階層部分10の位置合わせの精度は、貫通電極方式における複数のチップ間の位置合わせの精度に比べて緩やかでよい。

また、本実施の形態に係る積層チップパッケージの製造方法では、特許文献1に記載された積層チップパッケージの製造方法に比べて、工程数を少なくすることができ、その結果、積層チップパッケージのコストを低減することができる。

以上のことから、本実施の形態によれば、積層チップパッケージ1を低コストで短時間に大量生産することが可能になる。

また、本実施の形態に係る積層チップパッケージ1の製造方法によれば、積層基礎構造物115を構成する複数の基礎構造物110を、それらが損傷を受けることを防止しながら、容易に薄くすることができる。そのため、本実施の形態によれば、小型で集積度の高い積層チップパッケージ1を、高い歩留まりで製造することが可能になる。

なお、本実施の形態において、積層基礎構造物115を作製する方法は、図5ないし図27を参照して説明した方法に限らない。例えば、以下のような方法で積層基礎構造物115を作製してもよい。すなわち、まず、第1の研磨前基礎構造物109の第1の面109aが治具に対向するように、第1の研磨前基礎構造物109を治具に張り付ける。次に、第1の研磨前基礎構造物109が研磨により薄くされることによって、第1の基礎構造物110が、治具に張り付けられた状態で形成されるように、治具に張り付けられた第1の研磨前基礎構造物109における第2の面109bを研磨する。次に、第2の研磨前基礎構造物109の第1の面109aが、第1の基礎構造物110の研磨された面に対向するように、第1の基礎構造物110に第2の研磨前基礎構造物109を張り付ける。次に、第2の研磨前基礎構造物109が研磨により薄くされることによって、第2の基礎構造物110が、第1の基礎構造物110上に積層された状態で形成されるように、第2の研磨前基礎構造物109における第2の面109bを研磨する。更に、必要に応じて、第2の基礎構造物110の形成方法と同様の方法で、第2の基礎構造物110の上に1つ以上の基礎構造物110を積層して、積層基礎構造物115を作製する。

あるいは、第2の面110b同士が対向するように2つの基礎構造物110を張り合わせて、2つの基礎構造物110を含む積層体を作製し、この積層体を複数積層して積層基礎構造物115を作製してもよい。

[第2の実施の形態]

次に、本発明の第2の実施の形態に係る積層チップパッケージ1の製造方法について説明する。本実施の形態に係る積層チップパッケージ1の製造方法では、フレーム108を形成する工程のみが、第1の実施の形態と異なっている。まず、本実施の形態では、フレーム108を形成するためのフォトレジスト層はポジ型である。

以下、図40のフローチャートを参照して、本実施の形態におけるフレーム108を形成するためのフォトレジスト層の露光工程について説明する。第1の実施の形態と同様に、本実施の形態においても、この露光工程では、フォトレジスト層のうち、正常に動作しない半導体チップ予定部30Pに対応する部分には、正常に動作しない半導体チップ予定部30Pに接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有する電極に対応する潜像が形成されず、フォトレジスト層のうち、正常に動作する半導体チップ予定部30Pに対応する部分には、複数の電極32に対応した潜像が形成されるように、フォトレジスト層の露光を行う。この露光工程では、まず、図14に示した露光装置において、複数の半導体チップ予定部30Pに対応する複数のパターン投影領域のうち、最初の半導体チップ予定部30Pに対応するパターン投影領域が露光される状態に設定される(ステップS201)。次に、設定されたパターン投影領域に対応する半導体チップ予定部30Pが正常に動作する半導体チップ予定部30Pか否かが、制御装置250によって判断される(ステップS202)。

ステップS202において、正常に動作する半導体チップ予定部30Pであると判断された場合(Y)には、複数の電極32に対応した電極パターンを有するマスク201を用いて、フォトレジスト層のうち、正常に動作する半導体チップ予定部30Pに対応する部分に対して、電極パターンによる露光を行う(ステップS203)。本実施の形態における電極パターンは、具体的には、パターン投影領域のうち、後に電極32を収容する溝部108aが形成される部分に対しては光が照射され、他の部分に対しては光が照射されないようにするパターンである。この露光により、フォトレジスト層のうち、正常に動作する半導体チップ予定部30Pに対応する部分には、複数の電極32に対応した潜像が形成される。具体的には、この露光が行われた後、フォトレジスト層のうち、正常に動作する半導体チップ予定部30Pに対応する部分では、後に電極32を収容する溝部108aが形成される部分は現像液に対して可溶性になり、他の部分は現像液に対して不溶性である。

ステップS202において、正常に動作しない半導体チップ予定部30Pであると判断された場合(N)には、フォトレジスト層のうち、正常に動作しない半導体チップ予定部30Pに対応する部分に対して露光を行わない(ステップS204)。これにより、フォトレジスト層のうち、正常に動作しない半導体チップ予定部30Pに対応する部分には、正常に動作しない半導体チップ予定部30Pに接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有する電極に対応する潜像は形成されない。具体的には、フォトレジスト層のうち、正常に動作しない半導体チップ予定部30Pに対応する部分の全体が、現像液に対して不溶性になる。なお、第2の種類の階層部分10が、正常に動作しない半導体チップ30に接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有するような形態の電極ではない、他の形態の電極や配線を含んでいる場合には、ステップS204において、露光を行わない代りに、他の形態の電極や配線に対応する潜像が形成されるように露光を行う。この場合にも、フォトレジスト層のうち、正常に動作しない半導体チップ予定部30Pに対応する部分には、正常に動作しない半導体チップ予定部30Pに接続されると共に配線3が配置された本体2の少なくとも1つの側面に配置される端面を有する電極に対応する潜像は形成されない。

ステップS203またはステップS204の実行後は、ステップS203またはステップS204を実行したパターン投影領域が、最後の半導体チップ予定部30Pに対応するパターン投影領域であったか否かが、制御装置250によって判断される(ステップS205)。最後の半導体チップ予定部30Pに対応するパターン投影領域であった場合(Y)には、露光工程を終了する。最後の半導体チップ予定部30Pに対応するパターン投影領域ではなかった場合(N)には、次の半導体チップ予定部30Pに対応するパターン投影領域が露光される状態に設定されて(ステップS206)、ステップS202以降の処理が繰り返される。

図41は、図40に示した露光工程を示す説明図である。図41において、符号108Pは、フレーム108を形成するために用いられるフォトレジスト層を示している。図41において、(a)、(b)、(c)、(d)は、ステップS203またはステップS204が実行される領域を表している。図41に示した例では、領域(a)、(b)、(c)、(d)の順に、ステップS203またはステップS204が実行されている。また、領域(a)、(c)、(d)では、ステップS202において、正常に動作する半導体チップ予定部30Pであると判断され、電極パターンを有するマスク201Cを用いて、フォトレジスト層108Pのうち、正常に動作する半導体チップ予定部30Pに対応する部分に対して、電極パターンによる露光が行われている。領域(b)では、ステップS202において、正常に動作しない半導体チップ予定部30Pであると判断され、フォトレジスト層108Pのうち、正常に動作しない半導体チップ予定部30Pに対応する部分に対して露光が行われていない。図41において、(e)は、露光によってフォトレジスト層108Pに形成された潜像の平面形状を表している。

上記の露光工程の後、フォトレジスト層108Pは、現像液によって現像され、これにより、フレーム108が形成される。このフレーム108の形状は、第1の実施の形態と同様である。

本実施の形態におけるその他の構成、作用および効果は、第1の実施の形態と同様である。

[第3の実施の形態]

次に、本発明の第3の実施の形態に係る積層チップパッケージ1の製造方法について説明する。本実施の形態に係る積層チップパッケージ1の製造方法では、フレーム108を形成する工程のみが、第1の実施の形態と異なっている。まず、本実施の形態では、フレーム108を形成するためのフォトレジスト層はネガ型である。

本実施の形態では、フレーム108を形成する工程は、フォトレジスト層のうち、複数の半導体チップ予定部30Pに対応する複数の部分の全て、すなわち全てのパターン投影領域に対して、複数の電極32に対応した電極パターンによる露光を行う第1の露光工程と、第1の露光工程の前または後において、フォトレジスト層のうち、正常に動作しない半導体チップ予定部30Pに対応する部分のみに対して、全面的に露光を行う第2の露光工程と、第1および第2の露光工程の後で、フォトレジスト層を現像する工程とを含んでいる。

ここで、図42および図43を参照して、第1の露光工程の後に第2の露光工程を行う場合について説明する。図42は第1の露光工程を示す説明図であり、図43は第2の露光工程を示す説明図である。図42および図43において、符号108Pは、フレーム108を形成するために用いられるフォトレジスト層を示している。

図42において、(a)、(b)、(c)、(d)は、それぞれ、第1の露光工程において、電極パターンによる露光が行われる領域を表している。第1の露光工程では、電極パターンを有するマスク201Aを用いて、フォトレジスト層108Pのうち、複数の半導体チップ予定部30Pに対応する複数の部分の全てに対して、電極パターンによる露光を行う。これにより、フォトレジスト層108Pのうち、複数の半導体チップ予定部30Pに対応する複数の部分の全てにおいて、電極パターンによる潜像が形成される。図42において(e)は、露光によってフォトレジスト層108Pに形成された潜像の平面形状を表している。

図43における領域(a)、(b)、(c)、(d)は、図42における領域(a)、(b)、(c)、(d)に対応している。図43に示した例では、領域(a)、(c)、(d)における半導体チップ予定部30Pは、正常に動作する半導体チップ予定部30Pであり、領域(b)における半導体チップ予定部30Pは、正常に動作しない半導体チップ予定部30Pであるものとする。第2の露光工程では、領域(b)において、フォトレジスト層108Pのうち、正常に動作しない半導体チップ予定部30Pに対応する部分に対して、全面的に露光を行う。図43において、(e)は、露光によってフォトレジスト層108Pに形成された潜像の平面形状を表している。

領域(b)では、図42に示したように、第1の露光工程により潜像が形成されるが、第2の露光工程における全面的な露光により潜像は消滅し、フォトレジスト層108Pのうち、正常に動作しない半導体チップ予定部30Pに対応する部分の全体が、現像液に対して不溶性になる。

上記の第1および第2の露光工程の後、フォトレジスト層108Pは、現像液によって現像され、これにより、フレーム108が形成される。このフレーム108の形状は、第1の実施の形態と同様である。

なお、本実施の形態では、第2の露光工程の後に第1の露光工程を行ってもよい。この場合には、まず、第2の露光工程において、フォトレジスト層108Pのうち、正常に動作しない半導体チップ予定部30Pに対応する部分の全体が、現像液に対して不溶性になる。その後、第1の露光工程により、フォトレジスト層108Pのうち、正常に動作する半導体チップ予定部30Pに対応する部分に、電極パターンによる潜像が形成される。このとき、フォトレジスト層108Pのうち、正常に動作しない半導体チップ予定部30Pに対応する部分に対しても、電極パターンによる露光が行われるが、この部分は既に全面的な露光により、その全体が現像液に対して不溶性になっている。第2の露光工程の後に第1の露光工程を行った場合にも、第1の露光工程の後に第2の露光工程を行った場合と同様のフレーム108が形成される。

本実施の形態では、第1の露光工程と第2の露光工程のいずれにおいても、途中でマスク201を交換する必要がないので、第1の露光工程と第2の露光工程のいずれも短時間で実行することができる。特に第1の露光工程では、全てのパターン投影領域に対して、同じ電極パターンによる露光を行うので、ステッパーを用いて、複数、例えば4〜6のパターン投影領域に対する露光を同時に行うことができる。また、第1の露光工程では、ステッパーの代りに、例えばコンタクトアライナーやプロジェクションアライナーを用いて、全てのパターン投影領域に対する露光を同時に行うことができる。このように第1の露光工程において、複数のパターン投影領域に対する露光を同時に行うことにより、第1の露光工程の所要時間を短縮することができる。以上のことから、本実施の形態によれば、第1または第2の実施の形態に比べて、フレーム108を形成するためにフォトレジスト層108Pを露光する工程の所要時間を短くすることができ、生産性を向上させることができる。

本実施の形態におけるその他の構成、作用および効果は、第1の実施の形態と同様である。

なお、本発明は、上記各実施の形態に限定されず、種々の変更が可能である。例えば、実施の形態では、複数の本体集合体130を並べて、この複数の本体集合体130における各本体予定部2Pに対して同時に配線3を形成したが、複数の本体集合体130を並べずに、1つの本体集合体130における各本体予定部2Pに対して配線3を形成してもよい。

また、配線3が形成された後の本体集合体130を切断して本体2を形成した後、本体集合体130を切断することによって本体2に形成された面に、更に他の配線を形成してもよい。

また、積層チップパッケージ1の本体2は、端子層20を含まずに、配線3の一部が外部接続端子を兼ねていてもよい。