JP2010049696A - 行列計算を行うためのプロセッサ素子のパイプライン処理線形アレー - Google Patents

行列計算を行うためのプロセッサ素子のパイプライン処理線形アレー Download PDFInfo

- Publication number

- JP2010049696A JP2010049696A JP2009234277A JP2009234277A JP2010049696A JP 2010049696 A JP2010049696 A JP 2010049696A JP 2009234277 A JP2009234277 A JP 2009234277A JP 2009234277 A JP2009234277 A JP 2009234277A JP 2010049696 A JP2010049696 A JP 2010049696A

- Authority

- JP

- Japan

- Prior art keywords

- processor element

- array

- processor

- matrix

- complex

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/38—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation

- G06F7/48—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation using non-contact-making devices, e.g. tube, solid state device; using unspecified devices

- G06F7/4806—Computations with complex numbers

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/02—Digital function generators

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F17/00—Digital computing or data processing equipment or methods, specially adapted for specific functions

- G06F17/10—Complex mathematical operations

- G06F17/16—Matrix or vector computation, e.g. matrix-matrix or matrix-vector multiplication, matrix factorization

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3877—Concurrent instruction execution, e.g. pipeline or look ahead using a slave processor, e.g. coprocessor

- G06F9/3879—Concurrent instruction execution, e.g. pipeline or look ahead using a slave processor, e.g. coprocessor for non-native instruction execution, e.g. executing a command; for Java instruction set

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2101/00—Indexing scheme relating to the type of digital function generated

- G06F2101/08—Powers or roots

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2207/00—Indexing scheme relating to methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F2207/38—Indexing scheme relating to groups G06F7/38 - G06F7/575

- G06F2207/3804—Details

- G06F2207/386—Special constructional features

- G06F2207/3884—Pipelining

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/38—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation

- G06F7/48—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation using non-contact-making devices, e.g. tube, solid state device; using unspecified devices

- G06F7/499—Denomination or exception handling, e.g. rounding or overflow

- G06F7/49936—Normalisation mentioned as feature only

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Mathematical Analysis (AREA)

- Software Systems (AREA)

- Computational Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- Computing Systems (AREA)

- Mathematical Physics (AREA)

- Data Mining & Analysis (AREA)

- Algebra (AREA)

- Databases & Information Systems (AREA)

- Complex Calculations (AREA)

Abstract

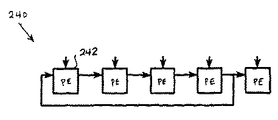

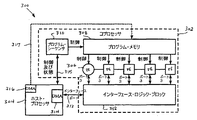

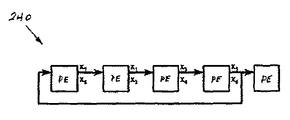

【解決手段】線形アレーは、ヘッド・プロセッサ素子と、一組の通常のプロセッサ素子とを含み、ヘッド・プロセッサ素子は、アレーの最も近い隣接プロセッサ素子と相互接続していて、隣接していない通常のプロセッサ素子から、ヘッド・プロセッサ素子へのフィードバック経路を持つ。各プロセッサ素子は、乗算、組合せおよび演算の累算を行うための演算回路、およびレジスタ・ファイルを含む。ヘッド・プロセッサ素子は、非線形関数ゼネレータを含む。各プロセッサ素子は、終了する算術演算の待ち時間を、それにより新しい演算をスタートする周期の倍数になるように、パイプライン処理している。アレーを制御するために、超長命令語(VLIW)プログラム、またはその他のタイプのプログラムを使用することができる。

【選択図】図7

Description

本出願は、「QR分解用のパイプライン処理線形プロセッサ・アレー」という名称の、発明者A.J.グリーンバーガーの1999年6月10日付の米国仮出願60/138,423号の優先権を主張する。

2.マトリックス反転。一つの可能なアプローチは、ギブンズ回転によりQR分解を使用して一組の方程式を三角形に変換し、その後で、多重逆置換により、逆数について上記一組の三角形に変換した方程式を解く方法である。

3.マトリックス−マトリックス乗算。

4.共分散および相互相関。後でさらに処理が行われる行列およびベクトルを形成するために、入力信号のベクトルに関する上記統計を計算する必要がある。

一組の一次方程式を解く場合には、行列表示は下記式のようになる。

Ax=y (1)

ここで、Aは複素数値の既知の正方行列であり、yは複素数値の既知のベクトルであり、xは未知の複素数ベクトルである。上記式を数値解法するには多くの技術が使用される。しかし、これらの技術のうちのいくつかは、数値が不安定であるという欠点がある。式(1)を解くための数値的に安定な技術は、ギブンズ回転によるQR分解またはQR因数分解と呼ばれ、例えば、1996年に、ジョンズ・ホプキンス大学出版部が発行した、H.ゴルブおよびC.F.バン・ローンの「行列計算」第3版に記載されている。このアプローチは、行列Aを積に因数分解するプロセスを含む。

A≡QR (2)

QHAx=QHy (3)

式(2)を式(3)に代入すると、下記式が得られる。

QHQRx=QHy (4)

QHQは、単位行列に等しいので、式(4)は下記式のようになる。

Rx=QHy (5)

AA-1=I (14)

A=QR (15)

QAR-1=I (16)

RA-1=QH (17)

Rxj=yj (18)

RxWopt=rxd (22)

rxd=E{xy* d} (24)

<プロセッサ素子アーキテクチャ>

高い効率で行列演算を行うために、上記のように構成されている多数のプロセッサ素子は、線形アレーの形に相互接続される。異なるプロセッサ素子相互接続技術は、通常、例えば、QR分解、逆置換、マトリックス反転、マトリックス−マトリックス乗算、および共解散および相互相関の形成のような、異なるタイプの計算のために使用される。

すでに説明したように、QR分解は、二次元三角収縮アレーを使用して、従来技術により達成される。この節においては、図14に示す本発明の線形アレー上で、同じアルゴリズムを、かなり少ないハードウェアを使用して、ほとんど同じ性能で実行する方法について以下に説明する。

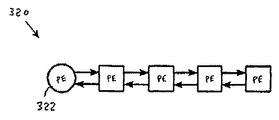

図19は、本発明の5素子線形アレー320である。この線形アレー320は、上記式(13)を解くための二方向相互接続を含む。QR分解プロセスの終了時に計算を行う、アレー320のヘッドプロセッサ素子322は、r行列である、r11、r22、r33およびr44のすべての主要な対角線方向の素子を保持する。その右に隣接するプロセッサ素子は、右に隣接する対角線方向の素子、すなわち、r12、r23、r34およびy4を保持する。

すでに説明したように、QR分解を行った後で、共通のRを共有する多重逆置換を行うことにより、行列を反転することができる。この節においては、ただ一回の逆置換を行う間の、全待ち時間を少し長くするだけで、パイプライン処理素子の線形アレー上で、複数の逆置換を可能にする方法について説明する。

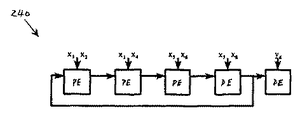

この節においては、図15の例示としての線形アレー230を使用して、第三の複素数行列、AB≡Cを形成するために、8×8複素数行列を掛け算する方法を説明する。使用する技術の場合、計算は、ブロックまたは部分行列に分割される。図20は、16の2×2の積の部分行列に分割された、8×8複素数積行列Cを示す。この図においては、c35、c36、c45およびc46を示す、一つの部分行列を強調してある。以下に示す例の場合には、図15の四つの素子アレー230の各プロセッサ素子は、図20の四つの列のうちの一つを計算するために専用に使用される。この場合、左から三番目のプロセッサ素子により計算される部分行列を強調してある。図20の四つの行のうちの一つの行全体が、アレーの四つのプロセッサ素子により同時に計算される。

この節においては、共分散および相互相関を同時に計算するための、図16の線形アレー240の使用方法を説明する。式(23)および(24)は、共分散および相互相関を計算するためには、フォームの項、xxHおよびxydを計算しなければならないことを示す。

図25、図26および図27を参照しながら、図10のところですでに説明した平方根正規化プロセスについて、さらに詳細に説明する。本発明のこの機能は、ある関数に対するアーギュメントの範囲縮小、および必要な機能を達成するための移行の結果の変換を助けるデジタル・ハードウェアを提供する。説明の都合上、上記関数は下記式で表わされるものと仮定する。

Claims (10)

- 少なくとも一つのデジタル・プロセッサ素子を含む装置であって、

前記デジタル・プロセッサ素子が、

少なくとも二つの複素数の実数部および虚数部に、別の少なくとも二つの複素数の実数部と虚数部とを掛け、それにより少なくとも16個の部分的積を形成するよう動作し、また前記部分的積の、各々が実数または虚数を表わす一つまたはそれより多くの加法組合せを形成するよう動作する演算回路と、

少なくとも第一のポートおよび第二のポートであって、その各々が、前記レジスタ・ファイルへ、または前記レジスタ・ファイルから、二つの複素数語を書き込むことができ、または二つの複素数語を読み出すことができるような第一のポートおよび第二のポートを有し、このポートが、前記複素数語をそこに供給し、そこから前記実数または虚数を受け取るために演算回路に接続されているようなレジスタ・ファイルとを含む装置。 - 請求項1に記載の装置において、前記演算回路が、一つの演算の開始から終了までの待ち時間が、新しい演算をスタートすることができる周期よりも長くなるように構成されたパイプライン処理ロジックを含み、それにより、前記プロセッサ素子が、同時に、各演算が異なる開始時間を持つ一つ以上の演算を計算することができる装置。

- 請求項1に記載の装置において、前記レジスタ・ファイルの前記第一または第二のポートのうちの少なくとも一つが、読み出しまたは書き込みによりアクセスされる前記二つの複素数語の所与の組が、一対の各語線からの同じ語線または別の語線からのものでよいように、語線を制御可能であるように共にペアにするロジックを含む装置。

- 請求項1に記載の装置において、前記演算回路が、さらに、前記部分的積を受け取ることができる入力を持つ少なくとも八つの加算装置を含み、前記加算装置が、前記部分的積の一つまたはそれ以上の加法組合せを形成することができ、前記各加算装置が、一つの実数または虚数を表わし、前記八つの加算装置が一緒になって、四つの複素数の合計を形成することができ、また、各加算装置が、新しい入力数と以前の合計と合計に対応する新しい合計を累算することができるように、その入力に加算する結果からのフィードバック接続を持つ装置。

- 請求項1に記載の装置であって、さらに、前記プロセッサ素子の線形アレーを備え、前記線形アレーの前記各プロセッサ素子が、前記アレーの少なくとも一つの他のプロセッサ素子に接続している装置。

- 請求項5に記載の装置において、前記プロセッサ素子の前記線形アレーが、さらに、一つのヘッド・プロセッサ素子と、複数の通常のプロセッサ素子とを備え、前記ヘッド・プロセッサ素子が、前記各通常のプロセッサ素子の機能のスーパーセットを供給する装置。

- 請求項1に記載の装置において、前記プロセッサ素子が、さらに、非線形関数ゼネレータを含む装置。

- 請求項7に記載の装置において、

前記非線形関数ゼネレータが、ある変数を固定の領域内にシフトすることにより、前記変数をスケールすることができる正規化回路であって、その正規化ロジックが、前記変数をどれだけシフトしたかを示すべき指数値を出力する正規化回路と、

少なくとも1つの非線形関数に対する補間係数の数値のテーブルを記憶するためのメモリと、

選択した数の前記変数の最上位ビットだけを取り上げ、前記変数のところの前記関数の前記数値が、前記補間係数を使用して補間を計算することにより近似できるように、選択した数の最上位ビットを、前記テーブル内の前記関数の補間係数を発見するために、アドレスとして使用するロジック回路とを備える装置。 - 請求項1に記載の装置において、前記プロセッサ素子が、さらに、

前にその入力のところに現われた同じ一連のデジタル語を出力することができるパイプライン処理遅延ラインであって、前記シーケンスの複数の要素が一度に種々の段の遅延ラインを横切るパイプライン処理遅延ラインと、

前記遅延ラインの出力、または前記遅延ラインの遅延のない入力シーケンスとして、その出力を選択することができるマルチプレクサであって、前記選択が前記プロセッサ素子の入力により制御されるマルチプレクサとを備える装置。 - 線形アレーに配置されている複数のデジタル・プロセッサ素子であって、その各々が前記アレーの少なくとも1つの別のプロセッサ素子に接続されているようなデジタル・プロセッサ素子を含む装置において、少なくとも1つの前記デジタル・プロセッサ素子が、

少なくとも二つの複素数の実数部および虚数部に、別の少なくとも二つの複素数の実数部と虚数部とを掛け、それにより少なくとも16個の部分的積を形成するよう動作し、また前記部分的積の、各々が実数または虚数を表わす一つまたはそれより多くの加法組合せを形成するよう動作する演算回路と、

少なくとも第一のポートおよび第二のポートであって、その各々が前記レジスタ・ファイルへ、または前記レジスタ・ファイルから、二つの複素数語を書き込むことができ、または二つの複素数語を読み出すことができるような第一のポートおよび第二のポートを有し、このポートが、前記複素数語をそこに供給し、そこから前記実数または虚数を受け取るために演算回路に接続されているようなレジスタ・ファイルとを含む装置。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13842399P | 1999-06-10 | 1999-06-10 | |

| US60/138423 | 1999-06-10 | ||

| US09/556,760 US6675187B1 (en) | 1999-06-10 | 2000-04-21 | Pipelined linear array of processor elements for performing matrix computations |

| US09/556760 | 2000-04-21 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000174354A Division JP4422299B2 (ja) | 1999-06-10 | 2000-06-09 | 行列計算を行うためのプロセッサ素子のパイプライン処理線形アレー |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010049696A true JP2010049696A (ja) | 2010-03-04 |

| JP5491122B2 JP5491122B2 (ja) | 2014-05-14 |

Family

ID=26836183

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000174354A Expired - Fee Related JP4422299B2 (ja) | 1999-06-10 | 2000-06-09 | 行列計算を行うためのプロセッサ素子のパイプライン処理線形アレー |

| JP2009234277A Expired - Fee Related JP5491122B2 (ja) | 1999-06-10 | 2009-10-08 | 行列計算を行うためのプロセッサ素子のパイプライン処理線形アレー |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000174354A Expired - Fee Related JP4422299B2 (ja) | 1999-06-10 | 2000-06-09 | 行列計算を行うためのプロセッサ素子のパイプライン処理線形アレー |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6675187B1 (ja) |

| JP (2) | JP4422299B2 (ja) |

Families Citing this family (89)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6675187B1 (en) * | 1999-06-10 | 2004-01-06 | Agere Systems Inc. | Pipelined linear array of processor elements for performing matrix computations |

| US7080183B1 (en) * | 2000-08-16 | 2006-07-18 | Koninklijke Philips Electronics N.V. | Reprogrammable apparatus supporting the processing of a digital signal stream and method |

| WO2002037259A1 (en) * | 2000-11-01 | 2002-05-10 | Bops, Inc. | Methods and apparatus for efficient complex long multiplication and covariance matrix implementation |

| JP2002333978A (ja) * | 2001-05-08 | 2002-11-22 | Nec Corp | Vliw型プロセッサ |

| US7382787B1 (en) | 2001-07-30 | 2008-06-03 | Cisco Technology, Inc. | Packet routing and switching device |

| US7418536B2 (en) * | 2001-07-30 | 2008-08-26 | Cisco Technology, Inc. | Processor having systolic array pipeline for processing data packets |

| US7069372B1 (en) * | 2001-07-30 | 2006-06-27 | Cisco Technology, Inc. | Processor having systolic array pipeline for processing data packets |

| WO2003015027A2 (en) * | 2001-08-07 | 2003-02-20 | Board Of Trustees Operating Michigan State University | Self-programmable chip |

| US20030052711A1 (en) * | 2001-09-19 | 2003-03-20 | Taylor Bradley L. | Despreader/correlator unit for use in reconfigurable chip |

| US7218624B2 (en) | 2001-11-14 | 2007-05-15 | Interdigital Technology Corporation | User equipment and base station performing data detection using a scalar array |

| TW518833B (en) * | 2001-12-12 | 2003-01-21 | Defence Dept Chung Shan Inst | Decoding method and circuits for comma-free reed-Solomon codes |

| JP2003242133A (ja) * | 2002-02-19 | 2003-08-29 | Matsushita Electric Ind Co Ltd | 行列演算装置 |

| US6944813B2 (en) * | 2002-04-12 | 2005-09-13 | Chung Shan Institute Of Science And Technology | Weighted decoding method and circuits for Comma-Free Reed-Solomon codes |

| US7051263B2 (en) * | 2002-04-12 | 2006-05-23 | Chung Shan Institute Of Science And Technology | Systolic architecture for Comma-Free Reed-Solomon decoding circuit |

| US7710991B1 (en) | 2002-06-20 | 2010-05-04 | Cisco Technology, Inc. | Scalable packet routing and switching device and method |

| US7450438B1 (en) | 2002-06-20 | 2008-11-11 | Cisco Technology, Inc. | Crossbar apparatus for a forwarding table memory in a router |

| US7525904B1 (en) | 2002-06-20 | 2009-04-28 | Cisco Technology, Inc. | Redundant packet routing and switching device and method |

| US7536476B1 (en) | 2002-12-20 | 2009-05-19 | Cisco Technology, Inc. | Method for performing tree based ACL lookups |

| CN1930783A (zh) * | 2004-02-25 | 2007-03-14 | 三菱电机株式会社 | 接收装置 |

| ITMI20040600A1 (it) * | 2004-03-26 | 2004-06-26 | Atmel Corp | Sistema dsp su chip a doppio processore a virgola mobile nel dominio complesso |

| JP2006099232A (ja) * | 2004-09-28 | 2006-04-13 | Renesas Technology Corp | 半導体信号処理装置 |

| US7889712B2 (en) * | 2004-12-23 | 2011-02-15 | Cisco Technology, Inc. | Methods and apparatus for providing loop free routing tables |

| US7933353B2 (en) * | 2005-09-30 | 2011-04-26 | Intel Corporation | Communication system and technique using QR decomposition with a triangular systolic array |

| US7899857B2 (en) * | 2005-12-30 | 2011-03-01 | L3 Communications Corporation | CPU datapipe architecture with crosspoint switch |

| US8045021B2 (en) * | 2006-01-05 | 2011-10-25 | Qualcomm Incorporated | Memory organizational scheme and controller architecture for image and video processing |

| JP4657998B2 (ja) | 2006-07-21 | 2011-03-23 | ルネサスエレクトロニクス株式会社 | シストリックアレイ |

| US8346831B1 (en) * | 2006-07-25 | 2013-01-01 | Vivante Corporation | Systems and methods for computing mathematical functions |

| US7990989B2 (en) * | 2006-09-16 | 2011-08-02 | Mips Technologies, Inc. | Transaction selector employing transaction queue group priorities in multi-port switch |

| US7773621B2 (en) * | 2006-09-16 | 2010-08-10 | Mips Technologies, Inc. | Transaction selector employing round-robin apparatus supporting dynamic priorities in multi-port switch |

| US7961745B2 (en) * | 2006-09-16 | 2011-06-14 | Mips Technologies, Inc. | Bifurcated transaction selector supporting dynamic priorities in multi-port switch |

| US7760748B2 (en) * | 2006-09-16 | 2010-07-20 | Mips Technologies, Inc. | Transaction selector employing barrel-incrementer-based round-robin apparatus supporting dynamic priorities in multi-port switch |

| JP2009075676A (ja) * | 2007-09-18 | 2009-04-09 | Nec Electronics Corp | マイクロプロセッサ |

| US8589467B2 (en) * | 2007-11-22 | 2013-11-19 | Nec Corporation | Systolic array and calculation method |

| TW200925559A (en) * | 2007-12-05 | 2009-06-16 | Univ Nat Central | Adaptive real-time analyzing method for dynamic signals generated by rotating machines |

| US8307021B1 (en) | 2008-02-25 | 2012-11-06 | Altera Corporation | Hardware architecture and scheduling for high performance solution to cholesky decomposition |

| US8782115B1 (en) * | 2008-04-18 | 2014-07-15 | Altera Corporation | Hardware architecture and scheduling for high performance and low resource solution for QR decomposition |

| US8533251B2 (en) * | 2008-05-23 | 2013-09-10 | International Business Machines Corporation | Optimized corner turns for local storage and bandwidth reduction |

| US8250130B2 (en) * | 2008-05-30 | 2012-08-21 | International Business Machines Corporation | Reducing bandwidth requirements for matrix multiplication |

| WO2010135745A1 (en) * | 2009-05-22 | 2010-11-25 | Maxlinear, Inc. | Signal processing block for a receiver in wireless communication |

| US8473540B1 (en) | 2009-09-01 | 2013-06-25 | Xilinx, Inc. | Decoder and process therefor |

| US8510364B1 (en) | 2009-09-01 | 2013-08-13 | Xilinx, Inc. | Systolic array for matrix triangularization and back-substitution |

| US8417758B1 (en) | 2009-09-01 | 2013-04-09 | Xilinx, Inc. | Left and right matrix multiplication using a systolic array |

| US8473539B1 (en) | 2009-09-01 | 2013-06-25 | Xilinx, Inc. | Modified givens rotation for matrices with complex numbers |

| GR1007291B (el) | 2009-10-01 | 2011-06-01 | Intracom Telecom, | Αντιστροφη πινακα δια εφαρμογης qr αποδομησης επι αρχιτεκτονικης δομης παραλληληλης διοχετευμενης συστολικης διαταξεως |

| US8892620B2 (en) * | 2009-10-07 | 2014-11-18 | Qsigma, Inc. | Computer for Amdahl-compliant algorithms like matrix inversion |

| US8559544B2 (en) * | 2009-11-10 | 2013-10-15 | Georgia Tech Research Corporation | Systems and methods for lattice reduction |

| US8416841B1 (en) * | 2009-11-23 | 2013-04-09 | Xilinx, Inc. | Multiple-input multiple-output (MIMO) decoding with subcarrier grouping |

| US8620984B2 (en) | 2009-11-23 | 2013-12-31 | Xilinx, Inc. | Minimum mean square error processing |

| WO2011150428A1 (en) | 2010-05-28 | 2011-12-01 | Maxlinear, Inc. | Method and system for a low-complexity soft-output mimo detection |

| US8406334B1 (en) * | 2010-06-11 | 2013-03-26 | Xilinx, Inc. | Overflow resistant, fixed precision, bit optimized systolic array for QR decomposition and MIMO decoding |

| US8443031B1 (en) | 2010-07-19 | 2013-05-14 | Xilinx, Inc. | Systolic array for cholesky decomposition |

| JP5787527B2 (ja) * | 2011-01-18 | 2015-09-30 | キヤノン株式会社 | 信号処理回路及び超音波診断装置 |

| US9014249B2 (en) | 2012-11-02 | 2015-04-21 | Harris Corporation | Communications receiver with channel identification using A-priori generated gain vectors and associated methods |

| US9384168B2 (en) | 2013-06-11 | 2016-07-05 | Analog Devices Global | Vector matrix product accelerator for microprocessor integration |

| RU2562389C1 (ru) * | 2014-12-27 | 2015-09-10 | Артем Николаевич Новиков | Устройство обращения ковариационной матрицы помеховых сигналов |

| US9846623B2 (en) | 2015-08-20 | 2017-12-19 | Qsigma, Inc. | Simultaneous multi-processor apparatus applicable to acheiving exascale performance for algorithms and program systems |

| US10635909B2 (en) * | 2015-12-30 | 2020-04-28 | Texas Instruments Incorporated | Vehicle control with efficient iterative triangulation |

| US10489479B1 (en) | 2016-09-12 | 2019-11-26 | Habana Labs Ltd. | Matrix multiplication engine |

| US10528321B2 (en) * | 2016-12-07 | 2020-01-07 | Microsoft Technology Licensing, Llc | Block floating point for neural network implementations |

| US10228937B2 (en) * | 2016-12-30 | 2019-03-12 | Intel Corporation | Programmable matrix processing engine |

| JP6907700B2 (ja) * | 2017-05-23 | 2021-07-21 | 富士通株式会社 | 情報処理装置、マルチスレッド行列演算方法、およびマルチスレッド行列演算プログラム |

| US10795677B2 (en) | 2017-09-29 | 2020-10-06 | Intel Corporation | Systems, apparatuses, and methods for multiplication, negation, and accumulation of vector packed signed values |

| US10552154B2 (en) * | 2017-09-29 | 2020-02-04 | Intel Corporation | Apparatus and method for multiplication and accumulation of complex and real packed data elements |

| US11243765B2 (en) | 2017-09-29 | 2022-02-08 | Intel Corporation | Apparatus and method for scaling pre-scaled results of complex multiply-accumulate operations on packed real and imaginary data elements |

| US10534838B2 (en) | 2017-09-29 | 2020-01-14 | Intel Corporation | Bit matrix multiplication |

| US10664277B2 (en) | 2017-09-29 | 2020-05-26 | Intel Corporation | Systems, apparatuses and methods for dual complex by complex conjugate multiply of signed words |

| US10802826B2 (en) | 2017-09-29 | 2020-10-13 | Intel Corporation | Apparatus and method for performing dual signed and unsigned multiplication of packed data elements |

| US10514924B2 (en) | 2017-09-29 | 2019-12-24 | Intel Corporation | Apparatus and method for performing dual signed and unsigned multiplication of packed data elements |

| US11256504B2 (en) | 2017-09-29 | 2022-02-22 | Intel Corporation | Apparatus and method for complex by complex conjugate multiplication |

| US11074073B2 (en) | 2017-09-29 | 2021-07-27 | Intel Corporation | Apparatus and method for multiply, add/subtract, and accumulate of packed data elements |

| US10795676B2 (en) | 2017-09-29 | 2020-10-06 | Intel Corporation | Apparatus and method for multiplication and accumulation of complex and real packed data elements |

| US10346163B2 (en) * | 2017-11-01 | 2019-07-09 | Apple Inc. | Matrix computation engine |

| US11321092B1 (en) | 2017-11-08 | 2022-05-03 | Habana Labs Ltd. | Tensor-based memory access |

| US10915297B1 (en) * | 2017-11-15 | 2021-02-09 | Habana Labs Ltd. | Hardware accelerator for systolic matrix multiplication |

| US10970078B2 (en) | 2018-04-05 | 2021-04-06 | Apple Inc. | Computation engine with upsize/interleave and downsize/deinterleave options |

| US10642620B2 (en) | 2018-04-05 | 2020-05-05 | Apple Inc. | Computation engine with strided dot product |

| US11250106B2 (en) * | 2018-05-18 | 2022-02-15 | Dmitri Pescianschi | Memory device and matrix processing unit utilizing the memory device |

| US10754649B2 (en) | 2018-07-24 | 2020-08-25 | Apple Inc. | Computation engine that operates in matrix and vector modes |

| WO2020032998A1 (en) | 2018-08-06 | 2020-02-13 | Hi Llc | Systems and methods to reduce data and complexity in neural signal processing chain |

| US10831488B1 (en) | 2018-08-20 | 2020-11-10 | Apple Inc. | Computation engine with extract instructions to minimize memory access |

| US12124530B2 (en) | 2019-03-11 | 2024-10-22 | Untether Ai Corporation | Computational memory |

| EP3938921A4 (en) * | 2019-03-11 | 2022-12-14 | Untether AI Corporation | CALCULATION MEMORY |

| US10884707B1 (en) * | 2019-06-27 | 2021-01-05 | Amazon Technologies, Inc. | Transpose operations using processing element array |

| US11947959B2 (en) * | 2019-09-10 | 2024-04-02 | Micron Technology, Inc. | Re-using processing elements of an artificial intelligence processor |

| US11342944B2 (en) | 2019-09-23 | 2022-05-24 | Untether Ai Corporation | Computational memory with zero disable and error detection |

| CN111242293B (zh) * | 2020-01-13 | 2023-07-18 | 腾讯科技(深圳)有限公司 | 一种处理部件、数据处理的方法以及电子设备 |

| US11468002B2 (en) | 2020-02-28 | 2022-10-11 | Untether Ai Corporation | Computational memory with cooperation among rows of processing elements and memory thereof |

| CN111401522B (zh) * | 2020-03-12 | 2023-08-15 | 上海交通大学 | 脉动阵列变速控制方法及可变速脉动阵列微框架系统 |

| CN113867788A (zh) * | 2020-06-30 | 2021-12-31 | 上海寒武纪信息科技有限公司 | 一种计算装置、芯片、板卡、电子设备和计算方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60127598A (ja) * | 1983-12-14 | 1985-07-08 | Toshiba Corp | 半導体集積回路装置 |

| JPH05151249A (ja) | 1991-11-28 | 1993-06-18 | Fujitsu Ltd | 複素数乗算器 |

| JPH05182464A (ja) | 1991-06-25 | 1993-07-23 | Fujitsu Ltd | 半導体記憶装置 |

| JPH08322299A (ja) * | 1995-05-22 | 1996-12-03 | Mitsutoyo Corp | モータのベクトル制御方式 |

| WO1999000746A1 (fr) * | 1997-06-26 | 1999-01-07 | Asahi Kasei Kogyo Kabushiki Kaisha | Unites arithmetiques paralleles et processeur de signaux numeriques utilisant lesdites unites |

| JP2001056808A (ja) * | 1999-06-10 | 2001-02-27 | Lucent Technol Inc | 行列計算を行うためのプロセッサ素子のパイプライン処理線形アレー |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4354249A (en) * | 1980-03-24 | 1982-10-12 | Motorola Inc. | Processing unit for multiplying two mathematical quantities including at least one complex multiplier |

| US5195050A (en) * | 1990-08-20 | 1993-03-16 | Eastman Kodak Company | Single chip, mode switchable, matrix multiplier and convolver suitable for color image processing |

| US6002880A (en) * | 1992-12-29 | 1999-12-14 | Philips Electronics North America Corporation | VLIW processor with less instruction issue slots than functional units |

| US5983253A (en) * | 1995-09-05 | 1999-11-09 | Intel Corporation | Computer system for performing complex digital filters |

| US5764943A (en) * | 1995-12-28 | 1998-06-09 | Intel Corporation | Data path circuitry for processor having multiple instruction pipelines |

| US6038583A (en) * | 1997-10-23 | 2000-03-14 | Advanced Micro Devices, Inc. | Method and apparatus for simultaneously multiplying two or more independent pairs of operands and calculating a rounded products |

| US6411979B1 (en) * | 1999-06-14 | 2002-06-25 | Agere Systems Guardian Corp. | Complex number multiplier circuit |

-

2000

- 2000-04-21 US US09/556,760 patent/US6675187B1/en not_active Expired - Lifetime

- 2000-06-09 JP JP2000174354A patent/JP4422299B2/ja not_active Expired - Fee Related

-

2009

- 2009-10-08 JP JP2009234277A patent/JP5491122B2/ja not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60127598A (ja) * | 1983-12-14 | 1985-07-08 | Toshiba Corp | 半導体集積回路装置 |

| JPH05182464A (ja) | 1991-06-25 | 1993-07-23 | Fujitsu Ltd | 半導体記憶装置 |

| JPH05151249A (ja) | 1991-11-28 | 1993-06-18 | Fujitsu Ltd | 複素数乗算器 |

| JPH08322299A (ja) * | 1995-05-22 | 1996-12-03 | Mitsutoyo Corp | モータのベクトル制御方式 |

| WO1999000746A1 (fr) * | 1997-06-26 | 1999-01-07 | Asahi Kasei Kogyo Kabushiki Kaisha | Unites arithmetiques paralleles et processeur de signaux numeriques utilisant lesdites unites |

| JP2001056808A (ja) * | 1999-06-10 | 2001-02-27 | Lucent Technol Inc | 行列計算を行うためのプロセッサ素子のパイプライン処理線形アレー |

Non-Patent Citations (8)

| Title |

|---|

| CSNG200000540020; 藤岡与周 外2名: '再構成可能並列プロセッサと知能ロボット制御への応用' 日本ロボット学会誌 第13巻、第6号, 19950915, p.112-119, 社団法人日本ロボット学会 * |

| CSNG200001105001; 酒井英昭・他: '「適応フィルタとVLSI実現」' システム/制御/情報(システム制御情報学会誌) 第38巻、第8号, 19940815, 第1〜6頁, システム制御情報学会 * |

| CSNG200201230003; 渋沢進: '「時空間適応処理のための並列QR分解の方法について」' 電子情報通信学会技術研究報告 第97巻、第375号, 19971114, 第17〜24頁, 社団法人電子情報通信学会 * |

| CSNJ199800014001; 北原直紀・他: '「CORDICプロセッサを用いた超複素数乗算器」' 1998年電子情報通信学会総合大会講演論文集 分冊:基礎・境界, 19980306, 第135頁, 社団法人電子情報通信学会 * |

| JPN6009016070; 北原直紀・他: '「CORDICプロセッサを用いた超複素数乗算器」' 1998年電子情報通信学会総合大会講演論文集 分冊:基礎・境界, 19980306, 第135頁, 社団法人電子情報通信学会 * |

| JPN6009016073; 渋沢進: '「時空間適応処理のための並列QR分解の方法について」' 電子情報通信学会技術研究報告 第97巻、第375号, 19971114, 第17〜24頁, 社団法人電子情報通信学会 * |

| JPN6009016079; 酒井英昭・他: '「適応フィルタとVLSI実現」' システム/制御/情報(システム制御情報学会誌) 第38巻、第8号, 19940815, 第1〜6頁, システム制御情報学会 * |

| JPN6013031398; 藤岡与周 外2名: '再構成可能並列プロセッサと知能ロボット制御への応用' 日本ロボット学会誌 第13巻、第6号, 19950915, p.112-119, 社団法人日本ロボット学会 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001056808A (ja) | 2001-02-27 |

| JP4422299B2 (ja) | 2010-02-24 |

| JP5491122B2 (ja) | 2014-05-14 |

| US6675187B1 (en) | 2004-01-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5491122B2 (ja) | 行列計算を行うためのプロセッサ素子のパイプライン処理線形アレー | |

| TW405093B (en) | Data processor and data processing system | |

| US5784636A (en) | Reconfigurable computer architecture for use in signal processing applications | |

| US9792118B2 (en) | Vector processing engines (VPEs) employing a tapped-delay line(s) for providing precision filter vector processing operations with reduced sample re-fetching and power consumption, and related vector processor systems and methods | |

| JP4980834B2 (ja) | 算術プロセッサ | |

| CN110383237B (zh) | 可重新配置的矩阵乘法器系统和方法 | |

| US9977676B2 (en) | Vector processing engines (VPEs) employing reordering circuitry in data flow paths between execution units and vector data memory to provide in-flight reordering of output vector data stored to vector data memory, and related vector processor systems and methods | |

| Ebeling et al. | RaPiD—Reconfigurable pipelined datapath | |

| US9684509B2 (en) | Vector processing engines (VPEs) employing merging circuitry in data flow paths between execution units and vector data memory to provide in-flight merging of output vector data stored to vector data memory, and related vector processing instructions, systems, and methods | |

| US7124160B2 (en) | Processing architecture having parallel arithmetic capability | |

| JP4555356B2 (ja) | 単一命令複数データ(simd)命令用の積和演算(mac)ユニット | |

| CN111353126A (zh) | 分块矩阵乘法运算系统 | |

| JP2018055677A (ja) | 外積累算演算のためのプロセッサおよび方法 | |

| KR20160084460A (ko) | 상관 벡터 프로세싱 연산들을 위해 탭핑-지연 라인을 이용하는 벡터 프로세싱 엔진, 및 관련된 벡터 프로세서 시스템들 및 방법들 | |

| EP0497772A4 (en) | High performance, low cost microprocessor | |

| KR20160085336A (ko) | 실행 유닛들과 벡터 데이터 메모리 사이의 데이터 흐름 경로들에서 역확산 회로를 이용하는 벡터 프로세싱 엔진, 및 관련된 방법 | |

| US20230177320A1 (en) | Neural network accelerator with a configurable pipeline | |

| US20190004794A1 (en) | Matrix multiplication at memory bandwidth | |

| JPS6125188B2 (ja) | ||

| Ebeling et al. | Configurable computing: The catalyst for high-performance architectures | |

| US6675286B1 (en) | Multimedia instruction set for wide data paths | |

| Chalamalasetti et al. | MORA-an architecture and programming model for a resource efficient coarse grained reconfigurable processor | |

| Managuli et al. | Mapping of two-dimensional convolution on very long instruction word media processors for real-time performance | |

| KR100722428B1 (ko) | 리소스 공유 및 파이프 라이닝 구성을 갖는 재구성가능배열구조 | |

| EP3232321A1 (en) | Signal processing apparatus with register file having dual two-dimensional register banks |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100705 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20101005 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20101008 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110105 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20110105 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110831 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20120924 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130927 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20131002 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131226 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140227 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5491122 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |