JP2010049399A - 回路図設計装置、回路図設計プログラム及び回路図設計方法 - Google Patents

回路図設計装置、回路図設計プログラム及び回路図設計方法 Download PDFInfo

- Publication number

- JP2010049399A JP2010049399A JP2008211735A JP2008211735A JP2010049399A JP 2010049399 A JP2010049399 A JP 2010049399A JP 2008211735 A JP2008211735 A JP 2008211735A JP 2008211735 A JP2008211735 A JP 2008211735A JP 2010049399 A JP2010049399 A JP 2010049399A

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- symbol

- connection relation

- circuit diagram

- parameter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000010586 diagram Methods 0.000 title claims abstract description 220

- 238000000034 method Methods 0.000 title claims abstract description 158

- 238000013461 design Methods 0.000 title claims abstract description 70

- 239000004065 semiconductor Substances 0.000 claims abstract description 34

- 230000015572 biosynthetic process Effects 0.000 claims description 55

- 238000005755 formation reaction Methods 0.000 claims description 55

- 238000007667 floating Methods 0.000 claims description 10

- 239000003086 colorant Substances 0.000 claims description 2

- 230000008569 process Effects 0.000 description 121

- 238000012545 processing Methods 0.000 description 21

- 230000006870 function Effects 0.000 description 13

- 238000009751 slip forming Methods 0.000 description 9

- 230000000694 effects Effects 0.000 description 5

- 239000003990 capacitor Substances 0.000 description 4

- 230000004044 response Effects 0.000 description 4

- 230000008859 change Effects 0.000 description 3

- 238000004590 computer program Methods 0.000 description 3

- 238000012937 correction Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 238000012795 verification Methods 0.000 description 2

- 238000004891 communication Methods 0.000 description 1

- 238000012938 design process Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Landscapes

- Design And Manufacture Of Integrated Circuits (AREA)

Abstract

【解決手段】 回路図設計装置100を、レイアウトされた回路図や選択画面から回路記号を選択する回路記号選択部12と、表示情報に基づき回路図の表示制御を行う回路図表示制御部16と、パラメータ設定可能な回路記号に対してマルチ素子回路を生成するためのパラメータを設定するパラメータ設定部18と、予め設定されたルールと回路記号に対して設定されたパラメータとに基づきマルチ素子回路の接続関係情報を生成する接続関係情報生成部20と、予め設定された表示方法のルールに基づきマルチ素子回路の回路記号の表示情報を生成する回路表示情報生成部22とを含んだ構成とした。

【選択図】 図1

Description

一方、回路記号選択手段によって、例えば、選択画面に表示された回路記号のうち、所定の回路記号としてパラメータが設定可能な回路記号、又はレイアウト領域にレイアウトされた回路記号のうち所定の回路記号としてパラメータが設定可能な回路記号が選択されると、パラメータ設定手段によって、選択された所定の回路記号に対して、回路素子の連続形成数及びダミー素子の形成数を含むマルチ素子回路を生成するためのパラメータが設定される。パラメータが設定されると、接続関係情報生成手段によって、設定されたパラメータに基づき、設定された連続形成数の回路素子から構成される本体部分と、該本体部分に接続される設定された形成数のダミー素子とを含んで構成されるマルチ素子回路の各回路素子の接続関係を示す接続関係情報が生成される。

従って、半導体基板(半導体ウェーハ)に形成される、能動素子(例えば、ダイオード、トランジスタなど)や、受動素子(例えば、抵抗、キャパシタ、インダクタなど)などの回路素子を、同じ回路素子同士で複数を連続接続(例えば、各回路素子の一部を他と共有させてひと繋がりに形成)した構成のマルチ素子回路含む半導体集積回路を設計(作成)するときに、例えば、手作業で同じ回路記号を1つずつ選択して形成することなく、選択した回路記号に対して連続形成数をパラメータ設定するだけで、該回路記号の回路素子を連続接続した構成のマルチ素子回路を生成することができる。更に、このマルチ素子回路において、例えば、該マルチ素子回路を構成する回路素子の一部の形状の違いなどから生じる回路素子特性のバラツキを低減するためのダミー素子についても、選択した回路記号に対してダミー素子の形成数をパラメータ設定するだけで、手作業でダミー素子の回路記号を1つずつ選択して形成することなく、連続接続された回路素子にダミー素子が付加接続された構成のマルチ素子回路を生成することができる。

また、回路素子のマルチ数やダミー素子の数をパラメータで管理することができるので、レイアウト検証(LVS)を、より確実に行うことができるという効果が得られる。

また、上記半導体集積回路に係る回路図は、例えば、上記JISに準拠した回路記号で表された回路図や、セル、ブロックなどで表されたマスクパターンのレイアウト図であるパターンレイアウト図などが該当する。以下、発明6の回路図設計プログラム、発明7の回路図設計方法において同じである。

更に、複数の回路素子を連続形成したときに、各回路素子の形状などの違いによって生じる回路特性のバラツキを低減するために、例えば、連続形成部分の両端にダミー素子として同じ回路素子を付加する。以下、発明6の回路図設計プログラム、発明7の回路図設計方法において同じである。

このような構成であれば、JISに準拠する回路記号をレイアウト領域にレイアウトして構成された回路図に対して、回路図表示手段によって、接続関係情報に基づき、パターレイアウト図を表示するための表示情報を生成し、該生成した表示情報に基づきパターンレイアウト図を表示することができる。

このような構成であれば、利用者は、表示された回路記号の色から、ダミー素子を含むマルチ素子回路が形成されていか否かを視覚的に容易に判断することができるという効果が得られる。

前記接続関係情報に基づき、前記回路記号及び前記配線パターンを含んで構成される回路図を表示する回路図表示手段として機能させるためのプログラムを含み、前記接続関係情報生成手段は、前記回路記号選択手段で選択された前記所定の回路記号に対して前記パラメータが設定されたときに、該設定されたパラメータに基づき、前記一繋がりに形成される本体部分と、該本体部分に接続される前記形成数分のダミー素子とを含んで構成されるマルチ素子回路の各回路素子の接続関係を示す接続関係情報を生成する。

このような構成であれば、上記発明1に記載の回路図設計装置と同等の作用及び効果が得られる。

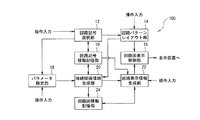

まず、本発明に係る回路図設計装置の機能構成を図1に基づき説明する。図1は、本発明に係る回路図設計装置100の機能構成を示すブロック図である。

回路図設計装置100は、図1に示すように、回路記号情報記憶部10と、回路記号選択部12と、回路パターンレイアウト部14と、回路図表示制御部16とを含んで構成される。

回路記号選択部12は、マウス、キーボード、タブレットなどの入力装置を介した利用者からの操作入力に応じて、回路素子の情報選択画面や、回路記号の選択画面を表示装置の表示画面上に画像表示すると共に、画像表示された複数種類の回路記号の中から操作入力に応じた回路記号を選択する機能を有している。更に、操作入力に応じて、既にレイアウトされた回路記号や配線パターンなどの回路の任意の構成要素を選択する機能も有している。

回路図表示制御部16は、回路表示情報生成部22から入力される表示情報に基づき、表示装置の表示画面上に、回路記号から構成される回路図を表示したり、マスクパターンのレイアウトを示すパターンレイアウト図を表示したり、警告メッセージを表示したりする機能を有している。

パラメータ設定部18は、ダイオード、トランジスタなどの能動素子、抵抗、キャパシタンス(コンデンサ)、インダクタンス(コイル)などの受動素子に対応する回路記号を選択したときに、選択した回路記号がマルチ素子回路を構成可能な場合に、入力装置を介した利用者からの操作入力に応じて、選択した回路記号に対して、各種パラメータを設定する機能を有している。

例えば、回路素子がMOSトランジスタの場合は、Nチャンネル型のMOSトランジスタ(NMOS)又はPチャンネル型のMOSトランジスタ(PMOS)の連続形成数(Multi=<Multi>)と、チャンネルサイズ(W(チャンネル幅)/L(チャンネル長)=<W>/<L>)と、該NMOS又はPMOSと同じ回路素子のダミーMOSの本体部分の端部ドレイン側への形成数(DDM=<DDM>)と、ダミーMOSの本体部分の端部ソース側への形成数(SDM=<SDM>)などがパラメータとして設定できる。

本実施の形態において、パラメータ設定が可能なNMOSの回路記号は、図2の左図に示すように、JISで標準化されているNMOSの回路記号の各端子部の傍に端子名G(Gate)、D(Drain)、S(Source)がそれぞれ表示され、更に、D端子の右側にパラメータ名「DDM(ドレイン側形成数)=<DDM>」と、S端子の右側にパラメータ名「SDM(ソース側形成数)=<SDM>」と、DDMとSDMの上下間に、パラメータ名「W(チャンネル幅)/L(チャンネル長)=<W>/<L>」と、パラメータ名「Multi(連続形成数)=<Multi>」とが表示されたものとなる。これらパラメータDDM、SDM、Multi、W/Lにそれぞれ任意の数値を設定することで、マルチ素子回路を生成するためのパラメータ設定が行われる。

例えば、NMOSの回路記号に対してパラメータ設定をした場合のマルチ素子回路を示す回路記号は、図2の左図に示すように、本体NMOSの回路記号に対して、そのドレイン端子にダミーNMOSが接続されていることを示す■記号と、そのソース端子にダミーNMOSが接続されていることを示す■記号とが付加された記号が表示装置の表示画面上に表示される。

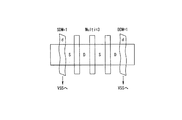

ここで、図3は、NMOSで構成されたマルチ素子回路のレイアウトパターン図の一例を示す図である。

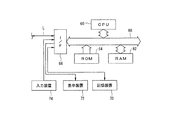

ここで、回路図設計装置100は、半導体集積回路に係る回路図の設計のための各種制御や前記回路記号選択部12、回路パターンレイアウト部14、回路図表示制御部16、パラメータ設定部18、接続関係情報生成部20、回路表示情報生成部22などの各機能をソフトウェア上で、すなわち専用のプログラムを実行することで実現するためのコンピュータシステムを備えており、そのハードウェア構成は、図4に示すように、各種制御や演算処理を担う中央演算処理装置であるCPU(Central Processing Unit)60と、主記憶装置(Main Storage)を構成するRAM(Random Access Memory)62と、読み出し専用の記憶装置であるROM(Read Only Memory)64とを含み、これらの間をPCI(Peripheral Component Interconnect)バス等からなる各種内外バス68で接続すると共に、このバス68に入出力インターフェース(I/F)66を介して、HDD(Hard Disk Drive)などの記憶装置(Secondary Storage)70や、LCDモニター等の表示装置72、マウス、キーボード、タブレットなどの入力装置74などを接続した構成となっている。

ここで、図5は、回路記号のレイアウト処理及び接続関係情報の生成処理を示すフローチャートである。

CPU60によって、専用のコンピュータプログラムの実行が開始されると、図5に示すように、まず、ステップS100に移行し、回路記号選択部12において、入力装置74を介した利用者からの操作入力に基づき、回路記号の選択画面又はレイアウト領域にレイアウト(表示)された回路図から、回路記号が選択されたか否かを判定し、選択されたと判定した場合(Yes)は、ステップS102に移行し、そうでない場合(No)は、選択されるまで判定処理を繰り返す。

ステップS104に移行した場合は、パラメータ設定部18において、入力装置74を介した利用者からの操作入力に基づき、選択された回路記号に対してパラメータの入力指示があったか否かを判定し、入力指示があったと判定した場合(Yes)は、ステップS106に移行し、そうでない場合(No)は、ステップS100に移行する。

このパラメータの入力画面は、例えば、選択された回路記号がMOSトランジスタであれば、本体MOSのマルチ数(連続形成数)、ダミーMOSのマルチ数(形成数)、各MOSのチャンネルサイズなどのパラメータ設定項目と、各項目に対する数値入力用のボックスとが表示された画面となる。

ステップS110に移行した場合は、接続関係情報生成部20において、入力値判定処理を実行して、ステップS112に移行する。

ステップS114に移行した場合は、接続関係情報生成部20において、選択された回路記号に対して設定されたパラメータに基づき、該回路記号の回路素子によって構成されるマルチ素子回路の接続関係情報を生成して、ステップS116に移行する。

ステップS118では、回路表示情報生成部22において、ステップS114で生成された接続関係情報と、ステップS116で決定された表示方法とに基づき、マルチ素子回路を示す回路記号の表示情報を生成し、これを表示要求と共に回路図表示制御部16に出力して、ステップS120に移行する。

なお、本実施の形態においては、回路表示情報生成部22に対して、選択した回路記号に対するマルチ素子回路を示すパターンレイアウト図の表示指示を行うことができる。この表示指示を行うことによって、回路表示情報生成部22は、ステップS114で生成された接続関係情報と、ステップS116で決定された表示方法とに基づき、マルチ素子回路のパターンレイアウト図の表示情報を生成し、回路図表示制御部16は、この表示情報に基づき、レイアウト領域内又は別ウィンドウにマルチ素子回路のパターンレイアウト図を表示する。

次に、図6に基づき、回路図設計装置100の接続関係情報生成部20におけるステップS110の入力値判定処理の流れを説明する。

ステップS110に移行し、入力値判定処理が開始されると、図6に示すように、まず、ステップS200に移行し、接続関係情報生成部20において、パラメータ「SDM」の値は「0」か否かを判定し、「0」であると判定した場合(Yes)は、ステップS202に移行し、そうでない場合(No)は、ステップS204に移行する。

一方、ステップS204に移行した場合は、接続関係情報生成部20において、パラメータ「SDM」の値は正の整数か否かを判定し、正の整数であると判定した場合(Yes)は、ステップS206に移行し、そうでない場合(No)は、ステップS214に移行する。

ステップS208に移行した場合は、接続関係情報生成部20において、パラメータ「SDM」の値は、「1」又は「2」か否かを判定し、「1」又は「2」であると判定した場合(Yes)は、ステップS202に移行し、そうでない場合(No)は、ステップS214に移行する。この場合は、本体MOS部の両端がソースとなっているため、「SDM」の値が「1」であれば、両端のソースのいずれか一方にダミーMOSが付加され、「2」であれば、両端のソースに1つずつダミーMOSが付加されることになる。

ここで「SDM」が「1」ではない場合は、「SDM」の値が「2」以上となっている。また、本体MOS部の片側がソース、他方の側がドレインとなっており、本実施の形態においては、ダミーMOSは、最大でも本体MOS部の両端に1つずつというルールが予め定められているため、妥当な値では無いと判定する。なお、両端に1つとする構成に限定する必要は無い。

一方、ステップS214に移行した場合は、接続関係情報生成部20において、入力された値は妥当ではないと判定して、一連の処理を終了し元の処理に復帰する。

ここで、図7は、接続関係情報生成部20における、MOSトランジスタに対する接続関係情報生成処理を示すフローチャートである。

ステップS304では、接続関係情報生成部20において、生成した接続関係情報を、回路表示情報生成部22に出力すると共に回路図情報記憶部24に保存して、一連の処理を終了し元の処理に復帰する。

ステップS308に移行した場合は、接続関係情報生成部20において、パラメータ「Multi」の値「M」に基づき、ダミーPMOSを付加していない状態の、M個のPMOSが連続して接続された構成の本体PMOS部分だけのマルチ素子回路の接続関係情報を生成してRAM62に記憶し、ステップS310に移行する。

ステップS312に移行した場合は、接続関係情報生成部20において、「DDM」の値に基づき、本体PMOS部分のドレイン端部にダミーPMOSを接続する情報を、RAM62に記憶された接続関係情報に追加して、ステップS314に移行する。

ステップS316に移行した場合は、接続関係情報生成部20において、本体PMOS部分のソース端部にダミーPMOSを接続する情報を、RAM62に記憶された接続関係情報に追加して、ステップS318に移行する。

ステップS320では、接続関係情報生成部20において、ダミーPMOS又はダミーNMOSの接続されていない端子をフローティングにする情報を、RAM62に記憶された接続関係情報に追加して、ステップS304に移行する。

ステップS326に移行した場合は、接続関係情報生成部20において、「DDM」の値に基づき、本体NMOS部分のドレイン端部にダミーNMOSを接続する情報を、RAM62に記憶された接続関係情報に追加して、ステップS328に移行する。

ステップS330に移行した場合は、接続関係情報生成部20において、本体NMOS部分のソース端部にダミーNMOSを接続する情報を、RAM62に記憶された接続関係情報に追加して、ステップS332に移行する。

なお、上記生成されたマルチ素子回路の接続関係情報は、最終的に、レイアウト領域にレイアウトされた回路全体の接続関係情報における、対応する回路記号に対応付けられて回路図情報記憶部24に保存されるか、回路全体の接続関係情報における、対応する回路記号の接続関係情報を置き換えて回路図情報記憶部24に保存される。

ここで、図8は、回路表示情報生成部22における表示方法決定処理を示すフローチャートである。

ステップS402に移行した場合は、回路表示情報生成部22において、表示形状に関するルールに基づきマルチ素子回路の回路記号の表示形状を決定して、ステップS404に移行する。

ステップS406に移行した場合は、回路表示情報生成部22において、表示色に関するルールに基づき、マルチ素子回路の回路記号の表示色を決定して、一連の処理を終了し元の処理に復帰する。

ここで、図9(a)は、NMOSの回路記号の一例を示す図であり、(b)は、(a)の回路記号に対するパラメータ入力画面の一例を示す図であり、(c)は、「ROW」の値を「2」にしたときのマルチ素子回路のパターンレイアウト図の一例を示す図である。また、図10(a)〜(d)は、パラメータ設定が可能な回路記号の表示形状の例を示す図である。また、図11(a)は、パラメータ設定が可能なPMOSの回路記号の一例を示す図であり、(b)は、(a)の回路記号に対するマルチ素子回路の回路構成の一例を示す図である。

いま、入力装置74を介して利用者からの、既に作成された接続関係情報に対する回路図の表示指示があったとする。回路表示情報生成部22は、表示指示(接続関係情報の指定及び表示形式の指定を含む)に応じて、回路図情報記憶部24から、指定された接続関係情報を読み出し、指示に応じた表示形態の回路図(回路記号で表された回路図、又はレイアウトパターン図)の表示情報を生成する。

ここでは、MOSトランジスタの回路記号を含む複数種類の回路記号及び配線パターンによって表された回路図が表示されたとする。

ここで、NMOSの回路記号は、図9(a)に示すように、NMOS本体部0800と、第1〜第4パラメータ表示領域0804〜0807とを含んで構成されている。

第1のパラメータ表示領域0804は、NMOS本体部のドレインに付加するダミーNMOSの数を示すパラメータ情報「DDM=<DDM>」を表示する領域であり、第4パラメータ表示領域0807は、NMOS本体部のソースに付加するダミーNMOSの数を示すパラメータ情報「SDM=<SDM>」を表示する領域である。ここで、<DDM>、<SDM>には入力装置74を介して入力された数値が入る。

NMOSの回路記号の場合に、パラメータ項目0821は、チャンネル幅「W」、同0822はチャンネル長「L」、同0823は、NMOS本体部の連続形成数「Multi」、同0824は、ドレイン側のダミーNMOSの形成数「DDM」、同0825は、ソース側のダミーNMOSの形成数「SDM」、同0826は、NMOSの段数「ROW」となる。

以下、説明の便宜上、「ROW」の値を「1」に固定して説明を行う。

そして、パラメータ値入力ボックス0831は、チャンネル幅の入力ボックス、同0832は、チャンネル長の入力ボックス、同0833は、NMOS本体部の連続形成数の入力ボックス、同0834は、ドレイン側のダミーNMOSの形成数の入力ボックス、同0835は、ソース側のダミーNMOSの形成数の入力ボックス、同0836は、NMOSの段数の入力ボックスとなる。

このようにして、パラメータ入力画面において、入力装置74を介して、各パラメータを入力し、該入力処理が全て完了すると(ステップS108の「Yes」の分岐)、次に、接続関係情報生成部20において、入力されたパラメータ値におけるダミーNMOSの入力値が妥当であるか否かを判定する入力値判定処理を実行する(ステップS110)。

具体的に、「SDM」の入力値が「0」のとき、「Multi」の入力ボックス0833の入力値が「2の倍数」であり「DDM」の入力値が1以上であるときは、本体NMOS部の両端が両方ともドレインとなるので、このときは、DDMの入力値が「1」〜「2」であれば妥当な値であると判定され、「0」以下の値や「3」以上の値であるときは、妥当な値ではないと判定される。更に、入力値「Multi」の値が奇数のときは、必ず本体NMOS部の一端がソースに他端がドレインとなるので、このときは、DDMの入力値が「1」のときは妥当な値であると判定され、それ以外の数値であるときは妥当な値ではないと判定される。ここでは、「Multi」の入力値が「6」で、「DDM」の入力値が「3」となっているので、妥当な値ではないと判定される。

従って、パラメータの入力値が妥当ではないため、マルチ素子回路を形成するためには入力値を修正する必要がある。

本体NMOS部の連続形成数が「5」の場合は奇数となるので、本体NMOS部の一端がドレインに他端がソースとなる(ステップS210の「No」の分岐)。更に、「SDM」の入力値が「1」(ステップS212の「Yes」の分岐)で、且つ「DDM」の入力値が「1」となるので、これら入力値は両方とも妥当な値であると判定される(ステップS112の「Yes」の分岐)。

接続関係情報生成処理が実行されると、まず、「DDM」の入力ボックス0834の入力値が「0」で、且つ「SDM」の入力ボックス0835の入力値が「0」か否かを判定する。先ほどの修正によって、「DDM」及び「SDM」の値は共に「1」となっているので(ステップS300の「No」の分岐)、次に、選択したMOSトランジスタがPMOSか否かを判定する(ステップS306)。ここでは、選択した回路記号はNMOSの回路記号であるので(ステップS306の「No」の分岐)、接続関係情報生成部20は、まず、ダミーNMOS無しのマルチ素子回路の接続関係情報を生成し、該生成した接続関係情報をRAM62に記憶する(ステップS322)。更に、「DDM」の値が「1」であるので(ステップS324の「Yes」の分岐)、RAM62に記憶された接続関係情報に、本体NMOS部の端部ドレイン側(以下、ドレイン端部と称す)にダミーNMOSを1つ接続する情報を追加する(ステップS326)。次に、「SDM」の値は「1」であるので(ステップS328の「Yes」の分岐)、RAM62に記憶された接続関係情報に、本体NMOS部の端部ソース側(以下、ソース端部と称す)にダミーNMOSを1つ接続する情報を追加する(ステップS330)。更に、RAM62に記憶された接続関係情報に、本体NMOS部のドレイン端部及びソース端部に接続したダミーNMOSのゲート端子を接地端子(VSS)に接続する情報を追加する(ステップS332)。更にまた、RAM62に記憶された接続関係情報に、ダミーNMOSにおけるドレイン端部又はソース端部に接続されていない側のソース端子又はドレイン端子をフローティングにする情報を追加し(ステップS320)、追加後の接続関係情報を、回路表示情報生成部22に出力すると共に、回路図情報記憶部24に、元の接続関係情報に追加する形で保存する(ステップS304)。

表示方法決定処理が開始されると、まず、回路表示情報生成部22において、表示形状に関するルールがあるか否かを判定する(ステップS400)。ここでは、表示形状に関するルールがあることとし(ステップS400の「Yes」の分岐)、この表示形状のルールとパラメータの設定内容とに基づき、パラメータの設定されたNMOSの回路記号の表示形状を決定する(ステップS402)。

ここでは、「SDM」及び「DDM」の入力値が共に「1」となっているので、表示形状ルール4に従って、図10(d)に示す表示形状に決定される。

なお、本実施の形態においては、マルチ素子回路のパターンレイアウト図についても表示形状に関する表示形状ルールがあり、図3に示すように、ダミーNMOSのゲートの形状を本体NMOS部のゲートの形状と異なる形状にするルールがある。図3の例は、表示形状ルール4に対応した形状となる。このことは、PMOSについても同様である。

回路表示情報生成部22は、表示形状が決定すると、次に、NMOSの回路記号に対する表示色に関するルール、又はマルチ素子回路のレイアウトパターン図の表示色に関するルールがあるか否かを判定する(ステップS404)。

具体的に、表示色に関するルールとして、パラメータの設定されたNMOSの回路記号を黄色表示し、パラメータの設定されていない回路記号を緑色表示する表示色ルール1と、マルチ素子回路のレイアウトパターン図における、本体NMOS部のゲートを黄色表示し、ダミーNMOS部のゲートを紫色表示する表示色ルール2とが設定されているとする。

このようにして、表示方法が決定されると、次に、選択した回路記号に対するマルチ素子回路の回路記号を、決定された表示方法で表示する表示情報を生成し、この表示情報を表示要求と共に回路図表示制御部16に出力する(ステップS118)。

更に、この黄色表示された回路記号に対するマルチ素子回路のレイアウトパターン図の表示指示があった場合は、回路表示情報生成部22は、該回路記号に設定されたパラメータと上記表示形状ルール及び表示色ルール2とに基づき、レイアウトパターン図の表示方法を決定すると共に、該決定された表示方法と接続関係情報とに基づきレイアウトパターン図の表示情報を生成する。そして、該表示情報を表示要求と共に回路図表示制御部16に出力する。

これにより、NMOSのマルチ素子回路のレイアウトパターン図が表示装置の表示画面に表示される。

ここで、PMOSの回路記号は、図11(a)に示すように、PMOS本体部1000と、第1〜第4パラメータ表示領域1004〜1007とを含んで構成されている。

第1のパラメータ表示領域1004は、PMOS本体部のソースに付加するダミーPMOSの数を示すパラメータ情報「SDM=<SDM>」を表示する領域であり、第4パラメータ表示領域1007は、PMOS本体部のドレインに付加するダミーPMOSの数を示すパラメータ情報「DDM=<DDM>」を表示する領域である。ここで、<SDM>、<DDM>には入力装置74を介して入力された数値が入る。

ここでは、NMOSと同様に、PMOSのパラメータ入力画面における「Multi」の入力ボックスの入力値を「5」に、「DDM」の入力ボックスの入力値を「1」に、「SDM」の入力ボックスの入力値を「1」に設定した場合の動作を説明する。

同様に、ダミーPMOSの回路記号1011、1021の回路部分の右横の1015、1025は、チャンネルサイズ(W/L)の情報であり、1014、1027は、連続形成数(Multi)の情報である。

以上、本実施の形態の回路図設計装置100は、マルチ素子回路を構成可能な回路素子に対して、回路素子の連続形成数やダミー素子の形成数などを含むパラメータを設定することで、その設定されたパラメータ値とそれに対応付けて予め設定されたルールとに基づき、付加的な回路素子(ダミー素子、電源端子、接地端子など)および配線パターンを含むマルチ素子回路の接続関係情報(ネットリスト)を生成することができる。

更に、表示方法のルールに従って、パラメータの設定された回路記号の表示形状及び表示色を、パラメータの設定されていない回路記号の表示形状及び表示色と異なる表示形状及び表示色で表示することができる。

更に、回路記号のパラメータの変更に伴い回路図上で表示される回路記号の形状および色が変わるため、その回路記号の表す回路構成を視覚的に確認でき、回路設計におけるミスを低減することができる。

上記実施の形態において、回路記号選択部12は、発明1、3、4、7及び8のいずれか1に記載の回路記号選択手段に対応し、パラメータ設定部18は、発明1、7及び8のいずれか1に記載のパラメータ設定手段に対応し、接続関係情報生成部20は、発明1、5、6、7及び8のいずれか1に記載の接続関係情報生成手段に対応し、回路図表示制御部16及び回路表示情報生成部22は、発明1、2、3、4、7及び8に記載の回路図表示手段に対応する。

また、上記実施の形態においては、パラメータの設定された(マルチ素子回路の生成された)回路記号を、表示形状及び表示色に関するルールに従って、パラメータの設定されていない回路記号とは異なる表示形状及び表示色で表示する構成としたが、これに限らず、表示形状及び表示色のいずれか一方のみをパラメータの設定されていない回路記号とは異なる表示形状及び表示色で表示する構成としてもよい。

また、上記実施の形態においては、マルチ素子回路に対応する回路記号の表示形状を、図10(a)〜(d)に示す形状とし、マルチ素子回路のパターンレイアウト図におけるダミーMOSのゲートの表示形状を、図3に示す形状としたが、これらに限らず、他の形状で表現するようにしてもよい。

10 回路記号情報記憶部

12 回路記号選択部

14 回路パターンレイアウト部

16 回路図表示制御部

18 パラメータ設定部

20 接続関係情報生成部

22 回路表示情報生成部

60 CPU

62 RAM

64 ROM

66 I/F

68 バス

70 記憶装置

72 表示装置

74 入力装置

Claims (8)

- 表示装置の画面上に表示されるレイアウト領域に、半導体集積回路を構成する各種回路素子に対応する回路記号と配線パターンとをレイアウトすることで、前記半導体集積回路に係る回路図を設計することが可能な回路図設計装置であって、

前記回路図の設計に係る所定の前記回路記号を選択する回路記号選択手段と、

前記回路記号選択手段で選択された前記所定の回路記号に対して、該回路記号の示す回路素子の連続形成数と、該連続形成数の回路素子を連続して一繋がりに形成することによって生じる回路素子特性のバラツキを低減するためのダミー素子の形成数とを含むパラメータを設定するパラメータ設定手段と、

前記レイアウト領域にレイアウトされた回路記号及び配線パターンの情報に基づき、前記レイアウトされた各回路記号の示す回路素子の接続関係を示す接続関係情報を生成する接続関係情報生成手段と、

前記接続関係情報に基づき、前記回路記号及び前記配線パターンを含んで構成される回路図を表示する回路図表示手段と、を備え、

前記接続関係情報生成手段は、前記回路記号選択手段で選択された前記所定の回路記号に対して前記パラメータが設定されたときに、該設定されたパラメータに基づき、前記一繋がりに形成される本体部分と、該本体部分に接続される前記形成数分のダミー素子とを含んで構成されるマルチ素子回路の各回路素子の接続関係を示す接続関係情報を生成することを特徴とする回路図設計装置。 - 前記回路図表示手段は、前記接続関係情報に基づき、前記半導体集積回路のマスクパターンのレイアウトを示すパターンレイアウト図を表示することを特徴とする請求項1に記載の回路図設計装置。

- 前記回路図表示手段は、前記回路記号選択手段で選択された回路記号に対して前記パラメータが設定されたときに、該パラメータの設定された回路記号を、前記パラメータの設定されていない回路記号とは異なる色で表示するようになっていることを特徴とする請求項1又は請求項2に記載の回路図設計装置。

- 前記回路図表示手段は、前記回路記号選択手段で選択された回路記号に対して前記パラメータが設定されたときに、該パラメータの設定された回路記号を、前記パラメータの設定されていない回路記号とは異なる形状の回路記号で表示するようになっていることを特徴とする請求項1乃至請求項3のいずれか1項に記載の回路図設計装置。

- 前記接続関係情報生成手段は、前記パラメータの設定された回路素子がMOSトランジスタであるときに、前記ダミー素子となるMOSトランジスタにおける、前記本体部分を構成するMOSトランジスタのソース又はドレインに接続されない方の端子をフローティングにする構成の接続関係情報を生成することを特徴とする請求項1乃至請求項4のいずれか1項に記載の回路図設計装置。

- 前記接続関係情報生成手段は、前記パラメータの設定された回路素子がPチャンネル型のMOSトランジスタであるときに、前記ダミー素子となるPチャンネル型のMOSトランジスタにおけるゲート端子を電源端子に接続する構成の接続関係情報を生成し、前記パラメータの設定された回路素子がNチャンネル型のMOSトランジスタであるときに、前記ダミー素子となるNチャンネル型のMOSトランジスタにおけるゲート端子を接地端子に接続する構成の接続関係情報を生成することを特徴とする請求項1乃至請求項5のいずれか1項に記載の回路図設計装置。

- 表示装置の画面上に表示されるレイアウト領域に、半導体集積回路を構成する各種回路素子に対応する回路記号と配線パターンとをレイアウトして、前記半導体集積回路に係る回路図を設計するために、コンピュータを、

前記回路図の設計に係る所定の前記回路記号を選択する回路記号選択手段、

前記回路記号選択手段で選択された前記所定の回路記号に対して、該回路記号の示す回路素子の連続形成数と、該連続形成数の回路素子を連続して一繋がりに形成することによって生じる回路素子特性のバラツキを低減するためのダミー素子の形成数とを含むパラメータを設定するパラメータ設定手段、

前記レイアウト領域にレイアウトされた回路記号及び配線パターンの情報に基づき、前記レイアウトされた各回路記号の示す回路素子の接続関係を示す接続関係情報を生成する接続関係情報生成手段、及び

前記接続関係情報に基づき、前記回路記号及び前記配線パターンを含んで構成される回路図を表示する回路図表示手段として機能させるためのプログラムを含み、

前記接続関係情報生成手段は、前記回路記号選択手段で選択された前記所定の回路記号に対して前記パラメータが設定されたときに、該設定されたパラメータに基づき、前記一繋がりに形成される本体部分と、該本体部分に接続される前記形成数分のダミー素子とを含んで構成されるマルチ素子回路の各回路素子の接続関係を示す接続関係情報を生成することを特徴とする回路図設計プログラム。 - 回路記号選択手段、パラメータ設定手段、接続関係情報生成手段及び回路図表示手段を備えた回路図設計装置を利用して、表示装置の画面上に表示されるレイアウト領域に、半導体集積回路を構成する各種回路素子に対応する回路記号と配線パターンとをレイアウトして、前記半導体集積回路に係る回路図を設計する回路図設計方法であって、

前記回路記号選択手段に、前記回路図の設計に係る所定の前記回路記号を選択させる回路記号選択ステップと、

前記パラメータ設定手段に、前記回路記号選択ステップで選択された前記所定の回路記号に対して、該回路記号の示す回路素子の連続形成数と、該連続形成数の回路素子を連続して一繋がりに形成することによって生じる回路素子特性のバラツキを低減するためのダミー素子の形成数とを含むパラメータを設定させるパラメータ設定ステップと、

前記接続関係情報生成手段に、前記レイアウト領域にレイアウトされた回路記号及び配線パターンの情報に基づき、前記レイアウトされた各回路記号の示す回路素子の接続関係を示す接続関係情報を生成させる接続関係情報生成ステップと、

前記回路図表示手段に、前記接続関係情報に基づき、前記回路記号及び前記配線パターンを含んで構成される回路図を表示させる回路図表示ステップとを含み、

前記接続関係情報生成ステップにおいて、前記回路記号選択ステップで選択された前記所定の回路記号に対して前記パラメータが設定されたときに、該設定されたパラメータに基づき、前記一繋がりに形成される本体部分と、該本体部分に接続される前記形成数分のダミー素子とを含んで構成されるマルチ素子回路の各回路素子の接続関係を示す接続関係情報を生成することを特徴とする回路図設計方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008211735A JP5276380B2 (ja) | 2008-08-20 | 2008-08-20 | 回路図設計装置、回路図設計プログラム及び回路図設計方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008211735A JP5276380B2 (ja) | 2008-08-20 | 2008-08-20 | 回路図設計装置、回路図設計プログラム及び回路図設計方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010049399A true JP2010049399A (ja) | 2010-03-04 |

| JP5276380B2 JP5276380B2 (ja) | 2013-08-28 |

Family

ID=42066443

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008211735A Expired - Fee Related JP5276380B2 (ja) | 2008-08-20 | 2008-08-20 | 回路図設計装置、回路図設計プログラム及び回路図設計方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5276380B2 (ja) |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000243841A (ja) * | 1999-02-19 | 2000-09-08 | Toshiba Corp | Cmos回路のパターンレイアウト |

| JP2005322827A (ja) * | 2004-05-11 | 2005-11-17 | Matsushita Electric Ind Co Ltd | 半導体集積回路の設計支援方法 |

| JP2005353905A (ja) * | 2004-06-11 | 2005-12-22 | Matsushita Electric Ind Co Ltd | 半導体装置およびそのレイアウト設計方法 |

| JP2007188188A (ja) * | 2006-01-11 | 2007-07-26 | Fujitsu Ltd | レイアウト方法、cad装置、プログラム及び記憶媒体 |

-

2008

- 2008-08-20 JP JP2008211735A patent/JP5276380B2/ja not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000243841A (ja) * | 1999-02-19 | 2000-09-08 | Toshiba Corp | Cmos回路のパターンレイアウト |

| JP2005322827A (ja) * | 2004-05-11 | 2005-11-17 | Matsushita Electric Ind Co Ltd | 半導体集積回路の設計支援方法 |

| JP2005353905A (ja) * | 2004-06-11 | 2005-12-22 | Matsushita Electric Ind Co Ltd | 半導体装置およびそのレイアウト設計方法 |

| JP2007188188A (ja) * | 2006-01-11 | 2007-07-26 | Fujitsu Ltd | レイアウト方法、cad装置、プログラム及び記憶媒体 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5276380B2 (ja) | 2013-08-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8434046B2 (en) | Method of fabricating an integrated circuit protected against reverse engineering | |

| US9928337B2 (en) | Integrated circuit and design method for same | |

| JP2001015602A (ja) | スタンダードセル、スタンダードセル列、スタンダードセルの配置配線装置および配置配線方法 | |

| US20140380256A1 (en) | Double patterning layout design method | |

| JP4580006B2 (ja) | 半導体集積回路のマスクレイアウト設計データの検証方法 | |

| US8312405B1 (en) | Method of placing input/output blocks on an integrated circuit device | |

| JP4220932B2 (ja) | 半導体集積回路の設計支援方法 | |

| US20070118825A1 (en) | Usage of a buildcode to specify layout characteristics | |

| JP5276380B2 (ja) | 回路図設計装置、回路図設計プログラム及び回路図設計方法 | |

| JP5276379B2 (ja) | 回路図設計装置、回路図設計プログラム及び回路図設計方法 | |

| US6629300B1 (en) | CAD system for an ASIC | |

| US8860191B2 (en) | On-chip transmission line structures with balanced phase delay | |

| JP3647803B2 (ja) | 集積回路解析方法、装置及びプログラム | |

| JP4668974B2 (ja) | 半導体装置の設計方法、半導体装置設計システム及びコンピュータプログラム | |

| JP4248925B2 (ja) | 自動フロアプラン決定方法 | |

| JP5650362B2 (ja) | 半導体集積回路の設計方法 | |

| JP4237611B2 (ja) | 半導体集積回路のレイアウト設計方法及びレイアウト設計装置 | |

| US12475292B2 (en) | Circuit layout generation system | |

| JP5407450B2 (ja) | 半導体集積回路の設計支援方法及び製造方法 | |

| TWI578177B (zh) | 用於積體電路製造的遮罩生成方法 | |

| JP2006173262A (ja) | 半導体集積回路のレイアウト設計方法及びシステム | |

| JP2010003965A (ja) | 集積回路装置のレイアウト設計方法及び製造方法並びに電子機器 | |

| JP2002151594A (ja) | 半導体集積回路の設計方法及び半導体集積回路の設計支援装置 | |

| JP3644413B2 (ja) | 素子及び配線の配置決定方法 | |

| JP2015210703A (ja) | Cad装置、セル、およびレイアウト方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110810 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120823 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120911 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121101 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130514 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130517 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5276380 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |