JP2010049398A - Circuit diagram-design device, circuit diagram-design program, and circuit diagram-design method - Google Patents

Circuit diagram-design device, circuit diagram-design program, and circuit diagram-design method Download PDFInfo

- Publication number

- JP2010049398A JP2010049398A JP2008211734A JP2008211734A JP2010049398A JP 2010049398 A JP2010049398 A JP 2010049398A JP 2008211734 A JP2008211734 A JP 2008211734A JP 2008211734 A JP2008211734 A JP 2008211734A JP 2010049398 A JP2010049398 A JP 2010049398A

- Authority

- JP

- Japan

- Prior art keywords

- parameter

- circuit

- value

- setting

- symbol

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Abstract

Description

本発明は、半導体集積回路のマスクパターンを生成するための回路図を設計する装置に係り、特に、MOSトランジスタなどの回路素子を共有部分を介して連続接続してなるマルチ素子回路を含む半導体集積回路に係る回路図を設計するのに好適な回路図設計装置、回路図設計プログラム及び回路図設計方法に関する。 The present invention relates to an apparatus for designing a circuit diagram for generating a mask pattern of a semiconductor integrated circuit, and in particular, a semiconductor integrated circuit including a multi-element circuit in which circuit elements such as MOS transistors are continuously connected through a shared portion. The present invention relates to a circuit diagram design apparatus, a circuit diagram design program, and a circuit diagram design method suitable for designing a circuit diagram related to a circuit.

半導体集積回路の微細化プロセス技術において、例えば、半導体ウェハに形成される回路素子の1つであるMOSトランジスタを複数、共有部分(ドレイン領域及びソース領域)を介して連続して接続した構成のマルチMOS回路の形成プロセスがある。このマルチMOS回路において、Vthが場所によって異なる現象が発生するという問題がある。この現象は、マルチMOS回路における連続接続されたMOSトランジスタの両端のゲートの形状と、その内側のMOSトランジスタのゲートの形状とが異なることが原因で生じることが判明している。図19に、そのイメージを示す(マルチ数=4のマルチMOS回路)。図19を見ると、両端のゲートの形状が内側のゲートの形状と異なっている様子が解る。この問題に対して、マルチMOS回路の両端にダミーMOSを付加する設計手法(図19の下図)が採用されている。この設計手法を用いることで、内側のMOSのマッチングが取れ、上記問題を回避することができる(例えば、特許文献1参照。)。 In the miniaturization process technology of a semiconductor integrated circuit, for example, a multi-structure having a configuration in which a plurality of MOS transistors, which are one of circuit elements formed on a semiconductor wafer, are continuously connected via a shared portion (drain region and source region). There is a process for forming a MOS circuit. In this multi-MOS circuit, there is a problem that a phenomenon in which V th varies depending on the location. It has been found that this phenomenon occurs due to the difference between the gate shapes of both ends of the MOS transistors connected continuously in the multi-MOS circuit and the gate shapes of the MOS transistors inside the MOS transistors. FIG. 19 shows an image thereof (multi-MOS circuit with multi-number = 4). Referring to FIG. 19, it can be seen that the shape of the gates at both ends is different from the shape of the inner gate. In order to solve this problem, a design method (lower diagram in FIG. 19) is adopted in which dummy MOSs are added to both ends of the multi-MOS circuit. By using this design method, the inner MOS can be matched and the above problem can be avoided (see, for example, Patent Document 1).

特許文献1の半導体装置は、中央部の内部セル領域を取り囲むように配線チャネル領域を設け、さらにその周囲を外部との信号の入出力等を行う回路配置されたI/Oセル領域が取り囲む構成の半導体装置において、内部セル領域の内部に設けられた多数のMOSトランジスタと寸法および配置密度がほぼ同一なダミーMOSトランジスタを配線チャネル領域に形成し、内部セル領域における辺縁部のMOSトランジスタの配置密度環境が、中央部のMOSトランジスタ群と等価になるようにして、製造時における拡散層パターンやゲートパターンの寸法ばらつきを防止するものである。

The semiconductor device of

図19の下図は、長破線で囲まれる部分が本体部、すなわち本来のMOSトランジスタの部分を示し、短破線で囲まれる部分がダミーとして付加されたMOSトランジスタ、すなわちダミーMOS部を示す。図19中の大文字のS、Dはそれぞれソース、ドレインを示し、小文字dで示した部分はダミーMOSのゲートを示し、S、Dに挟まれた何も無い縦長の長方形が本体部のゲートを示す。

しかしながら、上記従来の設計手法を採用した場合に、半導体集積回路に係る回路図を設計するCADや、半導体集積回路のマスクパターンを設計するCADなどを用いて、ダミーMOSを本体のMOSに1つずつ手入力で付加しなければならない。更に、ダミーMOSを1つ付加する毎に、付加した後のマルチMOS回路に対して、その検証(LVS:Layout Versus Schematic)を行わなくてはならない。そのため、設計者は、非効率で確実性の無い作業を強いられているのが現状である。 However, when the above conventional design method is adopted, one dummy MOS is used as the main body MOS by using CAD for designing a circuit diagram related to a semiconductor integrated circuit, CAD for designing a mask pattern of a semiconductor integrated circuit, or the like. It must be added manually. Furthermore, every time one dummy MOS is added, the verification (LVS: Layout Versus Schematic) must be performed on the added multi-MOS circuit. Therefore, the current situation is that designers are forced to perform inefficient and uncertain work.

そこで、本発明は、このような従来の技術の有する未解決の課題に着目してなされたものであって、MOSトランジスタなどの回路素子を連続接続してなるマルチ素子回路を含む半導体集積回路に係る回路図を設計するのに好適な回路図設計装置、回路図設計プログラム及び回路図設計方法を提供することを目的としている。 Therefore, the present invention has been made paying attention to such an unsolved problem of the conventional technology, and is applied to a semiconductor integrated circuit including a multi-element circuit in which circuit elements such as MOS transistors are continuously connected. An object of the present invention is to provide a circuit diagram design apparatus, a circuit diagram design program, and a circuit diagram design method suitable for designing such a circuit diagram.

〔発明1〕 上記目的を達成するために、発明1の回路図設計装置は、表示装置の画面上に表示されるレイアウト領域に、半導体集積回路を構成する各種回路素子に対応する回路記号と配線パターンとをレイアウトすることで、前記半導体集積回路に係る回路図を設計することが可能な回路図設計装置であって、前記回路図の設計に係る前記回路記号を選択する回路記号選択手段と、前記回路記号選択手段で選択された前記回路記号のうち特定の回路記号に対して、該特定の回路記号の示す回路素子の連続形成数を示すパラメータと、該連続形成数の回路素子を連続して一繋がりに形成して成るマルチ素子回路の動作特性のバラツキを低減するための付加素子であるダミー素子の形成数を示すパラメータとを含むパラメータを設定するパラメータ設定手段と、前記パラメータ設定手段で前記特定の回路記号に対して前記パラメータが設定されたときに、該設定されたパラメータの内容が正しいか誤りかを判定するパラメータ判定手段と、前記パラメータ判定手段の判定結果が誤りであるという判定結果であったときに、前記特定の回路記号に対して設定されたパラメータを予め設定された修正方法に基づき正しい内容に修正するパラメータ修正手段と、前記レイアウト領域にレイアウトされた回路記号及び配線パターンの情報と、前記パラメータ設定手段で設定されたパラメータとに基づき、前記マルチ素子回路を構成する各回路素子を含む前記レイアウトされた各回路記号の示す回路素子の接続関係を示す接続関係情報を生成する接続関係情報生成手段と、前記接続関係情報に基づき前記回路記号及び前記配線パターンを含んで構成されるシンボル回路図を表示する回路図表示手段と、を備える。

[Invention 1] In order to achieve the above object, a circuit diagram design apparatus of

このような構成であれば、回路記号選択手段によって、例えば、選択画面に表示された回路記号のうちパラメータが設定可能な特定の回路記号、又はレイアウト領域にレイアウトされた回路記号のうちパラメータが設定可能な特定の回路記号が選択されると、パラメータ設定手段によって、選択された特定の回路記号に対して、その回路素子の連続形成数及びダミー素子の形成数を示すパラメータを含むマルチ素子回路を生成するためのパラメータを設定することが可能である。特定の回路記号に対してパラメータが設定されると、パラメータ判定手段によって、設定されたパラメータ値の設定内容が正しいか誤りかが判定され、判定結果が誤りであるという判定結果のときに、パラメータ修正手段によって、特定の回路記号に対して設定された誤った設定内容のパラメータが、予め設定された修正方法に基づき正しい設定内容に自動的に修正される。 In such a configuration, the circuit symbol selection means, for example, sets a specific circuit symbol in which a parameter can be set among circuit symbols displayed on the selection screen or a parameter among circuit symbols laid out in the layout area. When a possible specific circuit symbol is selected, a multi-element circuit including a parameter indicating the number of continuous formations of the circuit elements and the number of formations of dummy elements is selected by the parameter setting means for the selected specific circuit symbol. It is possible to set parameters for generation. When a parameter is set for a specific circuit symbol, the parameter determination means determines whether the set content of the set parameter value is correct or incorrect. When the determination result indicates that the determination result is incorrect, the parameter The parameter of the erroneous setting content set for the specific circuit symbol is automatically corrected by the correcting means to the correct setting content based on a preset correction method.

一方、選択された特定の回路記号に対して正しいパラメータが設定されると、接続関係情報生成手段によって、レイアウト領域にレイアウトされた回路記号及び配線パターンの情報と、特定の回路記号に設定されたパラメータとに基づき、マルチ素子回路を構成する各回路素子を含むレイアウトされた各回路記号の示す回路素子の接続関係を示す接続関係情報が生成される。 On the other hand, when the correct parameter is set for the selected specific circuit symbol, the connection relation information generating means sets the circuit symbol and wiring pattern information laid out in the layout area and the specific circuit symbol. Based on the parameters, connection relation information indicating the connection relation of the circuit elements indicated by the respective circuit symbols laid out including the circuit elements constituting the multi-element circuit is generated.

また、接続関係情報が生成されると、回路図表手段によって、該生成された接続関係情報に基づき、回路記号及び配線パターンを含んで構成されるシンボル回路図が表示される。

従って、半導体基板(半導体ウェーハ)に形成される、能動素子(例えば、ダイオード、トランジスタなど)や、受動素子(例えば、抵抗、キャパシタ、インダクタなど)などの回路素子を、同じ回路素子同士で複数を連続接続(例えば、各回路素子の一部を他と共有させてひと繋がりに形成)した構成のマルチ素子回路を含む半導体集積回路を設計(作成)するときに、例えば、手作業で同じ回路記号を1つずつ選択して形成することなく、選択した回路記号に対して連続形成数をパラメータ設定するだけで、該回路記号の回路素子を連続接続した構成のマルチ素子回路を生成することができる。

When the connection relation information is generated, the circuit diagram means displays a symbol circuit diagram including a circuit symbol and a wiring pattern based on the generated connection relation information.

Accordingly, a plurality of circuit elements such as active elements (for example, diodes, transistors, etc.) and passive elements (for example, resistors, capacitors, inductors, etc.) formed on a semiconductor substrate (semiconductor wafer) can be used. When designing (creating) a semiconductor integrated circuit including a multi-element circuit having a configuration in which continuous connection (for example, a part of each circuit element is shared and formed in a single connection), for example, the same circuit symbol is used manually. A multi-element circuit having a configuration in which the circuit elements of the circuit symbol are continuously connected can be generated simply by setting the number of consecutive formations for the selected circuit symbol without selecting and forming each one. .

更に、マルチ素子回路において、例えば、該マルチ素子回路を構成する回路素子の一部の形状の違いなどから生じるマルチ素子回路の動作特性のバラツキを低減するため付加素子であるダミー素子についても、選択した回路記号に対してダミー素子の形成数をパラメータ設定するだけで、手作業でダミー素子の回路記号を1つずつ選択して形成することなく、連続接続された回路素子にダミー素子が付加接続された構成のマルチ素子回路を生成することができる。 In addition, in a multi-element circuit, for example, a dummy element that is an additional element is also selected in order to reduce variation in operating characteristics of the multi-element circuit caused by a difference in the shape of a part of the circuit elements constituting the multi-element circuit. By simply setting parameters for the number of dummy elements formed for each circuit symbol, the dummy elements can be added to the continuously connected circuit elements without manually selecting and forming the dummy element circuit symbols one by one. A multi-element circuit having the above-described configuration can be generated.

これによって、選択した回路記号に対してパラメータを設定するといった簡単な作業で、任意のダミー素子を含むマルチ素子回路を含む回路の接続関係情報を生成することができるという効果が得られる。

また、回路素子のマルチ数やダミー素子の数をパラメータで管理するようにしたので、確実にダミー素子を付加することができ、レイアウト検証(LVS)を、より確実に行うことができるという効果が得られる。

As a result, it is possible to generate connection relation information of a circuit including a multi-element circuit including an arbitrary dummy element by a simple operation of setting a parameter for the selected circuit symbol.

In addition, since the number of circuit elements and the number of dummy elements are managed by parameters, dummy elements can be added reliably, and layout verification (LVS) can be more reliably performed. can get.

また、選択した回路記号に対してパラメータを設定するので、本来の回路素子の連続接続数の情報とこの回路素子に付加的に接続されるダミー素子の情報とが関連付けられるので、この情報を、半導体集積回路のマスクパターンの生成に利用することで、マスクパターンの生成においても、ダミー素子を1つ1つ手作業で付加するといった労力を軽減することができるという効果が得られる。 In addition, since the parameter is set for the selected circuit symbol, the information on the number of continuous connections of the original circuit elements and the information on the dummy elements additionally connected to the circuit elements are associated with each other. By using it for generating a mask pattern of a semiconductor integrated circuit, it is possible to reduce the labor of manually adding dummy elements one by one even when generating a mask pattern.

更に、パラメータ判定手段によって設定内容の正誤判定を行ない、設定内容に誤りがあったときは、パラメータ修正手段によって修正を行なうようにした。これによって、ユーザの設定内容に間違いがあったときや、例えばパラメータMultiの数値を意図的に変更してパラメータDDM及びSDMの値との間に不整合が生じたときなどに、パラメータ修正手段が自動で正しい設定内容に修正を行ってくれるので、手作業による修正を行うことなく、簡易且つ確実に正しいパラメータ設定内容のマルチ素子回路を生成することができるという効果が得られる。 Further, the correctness / incorrectness of the setting contents is determined by the parameter determining means, and when there is an error in the setting contents, the parameter correcting means corrects the setting contents. As a result, when there is an error in the setting contents of the user, for example, when there is a mismatch between the values of the parameters DDM and SDM by intentionally changing the value of the parameter Multi, the parameter correction means Since the correct setting contents are automatically corrected, it is possible to easily and surely generate a multi-element circuit having the correct parameter setting contents without performing manual correction.

ここで、上記回路記号は、例えば、JIS C 0301 、JIS C 0617、JIS C 9309、JIS B 8601などのJISに準拠した回路記号や、これらの回路記号を基準にして作成されたもの、また、マスクパターンの生成にも対応させる場合は、各回路素子に対応するマスクパターンのセル、ブロックなどが該当する。

また、上記半導体集積回路に係る回路図は、例えば、上記JISに準拠した回路記号や配線パターンで表された回路図であるシンボル回路図や、セル、ブロックなどの回路記号で表されたマスクパターンのレイアウト図であるパターンレイアウト図などが該当する。以下、発明7の回路図設計プログラム、発明8の回路図設計方法において同じである。

Here, the circuit symbol is, for example, a circuit symbol compliant with JIS, such as JIS C 0301, JIS C 0617, JIS C 9309, JIS B 8601, or the like, created based on these circuit symbols, When the mask pattern generation is also supported, the mask pattern cell, block, and the like corresponding to each circuit element are applicable.

The circuit diagram relating to the semiconductor integrated circuit is, for example, a symbol circuit diagram which is a circuit diagram represented by a circuit symbol or wiring pattern compliant with the JIS, or a mask pattern which is represented by a circuit symbol such as a cell or a block. This corresponds to a pattern layout diagram that is a layout diagram. The same applies to the circuit diagram design program of the seventh invention and the circuit diagram design method of the eighth invention.

また、上記回路記号選択手段は、例えば、表示装置の画面上に回路記号の一覧を表示し、その中から任意の回路シンボルを選択したり、レイアウト領域にレイアウトされたシンボル回路図を構成する回路シンボルを選択したりする構成などが該当する。また、選択処理は、例えば、入力デバイス(マウス、タブレット、キーボードなど)を用いた利用者の操作入力に応じて行われ、利用者の任意の回路記号を選択できるようになっている。また、回路記号の一覧表示は、例えば、回路素子の種類毎に一覧を表示(一覧できないときは、ページ分けして表示)する。以下、発明7の回路図設計プログラム、発明8の回路図設計方法において同じである。 The circuit symbol selection means displays a list of circuit symbols on a screen of a display device, for example, selects an arbitrary circuit symbol from the list, or configures a symbol circuit diagram laid out in a layout area A configuration for selecting a symbol is applicable. In addition, the selection process is performed in accordance with, for example, a user operation input using an input device (such as a mouse, a tablet, or a keyboard), and an arbitrary circuit symbol of the user can be selected. The list display of the circuit symbols is, for example, a list for each type of circuit element (when the list cannot be displayed, it is displayed by dividing into pages). The same applies to the circuit diagram design program of the seventh invention and the circuit diagram design method of the eighth invention.

また、上記マルチ素子回路は、例えば、半導体基板に形成されるMOSトランジスタなどの能動素子、抵抗、コンデンサなどの受動素子などの回路素子を、同じものを複数連続して形成することで構成されるものである。このとき、例えば、MOSトランジスタであれば、隣り合う素子同士でソース領域やドレイン領域を共有するように連続形成される。

更に、複数の回路素子を連続形成したときに、各回路素子の形状などの違いによって生じる動作特性のバラツキを低減するために、例えば、連続形成部の両端にダミー素子として同じ種類、特性の回路素子を付加する。以下、発明7の回路図設計プログラム、発明8の回路図設計方法において同じである。

The multi-element circuit is configured by, for example, continuously forming a plurality of circuit elements such as active elements such as MOS transistors formed on a semiconductor substrate and passive elements such as resistors and capacitors. Is. At this time, for example, in the case of a MOS transistor, they are continuously formed so that adjacent elements share a source region and a drain region.

Furthermore, in order to reduce variation in operating characteristics caused by differences in the shape of each circuit element when a plurality of circuit elements are continuously formed, for example, circuits of the same type and characteristics as dummy elements at both ends of the continuous formation portion Add elements. The same applies to the circuit diagram design program of the seventh invention and the circuit diagram design method of the eighth invention.

また、上記接続関係情報生成手段は、例えば、レイアウト領域にレイアウトされた回路記号及び配線パターンから構成されるシンボル回路図の各回路記号の示す回路素子の識別情報と、各回路素子、各ダミー素子の各端子の接続情報とを含む、接続関係情報(例えば、SPICE(Simulation Program with Integrated Circuit Emphasis)のネットリストなど)を生成する。更に、特定の回路記号に対してパラメータが設定されたときは、その設定値に基づき、連続形成する各回路素子の識別情報と、ダミー素子などの各付加素子の識別情報と、各回路素子、各付加素子の各端子の接続情報とを含む、マルチ素子回路の接続関係情報を生成する。以下、発明7の回路図設計プログラム、発明8の回路図設計方法において同じである。 In addition, the connection relation information generating means includes, for example, circuit element identification information indicated by each circuit symbol of a symbol circuit diagram composed of circuit symbols and wiring patterns laid out in a layout area, each circuit element, and each dummy element. Connection relation information (for example, a net list of SPICE (Simulation Program with Integrated Circuit Emphasis) or the like) is generated. Further, when a parameter is set for a specific circuit symbol, based on the set value, identification information of each circuit element to be continuously formed, identification information of each additional element such as a dummy element, each circuit element, Multi-element circuit connection relation information including connection information of each terminal of each additional element is generated. The same applies to the circuit diagram design program of the seventh invention and the circuit diagram design method of the eighth invention.

〔発明2〕 更に、発明2の回路図設計装置は、発明1に記載の回路図設計装置において、前記パラメータ設定手段は、前記回路記号選択手段でMOS(metal-oxide-semiconductor)トランジスタの回路記号が選択されたときに、該MOSトランジスタの回路記号に対して、該MOSトランジスタの連続形成数を示すパラメータMultiと、該M個のMOSトランジスタを、ドレインとソースの領域を行方向となる一方向に交互に反復させながら一繋がりに形成したときの前記行方向の端部のドレイン領域に付加されるダミーMOSトランジスタの形成数を示すパラメータDDMと、前記行方向の端部のソース領域に付加されるダミーMOSトランジスタの形成数を示すパラメータSDMとを含むパラメータを設定することが可能であり、前記パラメータ判定手段は、前記パラメータMultiが偶数値に設定され且つ前記行方向の両端部が共にソース領域又はドレイン領域となるときに、前記パラメータDDM及び前記パラメータSDMにそれぞれ0以外の数値が設定される第1の設定内容と、前記パラメータMultiが偶数値に設定され且つ前記行方向の両端部が共にソース領域となるときに、前記パラメータDDMに0が設定され且つ前記パラメータSDMに1以下の数値又は3以上の奇数値が設定される第2の設定内容と、前記パラメータMultiが偶数値に設定され且つ前記行方向の両端部がドレイン領域となるときに、前記パラメータDDMに1以下の数値又は3以上の奇数値が設定され且つ前記パラメータSDMに0が設定される第3の設定内容とのうちいずれか1つの設定内容で、前記MOSトランジスタの回路記号に対してパラメータが設定されたときに、該パラメータの設定内容が誤りであると判定し、前記パラメータ修正手段は、前記第1の設定内容による誤り判定に対して、前記行方向の両端部が共にソース領域のときは、前記パラメータDDMの設定値が0で且つ前記パラメータSDMの設定値が所定の偶数値となるように設定値を修正し、前記行方向の両端部がドレイン領域のときは、前記パラメータDDMの設定値が所定の偶数値で且つ前記パラメータSDMの設定値が0となるように設定値を修正し、前記第2の設定内容による誤り判定に対して、前記パラメータSDMの設定値を所定の偶数値に修正し、前記第3の設定内容による誤り判定に対して、前記パラメータDDMの設定値を所定の偶数値に修正する。

[Invention 2] Further, the circuit diagram design apparatus according to

このような構成であれば、回路記号選択手段で選択されたMOSトランジスタの回路記号に対して、上記第1〜第3のいずれか1つの設定内容でパラメータが設定されると、パラメータ判定手段において、設定内容が誤りであると判定される。誤り判定がされると、パラメータ修正手段において、第1〜第3の設定内容のうち設定された内容に応じた修正方法で修正が行われる。具体的に、パラメータ修正手段は、第1の設定内容で設定が行われた場合に、パラメータDDM及びSDMの双方に0以外の数値が設定されているときは、両端がドレイン領域であれば、パラメータDDMの設定値が所定の偶数で且つパラメータSDMの設定値が0となるように設定値を修正する。一方、両端がソース領域であれば、パラメータSDMの設定値が所定の偶数で且つパラメータDDMの設定値が0となるように設定値を修正する。 With such a configuration, when a parameter is set according to any one of the first to third settings for the circuit symbol of the MOS transistor selected by the circuit symbol selection means, the parameter determination means , It is determined that the setting content is incorrect. When an error determination is made, the parameter correction means performs correction by a correction method according to the set contents among the first to third setting contents. Specifically, the parameter correction means is configured so that when both the parameters DDM and SDM are set to numerical values other than 0 when both are set in the first setting content, both ends are drain regions. The setting value is corrected so that the setting value of the parameter DDM is a predetermined even number and the setting value of the parameter SDM becomes zero. On the other hand, if both ends are source regions, the setting value is corrected so that the setting value of the parameter SDM is a predetermined even number and the setting value of the parameter DDM is zero.

また、第2の設定内容で設定が行われた場合に、パラメータSDMの設定値を所定の偶数値に修正し、第3の設定内容で設定が行われた場合に、パラメータDDMの設定値を所定の偶数値に修正する。

従って、マルチ素子回路を作成できるMOSトランジスタの回路記号に対して、誤ったパラメータを設定したときや、意図的にパラメータMultiの設定値を変更してパラメータDDM及びSDMの設定値との間に不整合が生じたときなどに、適切な内容のパラメータに自動的に修正することができる。

これにより、MOSトランジスタによって構成されるマルチ素子回路を、適切な回路構成で、より確実に作成することができるという効果が得られる。

In addition, when the setting is performed with the second setting content, the setting value of the parameter SDM is corrected to a predetermined even value, and when the setting is performed with the third setting content, the setting value of the parameter DDM is changed. Correct to a given even value.

Therefore, when an incorrect parameter is set for the circuit symbol of the MOS transistor capable of creating a multi-element circuit, or when the setting value of the parameter Multi is changed intentionally, it is not between the setting values of the parameters DDM and SDM. When matching occurs, the parameter can be automatically corrected to an appropriate content.

As a result, an effect is obtained that a multi-element circuit constituted by MOS transistors can be more reliably created with an appropriate circuit configuration.

〔発明3〕 更に、発明3の回路図設計装置は、発明1又は2に記載の回路図設計装置において、前記パラメータ設定手段は、前記回路記号選択手段でMOS(metal-oxide-semiconductor)トランジスタの回路記号が選択されたときに、前記パラメータMultiと、前記パラメータDDMと、前記パラメータSDMと、前記マルチ素子回路の前記行方向と直交する方向である列方向の形成数を示すパラメータROWとを含むパラメータを設定することが可能であり、前記接続関係情報生成手段は、前記パラメータROWに2以上の数値が設定されたときに、前記パラメータMultiの設定値を前記パラメータROWの設定値で割った数値をMOSトランジスタの前記連続形成数としたマルチ素子回路を、前記パラメータROWの数だけ前記列方向に連続して接続した構成のマルチ素子回路列の各回路素子の接続関係を示す接続関係情報を生成し、前記パラメータMultiの設定値(2以上の整数)を前記パラメータROWの設定値(Mの設定値>ROWの設定値≧1の整数)で除算した除算結果の数値をカラムパラメータの数値とし、前記パラメータMultiの設定値が前記パラメータROWの設定値で割り切れるときに、前記パラメータ判定手段は、前記パラメータROWが2以上の整数値に設定され且つ前記カラムパラメータの数値が奇数値となり、前記パラメータDDM及び前記パラメータSDMの少なくとも一方に前記パラメータROWの設定値をN倍(Nは1以上の整数)した数値とは異なる数値が設定される第4の設定内容と、前記パラメータROWが2以上の整数値に設定され且つ前記カラムパラメータの数値が偶数値となり、前記パラメータDDM及び前記パラメータSDMの少なくとも一方に前記パラメータROWの設定値をM倍(Mは2以上の偶数)にした数値とは異なる数値が設定される第5の設定内容とのうちいずれか1つの設定内容で、前記MOSトランジスタの回路記号に対してパラメータが設定されたときに、該パラメータの設定内容が誤りであると判定し、前記パラメータ修正手段は、前記第4の設定内容による誤り判定に対して、前記パラメータDDMの設定値及び前記パラメータSDMの設定値のうち前記パラメータROWの設定値をN倍した数値とは異なる数値が設定されているものを、前記パラメータROWの設定値となるように修正し、前記第5の設定内容による誤り判定に対して、前記行方向の両端部が共にソース領域のときは、前記パラメータDDMの設定値が0以外の数値のときは該設定値を0に且つ前記パラメータSDMの設定値を前記パラメータROWの設定値をM倍にした数値に修正し、前記行方向の両端部がドレイン領域のときは、前記パラメータDDMの設定値を前記パラメータROWの設定値をM倍にした数値に且つ前記パラメータSDMの設定値が0以外の数値のときは該設定値を0に修正する。

[Invention 3] Further, the circuit diagram design apparatus according to the

このような構成であれば、パラメータROWの数値を2以上に設定することで、複数のマルチ素子回路が、設定値の数だけ列方向に連続して接続された構成のマルチ素子回路列を生成することができる。更に、パラメータMultiの設定値(2以上の整数)をパラメータROWの設定値(Mの設定値>ROWの設定値≧1の整数)で除算して割り切れるときに、上記第4〜第5の設定内容で、MOSトランジスタの回路記号に対して、パラメータが設定されると、パラメータ判定手段において、設定内容が誤りであると判定される。 In such a configuration, by setting the numerical value of the parameter ROW to 2 or more, a multi-element circuit array having a configuration in which a plurality of multi-element circuits are continuously connected in the column direction by the number of set values is generated. can do. Further, when the setting value of the parameter Multi (an integer of 2 or more) is divided by the setting value of the parameter ROW (the setting value of M> the setting value of ROW ≧ an integer of 1), the above fourth to fifth settings When the parameter is set for the circuit symbol of the MOS transistor, the parameter determination means determines that the setting content is incorrect.

誤り判定がされると、パラメータ修正手段において、第4〜第5の設定内容のうち設定された内容に応じた修正方法で修正が行われる。

具体的に、パラメータ修正手段は、第4の設定内容で設定が行われた場合に、パラメータDDMの設定値及びパラメータSDMの設定値のうちパラメータROWの設定値とは異なる数値が設定されているものを、パラメータROWの設定値となるように修正する。

When an error determination is made, the parameter correction means performs correction by a correction method according to the set contents among the fourth to fifth set contents.

Specifically, the parameter correction means sets a value different from the setting value of the parameter ROW among the setting value of the parameter DDM and the setting value of the parameter SDM when the setting is performed with the fourth setting content. Is corrected so as to be the set value of the parameter ROW.

また、第5の設定内容で設定が行われた場合に、行方向の両端部が共にソース領域のときは、パラメータDDMの設定値が0以外の数値のときは該設定値を0に且つパラメータSDMの設定値をパラメータROWの設定値をM倍にした数値に修正し、行方向の両端部がドレイン領域のときは、パラメータDDMの設定値をパラメータROWの設定値をM倍にした数値に且つパラメータSDMの設定値が0以外の数値のときは該設定値を0に修正する。 In addition, when setting is performed with the fifth setting content, when both end portions in the row direction are source regions, when the setting value of the parameter DDM is a value other than 0, the setting value is set to 0 and the parameter The SDM setting value is corrected to a value obtained by multiplying the setting value of the parameter ROW by M times. When both ends in the row direction are drain regions, the setting value of the parameter DDM is changed to a value obtained by multiplying the setting value of the parameter ROW by M times. If the setting value of the parameter SDM is a value other than 0, the setting value is corrected to 0.

従って、マルチ素子回路列を作成できるMOSトランジスタの回路記号に対して、誤ったパラメータを設定したときや、意図的にパラメータMultiやROWの設定値を変更してパラメータDDM及びSDMの設定値との間に不整合が生じたときなどに、適切な内容のパラメータに自動的に修正することができる。

これにより、MOSトランジスタによって構成されるマルチ素子回路列を、適切な回路構成で、より確実に作成することができるという効果が得られる。

ここで、上記マルチ素子回路列は、各列のマルチ素子回路を構成するMOSトランジスタのゲート領域、ドレイン領域、ソース領域を列方向に共有して構成されるものなどが該当する。

Therefore, when an incorrect parameter is set for a circuit symbol of a MOS transistor that can create a multi-element circuit row, or when the setting values of the parameters Multi and ROW are intentionally changed, the setting values of the parameters DDM and SDM are changed. When inconsistency occurs, the parameter can be automatically corrected to an appropriate content.

As a result, an effect is obtained that a multi-element circuit array composed of MOS transistors can be more reliably created with an appropriate circuit configuration.

Here, the multi-element circuit column corresponds to a configuration in which the gate region, the drain region, and the source region of the MOS transistors constituting the multi-element circuit of each column are shared in the column direction.

〔発明4〕 更に、発明4の回路図設計装置は、発明1乃至3のいずれか1に記載の回路図設計装置において、前記回路図表示手段は、前記接続関係情報生成手段で生成された接続関係情報に基づき、前記半導体集積回路のマスクパターンのレイアウトを示すパターンレイアウト図を表示し、前記回路図表示手段で表示されたパターンレイアウト図を編集するレイアウト編集手段を備え、前記パラメータ修正手段は、前記レイアウト編集手段で前記パターンレイアウト図の編集が行われたときに、その編集結果に基づき前記特定の回路記号に設定されたパラメータを修正し、前記接続関係情報生成手段は、前記レイアウト編集手段で前記パターンレイアウト図の編集が行われたときに、その編集結果と前記パラメータ修正手段の修正結果とに基づき前記接続関係情報を修正する。

[Invention 4] Further, the circuit diagram design apparatus according to the

このような構成であれば、回路図表示手段によって、JISに準拠する回路記号をレイアウト領域にレイアウトしたり、特定の回路記号に対してパラメータを設定したりするなどして構成されたシンボル回路図に対して生成された接続関係情報に基づき、パターンレイアウト図を表示するための表示情報を生成し、該生成した表示情報に基づきマルチ素子回路のマスクパターンを含むパターンレイアウト図を表示することが可能である。 With such a configuration, a symbol circuit diagram configured by laying out circuit symbols conforming to JIS in the layout area or setting parameters for specific circuit symbols by means of circuit diagram display means. Display information for displaying a pattern layout diagram can be generated based on the connection relation information generated for the pattern, and a pattern layout diagram including a mask pattern of a multi-element circuit can be displayed based on the generated display information. It is.

更に、レイアウト編集手段によって、表示されたレイアウト図の編集を行うことが可能であり、編集が行われると、パラメータ修正手段によって、レイアウト編集手段の編集結果に基づき、特定の回路記号に対して設定されたパラメータが修正され、接続関係情報生成手段によって、編集手段の編集結果とパラメータ修正手段の修正結果に基づき接続関係情報が修正される。 Furthermore, it is possible to edit the displayed layout diagram by the layout editing means. When the editing is performed, the parameter correction means sets the specific circuit symbol based on the editing result of the layout editing means. The connection parameter information is corrected, and the connection relationship information generation unit corrects the connection relationship information based on the editing result of the editing unit and the correction result of the parameter correction unit.

従って、パターンレイアウト図に対して編集が行われたときに、その編集によって、マルチ素子回路の連続形成数などが変更されて、ダミー素子の数などに変更の必要性が生じたときに、パラメータ修正手段によってパラメータを自動的に適切な設定値に修正し、且つ、接続関係情報生成手段によって、前記修正結果と前記編集結果とに基づき、接続関係情報を自動的に適切な内容に修正することができる。 Therefore, when the pattern layout diagram is edited, the parameter changes when the number of continuous formations of multi-element circuits is changed by the editing and the number of dummy elements needs to be changed. The parameter is automatically corrected to an appropriate set value by the correcting means, and the connection relation information is automatically corrected to an appropriate content based on the correction result and the editing result by the connection relation information generating means. Can do.

これによって、パターンレイアウト図を編集して、マルチ素子回路の構成が変更されたときでも、その回路記号に対して設定されたパラメータを適切な値に自動で修正し、且つこの修正結果の反映された接続関係情報を自動で生成することができるので、手作業による修正と比較して、より確実に適切な構成のマルチ素子回路を含む回路及びマスクパターンを設計することができ、且つ設計した回路に対する検証(LVS)をより確実に行うことができるという効果が得られる。 As a result, even when the pattern layout diagram is edited and the configuration of the multi-element circuit is changed, the parameters set for the circuit symbol are automatically corrected to appropriate values, and the correction results are reflected. Since the connection relation information can be automatically generated, it is possible to design a circuit and a mask pattern including a multi-element circuit having an appropriate configuration more reliably than the manual correction, and the designed circuit. The effect that verification (LVS) can be performed more reliably is obtained.

〔発明5〕 更に、発明5の回路図設計装置は、発明3に記載の回路図設計装置において、前記回路図表示手段は、前記接続関係情報生成手段で生成された接続関係情報に基づき、前記半導体集積回路のマスクパターンのレイアウトを示すパターンレイアウト図を表示し、前記回路図表示手段で表示されたパターンレイアウト図を編集するレイアウト編集手段を備え、前記パラメータ修正手段は、前記レイアウト編集手段で前記パターンレイアウト図の編集が行われたときに、その編集結果に基づき前記特定の回路記号に設定されたパラメータを修正し、前記接続関係情報生成手段は、前記レイアウト編集手段で前記パターンレイアウト図の編集が行われたときに、その編集結果と前記パラメータ修正手段の修正結果とに基づき前記接続関係情報を修正し、前記レイアウト編集手段によって、前記MOSトランジスタを含んで構成されるマルチ素子回路の列方向の形成数が変更されたときに、前記パラメータ修正手段は、前記パラメータMultiの設定値を該設定値を前記形成数倍にした数値に修正すると共に前記パラメータROWの設定値を前記変更した形成数に修正し、前記カラムパラメータの数値が奇数値のときは、前記パラメータDDMの設定値及び前記パラメータSDMの設定値を、それぞれ修正後の前記パラメータROWの設定値に修正し、前記カラムパラメータの数値が偶数値のときに、前記行方向の両端部が共にソース領域のときは、前記パラメータDDMの設定値が0以外の数値のときは該設定値を0に且つ前記パラメータSDMの設定値を前記修正後のパラメータROWの設定値をM倍にした数値に修正し、前記行方向の両端部がドレイン領域のときは、前記パラメータDDMの設定値を前記修正後のパラメータROWの設定値をM倍にした数値に且つ前記パラメータSDMの設定値が0以外の数値のときは該設定値を0に修正する。

[Invention 5] Further, the circuit diagram design apparatus according to Invention 5 is the circuit diagram design apparatus according to

このような構成であれば、回路図表示手段によって、JISに準拠する回路記号をレイアウト領域にレイアウトしたり、特定の回路記号に対してパラメータを設定したりするなどして構成された回路図に対して生成された接続関係情報に基づき、パターンレイアウト図を表示するための表示情報を生成し、該生成した表示情報に基づきマルチ素子回路のマスクパターンを含むパターンレイアウト図を表示することが可能である。 In such a configuration, the circuit diagram display means lays out a circuit symbol conforming to JIS in the layout area or sets a parameter for a specific circuit symbol. It is possible to generate display information for displaying the pattern layout diagram based on the connection relation information generated for the pattern layout diagram and display the pattern layout diagram including the mask pattern of the multi-element circuit based on the generated display information. is there.

更に、レイアウト編集手段によって、表示されたレイアウト図の編集を行うことが可能であり、編集が行われると、パラメータ修正手段によって、レイアウト編集手段の編集結果に基づき、特定の回路記号に対して設定されたパラメータが修正され、接続関係情報生成手段によって、編集手段の編集結果とパラメータ修正手段の修正結果に基づき接続関係情報が修正される。 Furthermore, it is possible to edit the displayed layout diagram by the layout editing means. When the editing is performed, the parameter correction means sets the specific circuit symbol based on the editing result of the layout editing means. The connection parameter information is corrected, and the connection relationship information generation unit corrects the connection relationship information based on the editing result of the editing unit and the correction result of the parameter correction unit.

なお更に、パラメータ修正手段は、レイアウト編集手段によって、前記MOSトランジスタを含んで構成されるマルチ素子回路の列方向の形成数が変更されたときに、パラメータMultiの設定値を前記列方向の形成数倍に修正すると共にパラメータROWの設定値を変更した形成数となるように修正する。更に、パラメータ修正手段は、カラムパラメータの数値が奇数値のときは、パラメータDDMの設定値及びパラメータSDMの設定値を、それぞれ修正後のパラメータROWの設定値に修正する。 Still further, the parameter correction means changes the setting value of the parameter Multi to the number of formations in the column direction when the number of formations in the column direction of the multi-element circuit including the MOS transistor is changed by the layout editing means. The number of formations is corrected so that the number of formations is changed by changing the setting value of the parameter ROW. Further, the parameter correcting means corrects the setting value of the parameter DDM and the setting value of the parameter SDM to the setting value of the parameter ROW after correction when the numerical value of the column parameter is an odd value.

一方、カラムパラメータの数値が偶数値のときに、行方向の両端部が共にソース領域となるときは、パラメータDDMの設定値が0以外の数値のときは該設定値を0に且つパラメータSDMの設定値を修正後のパラメータROWの設定値をM倍にした数値に修正し、行方向の両端部がドレイン領域となるときは、パラメータDDMの設定値を修正後のパラメータROWの設定値をM倍にした数値に且つパラメータSDMの設定値が0以外の数値のときは該設定値を0に修正する。 On the other hand, when the column parameter value is an even value and both end portions in the row direction are source regions, the set value of the parameter DDM is 0 and the set value of the parameter SDM is set to 0 when the set value of the parameter DDM is a value other than 0. When the setting value is corrected to a value obtained by multiplying the setting value of the parameter ROW after the correction by M times, and both ends in the row direction are drain regions, the setting value of the parameter DDM is changed to the setting value of the parameter ROW after correction. When the value is doubled and the setting value of the parameter SDM is a value other than 0, the setting value is corrected to 0.

従って、パターンレイアウト図に対して編集が行われたときに、その編集によって、MOSトランジスタを含んで構成されるマルチ素子回路の列方向の形成数が変更されて、パラメータDDM及びパラメータSDMなどに変更の必要性が生じたときに、パラメータ修正手段によって、パラメータROWの変更内容に応じてパラメータDDM及びパラメータSDMの設定値を適切な設定内容に自動で修正することができる。 Therefore, when the pattern layout diagram is edited, the number of formations in the column direction of the multi-element circuit including the MOS transistor is changed by the editing, so that the parameter DDM and the parameter SDM are changed. Therefore, the parameter correction means can automatically correct the setting values of the parameter DDM and the parameter SDM to the appropriate setting contents according to the change contents of the parameter ROW.

これによって、パターンレイアウト図を編集して、MOSトランジスタのマルチ素子回路列の構成が変更されたときでも、その回路記号に対して設定されたパラメータDDM及びパラメータSDMを適切な値に自動で修正し、且つこの修正結果の反映された接続関係情報を自動で生成することができるので、手作業による修正と比較して、より確実に適切な構成のマルチ素子回路を含む回路及びマスクパターンを設計することができ、且つ設計した回路に対する検証(LVS)をより確実に行うことができるという効果が得られる。 Thus, even when the configuration of the multi-element circuit array of MOS transistors is changed by editing the pattern layout diagram, the parameters DDM and SDM set for the circuit symbols are automatically corrected to appropriate values. In addition, since the connection relation information reflecting the correction result can be automatically generated, the circuit and the mask pattern including the multi-element circuit having an appropriate configuration can be more reliably designed as compared with the manual correction. And the verification (LVS) for the designed circuit can be performed more reliably.

〔発明6〕 更に、発明6の回路図設計装置は、発明4又は5に記載の回路図設計装置において、前記レイアウト編集手段は、複数の前記マルチ素子回路を、これらを構成する回路素子の回路パターンの一部を共有させて合成する第1の合成処理部と、複数の前記マルチ素子回路を、これらを構成する回路素子の回路パターンを所定の組み合わせで合体させて合成する第2の合成処理部とを有する。

[Invention 6] Further, the circuit diagram design apparatus according to the

このような構成であれば、第1の合成処理部による合成や、第2の合成処理部による合成が行われて、マルチ素子回路の構成が変更されたときでも、その回路記号に対して設定されたパラメータを適切な値に自動で修正し、且つこの修正結果の反映された接続関係情報を自動で生成することができるので、手作業による修正と比較して、より確実に適切な構成のマルチ素子回路を含む回路及びマスクパターンを設計することができ、且つ設計した回路に対する検証(LVS)をより確実に行うことができるという効果が得られる。 In such a configuration, even when the synthesis by the first synthesis processing unit or the synthesis by the second synthesis processing unit is performed and the configuration of the multi-element circuit is changed, the circuit symbol is set. Since it is possible to automatically correct the specified parameter to an appropriate value and automatically generate the connection relation information reflecting the correction result, it is possible to more reliably make the appropriate configuration as compared with the manual correction. It is possible to design a circuit including a multi-element circuit and a mask pattern, and to perform verification (LVS) on the designed circuit more reliably.

〔発明7〕 一方、上記目的を達成するために、発明7の回路図設計プログラムは、表示装置の画面上に表示されるレイアウト領域に、半導体集積回路を構成する各種回路素子に対応する回路記号と配線パターンとをレイアウトして、前記半導体集積回路に係る回路図を設計するために、コンピュータを、前記回路図の設計に係る前記回路記号を選択する回路記号選択手段、前記回路記号選択手段で選択された前記回路記号のうち特定の回路記号に対して、該特定の回路記号の示す回路素子の連続形成数を示すパラメータと、該連続形成数の回路素子を連続して一繋がりに形成して成るマルチ素子回路の動作特性のバラツキを低減するための付加素子であるダミー素子の形成数を示すパラメータとを含むパラメータを設定するパラメータ設定手段、前記パラメータ設定手段で前記特定の回路記号に対して前記パラメータが設定されたときに、該設定されたパラメータの内容が正しいか誤りかを判定するパラメータ判定手段、前記パラメータ判定手段の判定結果が誤りであるという判定結果であったときに、前記特定の回路記号に対して設定されたパラメータを予め設定された修正方法に基づき正しい内容に修正するパラメータ修正手段、前記レイアウト領域にレイアウトされた回路記号及び配線パターンの情報と、前記パラメータ設定手段で設定されたパラメータとに基づき、前記マルチ素子回路を構成する各回路素子を含む前記レイアウトされた各回路記号の示す回路素子の接続関係を示す接続関係情報を生成する接続関係情報生成手段、及び前記接続関係情報に基づき前記回路記号及び前記配線パターンを含んで構成されるシンボル回路図を表示する回路図表示手段として機能させる。

このような構成であれば、コンピュータによってプログラムが読み取られ、読み取られたプログラムに従ってコンピュータが処理を実行すると、上記発明1に記載の回路図設計装置と同等の作用および効果が得られる。

[Invention 7] On the other hand, in order to achieve the above object, a circuit diagram design program according to Invention 7 includes circuit symbols corresponding to various circuit elements constituting a semiconductor integrated circuit in a layout area displayed on a screen of a display device. In order to design a circuit diagram related to the semiconductor integrated circuit by laying out a wiring pattern and a circuit pattern, a computer uses a circuit symbol selecting means for selecting the circuit symbol related to the design of the circuit diagram, and the circuit symbol selecting means. For a specific circuit symbol among the selected circuit symbols, a parameter indicating the continuous formation number of the circuit elements indicated by the specific circuit symbol and the continuous formation circuit elements are formed in a continuous manner. Parameter setting means for setting a parameter including a parameter indicating the number of dummy elements that are additional elements for reducing variation in operating characteristics of the multi-element circuit A parameter determination unit that determines whether the content of the set parameter is correct or incorrect when the parameter is set for the specific circuit symbol by the parameter setting unit; a determination result of the parameter determination unit Parameter correction means for correcting a parameter set for the specific circuit symbol to a correct content based on a preset correction method, when the result is a determination result that the error is incorrect, laid out in the layout area Based on the circuit symbol and wiring pattern information and the parameters set by the parameter setting means, the connection relationship of the circuit elements indicated by the laid out circuit symbols including the circuit elements constituting the multi-element circuit is shown. Connection relation information generating means for generating connection relation information, and the circuit description based on the connection relation information. And to function as a circuit diagram display means for displaying the constructed symbol circuit diagram including the wiring pattern.

With such a configuration, when the program is read by the computer and the computer executes processing according to the read program, the same operation and effect as those of the circuit diagram design apparatus according to the first aspect of the invention can be obtained.

〔発明8〕 また、上記目的を達成するために、発明8の回路図設計方法は、回路記号選択手段、パラメータ設定手段、パラメータ判定手段、パラメータ修正手段、接続関係情報生成手段及び回路図表示手段を備えた回路図設計装置を利用して、表示装置の画面上に表示されるレイアウト領域に、半導体集積回路を構成する各種回路素子に対応する回路記号と配線パターンとをレイアウトして、前記半導体集積回路に係る回路図を設計する回路図設計方法であって、前記回路記号選択手段に、前記回路図の設計に係る前記回路記号を選択させる回路記号選択ステップと、前記パラメータ設定手段に、前記回路記号選択ステップで選択された前記回路記号のうち特定の回路記号に対して、該特定の回路記号の示す回路素子の連続形成数を示すパラメータと、該連続形成数の回路素子を連続して一繋がりに形成して成るマルチ素子回路の動作特性のバラツキを低減するための付加素子であるダミー素子の形成数を示すパラメータとを含むパラメータを設定させるパラメータ設定ステップと、前記パラメータ判定手段に、前記パラメータ設定ステップで前記特定の回路記号に対して前記パラメータが設定されたときに、該設定されたパラメータの内容が正しいか誤りかを判定させるパラメータ判定ステップと、前記パラメータ修正手段に、前記パラメータ判定ステップの判定結果が誤りであるという判定結果であったときに、前記特定の回路記号に対して設定されたパラメータを予め設定された修正方法に基づき正しい内容に修正するパラメータ修正ステップと、前記接続関係情報生成手段に、前記レイアウト領域にレイアウトされた回路記号及び配線パターンの情報と、前記パラメータ設定ステップで設定されたパラメータとに基づき、前記マルチ素子回路を構成する各回路素子を含む前記レイアウトされた各回路記号の示す回路素子の接続関係を示す接続関係情報を生成させる接続関係情報生成ステップと、前記回路図表示手段に、前記接続関係情報に基づき前記回路記号及び前記配線パターンを含んで構成されるシンボル回路図を表示させる回路図表示ステップとを含む。

このような構成であれば、上記発明1に記載の回路図設計装置と同等の作用及び効果が得られる。

[Invention 8] In order to achieve the above object, a circuit diagram design method of Invention 8 includes circuit symbol selection means, parameter setting means, parameter determination means, parameter correction means, connection relation information generation means, and circuit diagram display means. Laying out circuit symbols and wiring patterns corresponding to various circuit elements constituting a semiconductor integrated circuit in a layout area displayed on a screen of a display device by using a circuit diagram design apparatus comprising: A circuit diagram design method for designing a circuit diagram related to an integrated circuit, wherein the circuit symbol selection unit causes the circuit symbol selection unit to select the circuit symbol related to the design of the circuit diagram, and the parameter setting unit includes the For a specific circuit symbol among the circuit symbols selected in the circuit symbol selection step, a parameter indicating the number of consecutive circuit elements indicated by the specific circuit symbol. A parameter including a meter and a parameter indicating the number of dummy elements that are additional elements for reducing variation in operating characteristics of a multi-element circuit formed by continuously connecting the circuit elements of the continuous formation number. A parameter setting step for setting the parameter, and the parameter determination means determines whether the content of the set parameter is correct or incorrect when the parameter is set for the specific circuit symbol in the parameter setting step. A parameter determination step, and the parameter correction means, when the determination result of the parameter determination step is an error, the parameter set for the specific circuit symbol is corrected in advance A parameter correcting step for correcting the correct content based on the method, and the connection relation information generating means; The circuit symbols and circuit patterns laid out in the layout area and the parameters set in the parameter setting step are used to determine the layout of each circuit symbol including each circuit element constituting the multi-element circuit. A connection relationship information generating step for generating connection relationship information indicating the connection relationship of the circuit elements shown, and a symbol circuit diagram including the circuit symbol and the wiring pattern on the circuit diagram display means based on the connection relationship information. And a circuit diagram display step for displaying.

With such a configuration, operations and effects equivalent to those of the circuit diagram design apparatus according to the first aspect of the invention can be obtained.

以下、本発明の実施の形態を図面に基づき説明する。図1〜図18は、本発明に係る回路図設計装置、回路図設計プログラム及び回路図設計方法の実施の形態を示す図である。

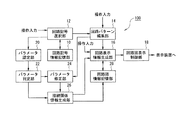

まず、本発明に係る回路図設計装置の機能構成を図1に基づき説明する。図1は、本発明に係る回路図設計装置100の機能構成を示すブロック図である。

回路図設計装置100は、図1に示すように、回路記号情報記憶部10と、回路記号選択部12と、回路パターン編集部14と、回路表示情報生成部16と、回路図表示制御部18とを含んで構成される。

Hereinafter, embodiments of the present invention will be described with reference to the drawings. 1 to 18 are diagrams showing embodiments of a circuit diagram design apparatus, a circuit diagram design program, and a circuit diagram design method according to the present invention.

First, the functional configuration of the circuit diagram design apparatus according to the present invention will be described with reference to FIG. FIG. 1 is a block diagram showing a functional configuration of a circuit

As shown in FIG. 1, the circuit

回路記号情報記憶部10は、記憶装置(後述)の所定の記憶領域に構成されており、回路図を生成するための各種回路素子に対応した複数種類の回路記号の情報が記憶される。

具体的に、回路記号としては、シンボル回路図を生成するためのJISに準拠する回路記号(以下、回路シンボルと称す)や、マスクパターンを生成するためのセルやブロックなどの回路記号(以下、マスクシンボルと称す)などが記憶される。

The circuit symbol

Specifically, as a circuit symbol, a circuit symbol conforming to JIS for generating a symbol circuit diagram (hereinafter referred to as a circuit symbol), a circuit symbol such as a cell or block for generating a mask pattern (hereinafter referred to as a circuit symbol) Etc.) are stored.

回路記号選択部12は、マウス、キーボード、タブレットなどの入力装置を介した利用者からの操作入力に応じて、回路素子の情報選択画面や、回路記号の選択画面を表示装置の表示画面上に画像表示すると共に、画像表示された複数種類の回路記号の中から操作入力に応じた回路記号を選択する機能を有している。更に、操作入力に応じて、既にレイアウトされた回路記号や配線パターンなどの回路の任意の構成要素を選択する機能も有している。

The circuit

回路パターン編集部14は、入力装置を介した利用者からの操作入力に応じて、シンボル回路図の編集モード(以下、編集モード1と称す)において、回路記号選択部12で選択された回路シンボルや配線パターンを表示画面上に画像表示されたレイアウト領域の指定位置にレイアウトしたり、指定位置にレイアウトされたものを削除したりする機能を有している。

The circuit

更に、回路パターン編集部14は、入力装置を介した利用者からの操作入力に応じて、パターンレイアウト図の編集モード(以下、編集モード2と称す)において、回路記号選択部12で選択されたマスクシンボルや、配線パターンなどを表示画面上に画像表示されたレイアウト領域の指定位置にレイアウトしたり、指定位置にレイアウトされたものを削除したりする機能を有している。

Furthermore, the circuit

回路表示情報生成部16は、回路パターン編集部14によって編集された回路図の表示情報を生成し、該表示情報を表示要求と共に回路図表示制御部18に出力する機能を有している。

更に、回路表示情報生成部16は、接続関係情報生成部26から入力された接続関係情報に基づき、回路シンボルから構成されるシンボル回路図又は、セル、ブロックなどのマスクシンボルから構成されるパターンレイアウト図のいずれか指定された方の表示情報を生成して、該表示情報を表示要求と共に回路図表示制御部18に出力する機能を有している。

The circuit display

Further, the circuit display

更に、回路表示情報生成部16は、入力装置を介した利用者からの操作入力に応じて、指定された接続関係情報を回路図情報記憶部28から読み出し、該読み出した接続関係情報に対応する回路シンボルから構成されたシンボル回路図又は、パターンレイアウト図のいずれか指定された方の表示情報を生成して、該表示情報を表示要求と共に回路図表示制御部18に出力する機能を有している。

Further, the circuit display

更に、回路表示情報生成部16は、接続関係情報生成部26から入力された、マルチ素子回路に対する接続関係情報に基づき、回路シンボルから構成されたマルチ素子回路のシンボル回路図又は、マルチ素子回路のパターンレイアウト図のいずれか指定された方の表示情報を生成して、該表示情報を表示要求と共に回路図表示制御部18に出力する機能を有している。

Further, the circuit display

回路図表示制御部18は、回路表示情報生成部16から入力される表示情報に基づき、表示装置の表示画面上に、回路シンボルから構成されるシンボル回路図を表示したり、マスクパターンのレイアウトを示すパターンレイアウト図を表示したりする機能を有している。

更に、回路図表示制御部18は、表示色や表示形状などの回路記号の表示方法のルールが設定されている場合に、該ルールに基づき、表示装置に、例えば、パラメータの設定された回路記号の色を、パラメータの設定されていない回路記号の色とは異なる色で表示させたり、パラメータの設定された回路記号の形状を、パラメータの設定されていない回路記号の形状とは異なる形状で表示させたりする機能を有している。

The circuit diagram

Further, when a rule for a method of displaying a circuit symbol such as a display color or a display shape is set, the circuit diagram

回路図設計装置100は、更に、パラメータ設定部20と、パラメータ判定部22と、パラメータ修正部24と、接続関係情報生成部26と、回路図情報記憶部28とを含んで構成される。

パラメータ設定部20は、ダイオード、トランジスタなどの能動素子、抵抗、キャパシタンス(コンデンサ)、インダクタンス(コイル)などの受動素子に対応する回路シンボルを選択したときに、選択した回路シンボルがマルチ素子回路を構成可能な場合に、入力装置を介した利用者からの操作入力に応じて、選択した回路シンボルに対して、各種パラメータを設定する機能を有している。

The circuit

When the

具体的なパラメータとしては、マルチ素子回路の本体部分を構成する回路素子の連続形成数と、連続形成したときに生じる動作特性のバラツキを低減するために本体部分に付加接続するダミー素子の形成数とがある。

例えば、回路素子がMOSトランジスタの場合は、Nチャンネル型のMOSトランジスタ(NMOS)又はPチャンネル型のMOSトランジスタ(PMOS)の行方向となる所定の一方向への連続形成数(Multi=<Multi>)、チャンネルサイズ(W(チャンネル幅)/L(チャンネル長)=<W>/<L>)、該NMOS又はPMOSと同じ回路素子のダミーMOSの前記連続形成してなる本体部の端部ドレイン側(以下、ドレイン端部と称す)への形成数(Multi=<DDM(Drain Dummy Multi)>)、ダミーMOSの本体部分の端部ソース側(以下、ソース端部と称す)への形成数(Multi=<SDM(Source Dummy Multi)>)、前記本体部とダミー素子とからなるマルチ素子回路を、前記行方向と垂直な方向である列方向に連続して形成する列数(ROW=<ROW>)などがパラメータとして設定できる。

Specific parameters include the number of circuit elements that form the main part of the multi-element circuit and the number of dummy elements that are additionally connected to the main part in order to reduce variations in the operating characteristics that occur when they are continuously formed. There is.

For example, when the circuit element is a MOS transistor, the number of consecutive N-channel type MOS transistors (NMOS) or P-channel type MOS transistors (PMOS) formed in a predetermined direction that is the row direction (Multi = <Multi> ), Channel size (W (channel width) / L (channel length) = <W> / <L>), end drain of the body portion formed by continuously forming the dummy MOS of the same circuit element as the NMOS or PMOS Number formed on the side (hereinafter referred to as the drain end) (Multi = <DDM (Drain Dummy Multi)>), the number formed on the end source side (hereinafter referred to as the source end) of the body portion of the dummy MOS (Multi = <SDM (Source Dummy Multi)>), the number of columns in which a multi-element circuit composed of the main body and dummy elements is continuously formed in a column direction which is a direction perpendicular to the row direction (ROW = <ROW>) and other parameters It can be set as.

本実施の形態では、更に、上記パラメータを設定することで自動設定されるパラメータとして、パラメータMultiの設定値をパラメータROWの設定値で除算した除算結果の数値が設定されるカラムパラメータ(Column=<Multi/ROW>)がある。

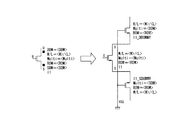

ここで、図2は、パラメータ設定可能なNMOSの回路シンボルの一例と、パラメータ設定後のマルチ素子回路のシンボル回路図の一例とを示す図である。

In the present embodiment, as a parameter automatically set by setting the above parameters, a column parameter (Column = <) in which a numerical value of a division result obtained by dividing the setting value of the parameter Multi by the setting value of the parameter ROW is set. Multi / ROW>).

Here, FIG. 2 is a diagram illustrating an example of an NMOS circuit symbol in which parameters can be set and an example of a symbol circuit diagram of a multi-element circuit after the parameters are set.

本実施の形態において、パラメータ設定が可能なNMOSの回路シンボルは、図2の左図に示すように、JISで標準化されているNMOSの回路シンボルの各端子部の傍に端子名G(Gate)、D(Drain)、S(Source)がそれぞれ表示され、更に、D端子の右側にパラメータ名「DDM(ドレイン端部側形成数)=<DDM>」と、S端子の右側にパラメータ名「SDM(ソース端部側形成数)=<SDM>」と、DDMとSDMの上下間に、パラメータ名「W(チャンネル幅)/L(チャンネル長)=<W>/<L>」と、パラメータ名「Multi(連続形成数)=<Multi>」と、パラメータ名「ROW=<ROW>」とが表示されたものとなる。パラメータ入力画面において、これらパラメータDDM、SDM、Multi、W/L、ROWにそれぞれ任意の数値を設定することで、マルチ素子回路を生成するためのパラメータ設定が行われる。 In this embodiment, as shown in the left diagram of FIG. 2, the NMOS circuit symbol whose parameters can be set is a terminal name G (Gate) beside each terminal portion of the NMOS circuit symbol standardized by JIS. , D (Drain), and S (Source) are displayed, and the parameter name “DDM (number of drain end side formations) = <DDM>” is displayed on the right side of the D terminal, and the parameter name “SDM” is displayed on the right side of the S terminal. (Number of source end side formations) = <SDM> ”, parameter name“ W (channel width) / L (channel length) = <W> / <L> ”and parameter name between the top and bottom of DDM and SDM “Multi (number of consecutive formations) = <Multi>” and the parameter name “ROW = <ROW>” are displayed. On the parameter input screen, by setting arbitrary numerical values for these parameters DDM, SDM, Multi, W / L, and ROW, parameter settings for generating a multi-element circuit are performed.

パラメータ判定部22は、パラメータ設定部20でパラメータ設定可能な回路シンボルに対して設定された設定内容が正しいか誤りかを、予め設定された正誤判定ルールに従って判定する機能を有している。

パラメータ修正部24は、パラメータ判定部22において、設定内容に誤りがあると判定されたときに、誤りのあった設定内容を、予め設定された修正ルールに従って修正する機能を有している。

The

The

更に、編集モード2において、回路パターン編集部14で編集された編集内容に基づき、編集された回路シンボルに対して設定されたパラメータを修正する機能を有している。

接続関係情報生成部26は、回路パターン編集部14でレイアウトされて構成された回路の接続関係情報を生成する機能と、予め設定されたルールに基づきパラメータ設定部20で設定されたパラメータに基づきマルチ素子回路の接続関係情報を生成する機能とを有している。生成された接続関係情報は、回路図情報記憶部28に記憶される。本実施の形態においては、更に、生成された接続関係情報のうちマルチ素子回路の接続関係情報は、回路表示情報生成部16に出力される。ここで、接続関係情報は、各回路素子(セル)の接続関係をテキストなどで表現した情報(ネットリストなど)である。

Further, in the

The connection relation

例えば、MOSトランジスタの回路シンボルに対してパラメータが設定された場合、予め設定されたルールに基づき、設定パラメータに応じた複数のMOSトランジスタとダミーMOSトランジスタとによって構成されるマルチ素子回路の各MOSトランジスタのゲート端子、ソース端子、ドレイン端子と他の回路素子(電源端子、接地端子などを含む)との接続関係が記述された接続関係情報が生成される。 For example, when a parameter is set for a circuit symbol of a MOS transistor, each MOS transistor of a multi-element circuit configured by a plurality of MOS transistors and a dummy MOS transistor according to a set parameter based on a preset rule The connection relationship information describing the connection relationship between the gate terminal, the source terminal, the drain terminal and other circuit elements (including the power supply terminal, the ground terminal, etc.) is generated.

なお、本実施の形態においては、NMOSのマルチ素子回路については、そのダミーNMOSのゲート端子を接地端子に接続すると共に、ダミーNMOSのNMOS本体部に接続されていない端子をフローティングにする接続関係情報を自動的に生成するルールが設定されている。更に、PMOSのマルチ素子回路については、そのダミーPMOSのゲート端子を電源端子に接続すると共に、ダミーPMOSのPMOS本体部に接続されていない端子をフローティングにする接続関係情報を自動的に生成するルールが設定されている。 In the present embodiment, for the NMOS multi-element circuit, connection information for connecting the gate terminal of the dummy NMOS to the ground terminal and floating the terminal not connected to the NMOS main body of the dummy NMOS is provided. A rule that automatically generates is set. Further, for a PMOS multi-element circuit, a rule for automatically generating connection relation information for connecting the gate terminal of the dummy PMOS to the power supply terminal and floating the terminal not connected to the PMOS main body of the dummy PMOS. Is set.

回路図情報記憶部28は、記憶装置(後述)の所定の記憶領域に構成されており、回路パターン編集部14によってレイアウトされた回路の情報や、接続関係情報生成部26で生成された接続関係情報などが記憶される。

以上の構成によって、回路図表示制御部18は、表示情報に基づき表示装置の表示制御を行ない、シンボル回路図又はパターンレイアウト図を表示装置の表示画面上に表示する。

The circuit diagram

With the above configuration, the circuit diagram

例えば、NMOSの回路シンボルに対してパラメータ設定をした場合のマルチ素子回路を示す回路シンボルは、図2の左図に示すように、本体NMOSの回路シンボルに対して、そのドレイン端子にダミーNMOSが接続されていることを示す■記号と、そのソース端子にダミーNMOSが接続されていることを示す■記号とが付加された回路シンボルが表示装置の表示画面上に表示される。 For example, a circuit symbol indicating a multi-element circuit when parameters are set for an NMOS circuit symbol is a dummy NMOS at the drain terminal of the main body NMOS circuit symbol as shown in the left diagram of FIG. A circuit symbol to which a ■ symbol indicating connection and a ■ symbol indicating that a dummy NMOS is connected to its source terminal is displayed on the display screen of the display device.

なお、図2の右図は、左図の回路シンボルに設定されたパラメータに基づき生成された接続関係情報を回路シンボルとパラメータ情報とによってイメージ化した回路図である。NMOSのマルチ素子回路は、本体NMOSの回路シンボルと、そのドレイン端子に接続されたダミーNMOSの回路シンボルと、そのソース端子に接続されたダミーNMOSの回路シンボルと、接地端子の回路シンボルとを含んで構成される回路図となる。 The right diagram in FIG. 2 is a circuit diagram in which connection relation information generated based on the parameters set in the circuit symbol in the left diagram is imaged by the circuit symbol and the parameter information. The NMOS multi-element circuit includes a body NMOS circuit symbol, a dummy NMOS circuit symbol connected to its drain terminal, a dummy NMOS circuit symbol connected to its source terminal, and a ground terminal circuit symbol. Is a circuit diagram composed of

具体的に、本体NMOSのドレイン及びソースにそれぞれダミーNMOSのドレイン及びソースがそれぞれ接続され、ダミーNMOSの本体NMOSに接続されていない端子はフローティング状態となり、ダミーNMOSのゲート端子は接地端子に接続されている。更に、各回路シンボルの右横には、各種パラメータ名と、その設定値とが表示されている。 Specifically, the drain and source of the dummy NMOS are connected to the drain and source of the main NMOS, respectively, the terminal not connected to the main NMOS of the dummy NMOS is in a floating state, and the gate terminal of the dummy NMOS is connected to the ground terminal. ing. Further, on the right side of each circuit symbol, various parameter names and their set values are displayed.

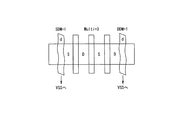

一方、NMOSの回路シンボルに対してパラメータ設定をした場合のマルチ素子回路のパターンレイアウト図は、図3に示すように、マスクシンボルによって形成された、本体NMOS(Multi=3)とダミーNMOS(DDM=1、SDM=1)のパターンレイアウトから構成されるパターンレイアウト図が表示装置の表示画面上に表示される。

ここで、図3は、NMOSで構成されたマルチ素子回路のパターンレイアウト図の一例を示す図である。

On the other hand, the pattern layout diagram of the multi-element circuit when parameters are set for the NMOS circuit symbol, as shown in FIG. 3, is the body NMOS (Multi = 3) and dummy NMOS (DDM) formed by the mask symbol. = 1, SDM = 1), a pattern layout diagram composed of the pattern layout is displayed on the display screen of the display device.

Here, FIG. 3 is a diagram showing an example of a pattern layout diagram of a multi-element circuit composed of NMOS.

具体的に、ダミーも含めたNMOS5つ分のソース領域とドレイン領域が同じ階層に行方向に交互に連続して形成され(隣り合う素子でソース領域とドレイン領域を共有)、更に、この階層よりも1つ上の階層における各ドレイン領域と各ソース領域との間の位置に各NMOSのゲート領域が形成された構成となっている。本体NMOS部は、中央の3つ分のNMOSから構成され、本体NMOS部の両端のNMOSが、それぞれダミーNMOSとなる。本実施の形態では、マルチ素子回路のパターンレイアウト図においてダミーNMOSが目視ですぐ判別できるようにするために、表示形状に関するルールに従って、そのゲート(図3中の「d」の付されたゲート)の形状を本体NMOS部のゲートの形状と異なる形状で表示している。 Specifically, source regions and drain regions for five NMOSs including a dummy are formed alternately and continuously in the row direction in the same hierarchy (the adjacent elements share the source region and the drain region). Also, the gate region of each NMOS is formed at a position between each drain region and each source region in the next higher layer. The main body NMOS unit is composed of three NMOSs in the center, and the NMOSs at both ends of the main body NMOS unit are dummy NMOSs. In the present embodiment, in order to allow the dummy NMOS to be immediately discriminated visually in the pattern layout diagram of the multi-element circuit, its gate (a gate indicated by “d” in FIG. 3) according to the rules regarding the display shape. Is shown in a shape different from the shape of the gate of the main body NMOS portion.

ここで、回路図設計装置100は、半導体集積回路に係る回路図の設計のための各種制御や前記回路記号選択部12、回路パターン編集部14、回路表示情報生成部16、回路図表示制御部18、パラメータ設定部20、パラメータ判定部22、パラメータ修正部24、接続関係情報生成部26などの各機能をソフトウェア上で、すなわち専用のプログラムを実行することで実現するためのコンピュータシステムを備えており、そのハードウェア構成は、図4に示すように、各種制御や演算処理を担う中央演算処理装置であるCPU(Central Processing Unit)60と、主記憶装置(Main Storage)を構成するRAM(Random Access Memory)62と、読み出し専用の記憶装置であるROM(Read Only Memory)64とを含み、これらの間をPCI(Peripheral Component Interconnect)バス等からなる各種内外バス68で接続すると共に、このバス68に入出力インターフェース(I/F)66を介して、HDD(Hard Disk Drive)などの記憶装置(Secondary Storage)70や、LCDモニター等の表示装置72、マウス、キーボード、タブレットなどの入力装置74などを接続した構成となっている。

Here, the circuit

そして、電源を投入すると、ROM64などに記憶されたBIOSなどのシステムプログラムが、ROM64に、予め記憶された各種専用のコンピュータプログラムを、あるいは、CD−ROMやDVD−ROM、フレキシブルディスク(FD)などの記録媒体を介して、またはインターネットなどの通信ネットワークLを介して、記憶装置70にインストールされた各種専用のコンピュータプログラムを、同じくRAM62にロードし、そのRAM62にロードされたプログラムに記述された命令に従ってCPU60が各種リソースを駆使して回路図の設計を実際に行うための各種制御及び演算処理を行うことで前述したような各部の機能をソフトウェア上で実現できるようになっている。

When the power is turned on, a system program such as BIOS stored in the

次に、図5に基づき、回路図設計装置100におけるマルチ素子回路の生成処理の流れを説明する。

ここで、図5は、マルチ素子回路の生成処理を示すフローチャートである。

CPU60によって、専用のコンピュータプログラムの実行が開始されると、図5に示すように、まず、ステップS100に移行し、回路記号選択部12において、入力装置74を介した利用者からの操作入力に基づき、回路シンボルの選択画面又はレイアウト領域にレイアウト(表示)されたシンボル回路図から、回路シンボルが選択されたか否かを判定し、選択されたと判定した場合(Yes)は、ステップS102に移行し、そうでない場合(No)は、選択されるまで判定処理を繰り返す。

Next, the flow of the multi-element circuit generation process in the circuit

Here, FIG. 5 is a flowchart showing a multi-element circuit generation process.

When the execution of the dedicated computer program is started by the

ステップS102に移行した場合は、パラメータ設定部20において、選択された回路シンボルがマルチ素子回路対応の回路シンボルか否かを判定し、対応の回路シンボルであると判定した場合(Yes)は、ステップS104に移行し、そうでない場合(No)は、ステップS100に移行する。

ステップS104に移行した場合は、パラメータ設定部20において、入力装置74を介した利用者からの操作入力に基づき、選択された回路シンボルに対してパラメータの入力指示があったか否かを判定し、入力指示があったと判定した場合(Yes)は、ステップS106に移行し、そうでない場合(No)は、ステップS100に移行する。

When the process proceeds to step S102, the

When the process proceeds to step S104, the

ステップS106に移行した場合は、パラメータ設定部20において、表示装置にパラメータの入力画面を表示させて、ステップS108に移行する。

このパラメータの入力画面は、例えば、選択された回路シンボルがMOSトランジスタであれば、本体MOSの連続形成数(Multi)、ダミーMOSの形成数(DDM,SDM)、各MOSのチャンネルサイズ(W/L)、マルチ素子回路の列方向の連続形成数(ROW)などのパラメータ設定項目と、各項目に対する数値入力用のボックスとが表示された画面となる。

When the process proceeds to step S106, the

For example, if the selected circuit symbol is a MOS transistor, the input screen for this parameter is the number of continuous formations of the main body MOS (Multi), the number of formations of the dummy MOSs (DDM, SDM), the channel size of each MOS (W / L), a screen on which parameter setting items such as the number of continuous formations (ROW) in the column direction of the multi-element circuit, and boxes for numerical input for each item are displayed.

ステップS108では、パラメータ判定部22において、パラメータの入力が完了したか否かを判定し、完了したと判定した場合(Yes)は、ステップS110に移行し、そうでない場合(No)は、パラメータの入力が完了するまで判定処理を繰り返す。

ステップS110に移行した場合は、パラメータ判定部22において、パラメータ判定処理を実行して、ステップS112に移行する。

In step S108, the

When the process proceeds to step S110, the

ステップS112では、パラメータ修正部24において、ステップS110の判定結果に基づき、設定値は正しいか否かを判定し、正しいと判定した場合(Yes)は、ステップS114に移行し、そうでない場合(No)は、ステップS122に移行する。

ステップS114に移行した場合は、接続関係情報生成部26において、選択された回路シンボルに対して設定されたパラメータに基づき、該回路シンボルの回路素子によって構成されるマルチ素子回路の接続関係情報を生成し、該生成した接続関係情報を回路表示情報生成部16に出力して、ステップS116に移行する。

In step S112, the

When the process proceeds to step S114, the connection relation

ステップS116では、回路表示情報生成部16において、マルチ素子回路の表示方法の決定処理を実行して、ステップS118に移行する。

ステップS118では、回路表示情報生成部16において、ステップS114で生成された接続関係情報と、ステップS116で決定された表示方法とに基づき、マルチ素子回路を示す回路シンボルの表示情報を生成し、これを表示要求と共に回路図表示制御部18に出力して、ステップS120に移行する。

In step S116, the circuit display

In step S118, the circuit display

ステップS120では、回路図表示制御部18において、表示情報に基づき、表示装置に、選択した回路シンボルに対するマルチ素子回路を示す回路シンボルを表示させて、ステップS100に移行する。

なお、本実施の形態においては、回路表示情報生成部16に対して、選択した回路シンボルに対するマルチ素子回路を示すパターンレイアウト図の表示指示を行うことができる。この表示指示を行うことによって、回路表示情報生成部16は、ステップS114で生成された接続関係情報と、ステップS116で決定された表示方法とに基づき、マルチ素子回路のパターンレイアウト図の表示情報を生成し、回路図表示制御部18は、この表示情報に基づき、レイアウト領域内又は別ウィンドウにマルチ素子回路のパターンレイアウト図を表示する。

In step S120, the circuit diagram

In the present embodiment, it is possible to instruct the circuit display

一方、ステップS112において、パラメータの設定値が正しくない(誤り)と判定され、ステップS122に移行した場合は、パラメータ修正部24において、パラメータ修正処理を実行して誤った設定値を修正し、ステップS114に移行する。

On the other hand, if it is determined in step S112 that the parameter setting value is not correct (error) and the process proceeds to step S122, the

次に、図6に基づき、回路図設計装置100のパラメータ判定部22におけるステップS110のパラメータ判定処理の流れを説明する。

ここで、図6は、パラメータ判定部22におけるMOSトランジスタの回路シンボルに対するパラメータ判定処理の一例を示すフローチャートである。

ステップS110に移行し、パラメータ判定処理が開始されると、図6に示すように、まず、ステップS200に移行し、パラメータ判定部22において、パラメータROWの値は「2」以上か否かを判定し、「2」以上であると判定した場合(Yes)は、ステップS202に移行し、そうでない場合(No)は、ステップS220に移行する。

Next, based on FIG. 6, the flow of the parameter determination process in step S110 in the

FIG. 6 is a flowchart showing an example of parameter determination processing for the circuit symbol of the MOS transistor in the

When the process proceeds to step S110 and the parameter determination process is started, as shown in FIG. 6, first, the process proceeds to step S200, where the

ステップS202に移行した場合は、パラメータ判定部22において、パラメータMultiの設定値をパラメータROWの設定値で除算して、ステップS204に移行する。

ステップS204では、パラメータ判定部22において、ステップS202の除算結果は割り切れた値か否かを判定し、割り切れた値であると判定した場合(Yes)は、ステップS206に移行し、そうでない場合(No)は、ステップS218に移行する。

When the process proceeds to step S202, the

In step S204, the

ステップS206に移行した場合は、パラメータ判定部22において、パラメータColumnに、ステップS202の除算結果を設定して、ステップS208に移行する。

ステップS208では、パラメータ判定部22において、パラメータColumnの設定値は奇数か否かを判定し、奇数であると判定した場合(Yes)は、ステップS210に移行し、そうでない場合(No)は、ステップS216に移行する。

When the process proceeds to step S206, the

In step S208, the

ステップS210に移行した場合は、パラメータDDM又はSDMに、パラメータROWの設定をN倍(Nは1以上の整数)した数値とは異なる値が設定されているか否かを判定し、設定されていると判定した場合(Yes)は、ステップS212に移行し、そうでない場合(No)は、ステップS214に移行する。

ステップS212に移行した場合は、パラメータ判定部22において、第4の設定内容による誤りと判定し、該判定結果をパラメータ修正部24に出力して、一連の処理を終了し元の処理に復帰する。

When the process proceeds to step S210, it is determined whether or not the parameter DDM or SDM is set to a value different from the value obtained by multiplying the parameter ROW by N (N is an integer of 1 or more). If determined (Yes), the process proceeds to step S212. If not (No), the process proceeds to step S214.

When the process proceeds to step S212, the

一方、ステップS214に移行した場合は、パラメータ判定部22において、設定値は正しいと判定し、該判定結果をパラメータ修正部24に出力して、一連の処理を終了し元の処理に復帰する。

また、ステップS208において、パラメータColumnの設定値が偶数で、ステップS216に移行した場合は、パラメータ判定部22において、パラメータDDM又はSDMに、パラメータROWの設定値をM倍(Mは2以上の偶数)した値とは異なる値が設定されているか否かを判定し、設定されていると判定した場合(Yes)は、ステップS218に移行し、そうでない場合(No)は、ステップS214に移行する。

On the other hand, when the process proceeds to step S214, the

In step S208, when the setting value of the parameter Column is an even number and the process proceeds to step S216, the

ステップS218に移行した場合は、パラメータ判定部22において、第5の設定内容による誤りと判定し、該判定結果をパラメータ修正部24に出力して、一連の処理を終了し元の処理に復帰する。

一方、ステップS204において、ステップS202の除算結果が割り切れずにステップS220に移行した場合は、パラメータColumnに除算結果の小数部分を切り捨てた値を設定して、ステップS208に移行する。

When the process proceeds to step S218, the

On the other hand, in step S204, if the division result in step S202 is not divisible and the process proceeds to step S220, the value obtained by rounding off the decimal part of the division result is set in the parameter Column, and the process proceeds to step S208.

また、ステップS200において、パラメータROWの設定値が1で(本実施の形態では1未満の数値は設定禁止とする)、ステップS222に移行した場合は、パラメータ判定部22において、パラメータMultiが偶数で且つ本体MOS部の両端はソース領域か否かを判定し、偶数且つソース領域であると判定した場合(Yes)は、ステップS224に移行し、そうでない場合(No)は、ステップS232に移行する。

In step S200, when the setting value of the parameter ROW is 1 (a numerical value less than 1 is prohibited in this embodiment) and the process proceeds to step S222, the

ステップS224に移行した場合は、パラメータDDM及びSDMの双方に「0」以外の数値が設定されているか否かを判定し、設定されていると判定した場合(Yes)は、ステップS226に移行し、そうでない場合(No)は、ステップS228に移行する。

ステップS226に移行した場合は、パラメータ判定部22において、第1の設定内容による誤りと判定し、該判定結果をパラメータ修正部24に出力して、一連の処理を終了し元の処理に復帰する。

When the process proceeds to step S224, it is determined whether or not a numerical value other than “0” is set in both parameters DDM and SDM. If it is determined that the parameter is set (Yes), the process proceeds to step S226. If not (No), the process proceeds to step S228.

When the process proceeds to step S226, the

一方、ステップS228に移行した場合は、パラメータ判定部22において、パラメータDDMに「0」が設定され、パラメータSDMに所定の偶数値が設定されているか否かを判定し、設定されていると判定した場合(Yes)は、ステップS214に移行し、そうでない場合(No)は、ステップS230に移行する。

ステップS230に移行した場合は、パラメータ判定部22において、第2の設定内容による誤りと判定し、該判定結果をパラメータ修正部24に出力して、一連の処理を終了し元の処理に復帰する。

On the other hand, when the process proceeds to step S228, the

When the process proceeds to step S230, the

また、ステップS222において、パラメータMultiが奇数又は両端部がソース領域じゃなくてステップS232に移行した場合は、パラメータ判定部22において、パラメータMultiが偶数で且つ本体MOS部の両端はドレイン領域か否かを判定し、偶数且つドレイン領域であると判定した場合(Yes)は、ステップS234に移行し、そうでない場合(No)は、ステップS214に移行する。

In step S222, if the parameter Multi is odd or both ends are not the source region and the process proceeds to step S232, the

ステップS234に移行した場合は、パラメータ判定部22において、パラメータDDM及びSDMの双方に「0」以外の数値が設定されているか否かを判定し、設定されていると判定した場合(Yes)は、ステップS226に移行し、そうでない場合(No)は、ステップS236に移行する。

ステップS236に移行した場合は、パラメータ判定部22において、パラメータSDMに「0」が設定され、パラメータDDMに所定の偶数値が設定されているか否かを判定し、設定されていると判定した場合(Yes)は、ステップS214に移行し、そうでない場合(No)は、ステップS238に移行する。

When the process proceeds to step S234, the

When the process proceeds to step S236, the

ステップS238に移行した場合は、パラメータ判定部22において、第3の設定内容による誤りと判定し、該判定結果をパラメータ修正部24に出力して、一連の処理を終了し元の処理に復帰する。

When the process proceeds to step S238, the

次に、図7に基づき、回路図設計装置100のパラメータ修正部24におけるステップS122のパラメータ修正処理の流れを説明する。

ここで、図7は、パラメータ修正部24における、MOSトランジスタに対するパラメータ修正処理を示すフローチャートである。

ステップS122に移行し、パラメータ修正処理が開始されると、図7に示すように、まず、ステップS300に移行し、パラメータ修正部24において、ステップS112の判定結果が第1の設定内容による誤り判定か否かを判定し、そうである場合(Yes)は、ステップS302に移行し、そうでない場合(No)は、ステップS308に移行する。

Next, the flow of the parameter correction process in step S122 in the

FIG. 7 is a flowchart showing parameter correction processing for the MOS transistor in the

When the process proceeds to step S122 and the parameter correction process is started, as shown in FIG. 7, the process first proceeds to step S300. If it is (Yes), the process proceeds to step S302. If not (No), the process proceeds to step S308.

ステップS302に移行した場合は、パラメータ修正部24において、本体MOS部の両端がソース領域か否かを判定し、そうである場合(Yes)は、ステップS304に移行し、そうでない場合(No)は、ステップS306に移行する。

ステップS304に移行した場合は、パラメータ修正部24において、パラメータDDMが「0」に且つパラメータSDMが所定の偶数値となるように修正して、一連の処理を終了し元の処理に復帰する。

When the process proceeds to step S302, the

When the process proceeds to step S304, the

一方、ステップS306に移行した場合は、パラメータ修正部24において、パラメータDDMが所定の偶数値に且つパラメータSDMが「0」となるように修正して、一連の処理を終了し元の処理に復帰する。

また、ステップS300において、第1の設定内容による誤り判定ではなく、ステップS308に移行した場合は、パラメータ修正部24において、ステップS112の判定結果が第2の設定内容による誤り判定か否かを判定し、そうである場合(Yes)は、ステップS310に移行し、そうでない場合(No)は、ステップS312に移行する。

On the other hand, when the process proceeds to step S306, the

Also, in step S300, if the error determination based on the first setting content is not performed but the process proceeds to step S308, the

ステップS310に移行した場合は、パラメータ修正部24において、パラメータSDMの設定値を所定の偶数値に修正して、一連の処理を終了し元の処理に復帰する。

一方、ステップS312に移行した場合は、パラメータ修正部24において、ステップS112の判定結果が第3の設定内容による誤り判定か否かを判定し、そうであると判定した場合(Yes)は、ステップS314に移行し、そうでない場合(No)は、ステップS316に移行する。

When the process proceeds to step S310, the

On the other hand, when the process proceeds to step S312, the

ステップS314に移行した場合は、パラメータ修正部24において、パラメータDDMを所定の偶数値に修正して、一連の処理を終了し元の処理に復帰する。

また、ステップS316に移行した場合は、パラメータ修正部24において、ステップS112の判定結果が第4の設定内容による誤り判定か否かを判定し、そうであると判定した場合(Yes)は、ステップS318に移行し、そうでない場合(No)は、ステップS320に移行する。

When the process proceeds to step S314, the

If the process proceeds to step S316, the

ステップS318に移行した場合は、パラメータ修正部24において、パラメータDDM及びSDMの設定値が双方ともROWの設定値をN倍にした数値となるようにこれら設定値を修正して、一連の処理を終了し元の処理に復帰する。

一方、ステップS320に移行した場合は、パラメータ修正部24において、本体MOS部の両端がソース領域か否かを判定し、そうである場合(Yes)は、ステップS322に移行し、そうでない場合(No)は、ステップS324に移行する。

When the process proceeds to step S318, the

On the other hand, when the process proceeds to step S320, the

ステップS322に移行した場合は,パラメータ修正部24において、パラメータDDMの設定値が「0」に且つパラメータSDMの設定値がパラメータROWの設定値をM倍した数値となるようにこれら設定値を修正して、一連の処理を終了し元の処理に復帰する。

また、ステップS324に移行した場合は、パラメータ修正部24において、パラメータSDMの設定値が「0」に且つパラメータDDMの設定値がパラメータROWの設定値をM倍した数値となるようにこれら設定値を修正して、一連の処理を終了し元の処理に復帰する。

When the process proceeds to step S322, the

When the process proceeds to step S324, the

次に、図8に基づき、回路図設計装置100の接続関係情報生成部26におけるステップS114の接続関係情報生成処理の流れを説明する。

ここで、図8は、接続関係情報生成部26における、MOSトランジスタに対する接続関係情報生成処理の一例を示すフローチャートである。

ステップS114に移行し、接続関係情報生成処理が開始されると、図8に示すように、まず、ステップS400に移行し、接続関係情報生成部26において、パラメータROWの設定値が「2」以上であるか否かを判定し、「2」以上であると判定した場合(Yes)は、ステップS402に移行し、そうでない場合(No)は、ステップS404に移行する。

Next, based on FIG. 8, the flow of the connection relationship information generation process of step S114 in the connection relationship

Here, FIG. 8 is a flowchart showing an example of connection relationship information generation processing for the MOS transistor in the connection relationship

When the process proceeds to step S114 and the connection relation information generation process is started, as shown in FIG. 8, first, the process proceeds to step S400, and the connection relation

ステップS402に移行した場合は、パラメータMulti、DDM、SDMの設定値をパラメータROWの設定値で除算した数値を、以降の接続関係生成処理に用いる各パラメータ値として設定して、ステップS404に移行する。

ステップS404では、接続関係情報生成部26において、パラメータDDMが「0」で且つパラメータSDMが「0」であるか否かを判定し、双方が「0」であると判定した場合(Yes)は、ステップS406に移行し、そうでない場合(No)は、ステップS414に移行する。

When the process proceeds to step S402, a numerical value obtained by dividing the setting values of the parameters Multi, DDM, and SDM by the setting value of the parameter ROW is set as each parameter value used for the subsequent connection relationship generation processing, and the process proceeds to step S404. .

In step S404, the connection relation

ステップS406に移行した場合は、接続関係情報生成部26において、パラメータMultiの値に基づき、ダミーMOS無しの本体MOS部のみのマルチ素子回路の接続関係情報を生成してRAM62に記憶し、ステップS408に移行する。

ステップS408では、接続関係情報生成部26において、パラメータROWの設定値が「2」以上であるか否かを判定し、「2」以上であると判定した場合(Yes)は、ステップS410に移行し、そうでない場合(No)は、ステップS412に移行する。

When the process proceeds to step S406, the connection relation

In step S408, the connection relationship

ステップS410に移行した場合は、接続関係情報生成部26において、パラメータROWの設定値に基づきRAM62に記憶された接続関係情報をマルチ素子回路列を構成する接続関係情報に補正して、ステップS412に移行する。

ステップS412では、接続関係情報生成部26において、生成した接続関係情報を、回路表示情報生成部16に出力すると共に回路図情報記憶部28に保存して、一連の処理を終了し元の処理に復帰する。

When the process proceeds to step S410, the connection relation

In step S412, the connection relation

一方、ステップS404において、パラメータSDM及びDDMの設定値の双方が「0」でなく、ステップS414に移行した場合は、接続関係情報生成部26において、選択された回路シンボルが、PMOSか否かを判定し、PMOSであると判定した場合(Yes)は、ステップS416に移行し、そうでない場合(No)は、ステップS430に移行する。

ステップS416に移行した場合は、接続関係情報生成部26において、パラメータMultiの設定値<Multi>に基づき、ダミーPMOSを付加していない状態の、<Multi>個のPMOSが連続して接続された構成の本体PMOS部だけのマルチ素子回路の接続関係情報を生成してRAM62に記憶し、ステップS418に移行する。

On the other hand, if both the setting values of the parameters SDM and DDM are not “0” in step S404 and the process proceeds to step S414, the connection relation

When the process proceeds to step S416, in the connection relation

ステップS418では、接続関係情報生成部26において、パラメータDDMの設定値は「1」以上か否かを判定し、「1」以上であると判定した場合(Yes)は、ステップS420に移行し、そうでない場合(No)は、ステップS422に移行する。

ステップS420に移行した場合は、接続関係情報生成部26において、パラメータDDMの設定値に基づき、本体PMOS部のドレイン端部にダミーPMOSを接続する情報を、RAM62に記憶された接続関係情報に追加して、ステップS422に移行する。

In step S418, the connection relation

When the process proceeds to step S420, the connection relation

ステップS422では、接続関係情報生成部26において、パラメータSDMの設定値は「1」以上か否かを判定し、「1」以上であると判定した場合(Yes)は、ステップS424に移行し、そうでない場合(No)は、ステップS426に移行する。

ステップS424に移行した場合は、接続関係情報生成部26において、本体PMOS部のソース端部にダミーPMOSを接続する情報を、RAM62に記憶された接続関係情報に追加して、ステップS426に移行する。

In step S422, the connection relation

When the process proceeds to step S424, the connection relation

ステップS426では、接続関係情報生成部26において、ダミーPMOSのゲート端子を電源端子に接続する情報を、RAM62に記憶された接続関係情報に追加して、ステップS428に移行する。

ステップS428では、接続関係情報生成部26において、ダミーPMOS又はダミーNMOSの接続されていない端子をフローティングにする情報を、RAM62に記憶された接続関係情報に追加して、ステップS408に移行する。

In step S426, the connection relation

In step S428, in the connection relation

一方、ステップS414において、選択された回路シンボルがPMOSではなくてNMOSであり、ステップS430に移行した場合は、接続関係情報生成部26において、パラメータMultiの設定値<Multi>に基づき、ダミーNMOSを付加していない状態の、<Multi>個のNMOSが連続して接続された構成の本体NMOS部だけのマルチ素子回路の接続関係情報を生成してRAM62に記憶し、ステップS432に移行する。

On the other hand, if the selected circuit symbol is not PMOS but NMOS in step S414 and the process proceeds to step S430, the connection relation

ステップS432では、接続関係情報生成部26において、パラメータDDMの設定値は「1」以上か否かを判定し、「1」以上であると判定した場合(Yes)は、ステップS434に移行し、そうでない場合(No)は、ステップS436に移行する。

ステップS434に移行した場合は、接続関係情報生成部26において、パラメータDDMの設定値に基づき、本体NMOS部のドレイン端部にダミーNMOSを接続する情報を、RAM62に記憶された接続関係情報に追加して、ステップS436に移行する。

In step S432, the connection relation

When the process proceeds to step S434, the connection relation

ステップS436では、接続関係情報生成部26において、パラメータSDMの設定値は「1」以上か否かを判定し、「1」以上であると判定した場合(Yes)は、ステップS438に移行し、そうでない場合(No)は、ステップS440に移行する。

ステップS438に移行した場合は、接続関係情報生成部26において、本体NMOS部のソース端部にダミーNMOSを接続する情報を、RAM62に記憶された接続関係情報に追加して、ステップS440に移行する。

In step S436, the connection relation

When the process proceeds to step S438, the connection relation

ステップS440では、接続関係情報生成部26において、ダミーNMOSのゲート端子を電源端子に接続する情報を、RAM62に記憶された接続関係情報に追加して、ステップS428に移行する。

なお、上記生成されたマルチ素子回路の接続関係情報は、最終的に、レイアウト領域にレイアウトされた回路全体の接続関係情報における、対応する回路シンボルに対応付けられて回路図情報記憶部28に保存されるか、回路全体の接続関係情報における、対応する回路シンボルの接続関係情報を置き換えて回路図情報記憶部28に保存される。

In step S440, the connection relation

The generated connection relationship information of the multi-element circuit is finally stored in the circuit diagram

次に、図9に基づき、回路図設計装置100の回路表示情報生成部16におけるステップ116の、回路シンボルの表示方法を決定する処理である表示方法決定処理の流れを説明する。

ここで、図9は、回路表示情報生成部16における表示方法決定処理を示すフローチャートである。

Next, based on FIG. 9, the flow of the display method determination process, which is the process of determining the circuit symbol display method, in step 116 in the circuit display

Here, FIG. 9 is a flowchart showing a display method determination process in the circuit display

ステップS116に移行し、表示方法決定処理が開始されると、図9に示すように、まず、ステップS500に移行し、回路表示情報生成部16において、表示形状に関するルールがあるか否かを判定し、表示形状に関するルールがあると判定した場合(Yes)は、ステップS502に移行し、そうでない場合(No)は、ステップS504に移行する。

ステップS502に移行した場合は、回路表示情報生成部16において、表示形状に関するルールに基づきマルチ素子回路の回路シンボルの表示形状を決定して、ステップS504に移行する。

When the process proceeds to step S116 and the display method determination process is started, as shown in FIG. 9, first, the process proceeds to step S500, and the circuit display

When the process proceeds to step S502, the circuit display

ステップS504では、回路表示情報生成部16において、表示色に関するルールがあるか否かを判定し、表示色に関するルールがあると判定した場合(Yes)は、ステップS506に移行し、そうでない場合(No)は、一連の処理を終了し元の処理に復帰する。

ステップS506に移行した場合は、回路表示情報生成部16において、表示色に関するルールに基づき、マルチ素子回路の回路シンボルの表示色を決定して、一連の処理を終了し元の処理に復帰する。

In step S504, the circuit display

When the process proceeds to step S506, the circuit display

次に、図10に基づき、回路図設計装置100におけるパターンレイアウト図の編集処理の流れを説明する。

ここで、図10は、回路図設計装置100におけるパターンレイアウト図の編集処理を示すフローチャートである。

CPU60によって専用のプログラムが実行され、パターンレイアウト図の編集処理が開始されると、図10に示すように、まず、ステップS600に移行し、回路表示情報生成部16において、入力装置74を介した利用者からの指定接続関係情報のパターンレイアウト図の表示指示があったか否かを判定し、あったと判定した場合(Yes)は、回路表示情報生成部16において、指定接続関係情報に基づき、そのパターンレイアウト図の表示情報を生成し、該生成した表示情報を表示要求と共に回路図表示制御部18に出力する。更に、回路図表示制御部18において、入力された表示情報に基づき表示装置72を制御して、表示画面上にパターンレイアウト図を表示して、ステップS604に移行する。

Next, the flow of the pattern layout diagram editing process in the circuit

Here, FIG. 10 is a flowchart showing the editing process of the pattern layout diagram in the circuit

When the dedicated program is executed by the

ステップS604では、回路パターン編集部14において、入力装置74を介した利用者からのレイアウト編集指示があったか否かを判定し、あったと判定した場合(Yes)は、ステップS606に移行し、そうでない場合(No)は、ステップS614に移行する。

本実施の形態において、編集指示内容としては、具体的に、パターンレイアウト図における、マルチ素子回路又は複数のマルチ素子回路列の列数の変更指示、マルチ素子回路又はマルチ素子回路列の各本体MOS部の連続形成数の変更指示、マルチ素子回路を構成するMOSトランジスタのPMOSからNMOSへ又はNMOSからPMOSへのいずれかへの変換指示、複数のマルチ素子回路又は複数のマルチ素子回路列の共有合成指示、複数のマルチ素子回路又は複数のマルチ素子回路列の所定合体構成(例えば、コモン・セントロイドなど)の合体合成指示などが可能である。

In step S604, the circuit

In the present embodiment, the editing instruction content specifically includes an instruction to change the number of columns of a multi-element circuit or a plurality of multi-element circuit columns in the pattern layout diagram, and each main body MOS of the multi-element circuit or multi-element circuit column. Instructions for changing the number of continuous formation of parts, instructions for conversion of MOS transistors constituting a multi-element circuit from either PMOS to NMOS or NMOS to PMOS, shared synthesis of multiple multi-element circuits or multiple multi-element circuit arrays An instruction, an instruction for merging and synthesizing a predetermined merging configuration (for example, a common centroid, etc.) of a plurality of multi-element circuits or a plurality of multi-element circuit arrays can be performed.

ステップS606に移行した場合は、回路パターン編集部14、回路表示情報生成部16、回路図表示制御部18において、編集指示に応じてパターンレイアウト図のレイアウトを変更して、ステップS608に移行する。

ステップS608では、パラメータ修正部24において、ステップS606の編集結果に基づき、マルチ素子回路が編集されたか否かを判定し、編集されたと判定した場合(Yes)は、ステップS610に移行し、そうでない場合(No)は、ステップS612に移行する。

When the process proceeds to step S606, the circuit

In step S608, the

ステップS610に移行した場合は、パラメータ修正部24において、ステップS606の編集結果に基づき、編集された回路シンボルに対するパラメータを修正して、ステップS612に移行する。

ステップS612では、接続関係情報生成部26において、ステップS606の編集結果及びステップS610のパラメータ修正結果に基づき接続関係情報を変更して、ステップS614に移行する。

When the process proceeds to step S610, the

In step S612, the connection relation

ステップS614では、回路図設計装置100において、パターンレイアウト図の編集処理の終了指示があったか否かを判定し、あったと判定した場合(Yes)は、ステップS616に移行し、そうでない場合(No)は、ステップS604に移行する。

ステップS616に移行した場合は、接続関係情報生成部26において、編集内容の反映された接続関係情報、パラメータ設定値などの回路図の情報を回路図情報記憶部28に記憶して、ステップS600に移行する。

In step S614, the circuit

When the process proceeds to step S616, the connection relationship

次に、図11に基づき、パターンレイアウト図の編集処理における、ステップS610のパラメータ修正処理の流れを説明する。

ここで、図11は、パラメータ修正部24の、パターンレイアウト図におけるMOSトランジスタのマルチ素子回路の編集処理に対するパラメータ修正処理の一例を示すフローチャートである。

Next, the flow of parameter correction processing in step S610 in the pattern layout diagram editing processing will be described with reference to FIG.

Here, FIG. 11 is a flowchart showing an example of parameter correction processing for the editing processing of the multi-element circuit of the MOS transistor in the pattern layout diagram of the

ステップS610に移行し、パターンレイアウト図におけるMOSトランジスタのマルチ素子回路の編集処理に対するパラメータ修正処理が開始されると、図11に示すように、まず、ステップS700に移行し、回路パターン編集部14において、MOSトランジスタから構成されたマルチ素子回路の列数が変更されたか否かを判定し、変更されたと判定した場合(Yes)は、その編集内容をパラメータ修正部24に通知して、ステップS706に移行し、そうでない場合(No)は、ステップS726に移行する。