JP2010039803A - インターフェース回路 - Google Patents

インターフェース回路 Download PDFInfo

- Publication number

- JP2010039803A JP2010039803A JP2008202634A JP2008202634A JP2010039803A JP 2010039803 A JP2010039803 A JP 2010039803A JP 2008202634 A JP2008202634 A JP 2008202634A JP 2008202634 A JP2008202634 A JP 2008202634A JP 2010039803 A JP2010039803 A JP 2010039803A

- Authority

- JP

- Japan

- Prior art keywords

- serial

- signal

- control unit

- transmission

- signal lines

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Information Transfer Systems (AREA)

Abstract

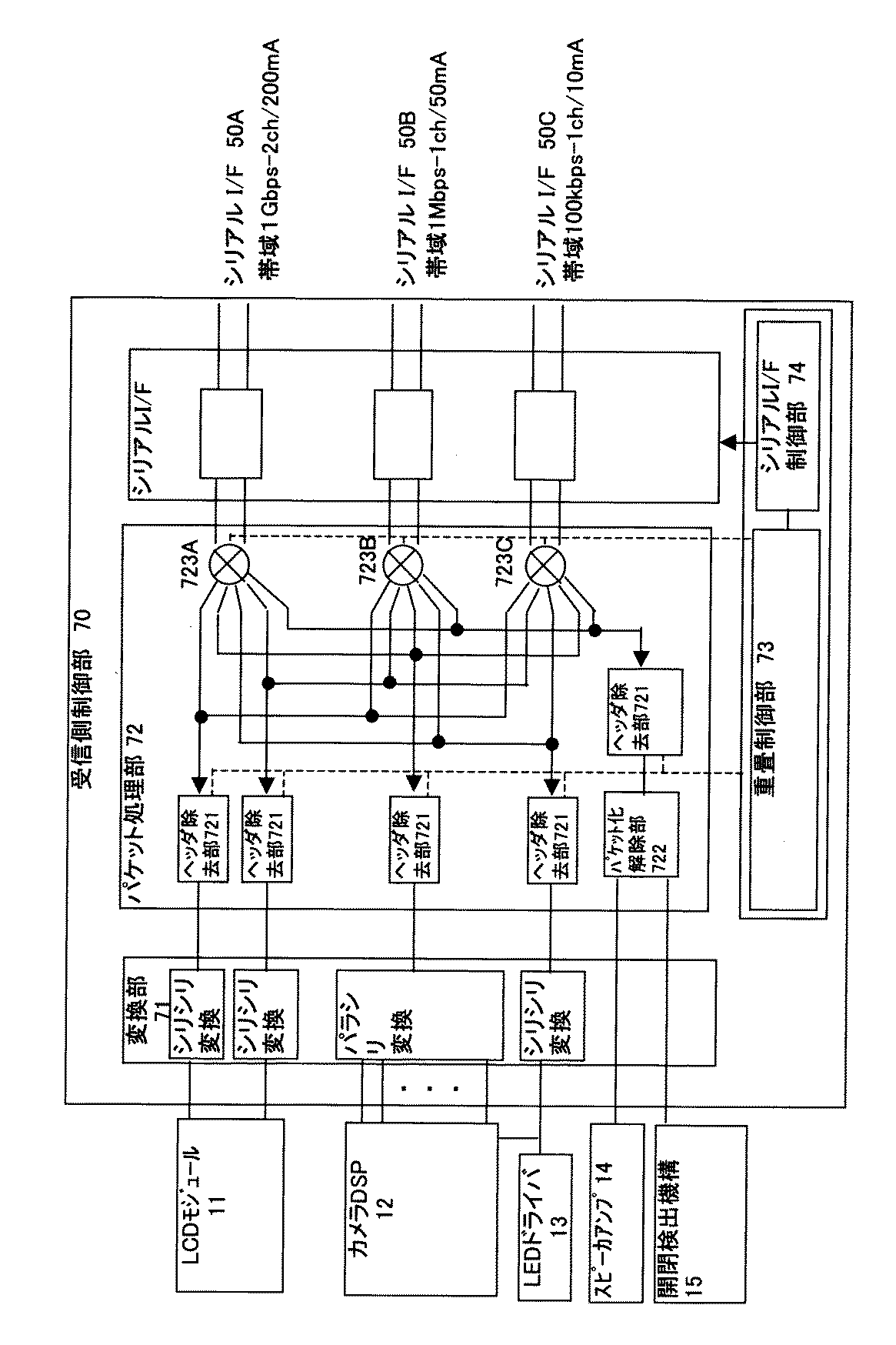

【解決手段】インターフェース回路は、帯域が異なる複数のシリアルインターフェースに対応する複数のシリアル信号線を備える。インターフェース回路は、当該シリアル信号線より多い本数の複数種類の信号線からなる信号伝送路上の途中に挿入され、送信側において、当該シリアル信号線より多い本数の信号線から入力される信号を重畳し、重畳信号の帯域に対応するシリアルインターフェースを選択して重畳信号を伝送し、受信側において、重畳信号を元の信号に戻して元の信号伝送路に出力する。

【選択図】図2

Description

特に、信号伝送に必要な帯域(所定の伝送条件)の変化に伴い、重畳信号を伝送するシリアルインターフェースを動的に変化させることで、帯域の変化に対して、最適なインターフェースを選択され、きめ細かい消費電流低減のための制御が達成される。また、消費電流削減のため、好ましくは、信号を伝送しないシリアルインターフェースへの電源供給を停止する。

帯域が異なる複数のシリアルインターフェースそれぞれに対応する複数のシリアル信号線と、

前記シリアル信号線の本数より多い複数の信号線から入力される複数種類の信号を重畳して、前記複数のシリアルインターフェースのうち、所定の伝送条件に従って該重畳信号を伝送するシリアルインターフェースを選択する送信側制御部と、

前記選択されたシリアルインターフェースのシリアル信号線を介して伝送された前記重畳信号を受信し、前記重畳信号を前記複数種類の信号に戻して、その種類毎の信号線に振り分ける受信側制御部とを備えることを特徴とするインターフェース回路。

(付記2)

付記1において、

前記送信側制御部は、前記所定の伝送条件の変化に伴い、前記重畳信号を伝送するシリアルインターフェースを変えることを特徴とするインターフェース回路。

付記1又は2において、

前記所定の伝送条件は、前記重畳信号の伝送に必要な帯域であることを特徴とするインターフェース回路。

付記3において、

前記重畳信号を伝送可能な帯域のシリアルインターフェースが複数ある場合、前記送信側制御部は、そのうちの最も帯域の狭いシリアルインターフェースを選択することを特徴とするインターフェース回路。

付記3において、

前記送信側制御部は、前記重畳信号を伝送しないシリアルインターフェースへの電源供給を停止することを特徴とするインターフェース回路。

表示部及びカメラを含む複数の機能部と、

前記複数の機能部を制御するプロセッサと、

各機能部それぞれと前記プロセッサ間を接続する複数の信号線と、

前記信号線の途中に挿入されるインターフェース回路とを備え、

前記インターフェース回路は、

前記複数の信号線の本数より少なく且つ帯域が異なる複数のシリアルインターフェースそれぞれに対応する複数のシリアル信号線と、

前記複数の信号線を介して入力される複数種類の信号を重畳して、該重畳信号を所定の伝送条件に従って前記複数のシリアルインターフェースのいずれかに振り分ける送信側制御部と、

前記振り分けられたシリアルインターフェースのシリアル信号線を介して伝送された前記重畳信号を受信し、前記重畳信号を前記複数種類の信号に戻して、その種類毎の信号線に振り分ける受信側制御部とを備えることを特徴とする携帯端末装置。

付記5において、

折りたたみ式携帯電話機であることを特徴とする携帯端末装置。

付記7において、

前記送信側制御部は、前記所定の伝送条件の変化に伴い、前記重畳信号を伝送するシリアルインターフェースを変えることを特徴とする携帯端末装置。

付記7において、

前記所定の伝送条件は、前記重畳信号の伝送に必要な帯域であることを特徴とする携帯端末装置。

付記9において、

前記重畳信号を伝送可能な帯域のシリアルインターフェースが複数ある場合、前記送信側制御部は、そのうちの最も帯域の狭いシリアルインターフェースを選択することを特徴とする携帯端末装置。

付記9において、

前記送信側制御部は、前記重畳信号を伝送しないシリアルインターフェースへの電源供給を停止することを特徴とする携帯端末装置。

Claims (5)

- 帯域が異なる複数のシリアルインターフェースそれぞれに対応する複数のシリアル信号線と、

前記シリアル信号線の本数より多い複数の信号線から入力される複数種類の信号を重畳して、前記複数のシリアルインターフェースのうち、所定の伝送条件に従って該重畳信号を伝送するシリアルインターフェースを選択する送信側制御部と、

前記選択されたシリアルインターフェースのシリアル信号線を介して伝送された前記重畳信号を受信し、前記重畳信号を前記複数種類の信号に戻して、その種類毎の信号線に振り分ける受信側制御部とを備えることを特徴とするインターフェース回路。 - 請求項1において、

前記送信側制御部は、前記所定の伝送条件の変化に伴い、前記重畳信号を伝送するシリアルインターフェースを変えることを特徴とするインターフェース回路。 - 請求項1又は2において、

前記所定の伝送条件は、前記重畳信号の伝送に必要な帯域であることを特徴とするインターフェース回路。 - 請求項3において、

前記重畳信号を伝送可能な帯域のシリアルインターフェースが複数ある場合、前記送信側制御部は、そのうちの最も帯域の狭いシリアルインターフェースを選択することを特徴とするインターフェース回路。 - 請求項3において、

前記送信側制御部は、前記重畳信号を伝送しないシリアルインターフェースへの電源供給を停止することを特徴とするインターフェース回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008202634A JP5168020B2 (ja) | 2008-08-06 | 2008-08-06 | インターフェース回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008202634A JP5168020B2 (ja) | 2008-08-06 | 2008-08-06 | インターフェース回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010039803A true JP2010039803A (ja) | 2010-02-18 |

| JP5168020B2 JP5168020B2 (ja) | 2013-03-21 |

Family

ID=42012278

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008202634A Expired - Fee Related JP5168020B2 (ja) | 2008-08-06 | 2008-08-06 | インターフェース回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5168020B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012038249A (ja) * | 2010-08-11 | 2012-02-23 | Buffalo Inc | サーバ装置、消費電力制御方法、ネットワークシステム |

| JP6090873B1 (ja) * | 2015-11-11 | 2017-03-08 | Necプラットフォームズ株式会社 | 情報処理装置およびシリアル通信データ分離多重変換方法 |

| JP2021145338A (ja) * | 2015-04-14 | 2021-09-24 | クアルコム,インコーポレイテッド | マルチモード変調を用いる向上した仮想gpio |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05114892A (ja) * | 1991-09-25 | 1993-05-07 | Fujitsu Ltd | 光インタフエース方式 |

| JP2000224229A (ja) * | 1999-01-29 | 2000-08-11 | Victor Co Of Japan Ltd | 伝送方法、送信装置及び受信装置 |

| JP2003131815A (ja) * | 2001-10-22 | 2003-05-09 | Fujitsu Media Device Kk | シリアルインタフェースのデータ転送システム |

| JP2004157590A (ja) * | 2002-11-01 | 2004-06-03 | Ricoh Co Ltd | 携帯型電子機器 |

| WO2006013641A1 (ja) * | 2004-08-04 | 2006-02-09 | Hitachi, Ltd. | 集積回路装置及び信号伝送システム |

| JP2006217327A (ja) * | 2005-02-04 | 2006-08-17 | Kddi Corp | 無線通信装置及び通信システム |

| JP2006270888A (ja) * | 2005-03-25 | 2006-10-05 | Fujitsu Ltd | 伝送装置 |

| JP2008090749A (ja) * | 2006-10-04 | 2008-04-17 | Kyocera Corp | 携帯電子機器および携帯電子機器の制御方法 |

-

2008

- 2008-08-06 JP JP2008202634A patent/JP5168020B2/ja not_active Expired - Fee Related

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05114892A (ja) * | 1991-09-25 | 1993-05-07 | Fujitsu Ltd | 光インタフエース方式 |

| JP2000224229A (ja) * | 1999-01-29 | 2000-08-11 | Victor Co Of Japan Ltd | 伝送方法、送信装置及び受信装置 |

| JP2003131815A (ja) * | 2001-10-22 | 2003-05-09 | Fujitsu Media Device Kk | シリアルインタフェースのデータ転送システム |

| JP2004157590A (ja) * | 2002-11-01 | 2004-06-03 | Ricoh Co Ltd | 携帯型電子機器 |

| WO2006013641A1 (ja) * | 2004-08-04 | 2006-02-09 | Hitachi, Ltd. | 集積回路装置及び信号伝送システム |

| JP2006217327A (ja) * | 2005-02-04 | 2006-08-17 | Kddi Corp | 無線通信装置及び通信システム |

| JP2006270888A (ja) * | 2005-03-25 | 2006-10-05 | Fujitsu Ltd | 伝送装置 |

| JP2008090749A (ja) * | 2006-10-04 | 2008-04-17 | Kyocera Corp | 携帯電子機器および携帯電子機器の制御方法 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012038249A (ja) * | 2010-08-11 | 2012-02-23 | Buffalo Inc | サーバ装置、消費電力制御方法、ネットワークシステム |

| JP2021145338A (ja) * | 2015-04-14 | 2021-09-24 | クアルコム,インコーポレイテッド | マルチモード変調を用いる向上した仮想gpio |

| JP6090873B1 (ja) * | 2015-11-11 | 2017-03-08 | Necプラットフォームズ株式会社 | 情報処理装置およびシリアル通信データ分離多重変換方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5168020B2 (ja) | 2013-03-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8341440B2 (en) | Power sharing between midspan and endspan for higher power PoE | |

| US7440443B2 (en) | Integrated universal network adapter | |

| JPH05227067A (ja) | 通信装置 | |

| US20090295230A1 (en) | Selective coupling of a powered component | |

| US6917792B2 (en) | System and method for controlling operation of mobile communication terminals capable of providing high-speed data rate service | |

| JP2004364237A (ja) | 時分割方式電力増幅モジュール | |

| CN105430606B (zh) | 一种分离式终端及其控制方法 | |

| CN103384199B (zh) | 一种供电方法、转换器及以太网供电系统 | |

| US20110150137A1 (en) | Architecture of multi-power mode serial interface | |

| US20060212624A1 (en) | Data transceiver using LVDS and a portable terminal employing the same and method therefor | |

| CN101371487A (zh) | 用于在通信总线和耦合到通信总线的设备之间传送多电平通信信号的总线接口和方法 | |

| JP5168020B2 (ja) | インターフェース回路 | |

| US20170010997A1 (en) | Usb control circuit with built-in bypass function | |

| EP3298760A1 (en) | Quality of service for a universal serial bus | |

| US20080214247A1 (en) | Communication method and communication system | |

| US10146728B2 (en) | USB control circuit with built-in signal repeater circuit | |

| US20070130290A1 (en) | Method and system for data transmission between a client and a server, wherein the client selects one out of several physical links | |

| CN201869164U (zh) | 一种小型化混传多工装置 | |

| EP3226428A1 (en) | Communication device and communication method | |

| KR101341406B1 (ko) | 스마트기기 및 컴퓨터의 다중 무선신호전송 시스템 | |

| CN111835487B (zh) | 一种信息处理方法、设备及计算机可读存储介质 | |

| CN205193955U (zh) | 一种vtm的音频信号转换器及vtm机 | |

| KR101830866B1 (ko) | 마이크 단자를 이용한 전원 통신 장치 | |

| CN212649622U (zh) | 一种支持双信号的无线传屏器 | |

| JP2006304086A (ja) | スイッチング電源、電力線搬送通信装置およびスイッチング電源制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110513 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120511 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120522 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120719 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121127 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121210 |

|

| LAPS | Cancellation because of no payment of annual fees |