JP2010021325A - 半導体装置の製造方法、及び半導体装置 - Google Patents

半導体装置の製造方法、及び半導体装置 Download PDFInfo

- Publication number

- JP2010021325A JP2010021325A JP2008179964A JP2008179964A JP2010021325A JP 2010021325 A JP2010021325 A JP 2010021325A JP 2008179964 A JP2008179964 A JP 2008179964A JP 2008179964 A JP2008179964 A JP 2008179964A JP 2010021325 A JP2010021325 A JP 2010021325A

- Authority

- JP

- Japan

- Prior art keywords

- film

- misfet

- strain

- strain film

- mask pattern

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/791—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions

- H10D30/792—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions comprising applied insulating layers, e.g. stress liners

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0167—Manufacturing their channels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0186—Manufacturing their interconnections or electrodes, e.g. source or drain electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

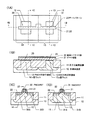

【解決手段】 PMOS及びNMOSを覆うように、引張歪膜を形成する。PMOSが配置された領域の引張歪膜を除去し、NMOSが配置された領域には引張歪膜を残す。全面に、圧縮歪膜を形成する。PMOSが配置された領域を覆い、NMOSが配置された領域は覆わないマスクを用いて圧縮歪膜の露出している部分を、厚さ方向の途中までエッチングする。PMOSが配置された領域を覆い、NMOSが配置された領域は覆わないマスクを用いて、NMOSが配置されている領域の圧縮歪膜を除去する。2種類のマスクの一方は、パターニングされた引張歪膜の少なくとも一部の縁と重なり、他方は、該縁から面内方向に隔てられている。圧縮歪膜を除去する際に、一方のマスクにのみ覆われていた領域に、圧縮歪膜の一部を残す。

【選択図】 図1−3

Description

半導体基板の第1の活性領域に第1導電型チャネルの第1のMISFETを形成し、該第1の活性領域から面内方向に隔てられた第2の活性領域に、該第1導電型とは逆の第2導電型チャネルの第2のMISFETを形成する工程と、

前記第1のMISFET及び第2のMISFETを覆うように、前記半導体基板の上に、第1の符号の歪を有する第1の歪膜を形成する工程と、

前記第1のMISFETが配置された領域の前記第1の歪膜が除去され、前記第2のMISFETが配置された領域に前記第1の歪膜が残るように、前記第1の歪膜をパターニングする工程と、

前記第1のMISFET、及びパターニングされた前記第1の歪膜を覆うように、前記半導体基板の上に、前記第1の符号とは反対符号の歪を有する第2の歪膜を形成する工程と、

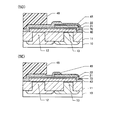

前記第1のMISFETが配置された領域を覆い、前記第2のMISFETが配置された領域は覆わない第1のマスクパターンを用いて前記第2の歪膜の露出している部分を、該第2の歪膜の厚さ方向の途中までエッチングして薄くする工程と、

前記第2の歪膜の一部を薄くした後、前記第1のMISFETが配置された領域を覆い、前記第2のMISFETが配置された領域は覆わない第2のマスクパターンを用いて、前記第2のMISFETが配置されている領域の前記第2の歪膜を除去する工程と

を有し、

前記第1のマスクパターンと第2のマスクパターンとの一方のマスクパターンは、パターニングされた前記第1の歪膜の少なくとも一部の縁と重なり、他方のマスクパターンは、該縁から面内方向に隔てられており、前記第2のMISFETが配置されている領域の前記第2の歪膜を除去する工程において、前記第1のマスクパターンと第2のマスクパターンとの一方にのみ覆われていた領域に、前記第2の歪膜の一部が残るように前記第2の歪膜を除去する。

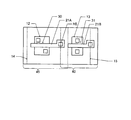

半導体基板の上に形成された第1導電型チャネルの第1のMISFET、及び該第1導電型とは逆の第2導電型チャネルの第2のMISFETと、

前記第2のMISFETが配置された領域を覆い、前記第1のMISFETが配置された領域は覆わず、第1の符号の歪を有する第1の歪膜と、

前記第1のMISFETが配置された領域を覆い、前記第2のMISFETが配置された領域は覆わず、前記第1の符号とは逆の第2の符号の歪を有する第2の歪膜と

を有し、

前記第2の歪膜の、前記第2のMISFET側の縁は、前記第1の歪膜の一部と重なり、前記第2の歪膜のうち、前記第1の歪膜と重なった部分、及び該重なった部分に連続する一部分の厚さが、前記第1のMISFETを覆っている部分の厚さよりも薄い。

・基板温度 400℃〜700℃

・圧力 13Pa〜53kPa(0.1〜400Torr)

・Si原料 SiH2Cl2+SiH4+Si2H6(5〜60sccm)

・N原料 NH3(500〜10000sccm)

・キャリアガス N2+Ar(500〜1000sccm)

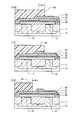

NMOS用活性領域13を覆うマスクパターン41を、感光性レジストにより形成する。マスクパターン41は、PMOS用活性領域12は覆わない。マスクパターン41の縁の一部は、PMOS用活性領域12とNMOS用活性領域13との間の素子分離絶縁膜の上を通過する。一例として、マスクパターン41の縁の一部は、PMOS用活性領域12からの距離と、NMOS用活性領域13からの距離とがほぼ等しくなる位置に配置される。

・ガス CHF3(20〜100sccm)+O2(100〜300sccm)

・圧力 6.7Pa〜27Pa(50〜200mTorr)

・RFパワー 100〜1000W

PMOSFET30が配置された領域の引張歪膜40が除去され、NMOSFET31が配置された領域には、引張歪膜40が残留する。引張歪膜40をエッチングした後、マスクパターン41を除去する。

・基板温度 400℃〜700℃

・圧力 13Pa〜53kPa(0.1〜400Torr)

・Si原料 SiH4(100〜1000sccm)

・N原料 NH3(500〜10000sccm)

・キャリアガス N2+Ar(500〜10000sccm)

・RFパワー 100〜1000W

図1Hに示すように、圧縮歪膜45の上に、PMOS用活性領域12を覆い、NMOS用活性領域13は覆わないマスクパターン46を、感光性レジストで形成する。マスクパターン46は、引張歪膜40の、PMOS用活性領域12側の一部と重なる。ただし、NMOS用活性領域13とは重ならない。引張歪膜40の縁からマスクパターン46の先端までの重なり幅Wの設計値は、位置ずれの許容範囲の最大値よりも広くされている。このため、引張歪膜40に対してマスクパターン46の位置ずれが生じても、両者の重なりが消滅することはない。

・ガス CF4(100〜500sccm)+O2(100〜500sccm)

・圧力 20〜100Pa

・マイクロ波パワー 200〜800W

これにより、マスクパターン46で覆われていない領域の圧縮歪膜45が薄くなる。エッチングする深さは、例えば、元の圧縮歪膜45の厚さの50%とする。その後、マスクパターン46を除去する。

・基板温度 400〜700℃

・ガス テトラエチルオルソシリケート(TEOS)

・圧力 13Pa〜53kPa

図1Nは、層間絶縁膜50にビアホールH1〜H5を形成した後の基板の平面図を示す。図1P〜図1Rは、それぞれ、図1Nの一点鎖線1P−1P、1Q−1Q、及び1R−1Rにおける断面図を示す。

・ガス C4F6(10〜30sccm)+O2(5〜20sccm)+Ar(500〜1000sccm)

・圧力 4.0〜11Pa(30〜80mTorr)

・RFパワー 2000〜4000W

引張歪膜40及び圧縮歪膜45のエッチング条件は、例えば下記の通りである。

・ガス CH3F(30〜100sccm)+O2(10〜100sccm)+Ar(100〜300sccm)

・圧力 6.7〜27Pa(50〜200mTorr)

・RFパワー 300〜1000W

ビアホールH1〜H5を形成した後、これらのビアホールH1〜H5内に、タングステン等の導電プラグ53を充填する。

11 素子分離絶縁膜

12 PMOS用活性領域

13 NMOS用活性領域

14 n型ウェル

15 p型ウェル

20 ゲート絶縁膜

21、21A、21B ゲート電極

22 金属シリサイド膜

23 ゲートパターン

30 PMOSFET

31 NMOSFET

40 引張歪膜

41、46、48、60、62 マスクパターン

45 圧縮歪膜

50 層間絶縁膜

53 導電プラグ

70 エッチング停止膜

H1〜H5 ビアホール

Claims (10)

- 半導体基板の第1の活性領域に第1導電型チャネルの第1のMISFETを形成し、該第1の活性領域から面内方向に隔てられた第2の活性領域に、該第1導電型とは逆の第2導電型チャネルの第2のMISFETを形成する工程と、

前記第1のMISFET及び第2のMISFETを覆うように、前記半導体基板の上に、第1の符号の歪を有する第1の歪膜を形成する工程と、

前記第1のMISFETが配置された領域の前記第1の歪膜が除去され、前記第2のMISFETが配置された領域に前記第1の歪膜が残るように、前記第1の歪膜をパターニングする工程と、

前記第1のMISFET、及びパターニングされた前記第1の歪膜を覆うように、前記半導体基板の上に、前記第1の符号とは反対符号の歪を有する第2の歪膜を形成する工程と、

前記第1のMISFETが配置された領域を覆い、前記第2のMISFETが配置された領域は覆わない第1のマスクパターンを用いて前記第2の歪膜の露出している部分を、該第2の歪膜の厚さ方向の途中までエッチングして薄くする工程と、

前記第2の歪膜の一部を薄くした後、前記第1のMISFETが配置された領域を覆い、前記第2のMISFETが配置された領域は覆わない第2のマスクパターンを用いて、前記第2のMISFETが配置されている領域の前記第2の歪膜を除去する工程と

を有し、

前記第1のマスクパターンと第2のマスクパターンとの一方のマスクパターンは、パターニングされた前記第1の歪膜の少なくとも一部の縁と重なり、他方のマスクパターンは、該縁から面内方向に隔てられており、前記第2のMISFETが配置されている領域の前記第2の歪膜を除去する工程において、前記第1のマスクパターンと第2のマスクパターンとの一方にのみ覆われていた領域に、前記第2の歪膜の一部が残るように前記第2の歪膜を除去する半導体装置の製造方法。 - 前記第1のマスクパターンが、パターニングされた前記第1の歪膜の前記縁と重なり、前記第2のマスクパターンは、該縁から面内方向に隔てられている請求項1に記載の半導体装置の製造方法。

- 前記第1のマスクパターンが、パターニングされた前記第1の歪膜の前記縁から面内方向に隔てられており、前記第2のマスクパターンは、該縁に重なっている請求項1に記載の半導体装置の製造方法。

- 前記第1の歪膜を形成した後パターニングする前に、前記第1の歪膜の上に、前記第2の歪膜とはエッチング耐性の異なるエッチング停止膜を形成し、

前記第1の歪膜をパターニングする際に、前記エッチング停止膜も該第1の歪膜と同一の平面形状にパターニングし、

前記第2の歪膜を除去する工程において、該第2の歪膜のエッチングレートが前記エッチング停止膜のエッチングレートよりも速い条件で該第2の歪膜のエッチングを行う請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。 - 前記第2のMISFETがn型チャネルMISFETである場合には、前記第1の歪膜が引張歪を有し、前記第2のMISFETがp型チャネルMISFETである場合には、前記第1の歪膜が圧縮歪を有する請求項1乃至4のいずれか1項に記載の半導体装置の製造方法。

- 前記第2の歪膜を除去する工程の後、さらに、

前記第1の歪膜及び第2の歪膜の上に、層間絶縁膜を形成する工程と、

前記第1のマスクパターンと前記第2のマスクパターンとの一方のマスクパターンには覆われていたが他方のマスクパターンには覆われていなかった領域に、前記層間絶縁膜を貫通するビアホールを形成する工程と

を有する請求項1乃至5のいずれか1項に記載の半導体装置の製造方法。 - 半導体基板の上に形成された第1導電型チャネルの第1のMISFET、及び該第1導電型とは逆の第2導電型チャネルの第2のMISFETと、

前記第2のMISFETが配置された領域を覆い、前記第1のMISFETが配置された領域は覆わず、第1の符号の歪を有する第1の歪膜と、

前記第1のMISFETが配置された領域を覆い、前記第2のMISFETが配置された領域は覆わず、前記第1の符号とは逆の第2の符号の歪を有する第2の歪膜と

を有し、

前記第2の歪膜の、前記第2のMISFET側の縁は、前記第1の歪膜の一部と重なり、前記第2の歪膜のうち、前記第1の歪膜と重なった部分、及び該重なった部分に連続する一部分の厚さが、前記第1のMISFETを覆っている部分の厚さよりも薄い半導体装置。 - 前記第2のMISFETがn型チャネルMISFETであり、かつ前記第1の歪膜が引張歪を有する請求項7に記載の半導体装置。

- 前記第2のMISFETがp型チャネルMISFETであり、かつ前記第1の歪膜が圧縮歪を有する請求項7に記載の半導体装置。

- さらに、

前記第1の歪膜及び第2の歪膜の上に配置された層間絶縁膜と、

前記層間絶縁膜、及び前記第2の歪膜の薄くなった部分を貫通するビアホールと、

前記ビアホール内に充填された導電部材と

を有する請求項7乃至9のいずれか1項に記載の半導体装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008179964A JP5262370B2 (ja) | 2008-07-10 | 2008-07-10 | 半導体装置の製造方法、及び半導体装置 |

| US12/500,277 US8274117B2 (en) | 2008-07-10 | 2009-07-09 | Method for manufacturing semiconductor device, and semiconductor device |

| US13/354,344 US8394693B2 (en) | 2008-07-10 | 2012-01-20 | Method for manufacturing semiconductor device, and semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008179964A JP5262370B2 (ja) | 2008-07-10 | 2008-07-10 | 半導体装置の製造方法、及び半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010021325A true JP2010021325A (ja) | 2010-01-28 |

| JP5262370B2 JP5262370B2 (ja) | 2013-08-14 |

Family

ID=41529542

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008179964A Expired - Fee Related JP5262370B2 (ja) | 2008-07-10 | 2008-07-10 | 半導体装置の製造方法、及び半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US8274117B2 (ja) |

| JP (1) | JP5262370B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9003338B2 (en) * | 2013-03-15 | 2015-04-07 | Taiwan Semiconductor Manufacturing Company Limited | Common template for electronic article |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006080161A (ja) * | 2004-09-07 | 2006-03-23 | Fujitsu Ltd | 半導体装置およびその製造方法 |

| JP2007173466A (ja) * | 2005-12-21 | 2007-07-05 | Toshiba Corp | 半導体装置 |

| JP2008124133A (ja) * | 2006-11-09 | 2008-05-29 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2009049206A (ja) * | 2007-08-20 | 2009-03-05 | Fujitsu Microelectronics Ltd | 半導体装置及びその製造方法 |

| JP2009194366A (ja) * | 2008-02-14 | 2009-08-27 | Toshiba Corp | 半導体装置の製造方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7521307B2 (en) | 2006-04-28 | 2009-04-21 | International Business Machines Corporation | CMOS structures and methods using self-aligned dual stressed layers |

| KR100772902B1 (ko) * | 2006-09-28 | 2007-11-05 | 삼성전자주식회사 | 반도체 소자 및 이의 제조 방법 |

| US7534678B2 (en) | 2007-03-27 | 2009-05-19 | Samsung Electronics Co., Ltd. | Methods of forming CMOS integrated circuit devices having stressed NMOS and PMOS channel regions therein and circuits formed thereby |

-

2008

- 2008-07-10 JP JP2008179964A patent/JP5262370B2/ja not_active Expired - Fee Related

-

2009

- 2009-07-09 US US12/500,277 patent/US8274117B2/en not_active Expired - Fee Related

-

2012

- 2012-01-20 US US13/354,344 patent/US8394693B2/en not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006080161A (ja) * | 2004-09-07 | 2006-03-23 | Fujitsu Ltd | 半導体装置およびその製造方法 |

| JP2007173466A (ja) * | 2005-12-21 | 2007-07-05 | Toshiba Corp | 半導体装置 |

| JP2008124133A (ja) * | 2006-11-09 | 2008-05-29 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2009049206A (ja) * | 2007-08-20 | 2009-03-05 | Fujitsu Microelectronics Ltd | 半導体装置及びその製造方法 |

| JP2009194366A (ja) * | 2008-02-14 | 2009-08-27 | Toshiba Corp | 半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8274117B2 (en) | 2012-09-25 |

| JP5262370B2 (ja) | 2013-08-14 |

| US20120115291A1 (en) | 2012-05-10 |

| US20100013023A1 (en) | 2010-01-21 |

| US8394693B2 (en) | 2013-03-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI745375B (zh) | 接觸結構的製造方法與半導體裝置 | |

| US9000534B2 (en) | Method for forming and integrating metal gate transistors having self-aligned contacts and related structure | |

| US20150001627A1 (en) | Spacer chamfering for a replacement metal gate device | |

| JP4794838B2 (ja) | 半導体装置およびその製造方法 | |

| US7923365B2 (en) | Methods of forming field effect transistors having stress-inducing sidewall insulating spacers thereon | |

| JP5268859B2 (ja) | 半導体装置 | |

| US20120292673A1 (en) | Semiconductor Device and Manufacturing Method Thereof | |

| US7612414B2 (en) | Overlapped stressed liners for improved contacts | |

| JP2007103694A (ja) | 半導体装置及びその製造方法 | |

| US8471341B2 (en) | Semiconductor device and method for fabricating the same | |

| JP5159828B2 (ja) | 半導体装置 | |

| US7659173B2 (en) | Method for manufacturing insulated-gate type field effect transistor | |

| JPWO2008117430A1 (ja) | 半導体装置の製造方法、半導体装置 | |

| WO2011030396A1 (ja) | 半導体装置およびその製造方法 | |

| JP5262370B2 (ja) | 半導体装置の製造方法、及び半導体装置 | |

| CN100533692C (zh) | 绝缘栅型场效应晶体管的制造方法 | |

| US20060163624A1 (en) | Semiconductor device, and manufacturing method thereof | |

| US11756839B2 (en) | Method for manufacturing metal oxide semiconductor transistor | |

| KR100735522B1 (ko) | 반도체 소자의 제조 방법 및 그에 의해 제조된 반도체 소자 | |

| JP2008192683A (ja) | 半導体装置及びその製造方法 | |

| JP2010067912A (ja) | 半導体装置及びその製造方法 | |

| TW202503974A (zh) | 半導體元件及其製作方法 | |

| US20110081781A1 (en) | Method for manufacturing semiconductor | |

| KR100481990B1 (ko) | 다마신 공법을 이용한 게이트 형성방법 | |

| JP2007123850A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110511 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130326 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130415 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5262370 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |