JP2010015606A - メモリカード - Google Patents

メモリカード Download PDFInfo

- Publication number

- JP2010015606A JP2010015606A JP2009242129A JP2009242129A JP2010015606A JP 2010015606 A JP2010015606 A JP 2010015606A JP 2009242129 A JP2009242129 A JP 2009242129A JP 2009242129 A JP2009242129 A JP 2009242129A JP 2010015606 A JP2010015606 A JP 2010015606A

- Authority

- JP

- Japan

- Prior art keywords

- card

- terminal

- memory

- controller

- interface

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 230000015654 memory Effects 0.000 claims abstract description 75

- 230000006870 function Effects 0.000 claims abstract description 38

- 238000012545 processing Methods 0.000 abstract description 18

- 238000000034 method Methods 0.000 description 26

- 230000008569 process Effects 0.000 description 25

- 238000004891 communication Methods 0.000 description 11

- 239000004065 semiconductor Substances 0.000 description 10

- 238000010586 diagram Methods 0.000 description 9

- 230000006698 induction Effects 0.000 description 9

- 238000000926 separation method Methods 0.000 description 8

- 238000003780 insertion Methods 0.000 description 7

- 230000037431 insertion Effects 0.000 description 7

- 230000035945 sensitivity Effects 0.000 description 5

- 230000004044 response Effects 0.000 description 4

- 101000837398 Homo sapiens T-cell leukemia/lymphoma protein 1B Proteins 0.000 description 3

- 102100028678 T-cell leukemia/lymphoma protein 1B Human genes 0.000 description 3

- 238000001514 detection method Methods 0.000 description 3

- 238000011156 evaluation Methods 0.000 description 3

- 238000007667 floating Methods 0.000 description 3

- 230000008520 organization Effects 0.000 description 3

- 238000007747 plating Methods 0.000 description 3

- 239000000758 substrate Substances 0.000 description 3

- 229910000838 Al alloy Inorganic materials 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- 229910000881 Cu alloy Inorganic materials 0.000 description 2

- 229910000640 Fe alloy Inorganic materials 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 238000004364 calculation method Methods 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 125000006850 spacer group Chemical group 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 230000002159 abnormal effect Effects 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- TWFZGCMQGLPBSX-UHFFFAOYSA-N carbendazim Chemical compound C1=CC=C2NC(NC(=O)OC)=NC2=C1 TWFZGCMQGLPBSX-UHFFFAOYSA-N 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 238000013523 data management Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000002708 enhancing effect Effects 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 230000005294 ferromagnetic effect Effects 0.000 description 1

- 230000004907 flux Effects 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 230000005291 magnetic effect Effects 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 230000005055 memory storage Effects 0.000 description 1

- 238000010295 mobile communication Methods 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

Images

Landscapes

- Credit Cards Or The Like (AREA)

Abstract

【解決手段】 本発明に係るメモリカード(5)は、外部とのインタフェース機能を有するコントローラ(7)と、前記コントローラに接続された不揮発性メモリ(8)と、外部との非接触インタフェース可能なマイクロコンピュータ(9)と、前記コントローラに与えられるクロック信号が入力されるクロック端子と、前記マイクロコンピュータに供給電圧を与える前記クロック端子と第1の距離を有する電圧供給端子と、前記マイクロコンピュータに接続され、それぞれが前記電源電圧端子と前記第1の距離より長い距離を有するアンテナ接続用の第1と第2のアンテナ端子と、を配線基板上に有する。

【選択図】図1

Description

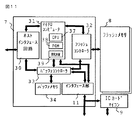

図2には本発明の一例に係るメモリカードを適用した携帯電話機などの通信携帯端末装置の概略が示される。通信携帯端末装置1は例えばシステム全体の制御を行うマイクロプロセッサ(MPU)2と、移動体通信のために変調及び復調などのベースバンド処理を行うベースバンド処理部(BB)3、規定の高周波による送受信を行う高周波部(RFcl)4、及びメモリカード(MRYC)5を有する。MRYC5は通信携帯端末装置1の図示を省略するカードスロットに着脱可能にされる。MPU2はMRYC5にとってカードホストとして位置付けられる。

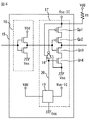

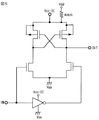

図1にはMRYC5の構成が例示される。MFMC5は、複数個の外部接続端子C1〜C16が形成された配線基板に、インタフェースコントローラ7と、前記インタフェースコントローラ7に接続されたフラッシュメモリ8と、前記インタフェースコントローラ7に接続されたセキュリティコントローラとしてのIC(インテグレーテッド・サーキット)カード用マイクロコンピュータ(ICカードマイコンとも称する)9が搭載される。前記インタフェースコントローラ7、フラッシュメモリ8、及びICカードマイコン9は夫々個別の半導体集積回路チップで構成されている。

図13には前記MRYC5をMMC規格のハーフサイズのパッケージに封止した時の外観を示す。図14には前記MRYC5をMMC規格のスタンダードサイズのパッケージに封止した時の外観を示す。両方の図面には外部接続端子の配列が明瞭に示されており、その配列は双方等しくされている。各端子C1〜C16の機能割り当ては図3で説明した通りである。C1〜C7はプリミティブなMMC規格に対応する。C8〜C9は4ビットモードのための拡張端子、C10〜C13はICカードマイコン接触インタフェース並びに8ビットモードのための拡張端子、C14及びC16は外部アンテナ接続用の拡張端子、C15はICカードマイコン専用の電源供給のための拡張端子である。C1〜C16はメモリカードの挿入方向(矢印X方向)の前後に隣合う列相互間で列方向の配置がずらされた千鳥状の配置を有する。第1列目はC1〜C7である。C8〜C13は第1列目の外部接続端子列に対して離間配置された第2列目を構成する。C10〜C13の外部接続端子の大きさはC1〜C7の外部接続端子の大きさと一定の範囲において同じである。C8の外部接続端子は前記第1列目に配置されコネクタ端子列の列方向一端の端子C7と列方向で完全に隣合う位置まで延在され、C9の外部接続端子は前記第1列目に配置され端子列の端子C1と列方向で部分的に重なって隣合う位置まで延在されている。第1列目の外部接続端子列と第2列目の外部接続端子列とは、C4とC15を除き、外部接続端子の列方向配置が列方向で相互にずれて、千鳥状に配置されている。

図23乃至図26にはメモリカードをカードスロットへ挿入する過程及びその過程の考察により得られたメモリカードへの電源供給について示されている。

また図示はしないが、カードスロット70からメモリカード5が引き抜かれる場合のことを考察する。この場合、フラッシュメモリ8においてデータの消去またはデータの書き込みの動作途中でカードスロット70からメモリカード5が引き抜かれた場合、フラッシュメモリ8への動作電源の供給が遮断されることで、不所望なデータの破損を生じ、またはデプリートと呼ばれる状態を生じることによりメモリカード5自体の認識ができなくなる場合がある。このような事態を回避するために、ホスト装置はセンサ71でメモリカード5がカードスロット70から引き抜かれたことを検知した場合、所定の端子を介してメモリカード5にそのことを通知するとともに、端子86から電位Vddを供給するようにすればよい。これにより図25の第2過程から図24の第1過程に亘って、端子C4に電位Vddを供給することができる。また端子74についても端子C3との接触時間を長くすることができるように、具体的には端子74を端子84と同程度の長さとするとともに、端子C3との接触点をより長くすることで電気的な接続を維持することが可能となる。これらのことにより、メモリカード5はデータの書き込みを完了させ、またはセンサ71での検出通知に応じて少なくともデプリート状態を回避する処理を行う時間を確保することが可能となる。

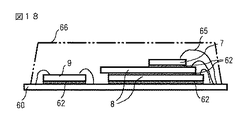

図17には夫々個別の半導体集積回路チップ化された前記インタフェースコントローラ7、フラッシュメモリ8、及びICカードマイコン9のスタック実装構造が平面的に示され、図18にはその実装構造の縦断面が概略的に示される。所要の配線層が形成されたガラスエポキシ樹脂基板のような配線基板60の一面には外部接続電極C1〜C16が形成され、他面には所要の配線に接続した多数のボンディングパッド61が形成されている。ボンディングパッド61はアルミニウム、銅又は鉄合金などの導電パターンで形成される。外部接続電極C1〜C16はアルミニウム、銅又は鉄合金などの導電パターンに金メッキやニッケルメッキ、パラジウムメッキ等が施されて形成される。外部接続電極C1〜C16とボンディングパッド61との接続は配線基板60上の図示を省略する配線パターン及び配線基板60を厚さ方向に貫通するスルーホール等によって行われる。配線基板60の上には、2個の個別チップ化されたフラッシュメモリ8がずれて重ねられ、その上に単一チップ化されたインタフェースコントローラ7が重ねられる。配線基板60とチップ、チップとチップの結合はダイボンド剤62にて行なわれる。重ねられらた3個のチップには重ねられた状態で同じ向きの辺に沿って電極パッド64が配置され、配置された電極パッド64に配線基板の対応するボンディングパッド61がボンディングワイヤ65でワイヤボンディングされる。重ねられた3個のチップのボンディング用電極パッド64は重ねられた状態で同じ向きの辺に沿って配置されているから、ボンディングワイヤ65を短くでき、ワイヤ65の干渉も少なくなる。単体チップのICカードマイコン9は単体で配線基板60にダイボンディングされて、チップの電極パッドが回路基板の対応するボンディングパッドにボンディングされる。配線基板60上にスタックされたチップは樹脂モールドなどで封止される。66はモールド封止領域である。

7 インタフェースコントローラ

8 フラッシュメモリ

9 デュアルウェイのICカードマイコン

10 アンテナ

11 インタフェース部

12 分離スイッチ回路

C4 Vdd供給用外部接続端子(第1の外部接続端子)

C12 Vcc−ic供給用外部接続端子

C15 Vcc−IC供給用外部接続端子(第2の外部接続端子)

C11 CLK−ic割当て用外部接続端子(第3の外部接続端子)

C13 I/O−ic割当て用外部接続端子(第4の外部接続端子)

C10 RES−ic割当て用外部接続端子(第5の外部接続端子)

C14,C16 アンテナ接続用外部接続端子

12 分離スイッチ回路

15 出力バッファ

17 クロックドインバータ

24 接触インタフェース型のICカードマイコン

25 非接触インタフェース型のICカードマイコン

60 回路基板

61 配線基板上の電極(ボンディングパッド)

64 半導体チップ上の電極パッド

65 ボンディングワイヤ

Claims (5)

- 外部とのインタフェース機能を有するコントローラと、

前記コントローラに接続された不揮発性メモリと、

外部との非接触インタフェース可能なマイクロコンピュータと、

前記コントローラに与えられるクロック信号が入力されるクロック端子と、

前記マイクロコンピュータに供給電圧を与える前記クロック端子と第1の距離を有する電圧供給端子と、

前記マイクロコンピュータに接続され、それぞれが前記電源電圧端子と前記第1の距離より長い距離を有するアンテナ接続用の第1と第2のアンテナ端子と、を配線基板上に有する、メモリカード。 - 前記電圧供給端子は、電源電圧を与える端子である、請求項1記載のメモリカード。

- 前記マイクロコンピュータは、前記コントローラと接続される、請求項1記載のメモリカード。

- 前記メモリカードは、

前記コントローラに接続されるデータの入出力に用いられるデータ端子を有し、

前記データ端子及び前記クロック端子は、配線基板上に1列状に配列され、

前記列と異なる列に、前記第1と第2のアンテナ端子が配置された、請求項1に記載のメモリカード。 - 前記電圧供給端子は、前記第1と第2のアンテナ端子に挟まれるように配置されている、請求項4に記載のメモリカード。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009242129A JP4906135B2 (ja) | 2009-10-21 | 2009-10-21 | メモリカード |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009242129A JP4906135B2 (ja) | 2009-10-21 | 2009-10-21 | メモリカード |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003316002A Division JP4412947B2 (ja) | 2003-09-08 | 2003-09-08 | メモリカード |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010015606A true JP2010015606A (ja) | 2010-01-21 |

| JP4906135B2 JP4906135B2 (ja) | 2012-03-28 |

Family

ID=41701597

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009242129A Expired - Fee Related JP4906135B2 (ja) | 2009-10-21 | 2009-10-21 | メモリカード |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4906135B2 (ja) |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2001084490A1 (fr) * | 2000-04-28 | 2001-11-08 | Hitachi,Ltd | Carte a circuit integre |

| JP2002342732A (ja) * | 2001-05-18 | 2002-11-29 | Matsushita Electric Ind Co Ltd | 小型icカード、小型icカードアダプタおよび端末装置 |

| JP2003091704A (ja) * | 2001-07-09 | 2003-03-28 | Hitachi Ltd | 不揮発性メモリを備えた記憶装置及びその記憶装置が着脱自在な情報処理装置 |

-

2009

- 2009-10-21 JP JP2009242129A patent/JP4906135B2/ja not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2001084490A1 (fr) * | 2000-04-28 | 2001-11-08 | Hitachi,Ltd | Carte a circuit integre |

| JP2002342732A (ja) * | 2001-05-18 | 2002-11-29 | Matsushita Electric Ind Co Ltd | 小型icカード、小型icカードアダプタおよび端末装置 |

| JP2003091704A (ja) * | 2001-07-09 | 2003-03-28 | Hitachi Ltd | 不揮発性メモリを備えた記憶装置及びその記憶装置が着脱自在な情報処理装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4906135B2 (ja) | 2012-03-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4412947B2 (ja) | メモリカード | |

| JP4447553B2 (ja) | マルチファンクションカードデバイス | |

| US7946500B2 (en) | Memory card and semiconductor device | |

| US7296754B2 (en) | IC card module | |

| CN1996351B (zh) | 集成电路卡 | |

| CN101512559A (zh) | Ic卡和ic卡用插槽 | |

| JP2006172122A (ja) | カード状記憶装置 | |

| CN101452540A (zh) | 内置ic卡功能的卡形存储装置 | |

| JP2007183776A (ja) | 半導体装置 | |

| JP4906135B2 (ja) | メモリカード | |

| JP4761479B2 (ja) | Icカード | |

| JP2010086550A (ja) | 半導体カードデバイス | |

| TWI309386B (ja) | ||

| CN101789263A (zh) | 多功能卡装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091021 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100527 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111020 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111206 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120105 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120106 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150120 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4906135 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |