JP2010004105A - Tdi方式イメージセンサ、及びその駆動方法 - Google Patents

Tdi方式イメージセンサ、及びその駆動方法 Download PDFInfo

- Publication number

- JP2010004105A JP2010004105A JP2008158856A JP2008158856A JP2010004105A JP 2010004105 A JP2010004105 A JP 2010004105A JP 2008158856 A JP2008158856 A JP 2008158856A JP 2008158856 A JP2008158856 A JP 2008158856A JP 2010004105 A JP2010004105 A JP 2010004105A

- Authority

- JP

- Japan

- Prior art keywords

- transfer

- wiring

- tdi

- clock

- stage number

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Transforming Light Signals Into Electric Signals (AREA)

Abstract

【解決手段】画素群110においてTDI段数を制限するためのブロックゲートを複数箇所に設け、それらのブロックゲートを、対となる転送ゲートに同数ずつ振り分けて配置する。又、その駆動方法は、設定したいTDI段数に応じた第1ブロックゲートに第1DC電圧を与え、第1ブロックゲートよりも反垂直転送方向181a側に位置する第2ブロックゲートに第1DC電圧よりも大きい第2DC電圧を与え、さらに、残りのブロックゲートに転送クロックを与える。

【選択図】図1

Description

しかしながら、垂直方向への電荷転送用の垂直転送クロックの立上り及び立下り時点において、駆動クロックの干渉によって、信号出力にスパイク状のカップリングノイズが重畳するといった課題がある。

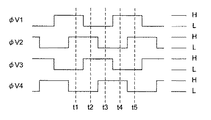

図5Aは、4相駆動CCDの電荷転送方向に沿った断面構造の模式図と、転送チャネルのポテンシャル変化のようすを時系列に表した図である。尚、4相駆動CCDとは、イメージセンサに含まれる一画素の構成部分に対して4相の転送クロックを供給して電荷転送を行うCCDである。又、図5Bは、図5Aに示す4相駆動CCDに与える転送クロックの波形を示す。尚、図5Bに示す転送クロックでは、上記特許文献1のように、垂直転送クロックφV1と垂直転送クロックφV3、及び垂直転送クロックφV2と垂直転送クロックφV4とは、互いに逆相としている。

図6Aは、TDI段数切り替え機能を有する従来の4相駆動CCDの転送方向に沿った断面構造の模式図、及び転送チャネルのポテンシャル変化のようすを時系列に表した図である。又、図6Bは、図6Aに示す4相駆動CCDに与える転送クロックの波形を示す。尚、図6Bに示す転送クロックにおいても、上記特許文献1のように、垂直転送クロックφV1と垂直転送クロックφV3、及び垂直転送クロックφV2と垂直転送クロックφV4とは、互いに逆相としている。

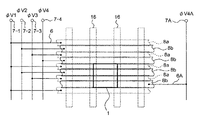

又、図8は、図7に示した従来の4相駆動CCDの画素部付近、具体的には入力ピン7A付近を拡大したレイアウト図である。

即ち、特許文献1に開示されるカップリングノイズの低減方法では、互いに逆相とされる、対になるCCD転送クロック(4相駆動CCDでは、φV1とφV3、及び、φV2とφV4)が供給される入力ピンの入力容量は等しく、これらの入力ピンで発生するカップリングノイズの絶対値は等しいことが前提となっている。

即ち、本発明の第1態様におけるTDI方式イメージセンサは、光電変換素子にて光電変換された信号電荷を垂直方向へ転送する転送ゲートを有する画素がマトリクス状に2次元配置された画素群を有し、それぞれの上記転送ゲートが接続され電気的に互いに独立したクロック配線に対となる2つの垂直転送クロックを互いに逆相にて供給して上記信号電荷を上記垂直方向へ時間遅延積分(TDI)して転送を行うTDI方式イメージセンサにおいて、上記画素群において上記垂直方向へ上記信号電荷をTDI転送させる段数を切り替えるTDI段数切替構成を備えたことを特徴とする。

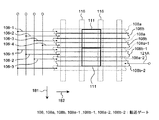

図1は、本発明の実施の形態1によるTDI方式リニアイメージセンサ101の回路構成を示す素子平面図である。当該TDI方式リニアイメージセンサ101は、大きく分けて、画素群110と、水平方向電荷転送部112と、電荷蓄積部113と、電荷排出ドレイン部114と、TDI段数切替構成120とを備え、信号電荷を垂直方向へ時間遅延積分(TDI)して転送を行う。

TDI段数切替構成120は、画素群110において垂直転送方向181へ信号電荷をTDI転送させる段数を切り替える構成部分であり、本実施形態では段数決定用候補配線121と、駆動部122とを備える。

勿論、TDI転送させる段の数は、上記6つに限定されず、又、設定段も上記2、3、5、…に限定されない。

駆動部122は、クロック配線106に対して上述の逆相の垂直転送クロックφV1、φV3と、垂直転送クロックφV2、φV4とを供給するとともに、段数決定用候補配線121に対して上記転送制御クロックを供給する部分である。ここで転送制御クロックは、上記逆相の垂直転送クロックφV1、φV3又はφV2、φV4、並びに一定電圧である。

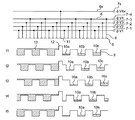

図3A及び図3Bは、TDI方式イメージセンサ101の駆動方法を説明するための図であり、図3Aは、TDI方式イメージセンサ101の信号転送方向に沿った断面構造の模式図であり、転送チャネルのポテンシャル変化のようすを時系列に表した図である。又、図3Bは、転送ゲート及びブロックゲートに供給する垂直転送クロックφV1〜φV4、及び上記第1一定電圧L1の波形を示す。

ブロックゲート131よりも右側では、クロック配線106−1〜106−4に供給される転送クロックφV1〜φV4によるCCDの転送動作によってポテンシャル井戸が図面右方へと移動するのに伴い、信号電荷130(130a〜130c)が図面右方へと電荷転送される。

駆動部122により、例えば段数決定用候補配線121Aに第1一定電圧L1を印加する。これにより、図1に示す構成において、1段目の画素111についてTDI転送が行われることになり、段数決定用候補配線121Aが段数決定配線となる。又、上述したように、駆動部122により、段数決定用候補配線121B、121D、121Fの中から例えば段数決定用候補配線121Fに第2一定電圧L2が印加される。さらに、駆動部122により、段数決定用候補配線121C、121Eには、クロック配線106−4に供給されるのと同じ転送クロックφV4が供給され、段数決定用候補配線121B、121Dには、クロック配線106−2に供給されるのと同じ転送クロックφV2が供給される。又、クロック配線106−1〜106−4には、駆動部122により、対になる転送クロックを互いに逆相とした4相駆動CCDの転送クロックφV1〜φV4が供給される。

又、段数決定用候補配線121A、121Fには、上述のように一定電圧L1、L2が印加されるため、転送クロックの干渉は生じない。

次に、駆動部122は、第2一定電圧L2を印加する段数決定用候補配線121を決定する。即ち、既に行った説明の繰り返しになるが、段数決定用候補配線121Cは、転送クロックφV4が供給されるクロック配線106−4に対応する配線であるので、駆動部122は、転送クロックφV4と逆相の転送クロックφV2が供給されるクロック配線106−2に対応する配線である段数決定用候補配線121B、121D、121Fの中から、段数決定用候補配線121Cよりも反垂直転送方向181a側に位置する段数決定用候補配線121D、121Fを抽出する。そして駆動部122は、段数決定用候補配線121D、121Fのいずれか一方に、(図4では段数決定用候補配線121Fを選択した場合を示している。)第2一定電圧L2を印加する。

又、上述した各説明では、4相の転送クロックを用いる場合を例に採ったが、転送クロックを6相等、4相以上の偶数相数にて駆動されるCCDに適用する場合についても、上述の実施形態は適用可能である。

106,106−1〜106−4 クロック配線、

108,108a,108b,108a−1,108b−1,108a−2,108b−2 転送ゲート、110 画素群、111 画素、112 水平方向電荷転送部、

113 電荷蓄積部、114 電荷排出ドレイン、

120 TDI段数切替構成、

121,121−1〜121−6 段数決定用候補配線、122 駆動部、

130 信号電荷、131 ブロックゲート、132 ポテンシャル障壁、

134 ブロックゲート、

181 垂直転送方向、181a 反垂直転送方向、182 水平転送方向。

Claims (4)

- 光電変換素子にて光電変換された信号電荷を垂直方向へ転送する転送ゲートを有する画素がマトリクス状に2次元配置された画素群を有し、それぞれの上記転送ゲートが接続され電気的に互いに独立したクロック配線に対となる2つの垂直転送クロックを互いに逆相にて供給して上記信号電荷を上記垂直方向へ時間遅延積分(TDI)して転送を行うTDI方式イメージセンサにおいて、

上記画素群において上記垂直方向へ上記信号電荷をTDI転送させる段数を切り替えるTDI段数切替構成を備えたことを特徴とするTDI方式イメージセンサ。 - 上記TDI段数切換構成は、段数決定用候補配線と、駆動部とを有し、

上記段数決定用候補配線は、上記画素群における所望の上記転送ゲートに接続され、上記クロック配線とは電気的に独立した偶数本から構成され、対となる互いに逆相の関係にある2つの上記垂直転送クロックが供給されるものの入力容量が互いに等しく、上記段数を決定する転送制御クロックが供給される配線であり、

上記駆動部は、それぞれの上記クロック配線に対して上記逆相の垂直転送クロックを供給するとともに、上記段数決定用候補配線に対して上記転送制御クロックを供給し、ここで転送制御クロックは、上記逆相の垂直転送クロック及び一定電圧である、

請求項1記載のTDI方式イメージセンサ。 - それぞれの上記画素は、4以上の偶数個の上記転送ゲートを有し、それぞれの上記クロック配線には、4以上の偶数相にてなり対となる2相が互いに逆相の関係にてなる複数組の垂直転送クロックが供給され、

上記段数決定用候補配線は、上記複数組の垂直転送クロックの内の1組の垂直転送クロックが供給される第1種配線及び第2種配線にて構成され、上記第1種配線及び上記第2種配線の本数並びに上記入力容量は互いに等しく、

上記駆動部は、上記段数決定用候補配線の内、TDI転送を行う所望段数に対応する一つの段数決定配線に上記一定電圧内の第1一定電圧を印加し、上記信号電荷の反垂直転送方向側に位置し上記段数決定配線とは反対種の上記段数決定用候補配線の一つに、上記第1一定電圧よりも高い第2一定電圧を印加し、その他の段数決定用候補配線には、上記第1種配線及び上記第2種配線に対応して上記1組の垂直転送クロックの垂直転送クロックを供給する、請求項2記載のTDI方式イメージセンサ。 - 光電変換素子にて光電変換された信号電荷を垂直方向へ転送する転送ゲートを有する画素がマトリクス状に2次元配置され、それぞれの上記転送ゲートが接続され電気的に互いに独立したクロック配線に4以上の偶数相にてなり対となる2相が互いに逆相の関係にてなる偶数組の垂直転送クロックを供給して上記信号電荷を垂直方向へ時間遅延積分(TDI)して転送を行うTDI方式イメージセンサであって、上記画素群における所望の上記転送ゲートに接続され、上記クロック配線とは電気的に独立した偶数本からなり、上記偶数組の垂直転送クロックの内の1組の垂直転送クロックが供給される第1種配線及び第2種配線にて構成され、上記第1種配線及び上記第2種配線の本数並びに上記入力容量が互いに等しい段数決定用候補配線を備えたTDI方式イメージセンサの駆動方法において、

上記段数決定用候補配線の内、TDI転送を行う所望の段数に対応する一つの段数決定配線に第1一定電圧を印加し、

上記段数決定配線よりも上記信号電荷の反垂直転送方向側に位置し上記段数決定配線とは反対種の上記段数決定用候補配線の一つに、上記第1一定電圧よりも高い第2一定電圧を印加し、

残りの上記段数決定用候補配線には、上記第1種配線及び上記第2種配線に対応して上記1組の垂直転送クロックを供給する、

ことを特徴とするTDI方式イメージセンサの駆動方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008158856A JP5052421B2 (ja) | 2008-06-18 | 2008-06-18 | Tdi方式イメージセンサ、及びその駆動方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008158856A JP5052421B2 (ja) | 2008-06-18 | 2008-06-18 | Tdi方式イメージセンサ、及びその駆動方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010004105A true JP2010004105A (ja) | 2010-01-07 |

| JP5052421B2 JP5052421B2 (ja) | 2012-10-17 |

Family

ID=41585489

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008158856A Expired - Fee Related JP5052421B2 (ja) | 2008-06-18 | 2008-06-18 | Tdi方式イメージセンサ、及びその駆動方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5052421B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20130016081A (ko) | 2011-08-05 | 2013-02-14 | 에스아이아이 나노 테크놀로지 가부시키가이샤 | 투과 x선 분석 장치 및 방법 |

| JP2016096387A (ja) * | 2014-11-12 | 2016-05-26 | 三菱電機株式会社 | Ccdイメージセンサ及びその駆動方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01221694A (ja) * | 1987-02-16 | 1989-09-05 | Optische Ind Oude Delft:Bv | 撮像装置 |

| JPH0690407A (ja) * | 1992-09-09 | 1994-03-29 | Fujitsu Ltd | 固体撮像素子 |

| JPH1013742A (ja) * | 1996-06-24 | 1998-01-16 | Sony Corp | 固体撮像装置およびその駆動方法 |

| JPH11298805A (ja) * | 1998-04-06 | 1999-10-29 | Nikon Corp | Tdi転送方式の固体撮像装置 |

| JP2000050063A (ja) * | 1998-07-31 | 2000-02-18 | Minolta Co Ltd | 画像読取り装置 |

| JP2007221368A (ja) * | 2006-02-15 | 2007-08-30 | Sony Corp | 負荷を駆動する駆動方法および駆動装置、並びに電子機器 |

-

2008

- 2008-06-18 JP JP2008158856A patent/JP5052421B2/ja not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01221694A (ja) * | 1987-02-16 | 1989-09-05 | Optische Ind Oude Delft:Bv | 撮像装置 |

| JPH0690407A (ja) * | 1992-09-09 | 1994-03-29 | Fujitsu Ltd | 固体撮像素子 |

| JPH1013742A (ja) * | 1996-06-24 | 1998-01-16 | Sony Corp | 固体撮像装置およびその駆動方法 |

| JPH11298805A (ja) * | 1998-04-06 | 1999-10-29 | Nikon Corp | Tdi転送方式の固体撮像装置 |

| JP2000050063A (ja) * | 1998-07-31 | 2000-02-18 | Minolta Co Ltd | 画像読取り装置 |

| JP2007221368A (ja) * | 2006-02-15 | 2007-08-30 | Sony Corp | 負荷を駆動する駆動方法および駆動装置、並びに電子機器 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20130016081A (ko) | 2011-08-05 | 2013-02-14 | 에스아이아이 나노 테크놀로지 가부시키가이샤 | 투과 x선 분석 장치 및 방법 |

| JP2013036805A (ja) * | 2011-08-05 | 2013-02-21 | Sii Nanotechnology Inc | 透過x線分析装置及び方法 |

| US8912503B2 (en) | 2011-08-05 | 2014-12-16 | Sii Nanotechnology Inc. | Transmission X-ray analyzer and transmission X-ray analysis method |

| JP2016096387A (ja) * | 2014-11-12 | 2016-05-26 | 三菱電機株式会社 | Ccdイメージセンサ及びその駆動方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5052421B2 (ja) | 2012-10-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9185319B2 (en) | Pixel-grouping image sensor | |

| KR102389417B1 (ko) | 고체 촬상 소자 및 촬상 장치 | |

| US6759641B1 (en) | Imager with adjustable resolution | |

| US20160014304A1 (en) | Solid-state imaging device | |

| JP4968227B2 (ja) | イメージセンサ及びその駆動方法 | |

| KR20230043243A (ko) | 광검출 장치 및 전자 기기 | |

| US8068158B2 (en) | Solid state imaging device capable of parallel reading of data from a plurality of pixel cells | |

| US7847848B2 (en) | Solid-state imaging device having a plurality of lines formed in at least two layers on semiconductor substrate | |

| JP5052421B2 (ja) | Tdi方式イメージセンサ、及びその駆動方法 | |

| US9392736B2 (en) | Methods for producing image sensors having multi-purpose architectures | |

| US10453980B2 (en) | Photodetection device and imaging device | |

| JP2011146924A (ja) | イメージセンサおよびそれを用いた撮像装置 | |

| JP3718103B2 (ja) | 固体撮像装置とその駆動方法、およびこれを用いたカメラ | |

| JP4514912B2 (ja) | 固体撮像装置およびその駆動方法 | |

| KR100339294B1 (ko) | 고체 이미지 센싱 장치와 그 구동방법 | |

| EP2530927B1 (en) | Multi-purpose architecture for CCD image sensors | |

| US8411189B2 (en) | Multi-purpose architecture for CCD image sensors | |

| US20110261240A1 (en) | Solid-state imaging device | |

| JP6967716B2 (ja) | 光検出装置、及び撮像装置 | |

| US20070262365A1 (en) | Solid-state imaging device and method of driving the same | |

| JP2009296451A (ja) | 固体撮像装置 | |

| US10580808B2 (en) | Photodetection device and imaging device | |

| JP6956666B2 (ja) | 撮像装置、飛翔体およびイメージセンサ駆動方法 | |

| CN117059632A (zh) | 一种低探测盲区雪崩二极管传感器 | |

| JP2012178399A (ja) | 固体撮像素子およびその製造方法並びに固体撮像装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100928 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120301 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120306 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120322 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120717 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120724 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150803 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |