JP2005332361A - プログラム命令圧縮装置および方法 - Google Patents

プログラム命令圧縮装置および方法 Download PDFInfo

- Publication number

- JP2005332361A JP2005332361A JP2004343921A JP2004343921A JP2005332361A JP 2005332361 A JP2005332361 A JP 2005332361A JP 2004343921 A JP2004343921 A JP 2004343921A JP 2004343921 A JP2004343921 A JP 2004343921A JP 2005332361 A JP2005332361 A JP 2005332361A

- Authority

- JP

- Japan

- Prior art keywords

- instruction

- program

- data path

- program instructions

- data processing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims abstract description 32

- 238000012545 processing Methods 0.000 claims abstract description 69

- 230000015654 memory Effects 0.000 claims description 39

- 238000004590 computer program Methods 0.000 claims description 31

- 230000004044 response Effects 0.000 claims description 11

- 230000006835 compression Effects 0.000 description 5

- 238000007906 compression Methods 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 230000008901 benefit Effects 0.000 description 4

- 230000009467 reduction Effects 0.000 description 4

- 230000006399 behavior Effects 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 210000003813 thumb Anatomy 0.000 description 3

- 101150098958 CMD1 gene Proteins 0.000 description 2

- 101100382321 Caenorhabditis elegans cal-1 gene Proteins 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 230000005055 memory storage Effects 0.000 description 2

- 230000009471 action Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000006837 decompression Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 230000009191 jumping Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 238000012552 review Methods 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3836—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution

- G06F9/3853—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution of compound instructions

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30098—Register arrangements

- G06F9/30101—Special purpose registers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30145—Instruction analysis, e.g. decoding, instruction word fields

- G06F9/30149—Instruction analysis, e.g. decoding, instruction word fields of variable length instructions

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3885—Concurrent instruction execution, e.g. pipeline, look ahead using a plurality of independent parallel functional units

Abstract

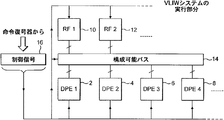

【解決手段】プログラム命令18が与えられると、その命令を復号してデータ経路構成要素を制御する制御信号を発生する。複数の命令セットは、異なる命令セットの異なる命令の中で異なって符号化される同一データ経路構成要素が実行する同一データ処理オペレーションによってサポートされる。この動作により、並列処理を期待できない場合はコードが圧縮され、並列動作が可能な場合は、完全な並列動作が指定される。

【選択図】図4

Description

プログラム命令の中の1つまたは複数の命令フィールドを復号して少なくともいくつかの制御信号を発生するように動作可能な命令復号器と、

前記制御信号に応答し、前記プログラム命令によって指定されたそれぞれのデータ処理オペレーションを独立して並列に実行する複数のデータ経路構成要素であって、前記命令復号器によって復号された少なくともいくつかのプログラム命令は、それぞれのデータ経路構成要素の制御命令が独立に指定されることを可能にする前記複数のデータ経路構成要素と、

を含んでおり、

前記命令復号器は、データ経路構成要素によって実行される所与のデータ処理オペレーションが、異なるプログラム命令の中で異なって符号化された命令フィールドを使用して指定されうるように動作可能である。

プログラム命令の中の1つまたは複数の命令フィールドを復号して少なくともいくつかの制御信号を発生するステップと、

前記制御信号に応答して複数のデータ経路構成要素を制御し、前記プログラム命令によって指定されたそれぞれのデータ処理オペレーションを並列に独立して実行し、少なくともいくつかのプログラム命令はそれぞれのデータ経路構成要素に対する制御信号が独立して指定されることを可能にするステップと、

を含み、

データ経路構成要素によって実行される所与のデータ処理オペレーションは、異なるプログラム命令の中で異なって符号化された命令フィールドを使用して指定されうる。

第1の符号化がデータ経路構成要素によって実行される所与のデータ処理オペレーションを指定する、符号化された命令フィールドを含む少なくとも1つのプログラム命令と、

前記第1の符号化とは異なる第2の符号化が前記データ経路構成要素によって実行される前記所与のデータ処理オペレーションを指定する、異なる符号化がされる命令フィールドを含む少なくとも1つの異なるプログラム命令と、

を含む。

1.サイクル1:

a.命令1の3つのコード語と命令2の1つの語を命令レジスタの中に読み込む。

2.サイクル2

a.命令2の2つのコード語と命令3の1つのコード語を命令レジスタの中に読み込む。

b.MSBに対してローテータを使用し、命令1を1語以上回転することによって命令復号器の入力のところに命令1を揃えて命令1を復号する(これは1つのバイトの配列(endianess)例であるが、本手法はこのようなシステムに限定されない)。

3.サイクル3:

a.命令3の別の2つのコード語と命令4の1つのコード語を命令レジスタの中に読み込む。

b.MSBに対してローテータを使用し、命令2を2語以上回転することによって命令復号器の入力のところに命令2を揃えて命令2を復号する。

4.サイクル4:

a.命令4と命令5の2つのコード語を命令レジスタの中に読み込む。

b.MSBに対してローテータを使用し、命令3を3語以上回転することによって命令復号器の入力のところに命令3を揃えて命令3を復号する。

5.サイクル5:

a.命令6の3つのコード語を命令レジスタの中に読み込む。

b.命令4を復号する。

6.サイクル6:

a.命令6の最終コード語を命令レジスタの中に読み込む。

b.MSBに対してローテータを使用し、命令5を3語以上回転することによって命令復号器の入力のところに命令5を揃えて命令5を復号する。

7. (以下省略)

14 バス・ネットワーク

10、12 レジスタファイル

16 制御信号レジスタ信号

18 プログラム命令

20 命令識別子フィールド

22 命令フィールドの制御ビットを含むセクション

24 プログラム命令

26 第2のプログラム命令

28 乗算器に関連する命令フィールド

30 第3のプログラム命令

32 専用命令フィールド

34 第4のプログラム命令

36、38 ルックアップテーブル

40、42、48 マルチプレクサ

44、46 回路要素

50 プログラムカウンタ

52 命令メモリ

54 命令レジスタ

56 ローテータ

58 命令復号器

60 制御レジスタ

62、64、66 データ経路構成要素

68 状態レジスタ

70 VLIWコントローラ

Claims (49)

- プログラム命令の中の1つまたは複数の命令フィールドを復号して少なくともいくつかの制御信号を発生するように動作可能な命令復号器と、

前記制御信号に応答し、前記プログラム命令によって指定されたそれぞれのデータ処理オペレーションを独立して並列に実行する複数のデータ経路構成要素であって、前記命令復号器によって復号された少なくともいくつかのプログラム命令は、それぞれのデータ経路構成要素のための制御命令が独立に指定されることを可能にする前記複数のデータ経路構成要素と

を含み、

前記命令復号器は、データ経路構成要素によって実行されるべき所与のデータ処理オペレーションが、異なるプログラム命令において異なって符号化された命令フィールドを使用して指定されうるように動作可能であるデータ処理装置。 - 請求項1に記載の装置において、前記データ処理オペレーションを表す前記異なって符号化された命令フィールドは、前記異なるプログラム命令の中に異なるビット長を有する前記装置。

- 請求項1に記載の装置において、前記データ処理オペレーションを表す前記異なって符号化された命令フィールドは、前記異なるプログラム命令の中に異なるビット位置を有する前記装置。

- 請求項1に記載の装置において、前記プログラム命令は複数の命令セットに分割され、前記命令復号器は、プログラム命令の中のフィールドを識別する少なくともある命令セットに応答して、前記プログラム命令の中のどのビットが、どのデータ経路構成要素に対する命令フィールドに対応するかを制御する前記装置。

- 請求項1に記載の装置において、前記プログラム命令は、可変プログラム命令長を有し、前記命令復号器は、前記命令セット識別子に応答してプログラム命令のプログラム命令長を決定する前記装置。

- 請求項1に記載の装置において、前記異なって符号化された命令フィールドは、前記データ経路構成要素によって実行されうるデータ処理オペレーションの異なるセットを表すように動作可能である前記装置。

- 請求項6に記載の装置において、プログラム命令の中の前記異なって符号化された命令フィールドの少なくとも1つは、異なるプログラム命令の中の前記異なって符号化された命令フィールドの異なる1つによって表されうるデータ処理オペレーションのサブセットを表すように動作可能である前記装置。

- 請求項7に記載の装置において、前記サブセットは、データ処理オペレーションの前記最大のセットと比較して減少したオペランド範囲を有する前記装置。

- 請求項8に記載の装置において、前記オペランド範囲は、

レジスタ指定子と、

プログラムの中の実行点におけるジャンプを表すジャンプアドレス指定子と、

アラインメント指定子と、

即値と、

の中の1つである前記装置。 - 請求項1に記載の装置において、プログラム命令自身の中の少なくとも1つの命令フィールドが、前記複数のデータ経路構成要素のうちのどれが前記少なくとも1つの命令フィールドによって制御されるかを指定する前記装置。

- 請求項1に記載の装置において、異なるプログラム命令に応答して、前記複数のデータ経路構成要素の可変個数のデータ経路構成要素が、アクティブであるかまたは非アクティブである前記装置。

- 請求項11に記載の装置において、所与のデータ経路構成要素に対して、データ処理オペレーションが指定されていないかまたはペンディングになっている場合、前記所与のデータ経路構成要素は非アクティブであり、Nopオペレーションを行なう前記装置。

- 請求項5に記載の装置であって、前記プログラム命令を格納するように動作可能であるとともに固定長メモリアクセスで可読な命令メモリを含む前記装置。

- 請求項13に記載の装置において、固定長メモリアクセスは、複数のプログラム命令の少なくともいくつかの部分を含む前記装置。

- 請求項14に記載の装置であって、前記命令復号器に供給するための所定位置に前記メモリアクセスの中のプログラム命令を揃えるように動作可能なローテータとプログラムカウンタ増分器(incrementer)とを含む前記装置。

- 請求項5に記載の装置であって、前記命令復号器に供給するための所定位置に前記メモリアクセスの中のプログラム命令を揃えるように動作可能なローテータとプログラムカウンタ増分器とを含み、前記ローテータは、前記命令セット識別子に応答して、前記プログラム命令を揃えるためにいかなる回転を与えるべきかを決定する前記装置。

- プログラム命令の中の1つまたは複数の命令フィールドを復号して少なくともいくつかの制御信号を発生するステップと、

前記制御信号に応答して複数のデータ経路構成要素を制御し、前記プログラム命令によって指定されたそれぞれのデータ処理オペレーションを並列に独立して実行し、少なくともいくつかのプログラム命令はそれぞれの各データ経路構成要素に対する制御信号が独立して指定されることを可能にするステップと

を含み、

データ経路構成要素によって行なわれる所与のデータ処理オペレーションは、異なるプログラム命令の中で異なって符号化された命令フィールドを使用して指定されうる方法。 - 請求項17に記載の方法において、前記データ処理オペレーションを表す前記異なって符号化された命令フィールドは、前記異なるプログラム命令の中に異なるビット長を有する前記方法。

- 請求項17に記載の方法において、前記データ処理オペレーションを表す前記異なって符号化された命令フィールドは、前記異なるプログラム命令の中に異なるビット位置を有する前記方法。

- 請求項17に記載の方法において、前記プログラム命令は複数の命令セットに分割され、前記命令復号器は、プログラム命令の中のフィールドを識別する少なくともある命令セットに応答して、前記プログラム命令の中のどのビットが、どのデータ経路構成要素に対する命令フィールドに対応するかを制御する前記方法。

- 請求項17に記載の方法において、前記プログラム命令は可変プログラム命令長を有し、前記命令復号器は、前記命令セット識別子に応答してプログラム命令のプログラム命令長を決定する前記方法。

- 請求項17に記載の方法において、前記異なって符号化された命令フィールドは、前記データ経路構成要素によって実行されうるデータ処理オペレーションの異なるセットを表すように動作可能である前記方法。

- 請求項22に記載の方法において、プログラム命令の中の少なくとも1つの前記異なって符号化された命令フィールドは、異なるプログラム命令の中の前記異なって符号化された命令フィールドの異なる1つによって表されうるデータ処理オペレーションのサブセットを表すように動作可能である前記方法。

- 請求項23に記載の方法において、前記サブセットは、データ処理オペレーションの前記最大のセットと比較して減少したオペランド範囲を有する前記方法。

- 請求項24に記載の方法において、前記オペランド範囲は、

レジスタ指定子と、

プログラムの中の実行点におけるジャンプを表すジャンプアドレス指定子と、

アラインメント指定子と、

即値と、

の中の1つである前記方法。 - 請求項17に記載の方法において、プログラム命令自身の中の少なくとも1つの命令フィールドが、前記複数のデータ経路構成要素のうちのどれが前記少なくとも1つの命令フィールドによって制御されるかを指定する前記方法。

- 請求項17に記載の方法において、異なるプログラム命令に応答して、前記複数のデータ経路構成要素の可変個数のデータ経路構成要素が、アクティブであるかまたは非アクティブである前記方法。

- 請求項27に記載の方法において、所与のデータ経路構成要素に対してデータ処理オペレーションが指定されていないかまたはペンディングになっている場合、前記所与のデータ経路構成要素は非アクティブでありNopオペレーションを実行する前記方法。

- 請求項21に記載の方法において、命令メモリは、前記プログラム命令を格納するように動作可能であるとともに固定長メモリアクセスで可読である前記方法。

- 請求項29に記載の方法において、固定長メモリアクセスは、複数のプログラム命令の少なくともいくつかの部分を含む前記方法。

- 請求項30に記載の方法において、ローテータとプログラムカウンタ増分器とは、前記命令復号器に供給するための所定位置に前記メモリアクセスの中のプログラム命令を揃えるように動作可能である前記方法。

- 請求項21に記載の方法において、ローテータとプログラムカウンタ増分器とは、前記命令復号器に供給するための所定位置に前記メモリアクセスの中のプログラム命令を揃えるように動作可能であり、前記ローテータは、前記命令セット識別子に応答して、前記プログラム命令を揃えるためにいかなる回転を与えるべきかを決定する前記方法。

- プログラム命令の中の1つまたは複数の命令フィールドを復号して、少なくともいくつかの制御信号を発生するように動作可能な命令復号器と、前記制御信号に応答して前記プログラム命令によって指定されたそれぞれのデータ処理オペレーションを独立して並列に実行する複数のデータ経路構成要素とを有するデータ処理装置を制御するコンピュータプログラム製品であって、

第1の符号化が、データ経路構成要素によって行なわれる所与のデータ処理オペレーションを指定する、符号化された命令フィールドを含む少なくとも1つのプログラム命令と、

前記第1の符号化とは異なる第2の符号化が、前記データ経路構成要素によって行なわれる前記所与のデータ処理オペレーションを指定する、異なって符号化された命令フィールドを含む少なくとも1つの異なるプログラム命令と

を含むコンピュータプログラム製品。 - 請求項33に記載のコンピュータプログラム製品において、前記データ処理オペレーションを表す前記異なって符号化された命令フィールドは、前記異なるプログラム命令の中の異なるビット長を有する前記コンピュータプログラム製品。

- 請求項33に記載のコンピュータプログラム製品において、前記データ処理オペレーションを表す前記異なって符号化された命令フィールドは、前記異なるプログラム命令の中に異なるビット位置を有する前記コンピュータプログラム製品。

- 請求項33に記載のコンピュータプログラム製品において、前記プログラム命令は複数の命令セットに分割され、前記命令復号器は、プログラム命令の中のフィールドを識別する少なくともある命令セットに応答して、前記プログラム命令の中のどのビットが、どのデータ経路構成要素に対する命令フィールドに対応するかを制御する前記コンピュータプログラム製品。

- 請求項33に記載のコンピュータプログラム製品において、前記プログラム命令は、可変プログラム命令長を有し、前記命令復号器は、前記命令セット識別子に応答してプログラム命令のプログラム命令長を決定する前記コンピュータプログラム製品。

- 請求項33に記載のコンピュータプログラム製品において、前記異なって符号化された命令フィールドは、前記データ経路構成要素によって実行されうるデータ処理オペレーションの異なるセットを表すように動作可能である前記コンピュータプログラム製品。

- 請求項38に記載のコンピュータプログラム製品において、プログラム命令の中の前記異なって符号化された命令フィールドの少なくとも1つは、異なるプログラム命令の中の前記異なって符号化された命令フィールドの異なる1つによって表されうるデータ処理オペレーションのサブセットを表すように動作可能である前記コンピュータプログラム製品。

- 請求項39に記載のコンピュータプログラム製品において、前記サブセットは、データ処理オペレーションの前記最大のセットと比較して減少したオペランド範囲を有する前記コンピュータプログラム製品。

- 請求項40に記載のコンピュータプログラム製品において、前記オペランド範囲は、

レジスタ指定子と、

プログラムの中の実行点におけるジャンプを表すジャンプアドレス指定子と、

アラインメント指定子と、

即値と、

の中の1つである前記コンピュータプログラム製品。 - 請求項33に記載のコンピュータプログラム製品において、プログラム命令自身の中の少なくとも1つの命令フィールドが、前記複数のデータ経路構成要素のうち、どれが前記少なくとも1つの命令フィールドによって制御されるかを指定する前記コンピュータプログラム製品。

- 請求項33に記載のコンピュータプログラム製品において、異なるプログラム命令に応答して、前記複数のデータ経路構成要素のうちの可変個数のデータ経路構成要素が、アクティブであるかまたは非アクティブである前記コンピュータプログラム製品。

- 請求項43に記載のコンピュータプログラム製品において、所定のデータ経路構成要素に対してデータ処理オペレーションが指定されていないかまたはペンディング、保留になっている場合、前記所与のデータ経路構成要素は非アクティブでありヌルオペレーションを実行する前記コンピュータプログラム製品。

- 請求項37に記載のコンピュータプログラム製品において、命令メモリは、前記プログラム命令を格納するように動作可能であるとともに固定長メモリアクセスで可読である前記コンピュータプログラム製品。

- 請求項45に記載のコンピュータプログラム製品において、固定長メモリアクセスは、複数のプログラム命令の少なくともいくつかの部分を含む前記コンピュータプログラム製品。

- 請求項46に記載のコンピュータプログラム製品において、ローテータとプログラムカウンタ増分器とは、前記命令復号器に供給するための所定位置に前記メモリアクセスの中のプログラム命令を揃えるように動作可能である前記コンピュータプログラム製品。

- 請求項37に記載のコンピュータプログラム製品において、

ローテータとプログラムカウンタ増分器とは、前記命令復号器に供給するための所定位置に前記メモリアクセスの中のプログラム命令を揃えるように動作可能であり、前記ローテータは、前記命令セット識別子に応答して、前記プログラム命令を揃えるためにいかなる回転を与えるべきかを決定する前記コンピュータプログラム製品。 - 請求項33に記載のコンピュータプログラムを発生するように動作可能なコンピュータプログラムコンパイラ。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GB0410986A GB2414308B (en) | 2004-05-17 | 2004-05-17 | Program instruction compression |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005332361A true JP2005332361A (ja) | 2005-12-02 |

| JP2005332361A5 JP2005332361A5 (ja) | 2007-02-22 |

Family

ID=32527186

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004343921A Pending JP2005332361A (ja) | 2004-05-17 | 2004-11-29 | プログラム命令圧縮装置および方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7302552B2 (ja) |

| JP (1) | JP2005332361A (ja) |

| GB (1) | GB2414308B (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015143991A (ja) * | 2006-09-22 | 2015-08-06 | インテル コーポレイション | 文字列を処理するための命令及び論理回路 |

| US10416888B2 (en) | 2016-09-09 | 2019-09-17 | Fujitsu Limited | Parallel processing device, method for controlling parallel processing device, and controller used in parallel processing device |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2370380B (en) | 2000-12-19 | 2003-12-31 | Picochip Designs Ltd | Processor architecture |

| GB2420884B (en) * | 2004-12-03 | 2009-04-15 | Picochip Designs Ltd | Processor architecture |

| US7581082B2 (en) * | 2005-05-13 | 2009-08-25 | Texas Instruments Incorporated | Software source transfer selects instruction word sizes |

| GB2430773A (en) * | 2005-10-03 | 2007-04-04 | Advanced Risc Mach Ltd | Alignment of variable length program instructions |

| US20080077772A1 (en) * | 2006-09-22 | 2008-03-27 | Ronen Zohar | Method and apparatus for performing select operations |

| US7624251B2 (en) * | 2006-11-01 | 2009-11-24 | Apple Inc. | Instructions for efficiently accessing unaligned partial vectors |

| US7620797B2 (en) * | 2006-11-01 | 2009-11-17 | Apple Inc. | Instructions for efficiently accessing unaligned vectors |

| CN101398752B (zh) * | 2007-09-29 | 2011-08-31 | 国际商业机器公司 | 重叠指令存取单元和重叠指令存取方法 |

| GB2454865B (en) | 2007-11-05 | 2012-06-13 | Picochip Designs Ltd | Power control |

| US20100312991A1 (en) * | 2008-05-08 | 2010-12-09 | Mips Technologies, Inc. | Microprocessor with Compact Instruction Set Architecture |

| CN102077195A (zh) * | 2008-05-08 | 2011-05-25 | Mips技术公司 | 具有紧凑指令集架构的微处理器 |

| GB2470037B (en) | 2009-05-07 | 2013-07-10 | Picochip Designs Ltd | Methods and devices for reducing interference in an uplink |

| GB2470771B (en) | 2009-06-05 | 2012-07-18 | Picochip Designs Ltd | A method and device in a communication network |

| GB2470891B (en) | 2009-06-05 | 2013-11-27 | Picochip Designs Ltd | A method and device in a communication network |

| GB2474071B (en) | 2009-10-05 | 2013-08-07 | Picochip Designs Ltd | Femtocell base station |

| GB2482869B (en) | 2010-08-16 | 2013-11-06 | Picochip Designs Ltd | Femtocell access control |

| GB2484489A (en) | 2010-10-12 | 2012-04-18 | Advanced Risc Mach Ltd | Instruction decoder using an instruction set identifier to determine the decode rules to use. |

| GB2489716B (en) | 2011-04-05 | 2015-06-24 | Intel Corp | Multimode base system |

| GB2489919B (en) | 2011-04-05 | 2018-02-14 | Intel Corp | Filter |

| GB2491098B (en) | 2011-05-16 | 2015-05-20 | Intel Corp | Accessing a base station |

| US20160179542A1 (en) * | 2014-12-23 | 2016-06-23 | Patrick P. Lai | Instruction and logic to perform a fused single cycle increment-compare-jump |

| KR20180031266A (ko) | 2016-09-19 | 2018-03-28 | 삼성전자주식회사 | 전자 장치, vliw 프로세서 및 그 제어 방법들 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09512651A (ja) * | 1994-05-03 | 1997-12-16 | アドバンスド リスク マシーンズ リミテッド | 複数命令セットのマッピング |

| JPH11194939A (ja) * | 1995-07-12 | 1999-07-21 | Mitsubishi Electric Corp | データ処理装置 |

| JP2002533815A (ja) * | 1998-12-18 | 2002-10-08 | ボプス インコーポレイテッド | 動的コンパクト命令を有するスケーラブル命令セットアーキテクチャのための方法及び装置 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5057837A (en) * | 1987-04-20 | 1991-10-15 | Digital Equipment Corporation | Instruction storage method with a compressed format using a mask word |

| US5826054A (en) * | 1996-05-15 | 1998-10-20 | Philips Electronics North America Corporation | Compressed Instruction format for use in a VLIW processor |

| US5922065A (en) * | 1997-10-13 | 1999-07-13 | Institute For The Development Of Emerging Architectures, L.L.C. | Processor utilizing a template field for encoding instruction sequences in a wide-word format |

| JP4502532B2 (ja) * | 2001-02-23 | 2010-07-14 | 株式会社ルネサステクノロジ | データ処理装置 |

| EP1530755B1 (en) * | 2002-08-16 | 2019-11-06 | Intel Corporation | Apparatus, method, and compiler enabling processing of variable length isntructions in a very long instruction word processor |

| AU2003253159A1 (en) * | 2002-09-24 | 2004-04-19 | Koninklijke Philips Electronics N.V. | Apparatus, method ,and compiler enabling processing of load immediate instructions in a very long instruction word processor |

-

2004

- 2004-05-17 GB GB0410986A patent/GB2414308B/en active Active

- 2004-10-14 US US10/963,722 patent/US7302552B2/en active Active

- 2004-11-29 JP JP2004343921A patent/JP2005332361A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09512651A (ja) * | 1994-05-03 | 1997-12-16 | アドバンスド リスク マシーンズ リミテッド | 複数命令セットのマッピング |

| JPH11194939A (ja) * | 1995-07-12 | 1999-07-21 | Mitsubishi Electric Corp | データ処理装置 |

| JP2002533815A (ja) * | 1998-12-18 | 2002-10-08 | ボプス インコーポレイテッド | 動的コンパクト命令を有するスケーラブル命令セットアーキテクチャのための方法及び装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015143991A (ja) * | 2006-09-22 | 2015-08-06 | インテル コーポレイション | 文字列を処理するための命令及び論理回路 |

| US10416888B2 (en) | 2016-09-09 | 2019-09-17 | Fujitsu Limited | Parallel processing device, method for controlling parallel processing device, and controller used in parallel processing device |

Also Published As

| Publication number | Publication date |

|---|---|

| US7302552B2 (en) | 2007-11-27 |

| US20050257028A1 (en) | 2005-11-17 |

| GB0410986D0 (en) | 2004-06-16 |

| GB2414308B (en) | 2007-08-15 |

| GB2414308A (en) | 2005-11-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2005332361A (ja) | プログラム命令圧縮装置および方法 | |

| US11669330B2 (en) | Method for performing random read access to a block of data using parallel LUT read instruction in vector processors | |

| KR102413832B1 (ko) | 벡터 곱셈 덧셈 명령 | |

| US7366874B2 (en) | Apparatus and method for dispatching very long instruction word having variable length | |

| JP4484925B2 (ja) | Simdデバイスにおける制御フロー管理のための方法及び装置 | |

| US7509483B2 (en) | Methods and apparatus for meta-architecture defined programmable instruction fetch functions supporting assembled variable length instruction processors | |

| US6957321B2 (en) | Instruction set extension using operand bearing NOP instructions | |

| US7574583B2 (en) | Processing apparatus including dedicated issue slot for loading immediate value, and processing method therefor | |

| JP7002462B2 (ja) | ベクトル述語命令 | |

| KR20000076285A (ko) | 기계 판독가능 매체 및 초대형 인스트럭션 워드 프로세서와, 컴퓨터 프로그램의 실행 방법 및 컴파일 방법 | |

| US7313671B2 (en) | Processing apparatus, processing method and compiler | |

| US11307855B2 (en) | Register-provided-opcode instruction | |

| US9965275B2 (en) | Element size increasing instruction | |

| US7895417B2 (en) | Select-and-insert instruction within data processing systems | |

| US11397583B2 (en) | Conditional execution specification of instructions using conditional extension slots in the same execute packet in a VLIW processor | |

| US7231507B2 (en) | Data access program instruction encoding | |

| CN107851022B (zh) | 向量长度查询指令 | |

| EP3655852A1 (en) | Vector interleaving in a data processing apparatus | |

| US20120260062A1 (en) | System and method for providing dynamic addressability of data elements in a register file with subword parallelism | |

| JPS623336A (ja) | 条件付きブランチ方式 | |

| US6886091B1 (en) | Replacing VLIW operation with equivalent operation requiring fewer issue slots | |

| JP2002073325A (ja) | データ処理装置及び方法 | |

| TW202307653A (zh) | 陳述技術 | |

| JPH1173314A (ja) | マイクロプロセッサ | |

| JP2000215058A (ja) | 計算機及び命令実行方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061228 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061228 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091102 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091110 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100210 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20101015 |