JP2005293372A - 低消費電力回路の設計方法および低消費電力回路の設計支援装置 - Google Patents

低消費電力回路の設計方法および低消費電力回路の設計支援装置 Download PDFInfo

- Publication number

- JP2005293372A JP2005293372A JP2004109259A JP2004109259A JP2005293372A JP 2005293372 A JP2005293372 A JP 2005293372A JP 2004109259 A JP2004109259 A JP 2004109259A JP 2004109259 A JP2004109259 A JP 2004109259A JP 2005293372 A JP2005293372 A JP 2005293372A

- Authority

- JP

- Japan

- Prior art keywords

- flip

- clock

- module

- data

- flop

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Information Transfer Systems (AREA)

Abstract

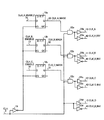

【解決手段】半導体集積回路の論理回路を、データを取り込むためのイネーブル条件が付いているフリップフロップが含まれるモジュールA,B,Cと、データを取り込むためのイネーブル条件が付かないフリップフロップが含まれるモジュールDとに分ける。そしてモジュールA,B,Cには前記イネーブル条件に従ってデータを取り込むタイミングでのみクロック供給となる供給・停止付きのクロック信号が供給されるようにし、モジュールDには常にクロック供給となるクロック信号が供給されるようにする。その後、前記分割したモジュール間のデータ転送経路に、データ送信側のモジュールに供給する前記クロック信号を反転したクロック信号でデータを取り込むフリップフロップを挿入する。

【選択図】 図1

Description

図1は、この発明にかかる低消費電力回路の設計方法の一実施の形態による低消費電力回路の設計方法を説明する図である。図1において、モジュールA1,モジュールB2,モジュールC3およびモジュールD4は、それぞれ論理回路の回路要素であるフリップフロップを、供給するクロック信号によってグループ化したモジュールであり、次のようにして分割され、クロックの供給が行われる。なお、少なくともモジュールA1,モジュールB2およびモジュールC3は、モジュール間のデータ転送に関わる信号数が少なくなるように分割されている。

図7は、この発明にかかる低消費電力回路の設計支援装置の一実施の形態による低消費電力回路の設計支援装置の構成を示すフローチャートである。この実施の形態2では、実施の形態1に示したクロック系統の異なるモジュール間のデータ転送を実現する低消費電力回路の設計において、モジュール間のデータ転送数を考慮しないでモジュールの分割を行う設計支援装置の構成例が示されている。

図8は、この発明にかかる低消費電力回路の設計支援装置の他の実施の形態による低消費電力回路の設計支援装置の構成を説明するフローチャートである。この実施の形態3では、実施の形態1に示したクロック系統の異なるモジュール間のデータ転送を実現する低消費電力回路の設計において、モジュール間のデータ転送数を考慮してモジュールの分割を行う設計支援装置の構成例が示されている。

2 モジュールB(論理回路の回路要素を供給するクロック信号でグループ化したモジュールで、データイネーブル付きのフリップフロップを含む)、

3 モジュールC(論理回路の回路要素を供給するクロック信号でグループ化したモジュール、データイネーブル付きのフリップフロップを含む)、

4 モジュールD(論理回路の回路要素を供給するクロック信号でグループ化したモジュールで、フリーランクロック信号によって駆動されるフリップフロップを含む)、

5 モジュールAのクロックイネーブル条件生成回路、

6 モジュールBのロックイネーブル条件生成回路、

7 モジュールCのクロックイネーブル条件生成回路、

8 クロック生成回路、

18a,18b,18c フリップフロップ、

20a,20b,20c,20d,20e,20f フリップフロップ、

21a,21b 2入力1出力のマルチプレクサ、

22a,22b,22c AND回路、

23a,23b,23c,23d インバータ、

24a,24b,24c,24d,37 バッファ、

35,36 フリップフロップ、

60 クロックスキュー、

100,101,102 記憶装置。

Claims (4)

- 半導体集積回路の論理回路におけるフリップフロップを、データを取り込むためのイネーブル条件が付いている第1フリップフロップのグループと前記データを取り込むためのイネーブル条件が付かない第2フリップフロップのグループとに分ける工程と、

前記第1フリップフロップのグループを複数の第1モジュールに分割し、前記第2フリップフロップのグループを1以上の第2モジュールに分割する工程と、

分割したモジュールを単位として、前記第1モジュールでは、そのモジュールに含まれる第1フリップフロップに対し、前記イネーブル条件に従ってデータを取り込むタイミングではクロック供給となりその他のタイミングではクロック停止となる供給・停止付きのクロック信号が供給されるようにし、前記第2モジュールでは、そのモジュールに含まれる第2フリップフロップに対し、常にクロック供給となりデータの取り込みを連続して行わせるクロック信号が供給されるようにする工程と、

前記分割したモジュール間のデータ転送経路に、データ送信側のモジュールに供給する前記クロック信号を反転したクロック信号でデータを取り込むフリップフロップを挿入する工程と、

を含むことを特徴とする低消費電力回路の設計方法。 - 前記モジュールに分割する工程では、少なくとも、前記第1フリップフロップのグループを複数の第1モジュールに分割する場合に、当該第1モジュール間でのデータ転送に関わる信号数が少なくなるように前記第1フリップフロップのグループを分割する工程を含むことを特徴とする請求項1に記載の低消費電力回路の設計方法。

- 半導体集積回路の論理回路を表現した論理記述データと前記半導体集積回路に含まれるクロック信号の総数が含まれる制約条件とに基づき、前記クロック信号に接続されるフリップフロップが、データを取り込むためのイネーブル条件付きであるか否かを判別する手段と、

前記判別手段の判別結果に基づき、イネーブル条件付きのフリップフロップをグループ化してモジュールに分割し、イネーブル条件付きでないフリップフロップをグループ化して別のモジュールに分割する手段と、

前記制約条件として与えた半導体集積回路に含まれるクロック信号数を満足するように前記分割したイネーブル条件付きのフリップフロップが含まれるモジュールを細かく分割する手段と、

系統の異なるクロック信号が供給されるモジュール間のデータ転送経路に、送信側のモジュールに供給するクロック信号を反転したクロック信号で駆動されるフリップフロップを挿入する手段と、

前記イネーブル条件付きのフリップフロップが含まれる各モジュールについてそのモジュール内のフリップフロップがデータを取り込むタイミングのみでクロック信号が供給されるようにするクロックイネーブル条件を生成する回路を生成する手段と、

前記イネーブル条件付きのフリップフロップが含まれる各モジュールに対しては各モジュールに対する前記クロックイネーブル条件に基づき、そのモジュール内のフリップフロップがデータを取り込むタイミングではクロック供給となりその他のタイミングではクロック供給停止となる供給・停止付きのクロック信号を生成する一方、前記イネーブル条件付きでないフリップフロップが含まれる各モジュールに対してはそのモジュール内のフリップフロップがデータの取り込みを連続して行うように常にクロック供給となるクロック信号を供給する回路を生成する手段と、

前記の各手段によって生成された論理記述データを設計結果として出力する手段と、

を備えたことを特徴とする低消費電力回路の設計支援装置。 - 半導体集積回路の論理回路を表現した論理記述データと前記半導体集積回路に含まれるクロック信号の総数が含まれる制約条件とに基づき、前記クロック信号に接続されるフリップフロップが、データを取り込むためのイネーブル条件付きであるか否かを判別する手段と、

前記判別手段の判別結果に基づき、イネーブル条件付きのフリップフロップをグループ化してモジュールに分割し、イネーブル条件付きでないフリップフロップをグループ化して別のモジュールに分割する手段と、

少なくとも、前記イネーブル条件付きのフリップフロップ間でのデータ転送経路を解析し、その経路総数を調べる手段と、

前記経路総数に基づき、モジュール分割後のモジュール間でのデータ転送を行う信号数が少なくなるように、前記分割したイネーブル条件付きのフリップフロップが含まれるモジュールを再分割する手段と、

系統の異なるクロック信号が供給されるモジュール間のデータ転送経路に、送信側のモジュールに供給するクロック信号を反転したクロック信号で駆動されるフリップフロップを挿入する手段と、

前記イネーブル条件付きのフリップフロップが含まれる各モジュールについてそのモジュール内のフリップフロップがデータを取り込むタイミングのみでクロック信号が供給されるようにするクロックイネーブル条件を生成する回路を生成する手段と、

前記イネーブル条件付きのフリップフロップが含まれる各モジュールに対しては各モジュールに対する前記クロックイネーブル条件に基づき、そのモジュール内のフリップフロップがデータを取り込むタイミングではクロック供給となりその他のタイミングではクロック供給停止となる供給・停止付きのクロック信号を生成する一方、前記イネーブル条件付きでないフリップフロップが含まれる各モジュールに対してはそのモジュール内のフリップフロップがデータの取り込みを連続して行うように常にクロック供給となるクロック信号を供給する回路を生成する手段と、

前記の各手段によって生成された論理記述データを設計結果として出力する手段と、

を備えたことを特徴とする低消費電力回路の設計支援装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109259A JP4319081B2 (ja) | 2004-04-01 | 2004-04-01 | 低消費電力回路の設計支援装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109259A JP4319081B2 (ja) | 2004-04-01 | 2004-04-01 | 低消費電力回路の設計支援装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005293372A true JP2005293372A (ja) | 2005-10-20 |

| JP4319081B2 JP4319081B2 (ja) | 2009-08-26 |

Family

ID=35326210

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004109259A Expired - Fee Related JP4319081B2 (ja) | 2004-04-01 | 2004-04-01 | 低消費電力回路の設計支援装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4319081B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN114970415A (zh) * | 2022-04-14 | 2022-08-30 | Oppo广东移动通信有限公司 | 电路生成方法及装置、存储介质及电子设备 |

-

2004

- 2004-04-01 JP JP2004109259A patent/JP4319081B2/ja not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN114970415A (zh) * | 2022-04-14 | 2022-08-30 | Oppo广东移动通信有限公司 | 电路生成方法及装置、存储介质及电子设备 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4319081B2 (ja) | 2009-08-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| Thonnart et al. | A fully-asynchronous low-power framework for GALS NoC integration | |

| Muttersbach et al. | Practical design of globally-asynchronous locally-synchronous systems | |

| US8286025B1 (en) | Selection of port adapters for clock crossing boundaries | |

| US9098666B2 (en) | Clock distribution network for 3D integrated circuit | |

| Kasapaki et al. | Argo: A time-elastic time-division-multiplexed noc using asynchronous routers | |

| Vitullo et al. | Low-complexity link microarchitecture for mesochronous communication in networks-on-chip | |

| US8578074B2 (en) | First in first out device and method thereof | |

| US20090271747A1 (en) | Logic circuit designing device, logic circuit designing method and logic circuit designing program for asynchronous logic circuit | |

| US8225259B1 (en) | Apparatus and methods for time-multiplex field-programmable gate arrays with multiple clocks | |

| Ax et al. | Comparing synchronous, mesochronous and asynchronous NoCs for GALS based MPSoCs | |

| US6711089B2 (en) | Method and apparatus for performing signal synchronization | |

| US20020029361A1 (en) | Logic circuit design method and logic circuit | |

| JP2002524790A (ja) | 同期多相クロック分配システム | |

| Takizawa et al. | A design support tool set for asynchronous circuits with bundled-data implementation on FPGAs | |

| JP4319081B2 (ja) | 低消費電力回路の設計支援装置 | |

| JP2007027841A (ja) | 半導体集積回路の設計装置と方法並びにプログラム | |

| Ludovici et al. | Comparing tightly and loosely coupled mesochronous synchronizers in a NoC switch architecture | |

| JPH10133768A (ja) | クロックシステム、半導体装置、半導体装置のテスト方法、及びcad装置 | |

| Pilato et al. | A runtime adaptive controller for supporting hardware components with variable latency | |

| WO2024066950A1 (zh) | 一种信号处理方法、信号处理装置、芯片及电子设备 | |

| US7676685B2 (en) | Method for improving the data transfer in semi synchronous clock domains integrated circuits at any possible m/n clock ratio | |

| Nag et al. | An autonomous clock gating technique in finite state machines based on registers partitioning | |

| KR100734521B1 (ko) | 시스템 온 칩을 위한 ip 모듈 | |

| Agiwal et al. | An architecture and a wrapper synthesis approach for multi-clock latency-insensitive systems | |

| JP2004326222A (ja) | データ処理システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061215 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090223 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090303 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090428 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090526 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090527 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120605 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130605 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |