JP2005293333A - リアルタイム制御システム - Google Patents

リアルタイム制御システム Download PDFInfo

- Publication number

- JP2005293333A JP2005293333A JP2004108735A JP2004108735A JP2005293333A JP 2005293333 A JP2005293333 A JP 2005293333A JP 2004108735 A JP2004108735 A JP 2004108735A JP 2004108735 A JP2004108735 A JP 2004108735A JP 2005293333 A JP2005293333 A JP 2005293333A

- Authority

- JP

- Japan

- Prior art keywords

- real

- host computer

- control system

- device controller

- time control

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Programmable Controllers (AREA)

- Testing And Monitoring For Control Systems (AREA)

Abstract

【課題】

【解決手段】

ホストコンピュータ10と、フィールドデバイスDSの制御を行う複数のデバイスコントローラが接続され、フィールドデバイスDSをリアルタイムで制御する。ホストコンピュータ10は、デバイスコントローラ100への制御内容を、一定時間で処理可能なファンクションに分割して転送し、デバイスコントローラ100は、ホストコンピュータ10から転送されたファンクションに基づいて、フィールドデバイスDSをリアルタイムで制御する。デバイスコントローラ100は、それぞれ、共通な部品で構成される標準部110と、接続されるフィールドデバイスによって異なる構成を持つ拡張部150とから分割して構成され、標準部110と拡張部150とは、コネクタC10,C20を介してバス接続される。

【選択図】 図1

Description

かかる構成により、システム全体としてリソースを有効活用し、開発から生産終了までの製品コストを削減し得るものとなる。

最初に、図1を用いて、本実施形態によるリアルタイム制御システムを適用した理化学装置の全体構成について説明する。

図1は、本発明の一実施形態によるリアルタイム制御システムを適用した理化学装置の全体構成を示す概略斜視図である。

図2(A),(B)は、本発明の一実施形態によるリアルタイム制御システムに用いるUSB伝送路30Cのバストポロジーの説明図である。

図3は、本発明の一実施形態によるリアルタイム制御システムに用いるUSBデバイスの伝送線伝送路の説明図である。

図4は、本発明の一実施形態によるリアルタイム制御システムに用いるデバイスコントローラの構成を示すブロック図である。なお、図1と同一符号は、同一部分を示している。

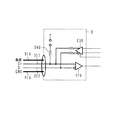

図5は、本発明の一実施形態によるリアルタイム制御システムに用いるデバイスコントローラ標準部と拡張部の接続コネクタの構成を示すブロック図である。なお、図4と同一符号は、同一部分を示している。

図6は、本発明の一実施形態によるリアルタイム制御システムに用いるデバイスコントローラの初期化処理の内容を示すフローチャートである。図6において、図6(A)は、ホストコンピュータ10の初期化処理の内容を示し、図6(B)は、デバイスコントローラ100の初期化処理の内容を示している。

図7は、本発明の一実施形態によるリアルタイム制御システムに用いるデバイスコントローラのキャッシュメモリの構成を示すメモリマップである。

図8は、本発明の一実施形態によるリアルタイム制御システムにおけるファンクションの実行処理の内容を示すフローチャートであり、図9は、本発明の一実施形態によるリアルタイム制御システムで用いられるファンクションの説明図である。図8において、図8(A)は、ホストコンピュータ10のファンクション転送処理の内容を示し、図8(B)は、デバイスコントローラ100のファンクション実行処理の内容を示している。

30C…USB伝送線

100…デバイスコントローラ

110…デバイスコントローラ標準部

112…USBプロトコル処理部

114…シリアルパラレル変換回路

116…キャッシュメモリ

118…デバイスコントローラCPU

120…プログラムカウンタコントローラ

122…プログラムカウンタ

124…比較器

150…デバイスコントローラ拡張部

152…DI

154…DO

156…フィールドネットワークインタフェイス

158…モータコントローラ

160…モータドライバ

C10…標準部コネクタ

C20…拡張部コネクタ

Claims (8)

- ホストコンピュータと、このホストコンピュータに接続され、フィールドデバイスの制御を行う複数のデバイスコントローラとからなり、前記フィールドデバイスをリアルタイムで制御するリアルタイム制御システムにおいて、

前記ホストコンピュータは、前記デバイスコントローラへの制御内容を、一定時間で処理可能なファンクションに分割して転送し、

前記デバイスコントローラは、前記ホストコンピュータから転送されたファンクションに基づいて、前記フィールドデバイスをリアルタイムで制御することを特徴とするリアルタイム制御システム。 - 請求項1記載のリアルタイム制御システムにおいて、

前記デバイスコントローラは、それぞれ、共通な部品で構成される標準部と、接続されるフィールドデバイスによって異なる構成を持つ拡張部とから分割して構成され、前記標準部と前記拡張部とは、コネクタを介してバス接続されることを特徴とするリアルタイム制御システム。 - 請求項2記載のリアルタイム制御システムにおいて、

前記デバイスコントローラは、前記拡張部で保持している識別子を読み出し、前記ホストコンピュータに伝送し、

前記ホストコンピュータは、前記デバイスコントローラから転送された識別子に基づいて、複数の前記デバイスコントローラを識別することを特徴とするリアルタイム制御システム。 - 請求項1記載のリアルタイム制御システムにおいて、

前記デバイスコントローラは、前記ホストコンピュータから転送されたファンクションを格納する揮発性メモリを備えたことを特徴とするリアルタイム制御システム。 - 請求項1記載のリアルタイム制御システムにおいて、

前記ホストコンピュータは、前記デバイスコントローラに対し、前記ファンクションを一定周期で送付することを特徴とするリアルタイム制御システム。 - 請求項5記載のリアルタイム制御システムにおいて、

前記ホストコンピュータは、USB(Universal Serial Bus)を用いて、前記デバイスコントローラに前記ファンクションを転送することを特徴とするリアルタイム制御システム。 - 請求項1記載のリアルタイム制御システムにおいて、

前記デバイスコントローラは、前記ファンクションを実行した結果を、返値として前記ホストコンピュータに送信することを特徴とするリアルタイム制御システム。 - 請求項1記載のリアルタイム制御システムにおいて、

前記ホストコンピュータ及び複数の前記デバイスコントローラは、ツリー型にネットワークにより接続されたことを特徴とするリアルタイム制御システム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108735A JP4418283B2 (ja) | 2004-04-01 | 2004-04-01 | リアルタイム制御システム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108735A JP4418283B2 (ja) | 2004-04-01 | 2004-04-01 | リアルタイム制御システム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005293333A true JP2005293333A (ja) | 2005-10-20 |

| JP4418283B2 JP4418283B2 (ja) | 2010-02-17 |

Family

ID=35326182

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004108735A Expired - Fee Related JP4418283B2 (ja) | 2004-04-01 | 2004-04-01 | リアルタイム制御システム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4418283B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009201245A (ja) * | 2008-02-21 | 2009-09-03 | Toshiba Corp | ディジタル保護継電器 |

| JP2009258790A (ja) * | 2008-04-11 | 2009-11-05 | Nst:Kk | 制御装置及び制御装置の制御方法 |

| US7786453B2 (en) | 2006-07-26 | 2010-08-31 | Nuflare Technology, Inc. | Charged-particle beam pattern writing method and apparatus with a pipeline process to transfer data |

-

2004

- 2004-04-01 JP JP2004108735A patent/JP4418283B2/ja not_active Expired - Fee Related

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7786453B2 (en) | 2006-07-26 | 2010-08-31 | Nuflare Technology, Inc. | Charged-particle beam pattern writing method and apparatus with a pipeline process to transfer data |

| JP2009201245A (ja) * | 2008-02-21 | 2009-09-03 | Toshiba Corp | ディジタル保護継電器 |

| JP2009258790A (ja) * | 2008-04-11 | 2009-11-05 | Nst:Kk | 制御装置及び制御装置の制御方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4418283B2 (ja) | 2010-02-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN113872796B (zh) | 服务器及其节点设备信息获取方法、装置、设备、介质 | |

| US4622633A (en) | Object building method for self configuring computer network | |

| US4635192A (en) | Self configuring bus structure for computer network | |

| JPH05158511A (ja) | 着脱式ファンクション・カード付きプログラマブル・コントローラ・プロセッサ | |

| US8543976B1 (en) | Generation of multi-domain code from a graphical program | |

| CN102902650A (zh) | 数据共享及传输的系统及方法 | |

| US20140359189A1 (en) | Systems and methods for providing connections to an information handling system | |

| US20170039151A1 (en) | Universal intelligent platform management interface (ipmi) host to baseboard management controller (bmc) communication for non-x86 and legacy free systems | |

| CN106598898A (zh) | 共享总线端口的系统及共享总线端口的方法 | |

| US10963406B2 (en) | Persistent universal serial bus (USB) device enumeration | |

| JP4418283B2 (ja) | リアルタイム制御システム | |

| EP3382567B1 (en) | Multiple storage devices implemented using a common connector | |

| KR20070108410A (ko) | 호스트 제어기 상에서의 독립적이면서 동시적인 데이터전달을 위한 방법 및 장치 | |

| JPH03196225A (ja) | プログラマブル割込みコントローラ | |

| JP4359618B2 (ja) | コンフィグレーション・レジスター・アクセス方法、設定方法、集積回路部品、コンピューター・システム、製品 | |

| KR950008229B1 (ko) | 퍼스널 컴퓨터 시스템 | |

| EP4675454A1 (en) | Processor platform, circuit board, and server | |

| CN113824741A (zh) | 一种iic设备的通信方法、装置、设备、系统及介质 | |

| TWI749658B (zh) | 具自動更新韌體功能的usb集線裝置及具有該usb集線裝置的主機系統 | |

| JP2940841B2 (ja) | プログラマブル制御装置用プロセッサ・モジュール | |

| JP2002342256A (ja) | データプロセッサ及びデータテーブルの更新方法 | |

| JP2582504B2 (ja) | パーソナル・コンピュータ・システム | |

| CN113806282A (zh) | 异构控制系统及异构控制系统的加载方法 | |

| CN202615386U (zh) | 一种单板及数据处理系统 | |

| CN112416832B (zh) | 基于mips架构处理器的通信系统 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060525 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20081111 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20081118 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090623 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090701 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091124 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091127 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4418283 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121204 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131204 Year of fee payment: 4 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |