JP2005292566A - 電気光学装置及び電子機器 - Google Patents

電気光学装置及び電子機器 Download PDFInfo

- Publication number

- JP2005292566A JP2005292566A JP2004109084A JP2004109084A JP2005292566A JP 2005292566 A JP2005292566 A JP 2005292566A JP 2004109084 A JP2004109084 A JP 2004109084A JP 2004109084 A JP2004109084 A JP 2004109084A JP 2005292566 A JP2005292566 A JP 2005292566A

- Authority

- JP

- Japan

- Prior art keywords

- circuit chip

- electro

- pixels

- basic

- optical device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Electroluminescent Light Sources (AREA)

Abstract

【課題】 電気光学装置の製造コストの削減を可能とする技術を提供すること。

【解決手段】 複数の色画素を含んでなる基本画素をマトリクス状に複数配列した表示領域を備え、当該表示領域が線順次走査方式で駆動される電気光学装置であって、複数の色画素を構成する複数の電気光学素子と、複数の基本画素のうち垂直走査方向に隣接配置される2つの基本画素ごとに1つ設けられて当該2つの基本画素を制御するための回路チップ(16)と、複数の配線(走査線51,524、データ線41R等、電源線53R等)と、これら配線と回路チップとの相互間に設けられる複数の接続端子(63)と、を含み、回路チップとデータ線との電気的接続を担う接続端子が、回路チップ内の各駆動回路のうちで隣接配置される2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられているものである。

【選択図】 図2

【解決手段】 複数の色画素を含んでなる基本画素をマトリクス状に複数配列した表示領域を備え、当該表示領域が線順次走査方式で駆動される電気光学装置であって、複数の色画素を構成する複数の電気光学素子と、複数の基本画素のうち垂直走査方向に隣接配置される2つの基本画素ごとに1つ設けられて当該2つの基本画素を制御するための回路チップ(16)と、複数の配線(走査線51,524、データ線41R等、電源線53R等)と、これら配線と回路チップとの相互間に設けられる複数の接続端子(63)と、を含み、回路チップとデータ線との電気的接続を担う接続端子が、回路チップ内の各駆動回路のうちで隣接配置される2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられているものである。

【選択図】 図2

Description

本発明は、薄膜トランジスタ等の素子を用いて画素駆動を行う表示装置(電気光学装置)及びその製造方法に関する。

薄膜トランジスタを画素駆動に用いる表示装置(電気光学装置)、例えば、薄膜トランジスタ駆動液晶表示装置、薄膜トランジスタ駆動有機エレクトロルミネッセンス表示装置、薄膜トランジスタ駆動発光ダイオード表示装置、薄膜トランジスタ駆動電気泳動表示装置などでは、薄膜トランジスタは装置全体の一部分をなすものであり、それ以外の大部分は配線や支持基板などからなる場合が少なくない。このような表示装置(薄膜トランジスタ駆動表示装置)を、薄膜トランジスタと配線や支持基板を一体として同一の製造プロセスを経て製造する場合には、薄膜トランジスタを作成するための高度で複雑な製造プロセスが必要とされるため、一般的に、製造コストが高額になる。しかしながら、配線や支持基板だけのためには、高度で複雑な製造プロセスは必要とされず、製造コストは安価である。もし、薄膜トランジスタと配線や支持基板を別個に作成し、必要とされる部分にだけ薄膜トランジスタを配置することができれば、薄膜トランジスタ駆動表示装置の製造コストを低減することが可能である。

このような要望に対して、転写元基材上に剥離層を介して、薄膜トランジスタ等の素子からなる被転写層を形成し、これを総て転写先基材に接合してから剥離層に光を照射し剥離を生じさせ、転写元基材を剥離層から離脱させることにより、転写先基材上の所望の位置に素子を形成する転写方法が開発されている。このような転写方法は、例えば、特開平10−125931号公報に開示されている(特許文献1)。上述した転写方法を用いることにより、必要とされる部分にだけ薄膜トランジスタを配置することができるので、全体として平均すれば、この薄膜トランジスタ駆動表示装置の製造コストを低減することが可能となる。

上述した転写方法を用いて電気光学装置(表示装置)を製造する場合に、被転写体と転写先基材との相互間に接続端子(電極パッド)を介在させて両者間を電気的に接続するフリップチップ接続を採用することが検討されている。現状では、接続信頼性を確保するために、比較的大きな接続端子を設ける必要がある。このため、回路チップ全体の面積は、集積される電気回路の占める面積よりも接続端子を配置するための面積が支配的である。このような理由により回路チップの面積の削減が難しいことから、単位面積当たりに形成可能な回路チップの数が少なくなり、1チップ当たりのコストの削減が難しかった。また、表示装置は通常、多数の画素を有することから、これらの画素のそれぞれに上記転写技術などを用いて薄膜回路を形成する場合には、回路チップの実装回数が非常に多くなり製造コストの削減の妨げとなる。

そこで、本発明は、有機EL表示装置等の電気光学装置の製造コストの削減を可能とする技術を提供することを目的とする。

第1の態様の本発明は、複数の色画素を含んでなる基本画素をマトリクス状に複数配列した表示領域を備え、当該表示領域が線順次走査方式で駆動される電気光学装置であって、複数の上記色画素を構成する複数の電気光学素子と、複数の上記基本画素のうち、垂直走査方向に隣接配置される2つの基本画素ごとに1つ設けられ、当該2つの基本画素に含まれる各色画素に対応する電気光学素子のそれぞれを制御するための複数の駆動回路を含む回路チップと、上記電気光学素子の駆動に用いる走査信号を上記回路チップに供給するための複数の走査線と、上記電気光学素子の駆動に用いるデータ信号を上記回路チップに供給するための複数のデータ線と、上記電気光学素子を発光させるための電力を上記回路チップに供給するための複数の電源線と、上記回路チップと、上記走査線、上記データ線及び上記電源線との相互間に設けられて電気的接続を担う複数の接続端子と、を含み、上記回路チップと上記データ線との電気的接続を担う上記接続端子は、上記回路チップ内の各駆動回路のうちで上記隣接配置される2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられている電気光学装置である。

隣接する2画素に着目し、これらに含まれる各電気光学素子のそれぞれに対する駆動回路(画素駆動回路)を1つの回路チップに集約することにより、転写技術やその他の実装技術を用いて回路チップを形成する際の実装回数(転写回数)が削減される。また、駆動回路の集約に伴い、回路チップに含まれる画素駆動回路のうち共通化が可能なものについては適宜共通配線とすることにより、当該回路チップと外部との電気的接続を担う電極パッドの数を削減してチップ面積の縮小を図ることができる。これらにより、単位面積当たりに製造可能なチップ数が増加し、かつチップの実装回数が削減されるので、有機EL表示装置等の電気光学装置の製造コストを削減することが可能となる。

また、上記回路チップと上記電源線との電気的接続を担う上記接続端子は、上記回路チップ内の各駆動回路のうちで、隣接配置される上記2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられていることが好ましい。

これにより、接続端子の数を更に削減し、チップ面積の縮小化を図ることが可能となる。

また、上記回路チップと上記走査線との電気的接続を担う上記接続端子は、上記回路チップ内の各駆動回路のうちで上記基本画素のそれぞれに対応する3つの駆動回路ごとに共用されて設けられていることが好ましい。

これにより、接続端子の数を更に削減し、チップ面積の縮小化を図ることが可能となる。

また、上記回路チップは、隣接配置される上記2つの基本画素の境界付近に配置されることが好ましい。

これにより、各基本画素と回路チップとの距離がほぼ均等になり、両者間を接続する補助配線の引き回しなどのレイアウト設計が容易となる。

また、上記回路チップ内の各駆動回路は、上記電気光学素子に流れる電流を制御する第1のトランジスタと、当該第1のトランジスタを上記データ信号に応じて動作させる第2のトランジスタと、を含んで構成されることが好ましい。

また、上記電気光学素子が有機エレクトロルミネセンス(EL)素子であることが好ましい。

これにより、低コストな有機EL表示装置が得られる。

第2の態様の本発明は、複数の色画素を含んでなる基本画素をマトリクス状に複数配列した表示領域を備え、当該表示領域が線順次走査方式で駆動される電気光学装置であって、複数の上記色画素を構成する複数の電気光学素子と、複数の上記基本画素のうち、走査タイミングが同じであり、かつ相互に隣接配置される2つの基本画素ごとに1つ設けられ、当該2つの基本画素に含まれる各色画素に対応する電気光学素子のそれぞれを制御するための複数の駆動回路を含む回路チップと、上記電気光学素子の駆動に用いる走査信号を上記回路チップに供給するための複数の走査線と、上記電気光学素子の駆動に用いるデータ信号を上記回路チップに供給するための複数のデータ線と、上記電気光学素子を発光させるための電力を上記回路チップに供給するための複数の電源線と、上記回路チップと、上記走査線、上記データ線及び上記電源線との相互間に設けられて電気的接続を担う複数の接続端子と、を含み、上記回路チップと上記走査線との電気的接続を担う上記接続端子は、上記回路チップ内の各駆動回路に共用されて設けられている電気光学装置である。

隣接する2画素に着目し、これらに含まれる各電気光学素子のそれぞれに対する駆動回路(画素駆動回路)を1つの回路チップに集約することにより、転写技術やその他の実装技術を用いて回路チップを形成する際の実装回数(転写回数)を削減している。また、駆動回路の集約に伴い、回路チップに含まれる画素駆動回路のうち共通化が可能なものについては適宜共通配線とすることにより、当該回路チップと外部との電気的接続を担う電極パッドの数を削減し、チップ面積の縮小を図ることができる。これらにより、単位面積当たりに製造可能なチップ数が増加し、かつチップの実装回数が削減されるので、有機EL表示装置等の電気光学装置の製造コストを削減することが可能となる。

また、上記回路チップと上記電源線との電気的接続を担う上記接続端子は、上記回路チップ内の各駆動回路のうちで上記隣接配置される2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられていることが好ましい。

これにより、接続端子の数を更に削減し、チップ面積の縮小化を図ることが可能となる。

また、上記回路チップは、隣接配置される上記2つの基本画素の境界付近に配置されることが好ましい。

これにより、各基本画素と回路チップとの距離がほぼ均等になり、両者間を接続する補助配線の引き回しなどのレイアウト設計が容易となる。

また、上記回路チップ内の各駆動回路は、上記電気光学素子に流れる電流を制御する第1のトランジスタと、当該第1のトランジスタを上記データ信号に応じて動作させる第2のトランジスタと、を含んで構成されることが好ましい。

また、上記電気光学素子が有機エレクトロルミネセンス(EL)素子であることが好ましい。

これにより、低コストな有機EL表示装置が得られる。

第3の態様の本発明は、複数の色画素を含んでなる基本画素をマトリクス状に複数配列した表示領域を備え、当該表示領域が線順次走査方式で駆動される電気光学装置であって、複数の上記色画素を構成する複数の電気光学素子と、複数の上記基本画素のうち、走査タイミングが同じであり隣接配置される2つの基本画素と、当該2つの基本画素のそれぞれと垂直走査方向に隣接配置される2つの基本画素とを合わせた4つの基本画素ごとに1つ設けられ、当該4つの基本画素に含まれる各色画素に対応する電気光学素子のそれぞれを制御するための複数の駆動回路を含む回路チップと、上記電気光学素子の駆動に用いる走査信号を上記回路チップに供給するための複数の走査線と、上記電気光学素子の駆動に用いるデータ信号を上記回路チップに供給するための複数のデータ線と、上記電気光学素子を発光させるための電力を上記回路チップに供給するための複数の電源線と、上記回路チップと、上記走査線、上記データ線及び上記電源線との相互間に設けられて電気的接続を担う複数の接続端子と、を含み、上記回路チップと上記走査線との電気的接続を担う上記接続端子は、上記回路チップ内の各駆動回路のうちで、上記走査タイミングが同じであり隣接配置される2つの基本画素内の各駆動回路に共用されて設けられ、上記回路チップと上記データ線との電気的接続を担う上記接続端子は、上記回路チップ内の各駆動回路のうちで上記垂直走査方向に隣接配置される2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられている電気光学装置である。

隣接する4画素に着目し、これらに含まれる各電気光学素子のそれぞれに対する駆動回路(画素駆動回路)を1つの回路チップに集約することにより、転写技術やその他の実装技術を用いて回路チップを形成する際の実装回数(転写回数)が削減される。また、駆動回路の集約に伴い、回路チップに含まれる画素駆動回路のうち共通化が可能なものについては適宜共通配線とすることにより、当該回路チップと外部との電気的接続を担う電極パッドの数を削減し、チップ面積の縮小を図ることができる。これらにより、単位面積当たりに製造可能なチップ数が増加し、かつチップの実装回数が削減されるので、有機EL表示装置等の電気光学装置の製造コストを削減することが可能となる。

また、上記回路チップと上記電源線との電気的接続を担う上記接続端子は、上記回路チップ内の各駆動回路のうちで上記基本画素内の同色の色画素のそれぞれに対応する4つの駆動回路ごとに共用されて設けられていることが好ましい。

これにより、接続端子の数を更に削減し、チップ面積の縮小化を図ることが可能となる。

また、上記回路チップは、隣接配置される上記4つの基本画素の相互の境界付近に配置されることが好ましい。

これにより、各基本画素と回路チップとの距離がほぼ均等になり、両者間を接続する補助配線の引き回しなどのレイアウト設計が容易となる。

また、上記回路チップ内の各駆動回路は、上記電気光学素子に流れる電流を制御する第1のトランジスタと、当該第1のトランジスタを上記データ信号に応じて動作させる第2のトランジスタと、を含んで構成されることが好ましい。

また、上記電気光学素子が有機エレクトロルミネセンス(EL)素子であることが好ましい。

これにより、低コストな有機EL表示装置が得られる。

第4の態様の本発明は、上記第1〜第3の態様の本発明のいずれかにかかる電気光学装置を用いて構成される電子機器である。

これにより、表示機能を備える電子機器を低コストに提供し得る。

以下、本発明を適用した一実施形態の有機EL(エレクトロルミネセンス)表示装置について説明する。

<第1の実施形態>

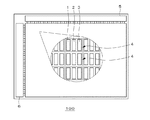

図1は、第1の実施形態の有機EL表示装置の構成について概略的に示す図である。同図に示す有機EL表示装置100は、3つの色画素1、2、3を含んで構成される基本画素4をマトリクス状に多数配列した表示領域を備え、当該表示領域が、データ線駆動回路5及び走査線駆動回路6によって線順次走査方式で駆動されて画像表示を行うものである。各色画素は、例えば、色画素1が赤色、色画素2が緑色、色画素3が青色に対応している。各画素4は、複数の薄膜トランジスタ(TFT)を含んで構成される駆動回路を内蔵した回路チップを用いて駆動される。

図1は、第1の実施形態の有機EL表示装置の構成について概略的に示す図である。同図に示す有機EL表示装置100は、3つの色画素1、2、3を含んで構成される基本画素4をマトリクス状に多数配列した表示領域を備え、当該表示領域が、データ線駆動回路5及び走査線駆動回路6によって線順次走査方式で駆動されて画像表示を行うものである。各色画素は、例えば、色画素1が赤色、色画素2が緑色、色画素3が青色に対応している。各画素4は、複数の薄膜トランジスタ(TFT)を含んで構成される駆動回路を内蔵した回路チップを用いて駆動される。

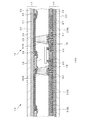

図2は、第1の実施形態における基本画素4の構造について説明する平面図であり、垂直走査方向に隣接配置される2つの基本画素4についての図を示している。なお、図2では説明の便宜上、構成要素の一部を省略して示している。図3は、基本画素4の構造について説明する断面図であり、図2におけるIII−III断面に対応している。

図3に示すように、本実施形態の有機EL表示装置100は、走査線やデータ線等の配線を備えるとともに上面に薄膜状の回路チップ(以下「薄膜回路チップ」という。)16が実装された配線基板10と、色画素を構成する有機EL素子14を備える表示素子基板12とを対向配置し、両者間を銀ペースト等の導電性部材18によって電気的に接続して構成されている。配線基板10と表示素子基板12との相互間にはアクリル樹脂等が適宜充填される。この有機EL表示装置100では、配線基板10側の薄膜回路チップ16によって、表示素子基板12側の各有機EL素子14を駆動している。図示の有機EL素子14が3つ1組となって1つの画素(基本画素4)を構成しており、垂直走査方向に隣接配置される2つの基本画素4に対応する画素駆動回路が1つの薄膜回路チップ16に含まれている。そして、薄膜回路チップ16は、隣接配置される2つの基本画素4の境界付近に配置されている。なお、図2では、表示素子基板12等が省略され、配線基板10の平面図(薄膜回路チップを除く)が示されている。配線基板10上への薄膜回路チップ16の形成は、例えば上述した特許文献1「特開平10−125931号公報」等に開示されるデバイス転写技術を用いて行われる。

配線基板10は、ガラス基板或いはフレキシブル基板等からなる基材20と、当該基材20上に形成された酸化硅素膜等の絶縁膜21、22と、絶縁膜21、22の内部に設けられたアルミニウム膜等の配線(詳細は後述する)とを含んで構成される。上述した薄膜回路チップ16は、ニッケル等からなる接続端子63を介して配線基板10側の配線と電気的に接続される。

表示素子基板12は、ガラス基板或いはフレキシブル基板等の透明基材30と、ITO等の透明導電膜からなり透明基材30上に設けられる透明電極(アノード)31と、当該透明電極31上にポリイミド等の絶縁物を用いて形成されており、所定位置に開口を有するバンク(隔壁)32、33と、当該バンク32、33の開口内に形成された正孔注入層34及び発光層35と、アルミニウム等からなり発光層35の上面に形成される電極(カソード)36と、を含んで構成されている。アノード31、正孔注入層34、発光層35及びカソード36を含んで有機EL素子14が構成されており、発光層35に電流を供給することにより当該発光層35から光が放出され、アノード31及び透明基材30を介して外部に放出される。すなわち、本例の有機EL表示装置100はいわゆるトップエミッション構造を採用している。上述した正孔輸送層34は、例えばポリエチレンジオキシチオフェンとポリスチレンスルフォン酸の混合体(PEDOT/PSS)を用いて形成され、発光層35は例えばポリジアルキルフルオレン誘導体を用いて形成される。

次に、主に図2を参照しながら配線基板10について更に詳細に説明する。図示のように、配線基板10上には、上述したデータ線駆動回路5と接続される複数のデータ線41R、41G、41Bと、電源引き込み用に用いられる引込配線43R、43G、43Bと、上述した走査線駆動回路6と接続される複数の走査線51、52と、図示しない電源と接続される電源線53R、53G、53Bと、各有機EL素子14と配線基板10との電気的接続を担う電極パッド(接続端子)61R、61G、61B、62R、62G、62Bと、薄膜回路チップ16と配線基板10との電気的接続を担う14個の電極パッド(接続端子)63と、を含んで構成されている。データ線41R等及び引込配線43Rを含んで第1配線層が構成され、基材20上に配置されている。また、走査線51等及び電源線53R等を含んで第2配線層が構成され、上記第1配線層の上側に配置されている。上述した薄膜回路チップ16は、図中、点線で示すように電極パッド63の上側に配置される。

データ線41R等は、有機EL素子14の駆動に用いるデータ信号を薄膜回路チップ16に供給するためのものであり、アルミニウム等の導電体膜からなる。これらのデータ線41R等は、第2配線層に含まれる補助配線と接続されており、当該補助配線を介して所定の電極パッド63と接続されている。これらのデータ線41R等は、垂直走査方向(線順次走査の進行方向)に沿って隣接配置される各基本画素4によって共用される。データ線41Rが色画素1(赤色)に対応し、データ線41Gが色画素2(緑色)に対応し、データ線41Bが色画素3(青色)に対応している。

引込配線43R等は、電源線53R等を介して供給される電力を薄膜回路チップ16に伝達するために便宜上用いられるものであり、アルミニウム等の導電体膜からなる。これらの引込配線43R等は、第2配線層に含まれる補助配線と接続されており、当該補助配線を介して所定の電極パッド63と接続されている。これらの引込配線43R等は、垂直走査方向(線順次走査の進行方向)に沿って隣接配置される各基本画素4によって共用される。引込配線43Rが色画素1(赤色)に対応し、引込配線43Gが色画素2(緑色)に対応し、引込配線43Bが色画素3(青色)に対応している。

走査線51等は、有機EL素子14の駆動に用いる走査信号を薄膜回路チップ16に供給するためのものであり、アルミニウム等の導電体膜からなる。これらの走査線51等は、第1配線層に含まれる補助配線と接続されており、当該補助配線を介して所定の電極パッド63と接続されている。走査線51、52のそれぞれは、水平走査方向に沿って隣接配置される一列分の各基本画素4によって共用される。

電源線53R等は、図示しない電源と接続され、有機EL素子14を発光させるための電力を薄膜回路チップ16に供給するためのものであり、アルミニウム等の導電体膜からなる。これらの電源線53R等は、第1配線層に含まれる引込配線42R等及び第2配線層に含まれる補助配線を介して所定の電極パッド63と接続されている。そして、これらの電源線53R等のそれぞれは、水平走査方向に沿って隣接配置される二列分の各基本画素4によって共用される。電源線53Rが色画素1(赤色)に対応し、電源線53Gが色画素2(緑色)に対応し、電源線53Bが色画素3(青色)に対応している。

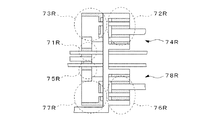

図4は、薄膜回路チップ16に含まれる回路の例を説明する図である。また、図5は、図4に示す薄膜回路チップ16のより具体的な構成例(薄膜回路のレイアウト例)を示す図である。図6は、図5に示す薄膜回路の部分的な拡大図である。これらの図に示す駆動回路は、スイッチングトランジスタ、ドライビングトランジスタ及び保持容量を各1つずつ含んで一の有機EL素子14に対応する画素駆動回路が構成されており、当該有機EL素子14に流す電流を制御する機能を有する。ドライビングトランジスタ(第1のトランジスタ)は有機EL素子14に流れる電流を制御するものであり、スイッチングトランジスタ(第2のトランジスタ)はドライビングトランジスタをデータ信号に応じて動作させるものである。

具体的には、スイッチングトランジスタ71R、ドライビングトランジスタ72R及び保持容量73Rを組み合わせて色画素1に対応する有機EL素子14の画素駆動回路74Rが構成され、スイッチングトランジスタ71G、ドライビングトランジスタ72G及び保持容量73Gを組み合わせて色画素2に対応する有機EL素子14の画素駆動回路74Gが構成され、スイッチングトランジスタ71B、ドライビングトランジスタ72B及び保持容量73Bを組み合わせて色画素3に対応する有機EL素子14の画素駆動回路74Bが構成されている。これら3つの画素駆動回路を含んで一の基本画素4の画素駆動回路が構成されている。そして、当該回路において各スイッチングトランジスタ71R、71G、71Bのゲートが共通化されており、外部接続端子としての電極パッド80aが設けられている。この電極パッド80aは、配線基板10側に対向配置される一の電極パッド63と当接することにより薄膜回路チップ16と走査線51との電気的接続を担うものであり、一の基本画素に対応する3つの画素駆動回路74R、74G、74Bごとに共用されて1つ設けられている。

同様に、スイッチングトランジスタ75R、ドライビングトランジスタ76R及び保持容量77Rを組み合わせて色画素1に対応する有機EL素子14の画素駆動回路78Rが構成され、スイッチングトランジスタ75G、ドライビングトランジスタ76G及び保持容量77Gを組み合わせて色画素2に対応する有機EL素子14の画素駆動回路78Gが構成され、スイッチングトランジスタ75B、ドライビングトランジスタ76B及び保持容量77Bを組み合わせて色画素3に対応する有機EL素子14の画素駆動回路78Bが構成されている。これら3つの画素駆動回路を含んで一の基本画素4の画素駆動回路が構成されている。そして、当該回路において各スイッチングトランジスタのゲートが共通化されており、当該回路において各スイッチングトランジスタ75R、75G、75Bのゲートが共通化されており、外部接続端子としての電極パッド80bが設けられている。この電極パッド80bは、配線基板10側に対向配置される一の電極パッド63と当接することにより薄膜回路チップ16と走査線52との電気的接続を担うものであり、一の基本画素に対応する3つの画素駆動回路78R、78G、78Bごとに共用されて1つ設けられている。

また、隣接する2つの基本画素4に対応する2つの画素駆動回路において、スイッチングトランジスタ71Rと75R、スイッチングトランジスタ71Gと75G、スイッチングトランジスタ71Bと75Bのそれぞれについてソースが共通化されており、外部接続端子としての電極パッド80c、80d、80eがそれぞれ設けられている。これらの電極パッド80c等は、配線基板10側に対向配置される各電極パッド63とそれぞれ当接することにより薄膜回路チップ16と各データ線41R、41G、41Bのそれぞれとの電気的接続を担うものであり、薄膜回路チップ16内の各駆動回路のうちで隣接配置される2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられている。詳細には、画素駆動回路74R及び78Rにより電極パッド80cが共用され、画素駆動回路74G及び78Gにより電極パッド80dが共用され、画素駆動回路74B及び78Bにより電極パッド80eが共用されている。

また、隣接する2つの基本画素4に対応する2つの画素駆動回路において、ドライビングトランジスタ72Rと76R、ドライビングトランジスタ72Gと76G、ドライビングトランジスタ72Bと76B、のそれぞれについてソースが共通化されており、外部接続端子としての電極パッド80f、80g、80hがそれぞれ設けられている。これらの電極パッド80f等は、配線基板10側に対向配置される各電極パッド63のそれぞれと当接することにより、薄膜回路チップ16と各電源線42R、42G、42Bのそれぞれとの電気的接続を担うものであり、薄膜回路チップ16内の各駆動回路のうちで隣接配置される2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられている、詳細には、画素駆動回路74R及び78Rにより電極パッド80fが共用され、画素駆動回路74G及び78Gにより電極パッド80gが共用され、画素駆動回路74B及び78Bにより電極パッド80hが共用されている。

また、各ドライビングトランジスタ74R、74G、74B、78R、78G、78Bのドレインに対して、各電極パッド80i、80j、80k、80m、80n、80pがそれぞれ設けられている。これらの電極パッド80i等が配線基板10側に対向配置される各電極パッド63と当接することにより、各有機EL素子14に対して電流が供給される。

このように、本実施形態では、隣接する2画素に着目し、これらに含まれる各有機EL素子14のそれぞれに対する駆動回路(画素駆動回路)を1つの薄膜回路チップ16に集約することにより、転写技術やその他の実装技術を用いて薄膜回路チップ16を形成する際の実装回数(転写回数)を削減している。また、駆動回路の集約に伴い、薄膜回路チップ16に含まれる画素駆動回路のうち共通化が可能なものについては適宜共通配線とすることにより、当該薄膜回路チップ16と外部との電気的接続を担う電極パッドの数を削減し、チップ面積の縮小を図っている。これらにより、単位面積当たりに製造可能なチップ数が増加し、かつチップの実装回数が削減されるので、有機EL表示装置の製造コストを削減することが可能となる。

また、本実施形態では、電源線の共用化によって当該電源線を配置可能な面積を増加させることが可能となり、各電源線を広幅化することができる。これにより、電源線を介して電力供給を行う際の電圧降下による影響を低減することが可能となる。

<第2の実施形態>

第2の実施形態として、複数の基本画素のうち水平走査方向に隣接する2つの画素、すなわち走査タイミングが同じであり、かつ相互に隣接配置される2つの基本画素ごとに、当該2つの基本画素に含まれる各色画素に対応する有機EL素子のそれぞれを制御するための複数の駆動回路を含む薄膜回路チップを設けるようにした有機EL表示装置を説明する。なお、上記第1の実施形態の有機EL表示装置と重複する内容については適宜説明を省略する。

第2の実施形態として、複数の基本画素のうち水平走査方向に隣接する2つの画素、すなわち走査タイミングが同じであり、かつ相互に隣接配置される2つの基本画素ごとに、当該2つの基本画素に含まれる各色画素に対応する有機EL素子のそれぞれを制御するための複数の駆動回路を含む薄膜回路チップを設けるようにした有機EL表示装置を説明する。なお、上記第1の実施形態の有機EL表示装置と重複する内容については適宜説明を省略する。

図7は、第2の実施形態における基本画素4の構造について説明する平面図であり、垂直走査方向に隣接配置される2つの基本画素4についての図を示している。なお、図7では説明の便宜上、構成要素の一部を省略して示している。なお、基本画素4の断面構造については上述した図3に示すものと同様でありここでは説明を省略する。

以下、図7を参照しながら、第2の実施形態における配線基板10について詳細に説明する。図示のように、配線基板10上には、上述したデータ線駆動回路5と接続される複数のデータ線141R、141G、141B、143R、143G、143Bと、電源引き込み用に用いられる引込配線142R、142G、142Bと、上述した走査線駆動回路6と接続される走査線151と、図示しない電源と接続される電源線153R、153G、153Bと、各有機EL素子14と配線基板10との電気的接続を担う電極パッド(接続端子)161R、161G、161B、162R、162G、162Bと、薄膜回路チップ116(詳細は後述する)と配線基板10との電気的接続を担う16個の電極パッド(接続端子)163と、を含んで構成されている。データ線141R等及び引込配線142Rを含んで第1配線層が構成され、基材20上に配置されている。また、走査線151等及び電源線153R等を含んで第2配線層が構成され、上記第1配線層の上側に配置されている。上述した薄膜回路チップ116は、電極パッド163の上側に配置される。

データ線141R等は、有機EL素子14の駆動に用いるデータ信号を薄膜回路チップ116に供給するためのものであり、アルミニウム等の導電体膜からなる。これらのデータ線141R等は、第2配線層に含まれる補助配線と接続されており、当該補助配線を介して所定の電極パッド163と接続されている。これらのデータ線141R等は、垂直走査方向(線順次走査の進行方向)に沿って隣接配置される各基本画素4によって共用される。データ線141R、143Rが色画素1(赤色)に対応し、データ線141G、143Gが色画素2(緑色)に対応し、データ線141B、143Bが色画素3(青色)に対応している。

引込配線142R等は、電源線153R等を介して供給される電力を薄膜回路チップ116に伝達するために便宜上用いられるものであり、アルミニウム等の導電体膜からなる。これらの引込配線142R等は、第2配線層に含まれる補助配線と接続されており、当該補助配線を介して所定の電極パッド163と接続されている。これらの引込配線142R等は、垂直走査方向(線順次走査の進行方向)に沿って隣接配置される各基本画素4によって共用される。引込配線142Rが色画素1(赤色)に対応し、引込配線142Gが色画素2(緑色)に対応し、引込配線142Bが色画素3(青色)に対応している。

走査線151は、有機EL素子14の駆動に用いる走査信号を薄膜回路チップ116に供給するためのものであり、アルミニウム等の導電体膜からなる。なお、同様にして、図示しない走査線が垂直走査方向に沿って複数設けられている。これらの走査線151等は、第1配線層に含まれる補助配線と接続されており、当該補助配線を介して所定の電極パッド163と接続されている。走査線151は、水平走査方向に沿って隣接配置される一列分の各基本画素4によって共用される。本実施形態では、水平走査方向に隣接配置される2つの基本画素4ごとに1つの電極パッド163が割り当てられ、当該電極パッド163を介して走査線151と薄膜回路チップ116とが電気的に接続される。

電源線153R等は、有機EL素子14を発光させるための電力を薄膜回路チップ116に供給するためのものであり、アルミニウム等の導電体膜からなる。これらの電源線153R等は、第1配線層に含まれる引込配線142R等及び第2配線層に含まれる補助配線を介して所定の電極パッド163と接続されている。そして、これらの電源線153R等のそれぞれは、水平走査方向に沿って隣接配置される一列分の各基本画素4によって共用される。電源線153Rが色画素1(赤色)に対応し、電源線153Gが色画素2(緑色)に対応し、電源線153Bが色画素3(青色)に対応している。

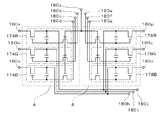

図8は、薄膜回路チップ116に含まれる回路の例を説明する図である。また、図9は、図8に示す薄膜回路チップ116のより具体的な構成例(薄膜回路のレイアウト例)を示す図である。なお、薄膜回路の部分的な拡大図については上記図6に示すものと同様である。これらの図に示す駆動回路は、スイッチングトランジスタ、ドライビングトランジスタ及び保持容量を各1つずつ含んで一の有機EL素子14に対応する画素駆動回路が構成されており、当該有機EL素子14に流す電流を制御する機能を有する。ドライビングトランジスタ(第1のトランジスタ)は有機EL素子14に流れる電流を制御するものであり、スイッチングトランジスタ(第2のトランジスタ)はドライビングトランジスタをデータ信号に応じて動作させるものである。

具体的には、図中左側の基本画素4については、色画素1に対応する有機EL素子14の画素駆動回路174Rが構成され、色画素2に対応する有機EL素子14の画素駆動回路174Gが構成され、色画素3に対応する有機EL素子14の画素駆動回路174Bが構成されている。これら3つの画素駆動回路を含んで一の基本画素4の画素駆動回路が構成されている。また、図中右側の基本画素4については、色画素1に対応する有機EL素子14の画素駆動回路178Rが構成され、色画素2に対応する有機EL素子14の画素駆動回路178Gが構成され、色画素3に対応する有機EL素子14の画素駆動回路178Bが構成されている。これら3つの画素駆動回路を含んで一の基本画素4の画素駆動回路が構成されている。各画素駆動回路の詳細内容については上述した第1の実施形態と同様である。そして、当該回路において各スイッチングトランジスタのゲートが共通化されており、外部接続端子としての電極パッド180aが設けられている。この電極パッド180aは、配線基板10側に対向配置される一の電極パッド163と当接することにより薄膜回路チップ116と走査線151との電気的接続を担うものであり、隣接する2つの基本画素4に対応する6つの画素駆動回路ごとに共用されて1つ設けられている。

また、隣接する2つの基本画素4に対応する2つの画素駆動回路において、各スイッチングトランジスタのソースに対して外部接続端子としての電極パッド180b、180c、180d、180e、180f、180gがそれぞれ設けられている。これらの電極パッド180b等は、配線基板10側に対向配置される各電極パッド163とそれぞれ当接することにより薄膜回路チップ116と各データ線141R等のそれぞれとの電気的接続を担う。

また、隣接する2つの基本画素4に対応する2つの画素駆動回路における各色画素ごとに各ドライビングトランジスタのソースが共通化されており、外部接続端子としての電極パッド180h、180i、180jがそれぞれ設けられている。これらの電極パッド180h等は、配線基板10側に対向配置される各電極パッド163のそれぞれと当接することにより、薄膜回路チップ116と各電源線142R、142G、142Bのそれぞれとの電気的接続を担うものであり、薄膜回路チップ16内の各駆動回路のうちで隣接配置される2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられている、詳細には、画素駆動回路174R及び178Rにより電極パッド180hが共用され、画素駆動回路174G及び178Gにより電極パッド180iが共用され、画素駆動回路174B及び178Bにより電極パッド180jが共用されている。

また、各ドライビングトランジスタのドレインに対して、各電極パッド180k、180m、180n、180p、180q、180rがそれぞれ設けられている。これらの電極パッド180k等が配線基板10側に対向配置される各電極パッド163と当接することにより、各有機EL素子14に対して電流が供給される。

このように、本実施形態では、隣接する2画素に着目し、これらに含まれる各有機EL素子14のそれぞれに対する駆動回路(画素駆動回路)を1つの薄膜回路チップ16に集約することにより、転写技術やその他の実装技術を用いて薄膜回路チップ16を形成する際の実装回数(転写回数)を削減している。また、駆動回路の集約に伴い、薄膜回路チップ16に含まれる画素駆動回路のうち共通化が可能なものについては適宜共通配線とすることにより、当該薄膜回路チップ16と外部との電気的接続を担う電極パッドの数を削減し、チップ面積の縮小を図っている。これらにより、単位面積当たりに製造可能なチップ数が増加し、かつチップの実装回数が削減されるので、有機EL表示装置の製造コストを削減することが可能となる。

<第3の実施形態>

第3の実施形態として、複数の基本画素のうち隣接する4つの画素、より詳細には走査タイミングが同じであり隣接配置される2つの基本画素と、当該2つの基本画素のそれぞれと垂直走査方向に隣接配置される2つの基本画素とを合わせた4つの基本画素ごとに、当該4つの基本画素に含まれる各色画素に対応する有機EL素子のそれぞれを制御するための複数の駆動回路を含む薄膜回路チップを設けるようにした有機EL表示装置を説明する。なお、上記第1又は第2の実施形態の有機EL表示装置と重複する内容については適宜説明を省略する。

第3の実施形態として、複数の基本画素のうち隣接する4つの画素、より詳細には走査タイミングが同じであり隣接配置される2つの基本画素と、当該2つの基本画素のそれぞれと垂直走査方向に隣接配置される2つの基本画素とを合わせた4つの基本画素ごとに、当該4つの基本画素に含まれる各色画素に対応する有機EL素子のそれぞれを制御するための複数の駆動回路を含む薄膜回路チップを設けるようにした有機EL表示装置を説明する。なお、上記第1又は第2の実施形態の有機EL表示装置と重複する内容については適宜説明を省略する。

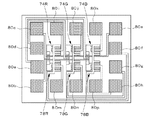

図10は、第3の実施形態における基本画素4の構造について説明する平面図であり、隣接配置される4つの基本画素4についての図を示している。なお、図10では説明の便宜上、構成要素の一部を省略して示している。なお、基本画素4の断面構造については上述した図3に示すものと同様でありここでは説明を省略する。

以下、図10を参照しながら、第3の実施形態における配線基板10について詳細に説明する。図示のように、配線基板10上には、上述したデータ線駆動回路5と接続される複数のデータ線241R、241G、241B、243R、243G、243Bと、電源引き込み用に用いられる引込配線242R、242G、242Bと、上述した走査線駆動回路6と接続される走査線251、252と、図示しない電源と接続される電源線253R、253G、253Bと、各有機EL素子14と配線基板10との電気的接続を担う電極パッド(接続端子)261R、261G、261B、262R、262G、262B、265R、265G、265B、266R、266G、266Bと、薄膜回路チップ216(詳細は後述する)と配線基板10との電気的接続を担う23個の電極パッド(接続端子)263と、を含んで構成されている。データ線241R等及び引込配線242Rを含んで第1配線層が構成され、基材20上に配置されている。また、走査線251等及び電源線253R等を含んで第2配線層が構成され、上記第1配線層の上側に配置されている。上述した薄膜回路チップ216は、電極パッド263の上側に配置される。

データ線241R等は、有機EL素子14の駆動に用いるデータ信号を薄膜回路チップ216に供給するためのものであり、アルミニウム等の導電体膜からなる。これらのデータ線241R等は、第2配線層に含まれる補助配線と接続されており、当該補助配線を介して所定の電極パッド263と接続されている。これらのデータ線241R等は、垂直走査方向(線順次走査の進行方向)に沿って隣接配置される各基本画素4によって共用される。データ線241R、243Rが色画素1(赤色)に対応し、データ線241G、243Gが色画素2(緑色)に対応し、データ線241B、243Bが色画素3(青色)に対応している。

引込配線242R等は、電源線253R等を介して供給される電力を薄膜回路チップ216に伝達するために便宜上用いられるものであり、アルミニウム等の導電体膜からなる。これらの引込配線242R等は、第2配線層に含まれる補助配線と接続されており、当該補助配線を介して所定の電極パッド263と接続されている。これらの引込配線242R等は、垂直走査方向(線順次走査の進行方向)に沿って隣接配置される各基本画素4によって共用される。引込配線242Rが色画素1(赤色)に対応し、引込配線242Gが色画素2(緑色)に対応し、引込配線242Bが色画素3(青色)に対応している。

走査線251等は、有機EL素子14の駆動に用いる走査信号を薄膜回路チップ116に供給するためのものであり、アルミニウム等の導電体膜からなる。これらの走査線251等は、第1配線層に含まれる補助配線と接続されており、当該補助配線を介して所定の電極パッド263と接続されている。走査線251等のそれぞれは、水平走査方向に沿って隣接配置される一列分の各基本画素4によって共用される。本実施形態では、水平走査方向に隣接配置される2つの基本画素4ごとに1つの電極パッド263が割り当てられ、当該電極パッド263を介して走査線251等と薄膜回路チップ216とが電気的に接続される。

電源線253R等は、有機EL素子14を発光させるための電力を薄膜回路チップ216に供給するためのものであり、アルミニウム等の導電体膜からなる。これらの電源線253R等は、第1配線層に含まれる引込配線242R等及び第2配線層に含まれる補助配線を介して所定の電極パッド263と接続されている。そして、これらの電源線253R等のそれぞれは、水平走査方向に沿って隣接配置される2列分の各基本画素4によって共用される。電源線253Rが色画素1(赤色)に対応し、電源線253Gが色画素2(緑色)に対応し、電源線253Bが色画素3(青色)に対応している。

図11は、薄膜回路チップ216に含まれる回路の例を説明する図である。また、図12は、図11に示す薄膜回路チップ216のより具体的な構成例(薄膜回路のレイアウト例)を示す図である。なお、薄膜回路の部分的な拡大図については上記図6に示すものと同様である。これらの図に示す駆動回路は、スイッチングトランジスタ、ドライビングトランジスタ及び保持容量を各1つずつ含んで一の有機EL素子14に対応する画素駆動回路が構成されており、当該有機EL素子14に流す電流を制御する機能を有する。

具体的には、図中左上側の基本画素4については、色画素1に対応する有機EL素子14の画素駆動回路274Rが構成され、色画素2に対応する有機EL素子14の画素駆動回路274Gが構成され、色画素3に対応する有機EL素子14の画素駆動回路274Bが構成されている。これら3つの画素駆動回路を含んで一の基本画素4の画素駆動回路が構成されている。また、図中右上側、図中左下側、図中右下側のそれぞれの基本画素4についても、色画素1に対応する有機EL素子14の画素駆動回路278R、294R、298Rがそれぞれが構成され、色画素2に対応する有機EL素子14の画素駆動回路278G、294G、298Gがそれぞれが構成され、色画素3に対応する有機EL素子14の画素駆動回路278B、294B、298Bがそれぞれが構成されている。各画素駆動回路の詳細内容については上述した第1の実施形態と同様である。

当該回路において各スイッチングトランジスタのゲートが共通化されており、外部接続端子としての電極パッド280a、280bがそれぞれ設けられている。これらの電極パッド180a等は、配線基板10側に対向配置される一の電極パッド263と当接することにより薄膜回路チップ216と走査線251又は252との電気的接続を担うものであり、隣接する2つの基本画素4に対応する6つの画素駆動回路ごとに共用されて1つ設けられている。

また、隣接する2つの基本画素4に対応する2つの画素駆動回路において、各スイッチングトランジスタのソースに対して外部接続端子としての電極パッド280c、280d、280e、280f、280g、280hがそれぞれ設けられている。これらの電極パッド280c等は、配線基板10側に対向配置される各電極パッド263とそれぞれ当接することにより薄膜回路チップ216と各データ線241R等のそれぞれとの電気的接続を担う。

また、隣接する2つの基本画素4に対応する2つの画素駆動回路における各色画素ごとに各ドライビングトランジスタのソースが共通化されており、外部接続端子としての電極パッド280i、280j、280kがそれぞれ設けられている。これらの電極パッド280i等は、配線基板10側に対向配置される各電極パッド263のそれぞれと当接することにより、薄膜回路チップ216と各電源線242R、242G、242Bのそれぞれとの電気的接続を担うものであり、薄膜回路チップ216内の各駆動回路のうちで隣接配置される4つの基本画素内の同色の色画素のそれぞれに対応する4つの駆動回路ごとに共用されて設けられている。詳細には、画素駆動回路274R、278R、294R及び298Rにより電極パッド280iが共用され、画素駆動回路274G、278G、294G及び298Gにより電極パッド280jが共用され、画素駆動回路274B、278B、294B及び298Bにより電極パッド280kが共用されている。

また、各ドライビングトランジスタのドレインに対して、各電極パッド280m、280n、280p、280q、280r、280s、280t、280u、280v、280w、280x、280yがそれぞれ設けられている。これらの電極パッド280m等が配線基板10側に対向配置される各電極パッド263と当接することにより、各有機EL素子14に対して電流が供給される。

このように、本実施形態では、隣接する4画素に着目し、これらに含まれる各有機EL素子14のそれぞれに対する駆動回路(画素駆動回路)を1つの薄膜回路チップ16に集約することにより、転写技術やその他の実装技術を用いて薄膜回路チップ16を形成する際の実装回数(転写回数)を削減している。また、駆動回路の集約に伴い、薄膜回路チップ16に含まれる画素駆動回路のうち共通化が可能なものについては適宜共通配線とすることにより、当該薄膜回路チップ16と外部との電気的接続を担う電極パッドの数を削減し、チップ面積の縮小を図っている。これらにより、単位面積当たりに製造可能なチップ数が増加し、かつチップの実装回数が削減されるので、有機EL表示装置の製造コストを削減することが可能となる。

また、本実施形態では、電源線の共用化によって当該電源線を配置可能な面積を増加させることが可能となり、各電源線を広幅化することができる。これにより、電源線を介して電力供給を行う際の電圧降下による影響を低減することが可能となる。

<第4の実施形態>

図13は、上述した各実施形態のいずれかにかかる有機EL表示装置(電気光学装置)を含んで構成される電子機器の具体例を説明する図である。図13(A)は携帯電話への適用例であり、当該携帯電話530はアンテナ部531、音声出力部532、音声入力部533、操作部534、および本発明の電気光学装置100を備えている。このように本発明の電気光学装置は表示部として利用可能である。図13(B)はビデオカメラへの適用例であり、当該ビデオカメラ540は受像部541、操作部542、音声入力部543、および本発明の電気光学装置100を備えている。図13(C)はテレビジョンへの適用例であり、当該テレビジョン550は本発明の電気光学装置100を備えている。なお、パーソナルコンピュータ等に用いられるモニタ装置に対しても同様に本発明に係る電気光学装置を適用し得る。図13(D)はロールアップ式テレビジョンへの適用例であり、当該ロールアップ式テレビジョン560は本発明の電気光学装置100を備えている。また、電子機器はこれらに限定されず、表示機能を有する各種の電子機器に適用可能である。例えばこれらの他に、表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、電子手帳、電光掲示盤、宣伝公告用ディスプレイなども含まれる。

図13は、上述した各実施形態のいずれかにかかる有機EL表示装置(電気光学装置)を含んで構成される電子機器の具体例を説明する図である。図13(A)は携帯電話への適用例であり、当該携帯電話530はアンテナ部531、音声出力部532、音声入力部533、操作部534、および本発明の電気光学装置100を備えている。このように本発明の電気光学装置は表示部として利用可能である。図13(B)はビデオカメラへの適用例であり、当該ビデオカメラ540は受像部541、操作部542、音声入力部543、および本発明の電気光学装置100を備えている。図13(C)はテレビジョンへの適用例であり、当該テレビジョン550は本発明の電気光学装置100を備えている。なお、パーソナルコンピュータ等に用いられるモニタ装置に対しても同様に本発明に係る電気光学装置を適用し得る。図13(D)はロールアップ式テレビジョンへの適用例であり、当該ロールアップ式テレビジョン560は本発明の電気光学装置100を備えている。また、電子機器はこれらに限定されず、表示機能を有する各種の電子機器に適用可能である。例えばこれらの他に、表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、電子手帳、電光掲示盤、宣伝公告用ディスプレイなども含まれる。

<変形実施例>

なお、本発明は上述した各実施形態の内容に限定されるものではなく、本発明の要旨の範囲内において種々の変形実施が可能である。

なお、本発明は上述した各実施形態の内容に限定されるものではなく、本発明の要旨の範囲内において種々の変形実施が可能である。

例えば、上述した実施形態では、電気光学装置の一例として有機EL表示装置を採り上げて説明していたが、本発明を適用可能な電気光学装置はこれに限定されるものではない。複数の色画素を含んでなる基本画素をマトリクス状に複数配列した表示領域を備え、当該表示領域が線順次走査方式で駆動される各種の表示装置(いわゆるアクティブマトリクス型表示装置)に対して本発明を適用することが可能である。

また、上述した実施形態では、配線基板と表示素子基板とを貼り合わせた構造の有機EL表示装置を例にして説明していたが、デバイス構造はこれに限定されるものではない。他にも、例えば、一の基板上に、配線を含む層と表示素子を含む層を積層したデバイス構造のもの等に対しても本発明を適用可能である。

1,2,3…色画素、 4…基本画素、 5…データ線駆動回路、 6…走査線駆動回路、 10…配線基板、 12…表示素子基板、 14…有機EL素子、 16…薄膜回路チップ、 20…基材、 23…接続端子、 41R,41G,41B…データ線、 51,52…走査線、 53R,53G,53B…電源線、 62R,62G,62B…配線基板側の電極パッド(接続端子)、 74R,74G,74B,78R,78G,78B…画素駆動回路、 80a,80b,80c,80d,80e,80f,80g,80h,80i,80j,80k,80m,80n,80p…薄膜回路チップ側の電極パッド(接続端子)

Claims (13)

- 複数の色画素を含んでなる基本画素をマトリクス状に複数配列した表示領域を備え、当該表示領域が線順次走査方式で駆動される電気光学装置であって、

複数の前記色画素を構成する複数の電気光学素子と、

複数の前記基本画素のうち、垂直走査方向に隣接配置される2つの基本画素ごとに1つ設けられ、当該2つの基本画素に含まれる各色画素に対応する電気光学素子のそれぞれを制御するための複数の駆動回路を含む回路チップと、

前記電気光学素子の駆動に用いる走査信号を前記回路チップに供給するための複数の走査線と、

前記電気光学素子の駆動に用いるデータ信号を前記回路チップに供給するための複数のデータ線と、

前記電気光学素子を発光させるための電力を前記回路チップに供給するための複数の電源線と、

前記回路チップと、前記走査線、前記データ線及び前記電源線との相互間に設けられて電気的接続を担う複数の接続端子と、

を含み、

前記回路チップと前記データ線との電気的接続を担う前記接続端子は、前記回路チップ内の各駆動回路のうちで前記隣接配置される2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられている、電気光学装置。 - 前記回路チップと前記電源線との電気的接続を担う前記接続端子は、前記回路チップ内の各駆動回路のうちで、隣接配置される前記2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられている、請求項1に記載の電気光学装置。

- 前記回路チップと前記走査線との電気的接続を担う前記接続端子は、前記回路チップ内の各駆動回路のうちで前記基本画素のそれぞれに対応する3つの駆動回路ごとに共用されて設けられている、請求項1に記載の電気光学装置。

- 前記回路チップは、隣接配置される前記2つの基本画素の境界付近に配置される、請求項1に記載の電気光学装置。

- 前記回路チップ内の各駆動回路は、前記電気光学素子に流れる電流を制御する第1のトランジスタと、当該第1のトランジスタを前記データ信号に応じて動作させる第2のトランジスタと、を含んで構成される、請求項1に記載の電気光学装置。

- 前記電気光学素子が有機エレクトロルミネセンス素子である、請求項1に記載の電気光学装置。

- 複数の色画素を含んでなる基本画素をマトリクス状に複数配列した表示領域を備え、当該表示領域が線順次走査方式で駆動される電気光学装置であって、

複数の前記色画素を構成する複数の電気光学素子と、

複数の前記基本画素のうち、走査タイミングが同じであり、かつ相互に隣接配置される2つの基本画素ごとに1つ設けられ、当該2つの基本画素に含まれる各色画素に対応する電気光学素子のそれぞれを制御するための複数の駆動回路を含む回路チップと、

前記電気光学素子の駆動に用いる走査信号を前記回路チップに供給するための複数の走査線と、

前記電気光学素子の駆動に用いるデータ信号を前記回路チップに供給するための複数のデータ線と、

前記電気光学素子を発光させるための電力を前記回路チップに供給するための複数の電源線と、

前記回路チップと、前記走査線、前記データ線及び前記電源線との相互間に設けられて電気的接続を担う複数の接続端子と、

を含み、

前記回路チップと前記走査線との電気的接続を担う前記接続端子は、前記回路チップ内の各駆動回路に共用されて設けられている、電気光学装置。 - 前記回路チップと前記電源線との電気的接続を担う前記接続端子は、前記回路チップ内の各駆動回路のうちで前記隣接配置される2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられている、請求項7に記載の電気光学装置。

- 前記回路チップは、隣接配置される前記2つの基本画素の境界付近に配置される、請求項7に記載の電気光学装置。

- 複数の色画素を含んでなる基本画素をマトリクス状に複数配列した表示領域を備え、当該表示領域が線順次走査方式で駆動される電気光学装置であって、

複数の前記色画素を構成する複数の電気光学素子と、

複数の前記基本画素のうち、走査タイミングが同じであり隣接配置される2つの基本画素と、当該2つの基本画素のそれぞれと垂直走査方向に隣接配置される2つの基本画素とを合わせた4つの基本画素ごとに1つ設けられ、当該4つの基本画素に含まれる各色画素に対応する電気光学素子のそれぞれを制御するための複数の駆動回路を含む回路チップと、

前記電気光学素子の駆動に用いる走査信号を前記回路チップに供給するための複数の走査線と、

前記電気光学素子の駆動に用いるデータ信号を前記回路チップに供給するための複数のデータ線と、

前記電気光学素子を発光させるための電力を前記回路チップに供給するための複数の電源線と、

前記回路チップと、前記走査線、前記データ線及び前記電源線との相互間に設けられて電気的接続を担う複数の接続端子と、

を含み、

前記回路チップと前記走査線との電気的接続を担う前記接続端子は、前記回路チップ内の各駆動回路のうちで、前記走査タイミングが同じであり隣接配置される2つの基本画素内の各駆動回路に共用されて設けられ、

前記回路チップと前記データ線との電気的接続を担う前記接続端子は、前記回路チップ内の各駆動回路のうちで前記垂直走査方向に隣接配置される2つの基本画素内の同色の色画素のそれぞれに対応する2つの駆動回路ごとに共用されて設けられている、電気光学装置。 - 前記回路チップと前記電源線との電気的接続を担う前記接続端子は、前記回路チップ内の各駆動回路のうちで前記基本画素内の同色の色画素のそれぞれに対応する4つの駆動回路ごとに共用されて設けられている、請求項10に記載の電気光学装置。

- 前記回路チップは、隣接配置される前記4つの基本画素の相互の境界付近に配置される、請求項10に記載の電気光学装置。

- 請求項1乃至12のいずれかに記載の電気光学装置を用いて構成される電子機器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109084A JP2005292566A (ja) | 2004-04-01 | 2004-04-01 | 電気光学装置及び電子機器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109084A JP2005292566A (ja) | 2004-04-01 | 2004-04-01 | 電気光学装置及び電子機器 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005292566A true JP2005292566A (ja) | 2005-10-20 |

Family

ID=35325536

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004109084A Pending JP2005292566A (ja) | 2004-04-01 | 2004-04-01 | 電気光学装置及び電子機器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005292566A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013502620A (ja) * | 2009-08-24 | 2013-01-24 | グローバル・オーエルイーディー・テクノロジー・リミテッド・ライアビリティ・カンパニー | チップレットを用いた電子デバイスの制御 |

| CN113689796A (zh) * | 2020-05-13 | 2021-11-23 | 京东方科技集团股份有限公司 | 阵列基板、其检测方法及拼接显示面板 |

| CN114566519A (zh) * | 2020-11-27 | 2022-05-31 | 京东方科技集团股份有限公司 | 显示基板以及显示装置 |

| WO2023184167A1 (zh) * | 2022-03-29 | 2023-10-05 | 京东方科技集团股份有限公司 | 显示基板和显示装置 |

-

2004

- 2004-04-01 JP JP2004109084A patent/JP2005292566A/ja active Pending

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013502620A (ja) * | 2009-08-24 | 2013-01-24 | グローバル・オーエルイーディー・テクノロジー・リミテッド・ライアビリティ・カンパニー | チップレットを用いた電子デバイスの制御 |

| CN113689796A (zh) * | 2020-05-13 | 2021-11-23 | 京东方科技集团股份有限公司 | 阵列基板、其检测方法及拼接显示面板 |

| CN114566519A (zh) * | 2020-11-27 | 2022-05-31 | 京东方科技集团股份有限公司 | 显示基板以及显示装置 |

| WO2023184167A1 (zh) * | 2022-03-29 | 2023-10-05 | 京东方科技集团股份有限公司 | 显示基板和显示装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN108878444B (zh) | 显示面板及显示装置 | |

| CN110911443B (zh) | 平铺显示装置 | |

| EP3331019B1 (en) | Display device | |

| CN114784077B (zh) | 显示面板及显示装置 | |

| KR101383085B1 (ko) | 유기 발광 표시 장치 | |

| JP3977299B2 (ja) | 電気光学装置、マトリクス基板、及び電子機器 | |

| WO2021102810A1 (zh) | 显示基板、显示面板及拼接屏 | |

| US20250261529A1 (en) | Display substrate including first reference voltage line being electrically coupled to first reference voltage auxiliary line through via holes penetrating through insulation layer therebetween, and display device having the same | |

| WO2022007571A1 (zh) | 显示装置及其制作方法 | |

| KR20220127919A (ko) | 로컬 능동 매트릭스 아키텍처 | |

| JP7410152B2 (ja) | アレイ基板及び表示装置 | |

| CN115377169A (zh) | 显示基板和显示装置 | |

| CN114300522A (zh) | 显示面板及其修复方法和显示装置 | |

| US6573660B2 (en) | Driving emissive displays | |

| CN113724592B (zh) | 一种显示模组及显示装置 | |

| US20240096905A1 (en) | Display panel and tiled display screen | |

| CN113764461B (zh) | 显示面板和显示装置 | |

| JP2005292566A (ja) | 電気光学装置及び電子機器 | |

| US11316002B2 (en) | Unit pixel and organic light emitting display device including the same | |

| WO2023123237A1 (zh) | 像素组、阵列基板和显示面板 | |

| US20240304634A1 (en) | Light emitting display device | |

| US20240258329A1 (en) | Display apparatus | |

| JP2022551619A (ja) | 表示デバイスおよび表示ユニット | |

| WO2021024063A1 (ja) | 表示装置 | |

| CN114649394B (zh) | 显示面板及显示装置 |