JP2005174292A - データシフト操作 - Google Patents

データシフト操作 Download PDFInfo

- Publication number

- JP2005174292A JP2005174292A JP2004308629A JP2004308629A JP2005174292A JP 2005174292 A JP2005174292 A JP 2005174292A JP 2004308629 A JP2004308629 A JP 2004308629A JP 2004308629 A JP2004308629 A JP 2004308629A JP 2005174292 A JP2005174292 A JP 2005174292A

- Authority

- JP

- Japan

- Prior art keywords

- data

- register

- instruction

- data element

- source

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/80—Architectures of general purpose stored program computers comprising an array of processing units with common control, e.g. single instruction multiple data processors

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

- G06F9/30025—Format conversion instructions, e.g. Floating-Point to Integer, decimal conversion

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

- G06F9/30036—Instructions to perform operations on packed data, e.g. vector, tile or matrix operations

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

- G06F9/30036—Instructions to perform operations on packed data, e.g. vector, tile or matrix operations

- G06F9/30038—Instructions to perform operations on packed data, e.g. vector, tile or matrix operations using a mask

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30098—Register arrangements

- G06F9/30105—Register structure

- G06F9/30109—Register structure having multiple operands in a single register

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30098—Register arrangements

- G06F9/30105—Register structure

- G06F9/30112—Register structure comprising data of variable length

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30098—Register arrangements

- G06F9/30105—Register structure

- G06F9/30116—Shadow registers, e.g. coupled registers, not forming part of the register space

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30098—Register arrangements

- G06F9/3012—Organisation of register space, e.g. banked or distributed register file

- G06F9/30138—Extension of register space, e.g. register cache

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30145—Instruction analysis, e.g. decoding, instruction word fields

- G06F9/3016—Decoding the operand specifier, e.g. specifier format

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30145—Instruction analysis, e.g. decoding, instruction word fields

- G06F9/3016—Decoding the operand specifier, e.g. specifier format

- G06F9/30167—Decoding the operand specifier, e.g. specifier format of immediate specifier, e.g. constants

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Computer Hardware Design (AREA)

- Computing Systems (AREA)

- Executing Machine-Instructions (AREA)

- Advance Control (AREA)

- Image Processing (AREA)

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GB0328525A GB2411974C (en) | 2003-12-09 | 2003-12-09 | Data shift operations |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005174292A true JP2005174292A (ja) | 2005-06-30 |

| JP2005174292A5 JP2005174292A5 (enExample) | 2007-08-30 |

Family

ID=30129903

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004308629A Withdrawn JP2005174292A (ja) | 2003-12-09 | 2004-10-22 | データシフト操作 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20050125638A1 (enExample) |

| JP (1) | JP2005174292A (enExample) |

| GB (1) | GB2411974C (enExample) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007073010A (ja) * | 2005-09-09 | 2007-03-22 | Ricoh Co Ltd | Simd方式プロセッサ、当該simd方式プロセッサを利用する画像処理方法、及び画像処理装置 |

| JP2012190389A (ja) * | 2011-03-14 | 2012-10-04 | Ricoh Co Ltd | プロセッサ装置及びその演算方法 |

| CN104603766A (zh) * | 2012-09-28 | 2015-05-06 | 英特尔公司 | 经加速的通道间的向量归约指令 |

| KR20170097008A (ko) * | 2014-12-23 | 2017-08-25 | 인텔 코포레이션 | 벡터 요소 세트에 대해 축소 연산을 수행하기 위한 방법 및 장치 |

| KR20190119075A (ko) * | 2017-02-23 | 2019-10-21 | 에이알엠 리미티드 | 데이터 처리장치에서의 요소 바이 벡터 연산 |

| JP2019185486A (ja) * | 2018-04-12 | 2019-10-24 | 富士通株式会社 | コード変換装置、コード変換方法、及びコード変換プログラム |

| US11436010B2 (en) | 2017-06-30 | 2022-09-06 | Intel Corporation | Method and apparatus for vectorizing indirect update loops |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20120254589A1 (en) * | 2011-04-01 | 2012-10-04 | Jesus Corbal San Adrian | System, apparatus, and method for aligning registers |

| US9529591B2 (en) | 2011-12-30 | 2016-12-27 | Intel Corporation | SIMD variable shift and rotate using control manipulation |

| US9292298B2 (en) * | 2013-07-08 | 2016-03-22 | Arm Limited | Data processing apparatus having SIMD processing circuitry |

| US9552209B2 (en) * | 2013-12-27 | 2017-01-24 | Intel Corporation | Functional unit for instruction execution pipeline capable of shifting different chunks of a packed data operand by different amounts |

| US10204044B2 (en) * | 2016-05-18 | 2019-02-12 | Sap Se | Memory management process using data sheet |

| CN106227508A (zh) * | 2016-07-25 | 2016-12-14 | 中国科学院计算技术研究所 | 一种无回边数据流循环方法、系统、装置、芯片 |

| US10162633B2 (en) * | 2017-04-24 | 2018-12-25 | Arm Limited | Shift instruction |

| US10915319B2 (en) * | 2017-05-15 | 2021-02-09 | Google Llc | Two dimensional masked shift instruction |

| US10318298B2 (en) * | 2017-09-29 | 2019-06-11 | Intel Corporation | Apparatus and method for shifting quadwords and extracting packed words |

| CN114444707A (zh) * | 2020-10-30 | 2022-05-06 | 深圳前海微众银行股份有限公司 | 数据处理方法、装置、设备及存储介质 |

| US12105589B2 (en) * | 2022-02-23 | 2024-10-01 | Micron Technology, Inc. | Parity-based error management for a processing system |

Family Cites Families (61)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3116411A (en) * | 1959-06-15 | 1963-12-31 | Control Data Corp | Binary multiplication system utilizing a zero mode and a one mode |

| GB1053686A (enExample) * | 1964-07-22 | |||

| US4876660A (en) * | 1987-03-20 | 1989-10-24 | Bipolar Integrated Technology, Inc. | Fixed-point multiplier-accumulator architecture |

| US4916640A (en) * | 1987-06-03 | 1990-04-10 | Allen-Bradley Company, Inc. | Video image processing system |

| JPH0778735B2 (ja) * | 1988-12-05 | 1995-08-23 | 松下電器産業株式会社 | キャッシュ装置と命令読出し装置 |

| JPH05233281A (ja) * | 1992-02-21 | 1993-09-10 | Toshiba Corp | 電子計算機 |

| US5408670A (en) * | 1992-12-18 | 1995-04-18 | Xerox Corporation | Performing arithmetic in parallel on composite operands with packed multi-bit components |

| US5481743A (en) * | 1993-09-30 | 1996-01-02 | Apple Computer, Inc. | Minimal instruction set computer architecture and multiple instruction issue method |

| DE69428466T2 (de) * | 1993-11-23 | 2002-05-23 | Hewlett-Packard Co. (N.D.Ges.D.Staates Delaware), Palo Alto | Parallele Datenverarbeitung in einem Einzelprozessor |

| US5390135A (en) * | 1993-11-29 | 1995-02-14 | Hewlett-Packard | Parallel shift and add circuit and method |

| US5881302A (en) * | 1994-05-31 | 1999-03-09 | Nec Corporation | Vector processing unit with reconfigurable data buffer |

| US6009508A (en) * | 1994-06-21 | 1999-12-28 | Sgs-Thomson Microelectronics Limited | System and method for addressing plurality of data values with a single address in a multi-value store on FIFO basis |

| GB9412434D0 (en) * | 1994-06-21 | 1994-08-10 | Inmos Ltd | Computer instruction compression |

| GB9412487D0 (en) * | 1994-06-22 | 1994-08-10 | Inmos Ltd | A computer system for executing branch instructions |

| GB9413267D0 (en) * | 1994-07-01 | 1994-08-24 | T & N Technology Ltd | Sintered reaction-bonded silicon nitride components |

| ZA9510127B (en) * | 1994-12-01 | 1996-06-06 | Intel Corp | Novel processor having shift operations |

| US5761103A (en) * | 1995-03-08 | 1998-06-02 | Texas Instruments Incorporated | Left and right justification of single precision mantissa in a double precision rounding unit |

| GB9509987D0 (en) * | 1995-05-17 | 1995-07-12 | Sgs Thomson Microelectronics | Manipulation of data |

| GB9509983D0 (en) * | 1995-05-17 | 1995-07-12 | Sgs Thomson Microelectronics | Replication of data |

| GB9509989D0 (en) * | 1995-05-17 | 1995-07-12 | Sgs Thomson Microelectronics | Manipulation of data |

| GB9509988D0 (en) * | 1995-05-17 | 1995-07-12 | Sgs Thomson Microelectronics | Matrix transposition |

| GB9513515D0 (en) * | 1995-07-03 | 1995-09-06 | Sgs Thomson Microelectronics | Expansion of data |

| GB9514684D0 (en) * | 1995-07-18 | 1995-09-13 | Sgs Thomson Microelectronics | An arithmetic unit |

| GB9514695D0 (en) * | 1995-07-18 | 1995-09-13 | Sgs Thomson Microelectronics | Combining data values |

| JP3526976B2 (ja) * | 1995-08-03 | 2004-05-17 | 株式会社日立製作所 | プロセッサおよびデータ処理装置 |

| US6295599B1 (en) * | 1995-08-16 | 2001-09-25 | Microunity Systems Engineering | System and method for providing a wide operand architecture |

| US6643765B1 (en) * | 1995-08-16 | 2003-11-04 | Microunity Systems Engineering, Inc. | Programmable processor with group floating point operations |

| US5907865A (en) * | 1995-08-28 | 1999-05-25 | Motorola, Inc. | Method and data processing system for dynamically accessing both big-endian and little-endian storage schemes |

| EP0789870B1 (en) * | 1995-09-01 | 2003-01-15 | Philips Electronics North America Corporation | Method and apparatus for custom operations of a processor |

| US6088783A (en) * | 1996-02-16 | 2000-07-11 | Morton; Steven G | DPS having a plurality of like processors controlled in parallel by an instruction word, and a control processor also controlled by the instruction word |

| US5937178A (en) * | 1996-02-13 | 1999-08-10 | National Semiconductor Corporation | Register file for registers with multiple addressable sizes using read-modify-write for register file update |

| US5808875A (en) * | 1996-03-29 | 1998-09-15 | Intel Corporation | Integrated circuit solder-rack interconnect module |

| US5838984A (en) * | 1996-08-19 | 1998-11-17 | Samsung Electronics Co., Ltd. | Single-instruction-multiple-data processing using multiple banks of vector registers |

| US6058465A (en) * | 1996-08-19 | 2000-05-02 | Nguyen; Le Trong | Single-instruction-multiple-data processing in a multimedia signal processor |

| US5996066A (en) * | 1996-10-10 | 1999-11-30 | Sun Microsystems, Inc. | Partitioned multiply and add/subtract instruction for CPU with integrated graphics functions |

| US6173366B1 (en) * | 1996-12-02 | 2001-01-09 | Compaq Computer Corp. | Load and store instructions which perform unpacking and packing of data bits in separate vector and integer cache storage |

| US5893145A (en) * | 1996-12-02 | 1999-04-06 | Compaq Computer Corp. | System and method for routing operands within partitions of a source register to partitions within a destination register |

| US5909572A (en) * | 1996-12-02 | 1999-06-01 | Compaq Computer Corp. | System and method for conditionally moving an operand from a source register to a destination register |

| US6112291A (en) * | 1997-01-24 | 2000-08-29 | Texas Instruments Incorporated | Method and apparatus for performing a shift instruction with saturate by examination of an operand prior to shifting |

| US5898896A (en) * | 1997-04-10 | 1999-04-27 | International Business Machines Corporation | Method and apparatus for data ordering of I/O transfers in Bi-modal Endian PowerPC systems |

| US5973705A (en) * | 1997-04-24 | 1999-10-26 | International Business Machines Corporation | Geometry pipeline implemented on a SIMD machine |

| US6047304A (en) * | 1997-07-29 | 2000-04-04 | Nortel Networks Corporation | Method and apparatus for performing lane arithmetic to perform network processing |

| US6209017B1 (en) * | 1997-08-30 | 2001-03-27 | Lg Electronics Inc. | High speed digital signal processor |

| GB2329810B (en) * | 1997-09-29 | 2002-02-27 | Science Res Foundation | Generation and use of compressed image data |

| US5864703A (en) * | 1997-10-09 | 1999-01-26 | Mips Technologies, Inc. | Method for providing extended precision in SIMD vector arithmetic operations |

| US5933650A (en) * | 1997-10-09 | 1999-08-03 | Mips Technologies, Inc. | Alignment and ordering of vector elements for single instruction multiple data processing |

| US6038583A (en) * | 1997-10-23 | 2000-03-14 | Advanced Micro Devices, Inc. | Method and apparatus for simultaneously multiplying two or more independent pairs of operands and calculating a rounded products |

| US6223198B1 (en) * | 1998-08-14 | 2001-04-24 | Advanced Micro Devices, Inc. | Method and apparatus for multi-function arithmetic |

| US6144980A (en) * | 1998-01-28 | 2000-11-07 | Advanced Micro Devices, Inc. | Method and apparatus for performing multiple types of multiplication including signed and unsigned multiplication |

| US6269384B1 (en) * | 1998-03-27 | 2001-07-31 | Advanced Micro Devices, Inc. | Method and apparatus for rounding and normalizing results within a multiplier |

| US6085213A (en) * | 1997-10-23 | 2000-07-04 | Advanced Micro Devices, Inc. | Method and apparatus for simultaneously multiplying two or more independent pairs of operands and summing the products |

| US6223277B1 (en) * | 1997-11-21 | 2001-04-24 | Texas Instruments Incorporated | Data processing circuit with packed data structure capability |

| US6223320B1 (en) * | 1998-02-10 | 2001-04-24 | International Business Machines Corporation | Efficient CRC generation utilizing parallel table lookup operations |

| US6334176B1 (en) * | 1998-04-17 | 2001-12-25 | Motorola, Inc. | Method and apparatus for generating an alignment control vector |

| US6292888B1 (en) * | 1999-01-27 | 2001-09-18 | Clearwater Networks, Inc. | Register transfer unit for electronic processor |

| GB2352065B (en) * | 1999-07-14 | 2004-03-03 | Element 14 Ltd | A memory access system |

| US6408345B1 (en) * | 1999-07-15 | 2002-06-18 | Texas Instruments Incorporated | Superscalar memory transfer controller in multilevel memory organization |

| US6546480B1 (en) * | 1999-10-01 | 2003-04-08 | Hitachi, Ltd. | Instructions for arithmetic operations on vectored data |

| US6748521B1 (en) * | 2000-02-18 | 2004-06-08 | Texas Instruments Incorporated | Microprocessor with instruction for saturating and packing data |

| US7039906B1 (en) * | 2000-09-29 | 2006-05-02 | International Business Machines Corporation | Compiler for enabling multiple signed independent data elements per register |

| US6721866B2 (en) * | 2001-12-21 | 2004-04-13 | Intel Corporation | Unaligned memory operands |

-

2003

- 2003-12-09 GB GB0328525A patent/GB2411974C/en not_active Expired - Lifetime

-

2004

- 2004-07-13 US US10/889,365 patent/US20050125638A1/en not_active Abandoned

- 2004-10-22 JP JP2004308629A patent/JP2005174292A/ja not_active Withdrawn

Cited By (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007073010A (ja) * | 2005-09-09 | 2007-03-22 | Ricoh Co Ltd | Simd方式プロセッサ、当該simd方式プロセッサを利用する画像処理方法、及び画像処理装置 |

| JP2012190389A (ja) * | 2011-03-14 | 2012-10-04 | Ricoh Co Ltd | プロセッサ装置及びその演算方法 |

| CN104603766A (zh) * | 2012-09-28 | 2015-05-06 | 英特尔公司 | 经加速的通道间的向量归约指令 |

| JP2015532755A (ja) * | 2012-09-28 | 2015-11-12 | インテル・コーポレーション | インターレーンベクトルリダクション命令の高速化 |

| JP2017076395A (ja) * | 2012-09-28 | 2017-04-20 | インテル・コーポレーション | 装置および方法 |

| CN104603766B (zh) * | 2012-09-28 | 2017-06-30 | 英特尔公司 | 经加速的通道间的向量归约指令 |

| US10209989B2 (en) | 2012-09-28 | 2019-02-19 | Intel Corporation | Accelerated interlane vector reduction instructions |

| KR102449616B1 (ko) * | 2014-12-23 | 2022-10-04 | 인텔 코포레이션 | 벡터 요소 세트에 대해 축소 연산을 수행하기 위한 방법 및 장치 |

| KR20170097008A (ko) * | 2014-12-23 | 2017-08-25 | 인텔 코포레이션 | 벡터 요소 세트에 대해 축소 연산을 수행하기 위한 방법 및 장치 |

| KR20190119075A (ko) * | 2017-02-23 | 2019-10-21 | 에이알엠 리미티드 | 데이터 처리장치에서의 요소 바이 벡터 연산 |

| JP2020508514A (ja) * | 2017-02-23 | 2020-03-19 | エイアールエム リミテッド | データ処理装置におけるベクトルによる要素演算 |

| US11327752B2 (en) * | 2017-02-23 | 2022-05-10 | Arm Limited | Element by vector operations in a data processing apparatus |

| JP7148526B2 (ja) | 2017-02-23 | 2022-10-05 | アーム・リミテッド | データ処理装置におけるベクトルによる要素演算 |

| TWI780116B (zh) * | 2017-02-23 | 2022-10-11 | 英商Arm股份有限公司 | 用於資料處理設備、方法、電腦可讀式儲存媒體及虛擬機器的向量逐元素操作 |

| KR102584031B1 (ko) * | 2017-02-23 | 2023-10-04 | 에이알엠 리미티드 | 데이터 처리장치에서의 요소 바이 벡터 연산 |

| US11436010B2 (en) | 2017-06-30 | 2022-09-06 | Intel Corporation | Method and apparatus for vectorizing indirect update loops |

| JP7035751B2 (ja) | 2018-04-12 | 2022-03-15 | 富士通株式会社 | コード変換装置、コード変換方法、及びコード変換プログラム |

| JP2019185486A (ja) * | 2018-04-12 | 2019-10-24 | 富士通株式会社 | コード変換装置、コード変換方法、及びコード変換プログラム |

Also Published As

| Publication number | Publication date |

|---|---|

| GB2411974C (en) | 2009-09-23 |

| GB2411974B (en) | 2006-06-21 |

| US20050125638A1 (en) | 2005-06-09 |

| GB2411974A (en) | 2005-09-14 |

| GB0328525D0 (en) | 2004-01-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

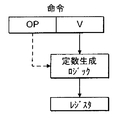

| JP5393643B2 (ja) | Simd処理における定数の生成 | |

| JP4727589B2 (ja) | データ処理レジスタに別名を付ける装置および方法 | |

| JP5366917B2 (ja) | データ要素に対するデータ処理操作を並列に実行するためのデータ処理装置及び方法 | |

| JP4699002B2 (ja) | Simdデータ処理における算術演算の実行のためのデータ処理装置及び方法 | |

| JP4588413B2 (ja) | Simd処理における多重化操作 | |

| JP4689621B2 (ja) | レジスタとメモリとの間でデータを移動するためのデータ処理装置および方法 | |

| JP4689622B2 (ja) | レジスタとメモリとの間でデータを移動するためのデータ処理装置および方法 | |

| JP4584673B2 (ja) | データ処理システム内部のテーブル検索操作 | |

| JP4660155B2 (ja) | レジスタとメモリとの間でデータを移動するためのデータ処理装置及び方法 | |

| JP2005174296A (ja) | Simdデータ処理システムにおけるエンディアンの補償 | |

| JP2005174298A (ja) | “ベクトル×スカラ”演算 | |

| JP2005174300A (ja) | 異なるレジスタデータ記憶装置のレジスタ間のデータ移動 | |

| JP2005174292A (ja) | データシフト操作 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061212 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061212 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070718 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20080710 |