JP2005084559A - Power-on reset circuit - Google Patents

Power-on reset circuit Download PDFInfo

- Publication number

- JP2005084559A JP2005084559A JP2003319117A JP2003319117A JP2005084559A JP 2005084559 A JP2005084559 A JP 2005084559A JP 2003319117 A JP2003319117 A JP 2003319117A JP 2003319117 A JP2003319117 A JP 2003319117A JP 2005084559 A JP2005084559 A JP 2005084559A

- Authority

- JP

- Japan

- Prior art keywords

- signal

- gate driver

- liquid crystal

- power

- crystal panel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Electronic Switches (AREA)

- Liquid Crystal (AREA)

Abstract

Description

本発明は、液晶パネルを駆動する駆動回路に使用されるゲートドライバの全出力端子を、電源が投入されてから操作が開始されるまでの間オフ状態にするパワーオンリセット回路に関する。 The present invention relates to a power-on reset circuit in which all output terminals of a gate driver used in a drive circuit for driving a liquid crystal panel are turned off until the operation is started after power is turned on.

図3に一般的な液晶パネルの駆動回路の構成図を示す。図3に示すように、液晶パネル31の表示データ線32はソースドライバ33を介して液晶駆動コントローラ34に接続されており、液晶パネル31の走査線35はゲートドライバ36を介して液晶駆動コントローラ34に接続されている。

FIG. 3 shows a configuration diagram of a general liquid crystal panel drive circuit. As shown in FIG. 3, the

液晶駆動コントローラ34は、液晶パネル31の表示データ線32にソースドライバ33を介して表示データを供給し、液晶パネル31の走査線35にゲートドライバ36を介して操作信号を供給する(例えば、特許文献1参照。)。

The liquid

図4にゲートドライバ36の内部回路の概略図を示す。図4に示すように、液晶パネルの駆動回路に使用されるゲートドライバは、クロック信号、操作開始信号、電源VDDなどが入力されるシフトレジスタ41と、シフトレジスタ41の出力を受けて走査線に操作信号を出力するレベルシフタ42とからなる。

FIG. 4 shows a schematic diagram of the internal circuit of the

以上のように構成された一般的な液晶パネルの駆動回路には以下の問題が存在する。すなわち、電源投入時にはクロック信号などの電圧レベルが不定であるため、ゲートドライバ内部のシフトレジスタの内部信号が不定な電圧レベルとなり、シフトレジスタから不定な電圧レベルの信号が出力され、レベルシフタの出力信号の電圧レベルを決定する電圧レベルが不定な電圧レベルとなり、その結果、電源投入時におけるゲートドライバの出力端子が“オフ状態”とならず、ゲートドライバから不定な電圧レベルの信号が出力され、液晶パネルに画面のちらつきや異常表示が発生するという問題があった。 The general liquid crystal panel drive circuit configured as described above has the following problems. That is, when the power is turned on, the voltage level of the clock signal and the like is indeterminate, so the internal signal of the shift register inside the gate driver becomes an indeterminate voltage level, an indefinite voltage level signal is output from the shift register, and the output signal of the level shifter The voltage level that determines the voltage level of the gate driver becomes an indeterminate voltage level. As a result, the output terminal of the gate driver at the time of turning on the power is not turned off, and a signal with an indefinite voltage level is output from the gate driver. There was a problem that screen flickering or abnormal display occurred on the panel.

なお、“オフ状態”は、ゲートドライバの全出力端子の電圧が液晶パネルの表示をOFFする電圧レベルにあることを意味する。

本発明は、上記問題点に鑑み、電源投入時にリセット信号を供給してゲートドライバの全出力端子をオフ状態にし、操作開始信号の入力時に上記リセット信号を解除してゲートドライバの全出力端子を通常動作状態に戻すことにより、電源投入時における液晶パネルの画面のちらつきや異常表示を回避することができるパワーオンリセット回路を提供することを目的とする。 In view of the above problems, the present invention supplies a reset signal when power is turned on to turn off all the output terminals of the gate driver, cancels the reset signal when an operation start signal is input, and sets all the output terminals of the gate driver. An object of the present invention is to provide a power-on reset circuit that can avoid flickering of the screen of the liquid crystal panel and abnormal display when the power is turned on by returning to the normal operation state.

本発明の請求項1記載のパワーオンリセット回路は、液晶パネルの表示データ線にソースドライバを介して表示データを供給し、液晶パネルの走査線にゲートドライバを介して操作信号を供給する液晶駆動コントローラを有する液晶パネルの駆動回路において、前記液晶パネルの電源投入時に、電源の立ち上がりに同期して前記ゲートドライバにリセット信号を供給し前記ゲートドライバの全出力端子をオフ状態にし、前記ゲートドライバに入力される操作開始信号の立ち上がりに同期して前記リセット信号を解除し前記ゲートドライバの全出力端子を通常動作状態に戻すものである。 The power-on reset circuit according to claim 1 of the present invention supplies liquid crystal display data to a display data line of a liquid crystal panel via a source driver and supplies an operation signal to a scan line of the liquid crystal panel via a gate driver. In the driving circuit of the liquid crystal panel having a controller, when the liquid crystal panel is turned on, a reset signal is supplied to the gate driver in synchronization with the rising of the power to turn off all output terminals of the gate driver, and the gate driver The reset signal is canceled in synchronization with the rising of the input operation start signal, and all the output terminals of the gate driver are returned to the normal operation state.

本発明によれば、電源投入時における液晶パネルの画面のちらつきや異常表示を防ぐことができる。 According to the present invention, it is possible to prevent flickering or abnormal display of the screen of the liquid crystal panel when the power is turned on.

以下、本発明の実施の形態について、図面を参照しながら具体的に説明する。

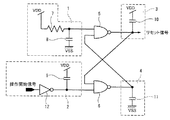

図1に本実施の形態におけるパワーオンリセット回路の構成図を示す。図1において、1〜4は電圧レベル設定回路であり、5、6はNAND回路である。また、7は抵抗、8〜11はコンデンサ、12はインバータである。

Embodiments of the present invention will be specifically described below with reference to the drawings.

FIG. 1 shows a configuration diagram of a power-on reset circuit in the present embodiment. In FIG. 1, 1 to 4 are voltage level setting circuits, and 5 and 6 are NAND circuits. 7 is a resistor, 8 to 11 are capacitors, and 12 is an inverter.

なお、NAND回路5、6およびインバータ12には電源VDDと基準電位VSSが接続されており、ハイレベルの信号として電位がVDDレベルの信号を出力し、ローレベルの信号として電位がVSSレベルの信号を出力する。

Note that the power supply VDD and the reference potential VSS are connected to the

また、該パワーオンリセット回路において使用する電源VDDと操作開始信号は、図4に示す電源VDDと操作開始信号である。

図1に示すように、第1の電圧レベル設定回路1は電源VDDに接続される抵抗7と基準電位VSSに接続されるコンデンサ8からなり、抵抗7とコンデンサ8との間から取り出した信号をNAND回路5の一方の入力へ出力する。

The power supply VDD and operation start signal used in the power-on reset circuit are the power supply VDD and operation start signal shown in FIG.

As shown in FIG. 1, the first voltage level setting circuit 1 includes a resistor 7 connected to a power supply VDD and a capacitor 8 connected to a reference potential VSS, and a signal extracted from between the resistor 7 and the capacitor 8 is obtained. Output to one input of the

また、第2の電圧レベル設定回路2は電源VDDに接続されるコンデンサ9と操作開始信号を入力とするインバータ12からなり、コンデンサ9とインバータ12の出力との間から取り出した信号をNAND回路6の一方の入力へ出力する。

The second voltage

また、NAND回路5の出力信号は、電源VDDに接続されるコンデンサ10からなる第3の電圧レベル設定回路3に接続され、NAND回路6の他方の入力となる。

また、NAND回路6の出力信号は、基準電位VSSに接続されるコンデンサ11からなる第4の電圧レベル設定回路4に接続され、NAND回路5の他方の入力となる。

The output signal of the

The output signal of the

次に、該パワーオンリセット回路の動作について説明する。

電源投入前、電源VDDは基準電位VSSレベルと同電位であり、また操作開始信号は基準電位VSSレベルに固定された状態にある。

Next, the operation of the power-on reset circuit will be described.

Before power-on, the power supply VDD is at the same potential as the reference potential VSS level, and the operation start signal is fixed at the reference potential VSS level.

電源VDDの電位がVSSレベルから徐々に立ち上がっていくと、第1の電圧レベル設定回路1からNAND回路5へ出力される信号の電位もこの立ち上がりに同期してVSSレベルから立ち上がっていく。

When the potential of the power supply VDD gradually rises from the VSS level, the potential of the signal output from the first voltage level setting circuit 1 to the

また、インバータ12へは電位がVSSレベルの信号が入力されるので、第2の電圧レベル設定回路2からNAND回路6へ出力される信号の電位も電源VDDの立ち上がりに同期してVSSレベルから立ち上がっていく。

Further, since a signal having a potential of VSS level is input to the

また、第4の電圧レベル設定回路4からはコンデンサ11より電位がVSSレベルの信号が出力されるので、NAND回路5の出力信号の電位も電源VDDの立ち上がりに同期してVSSレベルから立ち上がっていく。

Further, since the fourth voltage level setting circuit 4 outputs a signal having a potential of VSS level from the

従って、第3の電圧レベル設定回路3の出力信号は、電源VDDの立ち上がりに同期して電位がVSSレベルから立ち上がっていく信号となり、NAND回路6の出力信号は電位が概ねVSSレベルに固定された信号となる。

Therefore, the output signal of the third voltage

この結果、NAND回路5の出力とコンデンサ10との間から取り出されるリセット信号の電位は、電源投入時に電源VDDの立ち上がりに同期してVSSレベルから立ち上がっていき、電源VDDが完全に立ち上がったときVDDレベルとなる(図2のリセット信号アクティブ状態21を参照。)。

As a result, the potential of the reset signal taken out between the output of the

次に、リセット解除時の動作について説明する。

電位が基準電位VSSレベルに固定されていた操作開始信号が徐々に立ち上がっていくと、インバータ12の出力信号の電位はそれに同期して徐々に立ち下がっていく。そのため、NAND回路6の出力信号の電位は、操作開始信号に同期して電位VDDレベルまで立ち上がっていき、NAND回路5の出力信号の電位は、電位VSSレベルまで立ち下がっていく。

Next, the operation at the time of reset release will be described.

When the operation start signal whose potential has been fixed at the reference potential VSS level gradually rises, the potential of the output signal of the

その結果、リセット信号の電位は、操作開始信号の入力時に操作開始信号の立ち上がりに同期してVDDレベルからVSSレベルまで立ち下がる(図2のリセット信号解除状態22を参照。)。

As a result, the potential of the reset signal falls from the VDD level to the VSS level in synchronization with the rise of the operation start signal when the operation start signal is input (see the reset

以上のように構成されたパワーオンリセット回路が発生するリセット信号を図4に示すゲートドライバ内部のシフトレジスタへ入力することにより、液晶パネルの電源投入時にゲートドライバの全出力端子をオフ状態にすることができ、操作開始信号の入力時にリセット信号を解除しゲートドライバの全出力端子を通常動作状態に戻すことができる。 By inputting the reset signal generated by the power-on reset circuit configured as described above to the shift register inside the gate driver shown in FIG. 4, all the output terminals of the gate driver are turned off when the liquid crystal panel is turned on. The reset signal can be canceled when the operation start signal is input, and all the output terminals of the gate driver can be returned to the normal operation state.

本発明にかかるパワーオンリセット回路は、電源の投入をトリガとしてリセット信号を出力するので、電源投入時の内部信号の状態が不定であったり、電源投入時に不定な信号を出力したりする回路において有用である。 Since the power-on reset circuit according to the present invention outputs a reset signal triggered by power-on, the internal signal state at power-on is indefinite or an indeterminate signal is output at power-on. Useful.

1 第1の電圧レベル設定回路

2 第2の電圧レベル設定回路

3 第3の電圧レベル設定回路

4 第4の電圧レベル設定回路

5、6 NAND回路

7 抵抗

8、9、10、11 コンデンサ

12 インバータ

21 リセット信号アクティブ状態

22 リセット信号解除状態

31 液晶パネル

32 表示データ線

33 ソースドライバ

34 液晶駆動コントローラ

35 走査線

36 ゲートドライバ

41 シフトレジスタ

42 レベルシフタ

DESCRIPTION OF SYMBOLS 1 1st voltage

Claims (1)

前記液晶パネルの電源投入時に、電源の立ち上がりに同期して前記ゲートドライバにリセット信号を供給し前記ゲートドライバの全出力端子をオフ状態にし、前記ゲートドライバに入力される操作開始信号の立ち上がりに同期して前記リセット信号を解除し前記ゲートドライバの全出力端子を通常動作状態に戻すパワーオンリセット回路。

In a liquid crystal panel drive circuit having a liquid crystal drive controller that supplies display data to a display data line of a liquid crystal panel via a source driver and supplies an operation signal to a scan line of the liquid crystal panel via a gate driver.

When the power of the liquid crystal panel is turned on, a reset signal is supplied to the gate driver in synchronization with the rise of the power to turn off all the output terminals of the gate driver, and in synchronization with the rise of the operation start signal input to the gate driver A power-on reset circuit that releases the reset signal and returns all output terminals of the gate driver to a normal operation state.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003319117A JP2005084559A (en) | 2003-09-11 | 2003-09-11 | Power-on reset circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003319117A JP2005084559A (en) | 2003-09-11 | 2003-09-11 | Power-on reset circuit |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005084559A true JP2005084559A (en) | 2005-03-31 |

| JP2005084559A5 JP2005084559A5 (en) | 2006-09-14 |

Family

ID=34418154

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003319117A Pending JP2005084559A (en) | 2003-09-11 | 2003-09-11 | Power-on reset circuit |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005084559A (en) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010181656A (en) * | 2009-02-06 | 2010-08-19 | Mitsubishi Electric Corp | Initial reset signal generation circuit |

| US8269757B2 (en) | 2007-03-20 | 2012-09-18 | Samsung Electronics Co., Ltd. | LCD driving method using self-masking, and masking circuit and asymmetric latches thereof |

| US8319769B2 (en) | 2008-06-27 | 2012-11-27 | Samsung Electronics Co., Ltd. | LCD panel driver with self masking function using power on reset signal and driving method thereof |

| JP2014160917A (en) * | 2013-02-19 | 2014-09-04 | Nec Engineering Ltd | Control circuit, circuit system and control method |

| CN108023580A (en) * | 2016-10-28 | 2018-05-11 | 拉碧斯半导体株式会社 | The generation method of semiconductor device and power-on reset signal |

| WO2023273444A1 (en) * | 2021-06-30 | 2023-01-05 | 京东方科技集团股份有限公司 | Apparatus and method for driving display panel |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63304228A (en) * | 1987-06-05 | 1988-12-12 | Hitachi Ltd | Liquid crystal display device |

| JPH01253798A (en) * | 1988-04-01 | 1989-10-11 | Matsushita Electric Ind Co Ltd | Driving circuit |

| JPH02215218A (en) * | 1989-02-16 | 1990-08-28 | Matsushita Electric Ind Co Ltd | Latch circuit |

| JPH04204993A (en) * | 1990-11-30 | 1992-07-27 | Sharp Corp | Driving circuit for display device |

| JPH05235705A (en) * | 1992-02-17 | 1993-09-10 | Fujitsu Ltd | Rs flip-flop circuit |

| JPH08304773A (en) * | 1995-05-08 | 1996-11-22 | Nippondenso Co Ltd | Matrix type liquid crystal display device |

| JPH0968953A (en) * | 1995-08-30 | 1997-03-11 | Canon Inc | Liquid crystal display device |

| JPH11143432A (en) * | 1997-11-07 | 1999-05-28 | Matsushita Electric Ind Co Ltd | Liquid crystal panel driving device |

| JP2000098339A (en) * | 1998-09-18 | 2000-04-07 | Matsushita Electric Ind Co Ltd | Liquid crystal display panel scanning line driver |

-

2003

- 2003-09-11 JP JP2003319117A patent/JP2005084559A/en active Pending

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63304228A (en) * | 1987-06-05 | 1988-12-12 | Hitachi Ltd | Liquid crystal display device |

| JPH01253798A (en) * | 1988-04-01 | 1989-10-11 | Matsushita Electric Ind Co Ltd | Driving circuit |

| JPH02215218A (en) * | 1989-02-16 | 1990-08-28 | Matsushita Electric Ind Co Ltd | Latch circuit |

| JPH04204993A (en) * | 1990-11-30 | 1992-07-27 | Sharp Corp | Driving circuit for display device |

| JPH05235705A (en) * | 1992-02-17 | 1993-09-10 | Fujitsu Ltd | Rs flip-flop circuit |

| JPH08304773A (en) * | 1995-05-08 | 1996-11-22 | Nippondenso Co Ltd | Matrix type liquid crystal display device |

| JPH0968953A (en) * | 1995-08-30 | 1997-03-11 | Canon Inc | Liquid crystal display device |

| JPH11143432A (en) * | 1997-11-07 | 1999-05-28 | Matsushita Electric Ind Co Ltd | Liquid crystal panel driving device |

| JP2000098339A (en) * | 1998-09-18 | 2000-04-07 | Matsushita Electric Ind Co Ltd | Liquid crystal display panel scanning line driver |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8269757B2 (en) | 2007-03-20 | 2012-09-18 | Samsung Electronics Co., Ltd. | LCD driving method using self-masking, and masking circuit and asymmetric latches thereof |

| US8319769B2 (en) | 2008-06-27 | 2012-11-27 | Samsung Electronics Co., Ltd. | LCD panel driver with self masking function using power on reset signal and driving method thereof |

| JP2010181656A (en) * | 2009-02-06 | 2010-08-19 | Mitsubishi Electric Corp | Initial reset signal generation circuit |

| JP2014160917A (en) * | 2013-02-19 | 2014-09-04 | Nec Engineering Ltd | Control circuit, circuit system and control method |

| CN108023580A (en) * | 2016-10-28 | 2018-05-11 | 拉碧斯半导体株式会社 | The generation method of semiconductor device and power-on reset signal |

| CN108023580B (en) * | 2016-10-28 | 2023-12-22 | 拉碧斯半导体株式会社 | Semiconductor device and method for generating power-on reset signal |

| WO2023273444A1 (en) * | 2021-06-30 | 2023-01-05 | 京东方科技集团股份有限公司 | Apparatus and method for driving display panel |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8923473B2 (en) | Signal processing circuit, driver circuit, and display device | |

| KR100910562B1 (en) | Device of driving display device | |

| US7825919B2 (en) | Source voltage removal detection circuit and display device including the same | |

| US7990204B2 (en) | Voltage generator that prevents latch-up | |

| US10474267B2 (en) | Touch display apparatus | |

| JP2007114732A (en) | Flat panel display and method of driving same | |

| JP3139496B2 (en) | Flat display device control method | |

| CN110264971B (en) | Anti-flash screen circuit and method, driving circuit and display device | |

| JP4984391B2 (en) | Display drive device, display device, and drive control method thereof | |

| JP2009157371A (en) | Driving device for liquid crystal display and its driving method | |

| JP2009025804A (en) | Display device and its driving method | |

| CN106033660B (en) | Semiconductor device and electronic device | |

| CN111161664B (en) | Display device and terminal | |

| US20110193839A1 (en) | Level shifter for use in lcd display applications | |

| CN114255685A (en) | Display device | |

| JP2005084559A (en) | Power-on reset circuit | |

| EP3040977A1 (en) | Display device | |

| US20230196955A1 (en) | Display Apparatus and Overcurrent Detection Method Thereof | |

| JP2008083436A (en) | Display device | |

| CN111161661A (en) | Display device and starting control circuit, method and system of display panel of display device | |

| JP2004354518A (en) | Driving voltage generating circuit and liquid crystal drive device using the same | |

| JP2012078492A (en) | Discharge circuit and liquid crystal display device | |

| KR20030010286A (en) | Gate high voltage generation apparatus | |

| JP3922176B2 (en) | Drive power supply circuit for display device | |

| KR100925291B1 (en) | Liquid crystal display device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060728 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060728 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20080430 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091110 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100112 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100202 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100921 |