JP2004248279A - 異なるタイプのインタフェースからの入力信号、又は異なるタイプのインタフェースへの出力信号を共通フォーマットの中央演算処理でプリプロセスするための方法及び装置 - Google Patents

異なるタイプのインタフェースからの入力信号、又は異なるタイプのインタフェースへの出力信号を共通フォーマットの中央演算処理でプリプロセスするための方法及び装置 Download PDFInfo

- Publication number

- JP2004248279A JP2004248279A JP2004032633A JP2004032633A JP2004248279A JP 2004248279 A JP2004248279 A JP 2004248279A JP 2004032633 A JP2004032633 A JP 2004032633A JP 2004032633 A JP2004032633 A JP 2004032633A JP 2004248279 A JP2004248279 A JP 2004248279A

- Authority

- JP

- Japan

- Prior art keywords

- system clock

- different

- format

- signal

- word

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000012545 processing Methods 0.000 title claims abstract description 49

- 238000007781 pre-processing Methods 0.000 title claims abstract description 11

- 238000000034 method Methods 0.000 title claims description 27

- 238000012432 intermediate storage Methods 0.000 claims abstract description 10

- 230000001360 synchronised effect Effects 0.000 claims description 41

- 238000012546 transfer Methods 0.000 claims description 21

- 230000008569 process Effects 0.000 claims description 9

- 238000005070 sampling Methods 0.000 abstract description 10

- 238000005516 engineering process Methods 0.000 abstract description 4

- 230000000630 rising effect Effects 0.000 description 12

- 102000008816 Trefoil Factor-2 Human genes 0.000 description 7

- 108010088411 Trefoil Factor-2 Proteins 0.000 description 7

- 238000006243 chemical reaction Methods 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- 230000006870 function Effects 0.000 description 6

- 102000008817 Trefoil Factor-1 Human genes 0.000 description 4

- 108010088412 Trefoil Factor-1 Proteins 0.000 description 4

- 238000013461 design Methods 0.000 description 3

- 238000001514 detection method Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000003780 insertion Methods 0.000 description 3

- 230000037431 insertion Effects 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 238000003860 storage Methods 0.000 description 3

- 230000001629 suppression Effects 0.000 description 3

- 230000002776 aggregation Effects 0.000 description 2

- 238000004220 aggregation Methods 0.000 description 2

- 230000002457 bidirectional effect Effects 0.000 description 2

- 230000001934 delay Effects 0.000 description 2

- 230000001419 dependent effect Effects 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000005457 optimization Methods 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 230000002441 reversible effect Effects 0.000 description 2

- KFZUDNZQQCWGKF-UHFFFAOYSA-M sodium;4-methylbenzenesulfinate Chemical compound [Na+].CC1=CC=C(S([O-])=O)C=C1 KFZUDNZQQCWGKF-UHFFFAOYSA-M 0.000 description 2

- 230000002123 temporal effect Effects 0.000 description 2

- 230000004913 activation Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000003139 buffering effect Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000001186 cumulative effect Effects 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 230000005236 sound signal Effects 0.000 description 1

- 238000004148 unit process Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04H—BROADCAST COMMUNICATION

- H04H60/00—Arrangements for broadcast applications with a direct linking to broadcast information or broadcast space-time; Broadcast-related systems

- H04H60/02—Arrangements for generating broadcast information; Arrangements for generating broadcast-related information with a direct linking to broadcast information or to broadcast space-time; Arrangements for simultaneous generation of broadcast information and broadcast-related information

- H04H60/04—Studio equipment; Interconnection of studios

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/16—Sound input; Sound output

- G06F3/162—Interface to dedicated audio devices, e.g. audio drivers, interface to CODECs

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Health & Medical Sciences (AREA)

- Multimedia (AREA)

- Audiology, Speech & Language Pathology (AREA)

- General Health & Medical Sciences (AREA)

- Human Computer Interaction (AREA)

- Signal Processing (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Communication Control (AREA)

Abstract

【解決手段】 音声処理技術では、異なるサンプルクロックの周波数、及び/又は異なるデータフレーム又は異なるデータワードのフォーマットに関連する異なるタイプのインタフェースが存在する。異なるタイプのインタフェースからの入力信号は、その後の共通フォーマットの中央演算処理のためにプリプロセスされる。このプリプロセスは、共通のシステムクロックに対する同期、異なるタイプのインタフェースに符合する異なるチャネルプロトコルに従うチャネルデコードに対する同期、及び該PCMビットストリームから、これよりサンプルワードが中央演算処理に供給される中間的な記憶装置に記憶されるサンプルワードを形成するように同期を利用する。

【選択図】 図1

Description

Pチャネルオーディオ信号(P=1,2,3,サポートされるストリーム当たりの最大チャネル数)を転送するオーディオストリームは、サンプルのシーケンシャルな形式で転送され、それぞれのサンプル(たとえば、ステレオ又は6チャネルサンプル)は、チャネル当たり1つのP個のデータワード(たとえば、32ビットのデータワード)から構成されることが想定されている。そのとき、考慮されるオーディオインタフェースにより転送される入力ワードのオーディオコンテンツのサイズは、最大24ビットを超えない、すなわち最大24ビットを超える必要がない。したがって、たとえば、通常のRISCプロセッサ又はある種のDSP、或いはダブルワード2×16ビットとしてのオーディオワードを記憶する16ビットDSP向けのような、選択されたプロセッサ/メモリシステムのため、ワード当たりより多くのビットが利用可能である場合、又はたとえば、24ビットDSPの場合において24ビットのうちの全てのビットが要求されない場合、追加のワードビットを使用して、他のサイド情報を転送することができる。

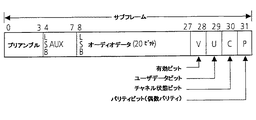

個々のサンプルワードに挿入される第一のタイプのかかる追加の情報は、サブコード情報とすることができ、SODIF(VUCP)、ADAT(C1..C4)、AC97(Tags)のような幾つかのインタフェースは、サブコード情報を定義している。SPDIFのケースでは、サブコードビットは、それぞれのサンプルと既に直接関連付けされて、転送される。図8aは、例示的な32ビットのワードフォーマットであり、24ビットをデータに使用し、ワード当たり最大5ビットをサブコードに使用し、3ビットを更なる情報に使用する。サブコードの総量及び内容は、インタフェースのタイプに依存する。本発明によれば、オリジナルのサブコードの総量は保持されるが、サブコードのビットに使用されるビット位置は固定及びユニークに選択することができる。唯一の例外は、有効ビット(V)であり、それぞれのサンプルの有効性を示している。この情報項目は、信号入力の場合に、ストリームユニット13により特別な方法で解釈及び処理することができる。

a)入力ワードは、Vビットを含んでおり、受信されたときに送出され、これにより、有効な情報のソフトウェア処理が可能となる。

b)又は、全てのサンプルワードが無効である場合に、Pチャネルサンプルは廃棄される(FIFO/メモリへの書き込みを禁止する)。

c)又は、無効なワードがミュートされる。

d)又は、サンプルワードは、CDプレーヤのような既存の装置で公知の形式で周囲の有効なワードから補間される。

(4つのサブコードビットを有するフォーマットについて)Pチャネルサンプルのうちの第一のワードにおける全てのADATサブコードビットを転送すること、

I2Sのケースにおける隣接する非PCMの位置(non−pcm location)にサブコードのビットを埋め、単一のI2Sインタフェースを介してDSPのような装置との結合されたオーディオとサブコードのデータ交換を可能にし、

及び/又は(データスロットに関係する)AClinkのタグビットで有効ビットを埋める。

オーディオ入力及び出力に関する1つの問題は、チャネルの置き換えに関する可能性である。これは、幾つかの典型的なマシンワード(典型的にはオーディオチャネル当たり1つ)が殆どのオーディオハードウェアの構成において単一のPチャネルサンプルを転送することが必要とされる事実による。したがって、プロセッサシステム(プロセッサ、DMAユニット、シリアルI/Oユニット、FIFO)は、個々のマシンワードに対応するのみであって、より大きなエンティティに対応するものではない。したがって、1つのデータワードがオーディオデータストリームから誤って挿入又は消去された場合、「マシン」ワードのシーケンスを読んでいる装置又はステージ(サブルーチン、スレッド、プロセッサ、オーディオインタフェースハードウェア等)は、どのワードがどのオーディオチャネルのうちの1つに関連されているかに関する情報のトラックを解放する可能性がある。

先に説明したストリームユニット13の拡張は、それぞれ独立な入力又は出力ストリーム当たりの1つの拡張、すなわちカウンタ92FCNT、レジスタ91FLEN、及びFビットメカニズムであり、DMAバッファ(図示せず)の真の最初のワードに関連するレジスタ95における正確なPTSタイムスタンプを取込むこと、及びDMAブロックにおける正確なサンプルのためのエラー情報を収集する累積的なエラーレジスタSERROR99を取込むことを容易にする。これは、比較結果93FCNT=FLEN−1及び当該取込みを可能にするためのsframe_enableを使用して行われる。

(FCNT=FLEN−1)AND sframe_enable

チャネルエラー記憶装置96CERRORは、SERRORレジスタ99によりサンプリングされたときクリアされ、その後、(たとえば、(FCNT=FLEN−1)AND sframe_enableで)再びサンプルされるまで、入力又は出力信号に関連する全てのエラー情報を収集する。したがって、SERRORは、まさに終了されたDMAブロック/終了されようとしているDMAブロックの全てのサンプルに関連するチャネルのエラー情報を正確に含んでいる。オーディオ入力の間、アクティブ状態にあるSERRORは、完全な入力ブロックがエラーについて更に検査されるべきであるか、又はミュート或いは無視されるべきかのいずれかであることを示し、後者の2つの機能は、ブロックベースで都合よくエラーを処理することができる。

図9と共に説明される更なる機能は、正確に時間設定されたストリームユニット13の起動である。ストリームユニットは、空きメモリ状態のFIFO14、及び停止されたストリームユニットシーケンサ(図示せず)で開始される。PTSレジスタ95は、(CTSに関連する)適切な開始時間、及びストリーム状態マシン98に発生されるRUN命令でロードされる。CTSが開始時間に進んだ後、すなわち、条件mod(CTS−PTS)≧0が真である場合、ランイネーブル信号RUN_ENがストリーム状態マシン98に発生される。

入力信号及び出力信号は、「ビットクロック(bck)領域」から更に高いシステムクロック(sys_clk)領域に同期することができ、それによって、ビットクロック領域の入力から出力まで“input−to−output”の遅延は、簡単な複数の「ビットクロック」周期により表現することができ、「システムクロック」周波数とは完全に独立である。先に説明したようなI2S(図5参照、BIT_CLKに同期するDATA/LRCK)又はAClink(AC97)インタフェースのような、別々のクロック、並びにデータ及び/又は同期信号を有するシリアルオーディオデータインタフェースに関連する信号は、インタフェースのビットクロック又はチャネルクロックに代わり、共通の(更に高い)システムクロック(図10、sys_clk)のみを使用するロジックにより処理される場合(図10におけるBCK=bck、図5におけるBIT_CLK)、オーディオインタフェースの1つ以上のクロックが固定位相を有さず、かつシステムクロックの整数倍の正確な周波数を有さない限り、追加のクロック同期ステージが必要とされる。このクロック同期は、図10に示されるようなRFF1/RFF2及び/又はCFF0/CFF1のそれぞれのような2つのDフリップフロップの構成を使用することで達成することができる。これらのDフリップフロップは、システムクロックsys_clkでクロックされる。同期されるべき1つ以上の入力信号(RFF0の出力Qでの信号及び/又はクロックbck)は、第一のフリップフロップCFF0及びRFF1のそれぞれのD入力に供給される。このように、「同期された」入力信号は、第二のフリップフロップCFF1及びRFF2のQ出力で利用可能である。かかる2つのフリップフロップ回路は、「準安定」という公知の影響のため、第一のフリップフロップのエラーの確率を十分に低い量に低減する。ホールドウィンドウに関する第一のフリップフロップの入力のセットアップの妨害により、技術に依存した確率に関係する所与の期間の間、フリップフロップの未定義の出力状態がもたらされる。フリップフロップのかかる準安定状態は、不安定である。しかし、2つのフリップフロップ回路により、それぞれのフリップフロップは、好都合なことに、約1クロック周期内でその2つの安定状態のうちの1つに強制的に再び設定される。

ビットクロックbckの同じタイプの「サンプル」エッジ(たとえば、立ち上がりエッジ)でクロックされる入力ステージRFF0及び出力ステージTFF1。反対のタイプの「出力」エッジでクロックされる第二の選択的な出力ステージTFF2。ビットクロックbck(CFF0,CFF1)及びデータ入力Din(RFF1、RFF2)のための準安定「抑圧」回路、すなわち、少なくとも1つのフリップフロップが、SYS_clkでクロックされ、かつbck_enでイネーブルされるsys_clk領域で動作し(RFF3及びTFF0)、以下の特性を有している(フリップフロップTFF0を用いることなしに、正確な値は図10における好適な実施の形態で適用される)。

12:チャネルデコーダユニット

13:ストリームユニット

14:FIFO

15:バスインタフェース

16:クロックユニット

17:タイマーユニット

18,19:レジスタファイル

101:入力同期回路

102:ビットクロック同期装置

103:出力同期回路

104:クロック選択ユニット

Claims (9)

- 共通のシステムクロック(sys_clk)を使用して、共通フォーマットの中央演算処理のために、異なるタイプのインタフェース(IEC958,I2S,AC−Link,ADAT)からの入力信号(SADI)をプリプロセスするための方法であって、前記異なるインタフェースタイプは、異なるサンプルクロック周波数、及び/又は異なるデータフレーム又はデータワードのフォーマットに関連しており、

前記異なるタイプのインタフェースからの入力信号(SADI)から、システムクロックに同期した入力信号を発生し(GPI)、

前記異なるタイプのインタフェースに関連する前記異なるチャネルプロトコル(IEC958,I2S,AC−Link,ADAT)に従い、前記システムクロックに同期した入力信号をチャネルデコードし(11)、一様なワードフォーマットを有する対応するPCMビットストリームのフォーマット信号を供給し、

前記PCMビットストリームのフォーマット信号から、たとえばFIFOのような、これよりサンプルワードが前記中央演算処理に供給される中間的な記憶装置(14)に記憶されるサンプルワードを形成するように、前記PCMビットストリームのフォーマット信号をさらに処理する(13)、

ことを特徴とする方法。 - 共通のシステムクロック(sys_clk)を使用して、共通フォーマットの中央演算処理において、異なるタイプのインタフェース(IEC958,I2S,AC−Link,ADAT)への出力信号(SADO)をプリプロセスするための方法であって、前記異なるインタフェースタイプは、異なるサンプルクロック周波数、及び/又は異なるデータフレーム又はデータワードのフォーマットに関連しており、

システムクロックに同期したPCMビットストリームのフォーマット信号をサンプルワードから形成することで、前記中央演算処理から出力され(SB)、たとえばFIFOのような中間的な記憶装置(14)に記憶される前記サンプルワードをさらに処理し(13)、PCMビットストリームのフォーマット信号は、一様なワードフォーマットを有し、かつ前記異なるタイプのインタフェース(IEC958,I2S,AC−Link,ADAT)に関連しており、

前記異なるタイプのインタフェースに関連する前記異なるチャネルプロトコル(IEC958,I2S,AC−Link,ADAT)に従い、一様なワードフォーマットを有する前記システムクロックに同期したPCMビットストリームのフォーマット信号をチャネルエンコードして、対応するシステムクロックに同期した出力信号を供給し(12)、

前記システムクロックに同期した出力信号から、もはやシステムクロックに同期しないが前記タイプのインタフェースに従うインタフェースタイプに適合した出力信号(SADO)を発生する(GPO)、

ことを特徴とする方法。 - 共通のシステムクロック(sys_clk)を使用して、共通フォーマットの中央演算処理のために、異なるタイプのインタフェース(IEC958,I2S,AC−Link,ADAT)からの入力信号(SADI)をプリプロセスするための装置であって、前記異なるインタフェースタイプは、異なるサンプルクロック周波数、及び/又は異なるデータフレーム又はデータワードのフォーマットに関連しており、

前記異なるタイプのインタフェースからの入力信号(SADI)から、システムクロックに同期した入力信号を発生するための手段(GPI)と、

前記異なるタイプのインタフェースに関連する前記異なるチャネルプロトコル(IEC958,I2S,AC−Link,ADAT)に従い、前記システムクロックに同期した入力信号をチャネルデコードして、一様なワードフォーマットを有する対応するPCMビットストリームのフォーマット信号を供給するための手段(11)と、

前記PCMビットストリームのフォーマット信号から、たとえばFIFOのような、これよりサンプルワードが前記中央演算処理に供給される中間的な記憶装置(14)に記憶されるサンプルワードを形成するように、前記PCMビットストリームのフォーマット信号をさらに処理するための手段(13)と、

を備えることを特徴とする装置。 - 共通のシステムクロック(sys_clk)を使用して、共通フォーマットの中央演算処理において、異なるタイプのインタフェース(IEC958,I2S,AC−Link,ADAT)への出力信号(SADO)をプリプロセスするための装置であって、前記異なるインタフェースタイプは、異なるサンプルクロック周波数、及び/又は異なるデータフレーム又はデータワードのフォーマットに関連しており、

システムクロックに同期したPCMビットストリームのフォーマット信号をサンプルワードから形成することで、前記中央演算処理から出力され(SB)、たとえばFIFOのような中間的な記憶装置(14)に記憶される前記サンプルワードをさらに処理するための手段と(13)、PCMビットストリームのフォーマット信号は、一様なワードフォーマットを有し、かつ前記異なるタイプのインタフェース(IEC958,I2S,AC−Link,ADAT)に関連しており、

前記異なるタイプのインタフェースに関連する前記異なるチャネルプロトコル(IEC958,I2S,AC−Link,ADAT)に従い、一様なワードフォーマットを有する前記システムクロックに同期したPCMビットストリームのフォーマット信号をチャネルエンコードして、対応するシステムクロックに同期した出力信号を供給するための手段と(12)、

前記システムクロックに同期した出力信号から、もはやシステムクロックに同期しないが前記タイプのインタフェースに従うインタフェースタイプに適合した出力信号(SADO)を発生するための手段(GPO)と、

を備えることを特徴とする装置。 - 前記インタフェースのタイプは、IEC958、I2S、AC−Link及びADATのうちの少なくとも2つを含む、

請求項1乃至4のいずれか記載の方法又は装置。 - チャネルの置き換えを検出して回避するために、システムクロックに同期した処理で、幾つかの個々のサンプルがそれらのチャネルタイプで記録又はチェックされ、前記チャネルの置き換えは、たとえばサンプルを挿入又は消去した場合に生じ、前記記録は、たとえば、前記システムクロックに同期した処理で特に使用されないサブコードのビットを使用して実行される、

請求項1乃至5のいずれか記載の方法又は装置。 - 前記中間的な記憶装置(14)に関するDMAブロック転送のために、それぞれのDMAデータブロックの最初のワードについてLFの記録が実行され、該LF記録は、DMAバッファ出力を準備するときにプロセッサの処理数を低減するために評価される、

請求項1乃至6のいずれか記載の方法又は装置。 - 前記サンプルワードの更なる処理を実行するストリームユニットの正確に時間設定されたスタートアップを容易にするために、内部発生されたタイムスタンプが中央演算処理により前記ストリームユニットに供給される、

請求項1乃至7のいずれか記載の方法又は装置。 - 個別のクロック、及びデータ又は前記システムクロックに対する同期信号を有するインタフェース信号の同期のために、同期されるクロック(bck)の同じエッジでクロックされる2つの連続するDフリップフロップが使用される、

請求項1乃至8のいずれか記載の方法又は装置。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP03090038A EP1447739A1 (en) | 2003-02-12 | 2003-02-12 | Method and apparatus for preprocessing input/output signals of/to different types of interfaces using a common format |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004248279A true JP2004248279A (ja) | 2004-09-02 |

| JP2004248279A5 JP2004248279A5 (ja) | 2007-03-08 |

Family

ID=32669012

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004032633A Pending JP2004248279A (ja) | 2003-02-12 | 2004-02-09 | 異なるタイプのインタフェースからの入力信号、又は異なるタイプのインタフェースへの出力信号を共通フォーマットの中央演算処理でプリプロセスするための方法及び装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7127537B2 (ja) |

| EP (1) | EP1447739A1 (ja) |

| JP (1) | JP2004248279A (ja) |

| KR (1) | KR20040073344A (ja) |

| CN (1) | CN100354798C (ja) |

| MX (1) | MXPA04001263A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007115036A (ja) * | 2005-10-20 | 2007-05-10 | Fujitsu Ltd | 非同期伝送装置、非同期伝送方法 |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20060020718A1 (en) * | 2004-06-28 | 2006-01-26 | Duresky Nicholas E | Resource sharing apparatus, systems, and methods |

| US7773733B2 (en) | 2005-06-23 | 2010-08-10 | Agere Systems Inc. | Single-transformer digital isolation barrier |

| US8213489B2 (en) * | 2005-06-23 | 2012-07-03 | Agere Systems Inc. | Serial protocol for agile sample rate switching |

| KR100746003B1 (ko) * | 2005-09-20 | 2007-08-06 | 삼성전자주식회사 | 어레이 마이크로폰의 아날로그 신호를 디지털 신호로변환하는 장치 및 이를 포함하는 컴퓨터 시스템 |

| CN100365631C (zh) * | 2005-11-22 | 2008-01-30 | 北京中星微电子有限公司 | 一种共相式多媒体集成播放系统和方法 |

| KR101116617B1 (ko) * | 2007-07-20 | 2012-03-07 | 삼성전자주식회사 | I2S(Inter-IC Sound) 형식의 오디오전송과 처리에 관한 방법 및 그 장치 |

| CN102522110B (zh) * | 2011-11-30 | 2014-07-30 | 苏州顺芯半导体有限公司 | 数字音频接口发送电路中实现数据预加载的方法和装置 |

| EP2672393A1 (en) | 2012-06-04 | 2013-12-11 | Dialog Semiconductor B.V. | Circuit and methods to use an audio interface to program a device within an audio stream |

| US10171540B2 (en) * | 2012-09-07 | 2019-01-01 | High Sec Labs Ltd | Method and apparatus for streaming video security |

| US9842071B2 (en) * | 2014-11-11 | 2017-12-12 | Microchip Technology Incorporated | Multi-channel I2S transmit control system and method |

| KR102276895B1 (ko) * | 2017-08-17 | 2021-07-12 | 삼성전자주식회사 | 반도체 장치 및 그 이벤트 프로파일링 방법 |

| US10452345B1 (en) * | 2018-05-15 | 2019-10-22 | Sonos, Inc. | Media playback system with virtual line-in |

| EP3573342B1 (en) * | 2018-05-25 | 2021-03-31 | Harman Becker Automotive Systems GmbH | Multi-rate digital sensor synchronization |

| TWI699656B (zh) * | 2018-12-27 | 2020-07-21 | 新唐科技股份有限公司 | 可切換的i2s介面 |

| CN110086549B (zh) * | 2019-04-02 | 2021-09-14 | 北京小米移动软件有限公司 | 音频数据传输方法及装置 |

| CN111027284B (zh) * | 2019-12-05 | 2023-08-25 | 集奥聚合(北京)人工智能科技有限公司 | 一种基于数据灵活接入标准化输出方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3886317A (en) * | 1973-12-17 | 1975-05-27 | Vidar Corp | Synchronous data channel for pulse code modulation communications system |

| US4607345A (en) * | 1982-01-07 | 1986-08-19 | Rockwell International Corporation | Serial data word transmission rate converter |

| DE3789543T2 (de) * | 1987-01-27 | 1994-11-10 | Hitachi Ltd | Verfahren und Gerät zur PCM-Aufzeichnung und -Wiedergabe eines Audiosignals. |

| US5341368A (en) * | 1992-05-05 | 1994-08-23 | American Tel-A-Systems, Inc. | Digital switching system interconnecting buses with imcompatible protocols |

| JP2941867B2 (ja) * | 1989-12-15 | 1999-08-30 | キヤノン株式会社 | 記録再生装置 |

| JPH0816181A (ja) * | 1994-06-24 | 1996-01-19 | Roland Corp | 効果付加装置 |

| US6128681A (en) * | 1997-08-07 | 2000-10-03 | Avid Technology, Inc. | Serial to parallel and parallel to serial, converter for a digital audio workstation |

| US6029221A (en) * | 1998-06-02 | 2000-02-22 | Ati Technologies, Inc. | System and method for interfacing a digital signal processor (DSP) to an audio bus containing frames with synchronization data |

-

2003

- 2003-02-12 EP EP03090038A patent/EP1447739A1/en not_active Withdrawn

-

2004

- 2004-02-09 JP JP2004032633A patent/JP2004248279A/ja active Pending

- 2004-02-10 US US10/775,468 patent/US7127537B2/en active Active

- 2004-02-10 MX MXPA04001263A patent/MXPA04001263A/es active IP Right Grant

- 2004-02-11 KR KR1020040008889A patent/KR20040073344A/ko not_active Application Discontinuation

- 2004-02-12 CN CNB2004100048933A patent/CN100354798C/zh not_active Expired - Lifetime

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007115036A (ja) * | 2005-10-20 | 2007-05-10 | Fujitsu Ltd | 非同期伝送装置、非同期伝送方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100354798C (zh) | 2007-12-12 |

| CN1521599A (zh) | 2004-08-18 |

| MXPA04001263A (es) | 2005-06-17 |

| US20040161040A1 (en) | 2004-08-19 |

| KR20040073344A (ko) | 2004-08-19 |

| EP1447739A1 (en) | 2004-08-18 |

| US7127537B2 (en) | 2006-10-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2004248279A (ja) | 異なるタイプのインタフェースからの入力信号、又は異なるタイプのインタフェースへの出力信号を共通フォーマットの中央演算処理でプリプロセスするための方法及び装置 | |

| US6385704B1 (en) | Accessing shared memory using token bit held by default by a single processor | |

| US6145007A (en) | Interprocessor communication circuitry and methods | |

| US7886271B2 (en) | Embedding event information in the timing stream | |

| US6782300B2 (en) | Circuits and methods for extracting a clock from a biphase encoded bit stream and systems using the same | |

| US7274313B2 (en) | High speed data recording with input duty cycle distortion | |

| US7739669B2 (en) | Paced trace transmission | |

| US20060255972A1 (en) | Trace Receiver Data Compression | |

| JPH05219141A (ja) | 制御及びステータス情報を受信しかつ送信するための回路及び方法 | |

| US5214705A (en) | Circuit and method for communicating digital audio information | |

| US5479445A (en) | Mode dependent serial transmission of digital audio information | |

| US5960401A (en) | Method for exponent processing in an audio decoding system | |

| JP4336860B2 (ja) | シリアルインタフェース回路、及びシリアル受信器 | |

| JP3451971B2 (ja) | パケット転送装置 | |

| US7676697B2 (en) | Using a delay line to cancel clock insertion delays | |

| EP1455471A2 (en) | Method and apparatus for preprocessing in a common-format, input signals of, or output signals for, interfaces of different type | |

| CN115437988A (zh) | 一种i2s音频时钟数据的同步方法、装置及应用 | |

| JP2948245B2 (ja) | 通信ネットワーク局のための送受信同期化装置 | |

| JP3358581B2 (ja) | パケット転送装置 | |

| JP3451973B2 (ja) | パケット転送装置 | |

| TMS320C672x et al. | Reference Guide | |

| US7613951B2 (en) | Scaled time trace | |

| EP1540863B1 (en) | Staged locking of phase locked loops | |

| JP3451972B2 (ja) | パケット転送装置 | |

| JP2005150860A (ja) | データ送信装置及びデータ受信装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070122 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070122 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090813 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090825 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100202 |