JP2004192518A - 定電流発生回路及びその定電流発生回路の定電流設定方法 - Google Patents

定電流発生回路及びその定電流発生回路の定電流設定方法 Download PDFInfo

- Publication number

- JP2004192518A JP2004192518A JP2002362154A JP2002362154A JP2004192518A JP 2004192518 A JP2004192518 A JP 2004192518A JP 2002362154 A JP2002362154 A JP 2002362154A JP 2002362154 A JP2002362154 A JP 2002362154A JP 2004192518 A JP2004192518 A JP 2004192518A

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- current

- voltage

- resistance

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Control Of Electrical Variables (AREA)

Abstract

【解決手段】NMOSトランジスタ22及び23を交互にオン/オフして、NMOSトランジスタ24のソースと負側電源電圧GNDとの間の合成抵抗値αと出力電流Io1との関係を示す2次曲線を近似演算で求め、該2次曲線から得られる所望の出力電流Io1に対する合成抵抗値αからヒューズFB1〜FBnの切断するヒューズを選択し、該選択したヒューズが接続された抵抗と抵抗27〜29の合成抵抗値αの温度係数を打ち消すように、ヒューズFA1〜FAnから切断するヒューズを選択して切断した後、定電圧回路2の出力電圧Vo1に基づいて、ヒューズFB1〜FBnの切断するヒューズを選択して切断する。

【選択図】 図1

Description

【発明の属する技術分野】

本発明は、温度依存性の小さい定電流発生回路に関し、特にトリミングによって目標電流値に対する精度を向上させることができる定電流発生回路及びその定電流発生回路の定電流設定方法に関する。

【0002】

【従来の技術】

定電流発生回路に求められる性能は、目標電流値に対する精度が高く、温度や電源電圧の変動に影響されないことであり、更にすべての回路を1チップに集積しやすいことも重要である。所望の定電流は、定電流ダイオードやFETのしきい値電圧を応用して作り出すことも可能であるが、ある程度の性能を得ようとする場合は、定電圧回路の出力電圧を電圧−電流変換回路によって電流に変換するのが一般的である。

例えば、2つのトランジスタのしきい値電圧の差を抵抗で電圧−電流変換した後、該変換して得られた電流を同種の抵抗で電流−電圧変換することで、温度依存性の小さいしきい値電圧差を増幅して基準電圧を得る回路があった(例えば、特許文献1参照。)。

【0003】

一方、近年、定電圧回路として、温度依存性が小さく、しかも集積回路に適したバンドギャップレギュレータが多く用いられている。例えば、抵抗とpn接合の順方向電圧を利用したバンドギャップ型の基準電圧で、順方向電圧のモニタを行うことで、サーマルボルテージにかかる倍率を抵抗のトリミングで調整し、基準電圧の温度特性を補正する基準電圧回路があった(例えば、特許文献2参照。)。

【0004】

図2は、このような定電圧回路及び電圧−電流変換回路を使用した従来の定電流発生回路の例を示した回路図である。

図2における定電流発生回路100は、バンドギャップレギュレータ101の出力電圧Vo、例えば約1.25Vを電圧−電流変換回路102によって定電流に変換して出力する。なお、バンドギャップレギュレータ101は公知であり、ここではその動作説明を省略する。

【0005】

電圧−電流変換回路102において、演算増幅器121とNMOSトランジスタ122によって、抵抗123の両端の電圧は定電圧回路101の出力電圧Voと同じ値になるように制御される。このため、抵抗123には定電圧回路101の出力電圧Voを抵抗123の抵抗値R123で除した電流(Vo/R123)が流れる。該電流は、NMOSトランジスタ122のドレイン電流となり、カレントミラー回路を構成しているPMOSトランジスタ124及び125を介してPMOSトランジスタ125のドレインから出力される。

【0006】

前記のように、電圧−電流変換回路102からの出力電流Ioは、定電圧回路101の出力電圧Voと抵抗123の抵抗値で決定されることから、定電流Ioを目標値にするためには、定電圧回路101の出力電圧Voを調整するか、又は抵抗123の抵抗値を調整すればよいことが分かる。しかし、定電圧回路101の出力電圧Voは物理的に決まった値であることから、通常は抵抗123の抵抗値をトリミングして設定する。

【0007】

抵抗123のトリミング方法としては、出力電流Ioを測定し、目標値とのずれ量からトリミングの量を決定する方法と、出力電流Ioを測定しながら抵抗123のトリミングを行い、出力電流Ioが目標値に達した時点でトリミングを終了する、いわゆるファンクショントリミングとがあった。

【0008】

【特許文献1】

特開平7−44255号公報

【特許文献2】

特開2002−91589号公報

【0009】

【発明が解決しようとする課題】

しかし、上述した前者のトリミング方法は、短時間に行うことができるが、出力電流Ioと目標値とのずれ量が大きい場合は、トリミング精度が悪くなる。このため、該ずれ量が大きい場合、精度を上げるためにトリミング量をやや少な目にして、2回又は3回同様のトリミングを繰り返すことで、出力電流Ioを所望の目標値にすることができるが、トリミングに要する時間が長くなるという問題があった。

【0010】

また、上述した後者のトリミング方法は、出力電流Ioの調整精度は高いがトリミングに時間がかかり、ファンクショントリミング用に、専用のトリミング装置が必要になる等の問題があった。更に、抵抗123をトリミングして抵抗値を最適値に調整しても、抵抗123の抵抗値が温度によって変化することから、出力電流Ioが変化するという問題があった。また、定電圧回路101と電圧−電流変換回路102をICに集積した場合、集積回路内に形成された抵抗123は通常、温度依存性を有するため、定電圧回路101に温度依存性の小さいバンドギャップレギュレータを使用しても、出力電流Ioは温度依存性を持ってしまい、正確な定電流出力を得ることができないという問題があった。

【0011】

本発明は、上記のような問題を解決するためになされたものであり、集積回路内に作り込まれた抵抗の温度依存性による定電流出力の変化を打ち消すことによって、温度依存性の小さい定電流発生回路及びその定電流発生回路の定電流設定方法を得ることを目的とする。

【0012】

【課題を解決するための手段】

この発明に係る定電流発生回路は、直流電源の電源電圧から所定の定電圧を生成して出力する、バンドギャップリファレンスで形成された定電圧回路部と、該定電圧回路部から出力された定電圧を電流に変換して所定の定電流を出力する電圧−電流変換回路部とを備えた定電流発生回路において、

前記定電圧回路部は、

前記所定の定電圧を出力する第1演算増幅器と、

複数の抵抗で合成抵抗を生成し、一端に該第1演算増幅器の出力電圧が入力される第1抵抗回路と、

該第1抵抗回路の他端と前記直流電源の負側電源電圧との間に接続された、第1抵抗と第1ダイオードが直列に接続されてなり、該第1抵抗と第1ダイオードとの接続部が前記第1演算増幅器の一方の入力端に接続された第1直列回路と、

前記第1抵抗回路の他端と前記直流電源の負側電源電圧との間に接続された、第2抵抗、第3抵抗及び第2ダイオードが直列に接続されてなり、該第2抵抗と第3抵抗との接続部が前記第1演算増幅器の他方の入力端に接続された第2直列回路と、

を備え、

前記電圧−電流変換回路部は、

前記定電圧回路部から出力された定電圧を出力すると共に、該定電圧に応じた電流を出力する電流供給回路と、

複数の抵抗で合成抵抗を生成し、該電流供給回路によって、前記定電圧回路部から出力された定電圧が印加されると共に該定電圧に応じた電流が供給される第2抵抗回路と、

該第2抵抗回路に流れた電流に応じた電流を出力する出力回路と、

を備え、

前記第2抵抗回路は、前記複数の抵抗と複数のヒューズで構成され、前記出力回路からの出力電流が所望の値になるように、前記定電圧回路部からの定電圧に応じた電流が前記第2抵抗回路の合成抵抗に流れるように該各ヒューズが選択的に切断されるものである。

【0013】

具体的には、前記第1抵抗回路は、前記複数の抵抗と複数のヒューズで構成され、前記電圧−電流変換回路部が有する温度特性を相殺する温度特性を有するように該各ヒューズが選択的に切断されるようにした。

【0014】

また、前記第2抵抗回路は、外部から入力された制御信号に応じてスイッチングを行い、第2抵抗回路の合成抵抗を変えるスイッチ回路を備えるようにしてもよい。

【0015】

一方、前記電流供給回路は、

前記定電圧回路部からの定電圧が一方の入力端に入力された第2演算増幅器と、

該第2演算増幅器の出力端に制御信号入力端が接続され、直流電源からの電流を前記第2抵抗回路に供給するトランジスタと、

を備え、

前記第2演算増幅器の他方の入力端は、前記トランジスタからの電流が入力される前記第2抵抗回路の入力端に接続されるようにした。

【0016】

また、本発明に係る定電流設定方法は、複数の抵抗及び複数のヒューズで構成され該ヒューズを選択的に切断することによって設定される第1抵抗回路の合成抵抗に応じて出力電圧が変わる、直流電源の電源電圧から所定の定電圧を生成して出力するバンドギャップリファレンスで形成された定電圧回路部と、複数の抵抗及び複数のヒューズを有し該ヒューズを選択的に切断することによって設定され前記定電圧回路部からの出力電圧が印加される第2抵抗回路の合成抵抗に流れる電流に応じた定電流を出力する、前記定電圧回路部から出力された定電圧を電流に変換して所定の定電流を出力する電圧−電流変換回路部とを備え、該電圧−電流変換回路部が、外部から入力された制御信号に応じてスイッチングを行い前記第2抵抗回路の合成抵抗を変えるスイッチ回路を有した定電流発生回路の定電流設定方法において、

前記スイッチ回路をスイッチングさせ、

該スイッチングに応じた前記第2抵抗回路の各合成抵抗に対する前記電圧−電流変換回路部の出力電流をそれぞれ測定し、

前記第2抵抗回路の該各合成抵抗値に対してそれぞれ測定した前記電圧−電流変換回路部の出力電流値から、近似演算を行って前記合成抵抗と出力電流との関係を示した特性を求め、

該得られた特性から、所望の出力電流値に対する前記第2抵抗回路の合成抵抗値を得るようにした。

【0017】

また、前記所望の出力電流値に対する前記第2抵抗回路の合成抵抗における温度特性を求め、

該得られた温度特性を相殺させる前記第1抵抗回路の合成抵抗を求め、

該得られた合成抵抗になるように前記第1抵抗回路のヒューズを選択的に切断し、

前記スイッチ回路をスイッチングさせ、

該スイッチングに応じた前記第2抵抗回路の各合成抵抗に対する前記電圧−電流変換回路部の出力電流をそれぞれ測定し、

前記第2抵抗回路の該各合成抵抗値に対してそれぞれ測定した前記電圧−電流変換回路部の出力電流値から、近似演算を行って前記合成抵抗と出力電流との関係を示した特性を求め、

該得られた特性から、所望の出力電流値に対する前記第2抵抗回路の合成抵抗値を求め、

前記第2抵抗回路の合成抵抗が該得られた合成抵抗値になるように前記第2抵抗回路のヒューズを選択的に切断するようにした。

【0018】

具体的には、前記スイッチ回路のスイッチングに応じた前記第2抵抗回路の3種類の合成抵抗に対する前記電圧−電流変換回路部の出力電流をそれぞれ測定し、第2抵抗回路の該3種類の合成抵抗値に対してそれぞれ測定した前記電圧−電流変換回路部の出力電流値から、近似演算を行って前記合成抵抗と出力電流との関係を示した2次曲線をなす特性を求めるようにしてもよい。

【0019】

【発明の実施の形態】

次に、図面に示す実施の形態に基づいて、本発明を詳細に説明する。

第1の実施の形態.

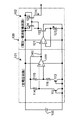

図1は、本発明の第1の実施の形態における定電流発生回路の例を示した回路図である。

図1において、定電流発生回路1は、バンドギャップリファレンスを構成する定電圧回路2と、該定電圧回路2から出力された定電圧Vo1を電流に変換して出力する電圧−電流変換回路3とで構成されている。なお、定電圧回路2は定電圧回路部を、電圧−電流変換回路3は電圧−電流変換回路部をそれぞれなす。定電圧回路2及び電圧−電流変換回路3は、直流電源5から供給される電源によって作動し、電圧−電流変換回路3から出力された電流が定電流発生回路1の出力電流Io1となる。

【0020】

定電圧回路2は、演算増幅器11、pnpトランジスタ12,13、抵抗A1〜Am(mは、m>1の整数),14〜16及びヒューズFA1〜FAmで構成されている。なお、演算増幅器11は第1演算増幅器を、抵抗A1〜Am及びヒューズFA1〜FAmは第1抵抗回路を、pnpトランジスタ12及び抵抗14は第1直列回路を、pnpトランジスタ13及び抵抗15,16は第2直列回路をそれぞれなす。また、pnpトランジスタ12は第1ダイオードを、pnpトランジスタ13は第2ダイオードをそれぞれなす。

【0021】

演算増幅器11の出力端と直流電源5の負側電源電圧GNDとの間には抵抗A1〜Amが直列に接続された直列回路と、抵抗14及びpnpトランジスタ12が直列に接続された直列回路が直列に接続されている。抵抗A1〜Amにはそれぞれ対応するヒューズFA1〜FAmが並列に接続され、抵抗14及びpnpトランジスタ12の直列回路には、抵抗15,16及びpnpトランジスタ13の直列回路が並列に接続されている。

【0022】

抵抗14とpnpトランジスタ12との接続部bは、演算増幅器11の非反転入力端に接続され、抵抗15と16との接続部cは、演算増幅器11の反転入力端に接続されている。抵抗Am、ヒューズFAm、抵抗14及び15の接続部を、接続部aとする。また、pnpトランジスタ12において、ベースはコレクタに接続され、pnpトランジスタ13においても、ベースはコレクタに接続され、pnpトランジスタ12,13はそれぞれダイオードをなしている。演算増幅器11の出力端から出力される電圧が、定電圧回路2の出力電圧Vo1をなす。

【0023】

次に、電圧−電流変換回路3は、演算増幅器21、NMOSトランジスタ22〜24、PMOSトランジスタ25,26、抵抗B1〜Bn(nは、n>1の整数),27〜29及びヒューズFB1〜FBnで構成されている。なお、演算増幅器21及びNMOSトランジスタ24は電流供給回路を、PMOSトランジスタ25及び26は出力回路を、NMOSトランジスタ22,23、抵抗B1〜Bn及びヒューズFB1〜FBnは第2抵抗回路をそれぞれなし、NMOSトランジスタ22及び23はスイッチ回路をなす。

演算増幅器21の非反転入力端には定電圧回路2の出力電圧Vo1が入力され、演算増幅器21の出力端はNMOSトランジスタ24のゲートに接続されている。

【0024】

PMOSトランジスタ25及び26は、カレントミラー回路を形成しており、各ゲートは接続されてPMOSトランジスタ25のドレインに接続され、PMOSトランジスタ25及び26の各ソースは、それぞれ直流電源5の正側電源電圧Vbatが印加されている。PMOSトランジスタ25のドレインと、直流電源5の負側電源電圧GNDとの間には、NMOSトランジスタ24、抵抗B1〜Bn及び27〜29が直列に接続されており、抵抗B1〜Bnには、対応するヒューズFB1〜FBnがそれぞれ並列に接続されている。

【0025】

抵抗28と抵抗29との直列回路に並列にNMOSトランジスタ22が接続され、抵抗29に並列にNMOSトランジスタ23が接続されている。NMOSトランジスタ22のゲートには外部からの制御信号S1が入力され、NMOSトランジスタ23のゲートには外部からの制御信号S2が入力されている。PMOSトランジスタ26のドレインから出力される電流が、出力電流Io1をなす。

【0026】

このような構成において、電圧−電流変換回路3について説明する。

抵抗B1〜抵抗Bnはトリミング用の抵抗であり、各々の抵抗にはトリミングのためのヒューズFB1〜FBnが並列接続されている。

スイッチ回路をなすNMOSトランジスタ22は、ゲートにハイレベルの信号が入力されるとオンし、抵抗27と抵抗28の接続部を負側電源電圧GNDに接続して、NMOSトランジスタ24のソースと負側電源電圧GNDとの間の合成抵抗値αを小さくすることができる。同様に、スイッチ回路をなすNMOSトランジスタ23は、抵抗28と抵抗29との接続部と負側電源電圧GNDとの間に接続され、ゲートにハイレベルの信号が入力されるとオンし、抵抗28と抵抗29の交点を負側電源電圧GNDに接続して、合成抵抗値αを小さくすることができる。

【0027】

演算増幅器21とNMOSトランジスタ24によって、NMOSトランジスタ24のソース電圧は定電圧回路2の出力電圧Vo1と同じになるように制御される。このことから、電圧−電流変換回路3の抵抗B1〜Bn,27〜29の抵抗群には定電圧回路2の出力電圧Vo1を合成抵抗値αで除した電流(Vo1/α)が流れる。該電流は、NMOSトランジスタ24のドレイン電流となり、PMOSトランジスタ25,26を介してPMOSトランジスタ26のドレインから出力される。

【0028】

ここで、抵抗B1〜Bnの各抵抗値をRB1〜RBnとし、抵抗27〜29の各抵抗値をR27〜R29とすると、トリミングを行う前の合成抵抗値αは、(R27+R28+R29)である。今、NMOSトランジスタ22及び23が共にオフの場合の出力電流Io1は、下記(1)式のようになる。

Io1=Vo1/(R27+R28+R29)………………(1)

【0029】

次に、NMOSトランジスタ22がオフで、NMOSトランジスタ23がオンしている場合の出力電流Io1は下記(2)式のようになる。

Io1=Vo1/(R27+R28)………………(2)

また、NMOSトランジスタ22がオンしたときの出力電流Io1は下記(3)式のようになる。

Io1=Vo1/(R27)………………(3)

【0030】

前記(1)〜(3)式の各出力電流Io1とそのときの合成抵抗値αから目標とする出力電流Io1が得られる合成抵抗値αを近似演算し、NMOSトランジスタ22,23をオン/オフする組み合わせと、トリミングによって切断するヒューズFB1〜FBnを決定する。

このように、2つのNMOSトランジスタ22,23を使用して、3種類の合成抵抗値αに対するそれぞれの出力電流Io1を測定し、合成抵抗値αと出力電流Io1の関係を示した2次曲線を得ることができる。このため、NMOSトランジスタ24の非直線部分を補うことができ、該2次曲線から所望の出力電流Io1を得るための合成抵抗値αを得ることができる。

【0031】

例えば、出力電流Io1をDC−DCコンバータのスイッチング周波数発生回路等に使用した場合は、NMOSトランジスタ22及び23のオン/オフの組み合わせごとにスイッチング周波数を測定し、該スイッチング周波数と合成抵抗値αを近似演算することによって、出力電流Io1からスイッチング周波数が生成される部分で生ずる非直線性を補償することができる。言うまでもなく、直線近似で十分な精度が得られる場合は、NMOSトランジスタ22又は23のいずれか1つを削除して合成抵抗値αと出力電流Io1の測定ポイントを2種類にし、近似演算を簡潔にしてもよい。

【0032】

一方、電圧−電流変換回路3をICに集積する場合、抵抗B1〜Bn及び27〜29を構成している各抵抗素子は温度依存性を有しており、前記の方法で出力電流Io1が目標電流値になるようにヒューズFB1〜FBnをトリミングしても、温度変化によって目標電流値から外れてしまうことがある。抵抗RB1〜RBn及び27〜29にP型ポリシリコン抵抗を使用した場合、温度係数は約600ppm/℃である。すなわち、該P型ポリシリコン抵抗を使用した場合、温度が1℃変化するごとに0.6%出力電流Io1が変動してしまう。例えば、携帯機器に使用する場合は、氷点下から40℃を超える温度範囲に対応しなければならないことから、温度変化は60℃以上にもなる。仮に温度変化を60℃とすると、出力電流Io1の変動は3.6%となり、用途によっては、目標電流値から逸脱してしまうことになる。

【0033】

このため、電圧−電流変換回路3に入力される定電圧回路2の出力電圧Vo1に温度依存性を持たせ、電圧−電流変換回路3の抵抗B1〜Bn及び27〜29の温度係数を打ち消すようにすればよい。

ここで、演算増幅器11の出力電圧Vo1を導出する。

pnpトランジスタ12のベース−エミッタ間電圧をVBE1に、pnpトランジスタ13のベース−エミッタ間電圧をVBE2にそれぞれし、抵抗14と抵抗15の抵抗値を同じにする。

【0034】

図1の接続部bと接続部cは、演算増幅器11の2つの入力端に対応して接続されているので同電圧である。また、抵抗14と抵抗15は接続部aで共通接続されているため、抵抗14と抵抗15の両端の電圧は等しい。すなわち、pnpトランジスタ12及び13の各コレクタ電流Icはそれぞれ等しくなり、該コレクタ電流Icは下記(4)式で表される。

なお、前記(4)式において、Nはpnpトランジスタ12とpnpトランジスタ13のエミッタ面積比であり、Isはpnpトランジスタ12とpnpトランジスタ13の飽和電流であり、kはボルツマン定数、qは電子の電荷量、Tは絶対温度である。

【0035】

前記(4)式から、ベース−エミッタ間電圧VBE1及びVBE2は下記(5)式及び(6)式のように示すことができる。

VBE1=(k×T)/q×ln(Ic/Is)………………(5)

VBE2=(k×T)/q×ln{Ic/(N×Is)}………………(6)

【0036】

また、抵抗14〜16の各抵抗値をR14〜R16とすると、VBE1=Ic×R16+VBE2であるから、

(k×T)/q×ln(Ic/Is)=Ic×R16+(k×T)/q×ln(Ic/N×Is)………………(7)

前記(7)式からIcを求めると、下記(8)式のようになる。

Ic=(k×T)/q×ln(N)/R16………………(8)

【0037】

以上の結果から、演算増幅器11の出力端と接続部aとの間の合成抵抗値をβとすると、演算増幅器11の出力電圧Vo1は下記(9)式のようになる。

【0038】

抵抗A1〜Am及び14〜16は、高抵抗ポリシリコンで形成されており、温度係数が約−2300ppm/℃の特性を有するものであり、(9)式がVBG/(1−KT×T)を満たすように抵抗A1〜Am及び14〜16を設定することによって、電圧−電流変換回路3の温度依存性を打ち消すことができる。なお、VBGはエネルギーバンドギャップに相当する電圧、KTは合成抵抗値αの温度係数である。

【0039】

次に、定電圧回路2の各ヒューズFA1〜FAm及び電圧−電流変換回路3の各ヒューズFB1〜FBnに対するトリミングの手順について説明する。

まず最初に、各ヒューズFB1〜FBnのトリミングを行う前に、電圧−電流変換回路3のNMOSトランジスタ22及び23を交互にオン/オフして、近似演算を行って合成抵抗値αと出力電流Io1との関係を示す2次曲線を求め、得られた2次曲線から所望の出力電流Io1に対する合成抵抗値αを得る。得られた合成抵抗値αからヒューズFB1〜FBnの内、切断するヒューズを選択する。該選択したヒューズが接続された抵抗と抵抗27〜29の合成抵抗値αの温度係数を打ち消すように、ヒューズFA1〜FAmの内、切断するヒューズを選択しトリミングを行って切断する。

【0040】

ヒューズFA1〜FAmの選択したヒューズの切断を行うと、定電圧回路2の出力電圧Vo1が若干変化するため、再度、電圧−電流変換回路3のNMOSトランジスタ22及び23を交互にオン/オフし、近似演算を行って合成抵抗値αと出力電流Io1との関係を示す2次曲線を求め、得られた2次曲線から所望の出力電流Io1に対する合成抵抗値αを得る。得られた合成抵抗値αからヒューズFB1〜FBnの内、切断するヒューズを選択しトリミングを行って切断する。本第1の実施の形態における定電流発生回路は、このような手順でヒューズFA1〜FAm及びFB1〜FBnをトリミングすることにより、高精度でかつ温度依存性の小さい定電流発生回路を得ることができる。

【0041】

【発明の効果】

上記の説明から明らかなように、本発明の定電流発生回路によれば、電圧−電流変換回路部の温度特性を、定電圧回路部の第1抵抗回路に温度特性を持たせることで相殺できるようにしたため、IC化して、電圧−電流変換回路部に温度係数の小さい抵抗が使えない場合でも、精度の高い安定した定電流を生成して出力することができる。

【0042】

また、本発明の定電流設定方法によれば、スイッチ回路をスイッチングさせて得られた前記第2抵抗回路の各合成抵抗値に対する前記電圧−電流変換回路部の出力電流値から、近似演算を行って第2抵抗回路の合成抵抗と出力電流との関係を示した特性を求め、得られた特性から所望の出力電流値に対する前記第2抵抗回路の合成抵抗値を得るようにした。このことから、所望のヒューズをトリミングして切断する前に、第2抵抗回路の合成抵抗値を得ることができ、切断するヒューズを選択することができ、短時間で高精度な定電流設定を行うことができる。

【図面の簡単な説明】

【図1】本発明の第1の実施の形態における定電流発生回路の例を示した回路図である。

【図2】従来の定電流発生回路の例を示した回路図である。

【符号の説明】

1 定電流発生回路

2 定電圧回路

3 電圧−電流変換回路

5 直流電源

11,21 演算増幅器

12,13 pnpトランジスタ

22〜24 NMOSトランジスタ

25,26 PMOSトランジスタ

A1〜Am,B1〜Bn,14〜16,27〜29 抵抗

FA1〜FAm,FB1〜FBn ヒューズ

Claims (7)

- 直流電源の電源電圧から所定の定電圧を生成して出力する、バンドギャップリファレンスで形成された定電圧回路部と、該定電圧回路部から出力された定電圧を電流に変換して所定の定電流を出力する電圧−電流変換回路部とを備えた定電流発生回路において、

前記定電圧回路部は、

前記所定の定電圧を出力する第1演算増幅器と、

複数の抵抗で合成抵抗を生成し、一端に該第1演算増幅器の出力電圧が入力される第1抵抗回路と、

該第1抵抗回路の他端と前記直流電源の負側電源電圧との間に接続された、第1抵抗と第1ダイオードが直列に接続されてなり、該第1抵抗と第1ダイオードとの接続部が前記第1演算増幅器の一方の入力端に接続された第1直列回路と、

前記第1抵抗回路の他端と前記直流電源の負側電源電圧との間に接続された、第2抵抗、第3抵抗及び第2ダイオードが直列に接続されてなり、該第2抵抗と第3抵抗との接続部が前記第1演算増幅器の他方の入力端に接続された第2直列回路と、

を備え、

前記電圧−電流変換回路部は、

前記定電圧回路部から出力された定電圧を出力すると共に、該定電圧に応じた電流を出力する電流供給回路と、

複数の抵抗で合成抵抗を生成し、該電流供給回路によって、前記定電圧回路部から出力された定電圧が印加されると共に該定電圧に応じた電流が供給される第2抵抗回路と、

該第2抵抗回路に流れた電流に応じた電流を出力する出力回路と、

を備え、

前記第2抵抗回路は、前記複数の抵抗と複数のヒューズで構成され、前記出力回路からの出力電流が所望の値になるように、前記定電圧回路部からの定電圧に応じた電流が前記第2抵抗回路の合成抵抗に流れるように該各ヒューズが選択的に切断されることを特徴とする定電流発生回路。 - 前記第1抵抗回路は、前記複数の抵抗と複数のヒューズで構成され、前記電圧−電流変換回路部が有する温度特性を相殺する温度特性を有するように該各ヒューズが選択的に切断されることを特徴とする請求項1記載の定電流発生回路。

- 前記第2抵抗回路は、外部から入力された制御信号に応じてスイッチングを行い、第2抵抗回路の合成抵抗を変えるスイッチ回路を備えることを特徴とする請求項2記載の定電流発生回路。

- 前記電流供給回路は、

前記定電圧回路部からの定電圧が一方の入力端に入力された第2演算増幅器と、

該第2演算増幅器の出力端に制御信号入力端が接続され、直流電源からの電流を前記第2抵抗回路に供給するトランジスタと、

を備え、

前記第2演算増幅器の他方の入力端は、前記トランジスタからの電流が入力される前記第2抵抗回路の入力端に接続されることを特徴とする請求項2又は3記載の定電流発生回路。 - 複数の抵抗及び複数のヒューズで構成され該ヒューズを選択的に切断することによって設定される第1抵抗回路の合成抵抗に応じて出力電圧が変わる、直流電源の電源電圧から所定の定電圧を生成して出力するバンドギャップリファレンスで形成された定電圧回路部と、複数の抵抗及び複数のヒューズを有し該ヒューズを選択的に切断することによって設定され前記定電圧回路部からの出力電圧が印加される第2抵抗回路の合成抵抗に流れる電流に応じた定電流を出力する、前記定電圧回路部から出力された定電圧を電流に変換して所定の定電流を出力する電圧−電流変換回路部とを備え、該電圧−電流変換回路部が、外部から入力された制御信号に応じてスイッチングを行い前記第2抵抗回路の合成抵抗を変えるスイッチ回路を有した定電流発生回路の定電流設定方法において、

前記スイッチ回路をスイッチングさせ、

該スイッチングに応じた前記第2抵抗回路の各合成抵抗に対する前記電圧−電流変換回路部の出力電流をそれぞれ測定し、

前記第2抵抗回路の該各合成抵抗値に対してそれぞれ測定した前記電圧−電流変換回路部の出力電流値から、近似演算を行って前記合成抵抗と出力電流との関係を示した特性を求め、

該得られた特性から、所望の出力電流値に対する前記第2抵抗回路の合成抵抗値を得ることを特徴とする定電流設定方法。 - 前記所望の出力電流値に対する前記第2抵抗回路の合成抵抗における温度特性を求め、

該得られた温度特性を相殺させる前記第1抵抗回路の合成抵抗を求め、

該得られた合成抵抗になるように前記第1抵抗回路のヒューズを選択的に切断し、

前記スイッチ回路をスイッチングさせ、

該スイッチングに応じた前記第2抵抗回路の各合成抵抗に対する前記電圧−電流変換回路部の出力電流をそれぞれ測定し、

前記第2抵抗回路の該各合成抵抗値に対してそれぞれ測定した前記電圧−電流変換回路部の出力電流値から、近似演算を行って前記合成抵抗と出力電流との関係を示した特性を求め、

該得られた特性から、所望の出力電流値に対する前記第2抵抗回路の合成抵抗値を求め、

前記第2抵抗回路の合成抵抗が該得られた合成抵抗値になるように前記第2抵抗回路のヒューズを選択的に切断することを特徴とする請求項5記載の定電流設定方法。 - 前記スイッチ回路のスイッチングに応じた前記第2抵抗回路の3種類の合成抵抗に対する前記電圧−電流変換回路部の出力電流をそれぞれ測定し、第2抵抗回路の該3種類の合成抵抗値に対してそれぞれ測定した前記電圧−電流変換回路部の出力電流値から、近似演算を行って前記合成抵抗と出力電流との関係を示した2次曲線をなす特性を求めることを特徴とする請求項5又は6記載の定電流設定方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002362154A JP4213459B2 (ja) | 2002-12-13 | 2002-12-13 | 定電流発生回路及びその定電流発生回路の定電流設定方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002362154A JP4213459B2 (ja) | 2002-12-13 | 2002-12-13 | 定電流発生回路及びその定電流発生回路の定電流設定方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004192518A true JP2004192518A (ja) | 2004-07-08 |

| JP4213459B2 JP4213459B2 (ja) | 2009-01-21 |

Family

ID=32760683

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002362154A Expired - Fee Related JP4213459B2 (ja) | 2002-12-13 | 2002-12-13 | 定電流発生回路及びその定電流発生回路の定電流設定方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4213459B2 (ja) |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007213270A (ja) * | 2006-02-09 | 2007-08-23 | Ricoh Co Ltd | 定電流回路 |

| JP2007233899A (ja) * | 2006-03-03 | 2007-09-13 | New Japan Radio Co Ltd | 電流源回路 |

| JP2008165287A (ja) * | 2006-12-27 | 2008-07-17 | Sharp Corp | 定電流ドライバ |

| JP2009116748A (ja) * | 2007-11-08 | 2009-05-28 | Panasonic Corp | 定電圧回路 |

| JP2010003115A (ja) * | 2008-06-20 | 2010-01-07 | Mitsumi Electric Co Ltd | 定電流回路 |

| JP2013106371A (ja) * | 2011-11-10 | 2013-05-30 | Rohm Co Ltd | 過電流保護回路及びこれを用いたスイッチング電源装置 |

| CN109756209A (zh) * | 2017-11-01 | 2019-05-14 | 中芯国际集成电路制造(上海)有限公司 | 一种熔丝单元及具有该熔丝单元的半导体器件和电子装置 |

| CN109960303A (zh) * | 2019-04-30 | 2019-07-02 | 深圳市明微电子股份有限公司 | 一种自适应恒流控制装置 |

| US10895888B2 (en) | 2019-04-04 | 2021-01-19 | Seiko Epson Corporation | Watch and manufacturing method of constant current circuit |

-

2002

- 2002-12-13 JP JP2002362154A patent/JP4213459B2/ja not_active Expired - Fee Related

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007213270A (ja) * | 2006-02-09 | 2007-08-23 | Ricoh Co Ltd | 定電流回路 |

| US7474145B2 (en) | 2006-02-09 | 2009-01-06 | Ricoh Company, Ltd. | Constant current circuit |

| JP2007233899A (ja) * | 2006-03-03 | 2007-09-13 | New Japan Radio Co Ltd | 電流源回路 |

| JP2008165287A (ja) * | 2006-12-27 | 2008-07-17 | Sharp Corp | 定電流ドライバ |

| JP2009116748A (ja) * | 2007-11-08 | 2009-05-28 | Panasonic Corp | 定電圧回路 |

| JP2010003115A (ja) * | 2008-06-20 | 2010-01-07 | Mitsumi Electric Co Ltd | 定電流回路 |

| JP2013106371A (ja) * | 2011-11-10 | 2013-05-30 | Rohm Co Ltd | 過電流保護回路及びこれを用いたスイッチング電源装置 |

| CN109756209A (zh) * | 2017-11-01 | 2019-05-14 | 中芯国际集成电路制造(上海)有限公司 | 一种熔丝单元及具有该熔丝单元的半导体器件和电子装置 |

| CN109756209B (zh) * | 2017-11-01 | 2023-05-02 | 中芯国际集成电路制造(上海)有限公司 | 一种熔丝单元及具有该熔丝单元的半导体器件和电子装置 |

| US10895888B2 (en) | 2019-04-04 | 2021-01-19 | Seiko Epson Corporation | Watch and manufacturing method of constant current circuit |

| CN109960303A (zh) * | 2019-04-30 | 2019-07-02 | 深圳市明微电子股份有限公司 | 一种自适应恒流控制装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4213459B2 (ja) | 2009-01-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10642305B2 (en) | High-accuracy CMOS temperature sensor and operating method | |

| US7750728B2 (en) | Reference voltage circuit | |

| US7622906B2 (en) | Reference voltage generation circuit responsive to ambient temperature | |

| JP4476276B2 (ja) | バンドギャップ基準電圧回路および温度曲率補正された基準電圧の生成方法 | |

| US7808068B2 (en) | Method for sensing integrated circuit temperature including adjustable gain and offset | |

| US8922190B2 (en) | Band gap reference voltage generator | |

| US7710096B2 (en) | Reference circuit | |

| KR101829416B1 (ko) | 보상된 밴드갭 | |

| US8212606B2 (en) | Apparatus and method for offset drift trimming | |

| US6783274B2 (en) | Device for measuring temperature of semiconductor integrated circuit | |

| US7633333B2 (en) | Systems, apparatus and methods relating to bandgap circuits | |

| JP2003258105A (ja) | 基準電圧発生回路及びその製造方法、並びにそれを用いた電源装置 | |

| US8461914B2 (en) | Reference signal generating circuit | |

| US20160077541A1 (en) | Method and circuit for low power voltage reference and bias current generator | |

| US20180074532A1 (en) | Reference voltage generator | |

| US7253599B2 (en) | Bandgap reference circuit | |

| US7843231B2 (en) | Temperature-compensated voltage comparator | |

| US20120262146A1 (en) | Reference-voltage generation circuit | |

| JP4213459B2 (ja) | 定電流発生回路及びその定電流発生回路の定電流設定方法 | |

| US20070040543A1 (en) | Bandgap reference circuit | |

| US7638996B2 (en) | Reference current generator circuit | |

| US20080164937A1 (en) | Band gap reference circuit which performs trimming using additional resistor | |

| JP2018128926A (ja) | 基準電圧発生回路及び方法 | |

| JP2002318626A (ja) | 定電圧回路 | |

| JPH0659751A (ja) | バンドギャップ基準電圧調整回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20051011 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20081021 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20081030 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111107 Year of fee payment: 3 |

|

| R150 | Certificate of patent (=grant) or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111107 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121107 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131107 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |