以下、図1〜図47を参照して、本発明の第1実施形態〜第5実施形態及び第1参考例〜第22参考例について説明する。

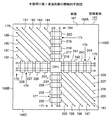

(第1実施形態・・図1〜図5)

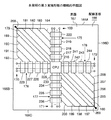

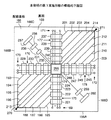

図1及び図2はそれぞれ本発明の第1実施形態の概略的平面図及び概略的下面図であり、図1及び図2において、166は配線基板、167は配線基板166の表面、168は配線基板166の裏面、169〜172はスルーホール群である。

また、図3及び図4はそれぞれ配線基板166の表面167及び裏面168に形成されている配線の一部分を示す概略的平面図及び概略的下面図であり、図3において、173は配線基板166の表面167の中央部に設定された矩形のCPU搭載領域であり、図4において、174は配線基板166の裏面168の中央部に設定された矩形の終端抵抗形成領域である。

また、図3、図4において、175はCPU搭載領域173の辺173Aの近傍から配線基板166の表面167側を配線基板166の辺166Aに向けて延び、スルーホール群169を介して配線基板166の裏面168側に折り返し、配線基板166の裏面168側を終端抵抗形成領域174に向けて延びるデータ線、アドレス信号線、コントロール信号線及びクロック信号線をなす等長平行配線とされた送信デジタル信号を相補信号化してなる相補送信デジタル信号を伝送する信号配線ペアからなる信号配線群である。

また、176はCPU搭載領域173の辺173Bの近傍から配線基板166の表面167側を配線基板166の辺166Bに向けて延び、スルーホール群170を介して配線基板166の裏面168側に折り返し、配線基板166の裏面168側を終端抵抗形成領域174に向けて延びるデータ線、アドレス信号線、コントロール信号線及びクロック信号線をなす等長平行配線とされた送信デジタル信号を相補信号化してなる相補送信デジタル信号を伝送する信号配線ペアからなる信号配線群である。

また、177はCPU搭載領域173の辺173Cの近傍から配線基板166の表面167側を配線基板166の辺166Cに向けて延び、スルーホール群171を介して配線基板166の裏面168側に折り返し、配線基板166の裏面168側を終端抵抗形成領域174に向けて延びるデータ線、アドレス信号線、コントロール信号線及びクロック信号線をなす等長平行配線とされた送信デジタル信号を相補信号化してなる相補送信デジタル信号を伝送する信号配線からなる信号配線群である。

また、178はCPU搭載領域173の辺173Dの近傍から配線基板166の表面167側を配線基板166の辺166Dに向けて延び、スルーホール群172を介して配線基板166の裏面168側に折り返し、配線基板166の裏面168側を終端抵抗形成領域174に向けて延びるデータ線、アドレス信号線、コントロール信号線及びクロック信号線をなす等長平行配線とされた送信デジタル信号を相補信号化してなる相補送信デジタル信号を伝送する信号配線からなる信号配線群である。

また、図3において、179、180はCPU用の電源・接地配線ペア、181〜184、189〜192、197〜200、205〜208はメモリ用の電源・接地配線ペア、図4において、185〜188、193〜196、201〜204、209〜212はメモリ用の電源・接地配線ペア、213、214は入出力チップ用の電源・接地配線ペアである。

また、図1において、216は配線基板166の表面167のCPU搭載領域173に搭載されたCPUであり、CPU216は、データ入出力端子、アドレス出力端子、コントロール信号出力端子、クロック入力端子、クロック出力端子を信号配線群175〜178の信号配線に接続され、電源電圧入力端子及び接地電圧入力端子を電源・接地配線ペア179、180を構成する電源配線及び、接地配線に接続されている。

また、図1及び図2において、217〜224、225〜232、233〜240、241〜248は配線基板166の表面167及び裏面168に搭載された同一品種のメモリである。

ここに、メモリ217〜224は、共に、データ入出力端子、アドレス入力端子、コントロール信号入力端子、クロック入力端子を信号配線群175の信号配線に接続されている。また、これらメモリ217〜224は、それぞれ、その電源電圧入力端子及び接地電圧入力端子を電源・接地配線ペア181〜188を構成する電源配線及び接地配線に接続されている。

また、メモリ225〜232は、共に、データ入出力端子、アドレス入力端子、コントロール信号入力端子、クロック入力端子を信号配線群176の信号配線に接続されている。また、これらメモリ225〜232は、それぞれ、その電源電圧入力端子及び接地電圧入力端子を電源・接地配線ペア189〜196を構成する電源配線及び接地配線に接続されている。

また、メモリ233〜240は、共に、データ入出力端子、アドレス入力端子、コントロール信号入力端子、クロック入力端子を信号配線群177の信号配線に接続されている。また、これらメモリ233〜240は、それぞれ、その電源電圧入力端子及び接地電圧入力端子を電源・接地配線ペア197〜204を構成する電源配線及び接地配線に接続されている。

また、メモリ241〜248は、共に、データ入出力端子、アドレス入力端子、コントロール信号入力端子、クロック入力端子を信号配線群178の信号配線に接続されている。また、これらメモリ241〜248は、それぞれ、その電源電圧入力端子及び接地電圧入力端子を電源・接地配線ペア205〜212を構成する電源配線及び接地配線に接続されている。

また、メモリ217、225、233、241は、それぞれ、信号配線群175、176、177、178のCPU216の信号端子接続端から同一距離に接続されている。

また、メモリ218、226、234、242は、それぞれ、信号配線群175、176、177、178のCPU216の信号端子接続端から同一距離に接続されている。

また、メモリ219、227、235、243は、それぞれ、信号配線群175、176、177、178のCPU216の信号端子接続端から同一距離に接続されている。

また、メモリ220、228、236、244は、それぞれ、信号配線群175、176、177、178のCPU216の信号端子接続端から同一距離に接続されている。

また、メモリ221、229、237、245は、それぞれ、信号配線群175、176、177、178のCPU216の信号端子接続端から同一距離に接続されている。

また、メモリ222、230、238、246は、それぞれ、信号配線群175、176、177、178のCPU216の信号端子接続端から同一距離に接続されている。

また、メモリ223、231、239、247は、それぞれ、信号配線群175、176、177、178のCPU216の信号端子接続端から同一距離に接続されている。

また、メモリ224、232、240、248は、それぞれ、信号配線群175、176、177、178のCPU216の信号端子接続端から同一距離に接続されている。

また、図5は終端抵抗形成領域174を示す概略的平面図であり、図5中、250は信号配線群175の信号配線ペアを終端する終端抵抗群、251は信号配線群176の信号配線ペアを終端する終端抵抗群、252は信号配線群177の信号配線ペアを終端する終端抵抗群、253は信号配線群178の信号配線ペアを終端する終端抵抗群である。

また、図2において、255は入出力チップ、256はクロック・ジェネレータ、257はPCIポート、258は画像音声ポート、259は信号圧縮伸長チップ、260は通信ポートである。

このように構成された本発明の第1実施形態によれば、CPU216と、CPU216によりアクセスされる32個のメモリ217〜248とを等長平行配線とされた信号配線で接続する必要がある電子装置を構成する必要がある場合において、信号配線を最も短く形成することができる。

また、信号配線群175、176、177、178を構成する信号配線は、相補送信デジタル信号を伝送する等長平行配線とされた信号配線ペアを構成しているので、信号配線を電磁界がほぼ閉じた伝送線路として機能させることができ、CPU216と、CPU216にアクセスされるメモリとの間の信号伝送に必要な相補信号エネルギーの伝送の高速化を図ることができる。

また、CPU216及びメモリ217〜248に電源・接地配線ペア179、180、181〜212のそれぞれは、電源配線及び接地配線を等長平行配線とされているので、CPU216及びメモリ217〜248に供給すべき相補信号エネルギーに対して電磁界がほぼ閉じた伝送線路として機能させることができ、CPU216及びメモリ217〜248に対する相補信号エネルギーの供給の高速化を図ることができる。

したがって、本発明の第1実施形態によれば、CPU216と、CPU216によりアクセスされる32個のメモリ217〜248とを等長平行配線とされた信号配線で接続する必要がある電子装置を1枚の配線基板166を使用して構成する場合において、CPU216とCPU216にアクセスされるメモリとの間の信号伝送の高速化を図ることができる。

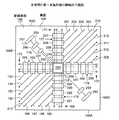

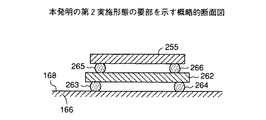

(第2実施形態・・図6)

図6は本発明の第2実施形態の要部を示す概略的断面図であり、本発明の第2実施形態は、配線基板166の裏面168に終端抵抗形成領域174を設けずに、終端抵抗を形成してなる終端抵抗チップ262を配線基板166の裏面168の中央部に搭載し、この終端抵抗チップ262上に入出力チップ255を搭載するようにし、その他については、図1及び図2に示す本発明の第1実施形態と同様に構成したものである。なお、図6中、263〜266は半田バンプである。

本発明の第2実施形態によれば、図1及び図2に示す本発明の第1実施形態と同様に、CPU216と、CPU216によりアクセスされる32個のメモリ217〜248とを等長平行配線とされた信号配線で接続する必要がある電子装置を1枚の配線基板166を使用して構成する場合において、CPU216とCPU216にアクセスされるメモリとの間の信号伝送の高速化を図ることができる。

(第3実施形態・・図7、図8)

図7及び図8はそれぞれ本発明の第3実施形態の概略的平面図及び概略的下面図であり、本発明の第3実施形態は、電源・接地配線ペアの構成を本発明の第1実施形態と異なる構成とし、その他については、本発明の第1実施形態と同様に構成したものである。

本発明の第3実施形態においては、配線基板166の表面167側に設けられる電源・接地配線ペア179、181〜184、189〜192は、電源・接地配線ペア268から分岐するように構成され、電源・接地配線ペア180、197〜200、205〜208は、電源・接地配線ペア269から分岐するように構成されている。

これら電源・接地配線ペア268、179、181〜184、189〜192及び電源・接地配線ペア269、180、197〜200、205〜208は、スタック配線構造とされている。

また、配線基板166の裏面168側に設けられる電源・接地配線ペア213、185〜188、193〜196は、電源・接地配線ペア270から分岐するように構成され、電源・接地配線ペア214、201〜204、209〜212は、電源・接地配線ペア271から分岐するように構成されている。

これら電源・接地配線ペア270、213、185〜188、193〜196及び電源・接地配線ペア271、214、201〜204、209〜212は、スタック配線構造とされている。

なお、これら電源・接地配線ペア268、179、181〜184、189〜192、電源・接地配線ペア269、180、197〜200、205〜208、電源・接地配線ペア270、213、185〜188、193〜196及び電源・接地配線ペア271、214、201〜204、209〜212は、それぞれ、分岐点において特性インピーダンスが整合するように構成されている。

本発明の第3実施形態によれば、CPU216と、CPU216によりアクセスされる32個のメモリ217〜248とを等長平行配線とされた信号配線で接続する必要がある電子装置を1枚の配線基板166を使用して構成する場合において、CPU216とCPU216にアクセスされるメモリとの間の信号伝送の高速化を図ることができる。

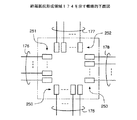

(第4実施形態・・図9)

図9は本発明の第4実施形態の概略的断面図であり、図9中、273、274は配線基板であり、配線基板273は、配線基板274との対向面275を素子搭載面、配線基板274は、配線基板273との対向面276を素子搭載面とされている。

本発明の第4実施形態においては、配線基板273の素子搭載面275側は、図1に示す本発明の第1実施形態の配線基板166の表面167側と同様の構成とされ、配線基板274の素子搭載面276は、図2に示す本発明の第1実施形態の配線基板166の裏面168側と同様に構成されている。

即ち、配線基板273の素子搭載面275には、図1に示す本発明の第1実施形態の配線基板166の表面167側に形成されている信号配線群175、176、177、178及び電源・接地配線ペア179、180、181〜184、189〜192、197〜200、205〜208が本発明の第1実施形態の場合と同様に形成されている。

また、配線基板273の素子搭載面275には、図1に示す本発明の第1実施形態の配線基板166の表面167側に搭載されているCPU216及びメモリ217〜220、225〜228、233〜236、241〜244が本発明の第1実施形態の場合と同様に搭載されている。

また、配線基板274の素子搭載面276には、図2に示す第1実施形態の配線基板166の裏面168側に形成されている信号配線群175、176、177、178及び電源・接地配線ペア185〜188、193〜196、201〜204、209〜212、213、214が本発明の第1実施形態の場合と同様に形成されている。

また、配線基板274の素子搭載面276には、図2に示す第1実施形態の配線基板166の裏面168側に搭載されているメモリ221〜224、229〜232、237〜240、245〜248及び入出力チップ255が本発明の第1実施形態の場合と同様に搭載されている。

そして、配線基板273と配線基板274とは、素子搭載面275と素子搭載面276とを対向させて半田バンプにより接続されており、配線基板274の周辺部には、外部との接続を図る電極が形成されている。なお、277、278は半田バンプの一部を示している。

本発明の第4実施形態によれば、CPU216と、CPU216によりアクセスされる32個のメモリ217〜248とを等長平行配線とされた信号配線で接続する必要がある電子装置を1対の配線基板273、274を使用して構成する場合において、CPU216とCPU216にアクセスされるメモリとの間の信号伝送の高速化を図ることができる。

なお、配線基板273の素子搭載面275側を図7に示す本発明の第3実施形態の配線基板166の表面167側と同様に構成し、配線基板274の素子搭載面276を図8に示す本発明の第3実施形態の配線基板166側の裏面168側と同様に構成しても良い。

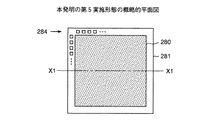

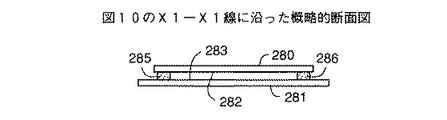

(第5実施形態・・図10、図11)

図10は本発明の第5実施形態の概略的平面図、図11は図10のX1−X1線に沿った概略的断面図である。図10中、280、281は半導体基板であり、半導体基板280は、半導体基板281との対向面282を素子形成面、半導体基板281は、半導体基板280との対向面283を素子形成面とされている。

本発明の第5実施形態においては、半導体基板280の素子形成面282側は、図1に示す本発明の第1実施形態の配線基板166の表面167側と同様の構成がウエハプロセスで形成され、半導体基板281の素子形成面283は、図2に示す本発明の第1実施形態の配線基板166の裏面168側と同様の構成がウエハプロセスで形成されている。

即ち、半導体基板280の素子形成面282には、図1に示す第1実施形態の配線基板166の表面167側に搭載されているCPU216及びメモリ217〜220、225〜228、233〜236、241〜244が本発明の第1実施形態の場合と同様の配置で形成されている。

また、半導体基板280の素子形成面282には、図1に示す第1実施形態の配線基板166の表面167側に形成されている信号配線群175、176、177、178及び電源・接地配線ペア179、180、181〜184、189〜192、197〜200、205〜208が本発明の第1実施形態の場合と同様の配置で形成されている。

また、半導体基板281の素子形成面283には、図2に示す第1実施形態の配線基板166の裏面168側に搭載されているメモリ221〜224、229〜232、237〜240、245〜248及び入出力チップ255が本発明の第1実施形態の場合と同様の配置で形成されている。

また、半導体基板281の素子形成面283には、図2に示す第1実施形態の配線基板166の裏面168側に形成されている信号配線群175、176、177、178及び電源・接地配線ペア185〜188、193〜196、201〜204、209〜212、213、214が本発明の第1実施形態の場合と同様の配置で形成されている。

そして、半導体基板280と半導体基板281とは、素子形成面282と素子形成面283とを対向させて半田バンプにより接続されており、半導体基板281の周辺部には、外部との接続を図る電極群284が形成されている。なお、285、286は半田バンプの一部を示している。

本発明の第5実施形態によれば、CPU216と、CPU216によりアクセスされる32個のメモリ217〜248とを等長平行配線とされた信号配線で接続する必要がある電子装置を1対の半導体基板280、281を使用して構成する場合において、CPU216とCPU216にアクセスされるメモリとの間の信号伝送の高速化を図ることができる。

なお、半導体基板280の素子形成面282側を図7に示す本発明の第3実施形態の配線基板166の表面167側と同様の構成をウエハプロセスで形成し、半導体基板281の素子形成面283を図8に示す本発明の第3実施形態の配線基板166の裏面168側と同様の構成をウエハプロセスで形成するようにしても良い。

(第1参考例・・図12〜図14)

図12は本発明の第1参考例の概念図であり、本発明の第1参考例は、1対の信号配線ペアを有し、この1対の信号配線ペアに分岐が存在せず、かつ、1方向の信号伝送を行う伝送回路が構成されている場合を例にするものである。

図12中、20は配線基板、21は配線基板20に形成されたカップリング係数を大とする等長平行配線とされた信号配線22、23からなる信号配線ペアである。

また、24は配線基板20に形成された正の電源電圧VDDを入力するための電源電圧入力端子、25は配線基板20に形成された接地電圧VSSを入力するための接地電圧入力端子である。

また、26は配線基板20に形成されたカップリング係数を大とする等長平行配線からなる電源配線27及び接地配線28からなる電源・接地配線ペアであり、この電源・接地配線ペア26は、その特性インピーダンスを信号配線ペア21の特性インピーダンスと同一とされている。

また、29は配線基板20に搭載された集積回路チップ(以下、ICチップという)であり、このICチップ29は、その電源電圧入力端子29Aを電源配線27に接続され、その接地電圧入力端子29Bを接地配線28に接続され、その信号出力端子29C、29Dをそれぞれ信号配線22、23の一端に接続されている。

また、ICチップ29において、30は内部回路(図示せず)から与えられる送信デジタル信号TSを相補送信デジタル信号CS、/CSに相補信号化し、これら相補送信デジタル信号CS、/CSを信号出力端子29C、29Dを介して信号配線22、23に出力するCMOS差動ドライバである。

また、CMOS差動ドライバ30において、31は図48に示すCMOSドライバ5と同一構成のCMOSドライバ、32は図48に示すCMOSインバータ8と同一構成のCMOSインバータである。

また、33は配線基板20に搭載されたICチップであり、ICチップ33は、その信号入力端子33A、33Bをそれぞれ信号配線22、23の他端に接続されている。

また、ICチップ33において、34は信号配線22、23を伝送されてくる相補送信デジタル信号CS、/CSを受信して送信デジタル信号TSに対応する受信デジタル信号RSを内部回路(図示せず)に対して出力するCMOS差動レシーバであり、このCMOS差動レシーバ34は、図48に示すCMOS差動レシーバ4と同一構成とされている。

なお、信号配線ペア21の特性インピーダンスは、20〜100[Ω]の間で自由に設定することができるが、CMOS差動レシーバ34のゲートがCMOSゲート(CMOSドライバ及びCMOSインバータ)であるため、信号配線ペア21を伝送されてきた相補送信デジタル信号CS、/CSが反射し、反射された相補送信デジタル信号CS、/CSは、信号配線ペア21を逆走し、CMOS差動ドライバ30に達してしまう。

そこで、CMOS差動ドライバ30のオン抵抗を信号配線ペア21の特性インピーダンスに整合させ、信号配線ペア21を逆走してくる反射相補送信デジタル信号CS、/CSを吸収するように構成することが好適であり、このように構成する場合には、信号配線ペア21を逆走してくる反射相補送信デジタル信号CS、/CSがCMOS差動ドライバ30側で再度反射することなく、順走相補送信デジタル信号CS、/CSをいかなるタイミングでも乱すことはなくなる。

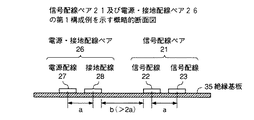

図13は信号配線ペア21及び電源・接地配線ペア26の第1構成例を示す概略的断面図であり、この第1構成例では、これら信号配線ペア21及び電源・接地配線ペア26がコプレーナ配線構造となるように、配線基板20を構成する絶縁基板35の同一面に、信号配線22、23と、電源配線27と、接地配線28とが平行に形成されており、信号配線ペア21及び電源・接地配線ペア26の周辺には、ペア配線構造ではない、いわゆるベタの電源配線や接地配線は形成されていない。

ここに、信号配線22と信号配線23の幅方向の中心間距離、及び、電源配線27と接地配線28の幅方向の中心間距離を共にaとし、信号配線ペア21と電源・接地配線ペア26との間隔をbとすると、b>2aとする場合には、信号配線22と信号配線23との間のカップリング係数、及び、電源配線27と接地配線28との間のカップリング係数を共に1に近くすることができ、信号配線ペア21及び電源・接地配線ペア26を電磁界がほぼ閉じた伝送線路とすることができる。

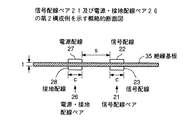

図14は信号配線ペア21及び電源・接地配線ペア26の第2構成例を示す概略的断面図であり、この第2構成例では、これら信号配線ペア21及び電源・接地配線ペア26がスタック配線構造となるように、絶縁基板35を挟んで、信号配線22と信号配線23とが対向し、電源配線27と接地配線28とが対向するように形成されており、信号配線ペア21及び電源・接地配線ペア26の周辺には、ペア配線構造ではない、いわゆるベタの電源配線、接地配線は形成されていない。

ここに、絶縁基板35の厚みをt、信号配線22、23、電源配線27及び接地配線28の配線幅を共にc、隣接する配線ペアとの間隔をsとすると、s/(t+c)>2とする場合には、信号配線22と信号配線23との間のカップリング係数、及び、電源配線27と接地配線28との間のカップリング係数を共に1に近くすることができ、信号配線ペア21及び電源・接地配線ペア26を電磁界がほぼ閉じた伝送線路とすることができる。

なお、電源・接地配線ぺア26は、信号配線ペア21と等長、かつ、平行である必要はなく、自由な方向に形成することができる。

このように構成された本発明の第1参考例においては、送信デジタル信号TSがLレベルからHレベルに遷移すると、CMOS差動レシーバ34の正相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがCMOSドライバ31から信号配線22に供給され、信号配線22上をCMOS差動レシーバ34の正相入力端子に向かって伝送されると共に、CMOS差動レシーバ34の逆相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがCMOSインバータ32から信号配線23に供給され、信号配線23上をCMOS差動レシーバ34の逆相入力端子に向かって伝送される。

これに対して、送信デジタル信号TSがHレベルからLレベルに遷移すると、CMOS差動レシーバ34の正相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがCMOSドライバ31から信号配線22に供給され、信号配線22上をCMOS差動レシーバ34の正相入力端子に向かって伝送されると共に、CMOS差動レシーバ34の逆相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがCMOSインバータ32から信号配線23に供給され、信号配線23上をCMOS差動レシーバ34の逆相入力端子に向かって伝送される。

このように、本発明の第1参考例においては、送信デジタル信号TSが遷移すると、相補信号エネルギーが信号配線22、23上をCMOS差動ドライバ30からCMOS差動レシーバ34に向かって伝送されるが、信号配線22、23は、カップリング係数を大とする等長平行配線からなるペア配線構造とされているので、信号配線22、23を電磁界がほぼ閉じた伝送線路とし、信号配線22、23上を伝送される相補信号エネルギーの損失を小さくしてTEM伝送に近いモードで伝送することができる。

また、電源配線27及び接地配線28も、カップリング係数を大とする等長平行配線からなるペア配線構造とされているので、電源・接地配線ペア26を電磁界がほぼ閉じた伝送線路とし、たとえ、電源・接地配線ペア26が長い場合であっても、相補送信デジタル信号CS、/CSをCMOS差動ドライバ30からCMOS差動レシーバ34に伝送するに必要な電源電圧入力端子24及び接地電圧入力端子25からCMOS差動ドライバ30への相補信号エネルギーの伝送を相補信号エネルギーの損失を小さくしてTEM伝送に近いモードで行うことができる。

しかも、電源・接地配線ペア26の特性インピーダンスは、信号配線ペア21の特性インピーダンスと同一とされ、電源・接地配線ペア26は、特性インピーダンス上、信号配線ペア21と整合するように構成されているので、信号配線ペア21で消費される相補信号エネルギーと、電源電圧入力端子24及び接地電圧入力端子25からCMOS差動ドライバ30に供給される相補信号エネルギーが整合し、その損失を小さくすることができる。

したがって、本発明の第1参考例によれば、相補送信デジタル信号CS、/CSの波形の変形が実質的になくなり、CMOS差動ドライバ30からCMOS差動レシーバ34への信号配線ペア21を介しての相補送信デジタル信号CS、/CSの光の速度に近い速度での伝送を行うことができる。

なお、ICチップ29内のCMOS差動ドライバ30に電源電圧及び接地電圧を供給する電源配線及び接地配線も等長平行配線からなるペア配線構造とすることが好適であり、このようにする場合には、CMOS差動ドライバ30からCMOS差動レシーバ34への信号配線ペア21を介しての相補送信デジタル信号CS、/CSの伝送の更なる高速化を図ることができる。

また、本発明の第1参考例によれば、ICチップ33は、レシーバとして差動レシーバ34を設けているが、差動レシーバ34は、同相ノイズ及び信号配線22、23のどちらか一方に乗ったノイズに対しては動作せず、相補送信デジタル信号CS、/CSのみに感知するので、伝送系をノイズマージンが大きい伝送系とすることができる。したがって、信号電圧を低く下げることができる。例えば、現行の回路で最も低い振幅は、0.8V〜1.5Vあたりであるが、0.1V程度まで下げることが可能である。これにより、立ち上がり及び立ち下がり勾配を低くでき、高周波信号の伝送を図ることができると共に、省電力を達成することができる。

(第2参考例・・図15〜図17)

図15は本発明の第2参考例の概念図であり、本発明の第2参考例は、2対の信号配線ペアを有し、これら2対の信号配線ペアに分岐が存在せず、かつ、1方向の信号伝送を行う伝送回路が構成されている場合を例にするものである。

図15中、36は配線基板、37は配線基板36に形成されたカップリング係数を大とする等長平行配線とされた信号配線38、39からなる信号配線ペア、40は配線基板36に形成されたカップリング係数を大とする等長平行配線とされた信号配線41、42からなる信号配線ペアである。なお、信号配線ペア37、40は、カップリング係数及び特性インピーダンスをそれぞれ同一とされ、等長、かつ、平行とされている。

また、43は配線基板36に形成された正の電源電圧VDDを入力するための電源電圧入力端子、44は配線基板36に形成された接地電圧VSSを入力するための接地電圧入力端子、45は配線基板36に形成されたカップリング係数を大とする等長平行配線とされた電源配線46及び接地配線47からなる電源・接地配線ペアである。

また、信号配線ペア37、40の特性インピーダンスをZ0、電源・接地配線ペア45の特性インピーダンスをZ1とすると、Z1=Z0/2(但し、2は信号配線ペアの数)とされている。なお、Z1=Z0/2とできない場合には、可能な限りこれに近い値とすることが好適である。

また、48は配線基板36に搭載されたICチップであり、ICチップ48は、その電源電圧入力端子48Aを電源配線46に接続され、その接地電圧入力端子48Bを接地配線47に接続され、その信号出力端子48C、48D、48E、48Fをそれぞれ信号配線38、39、41、42の一端に接続されている。

また、ICチップ48において、49は内部回路(図示せず)から与えられる送信デジタル信号TS1を相補送信デジタル信号CS1、/CS1に相補信号化し、これら相補送信デジタル信号CS1、/CS1を信号出力端子48C、48Dを介して信号配線38、39に出力するCMOS差動ドライバであり、このCMOS差動ドライバ49は、図48に示すCMOS差動ドライバ3と同一構成とされている。

また、50は内部回路から与えられる送信デジタル信号TS2を相補送信デジタル信号CS2、/CS2に相補信号化し、これら相補送信デジタル信号CS2、/CS2を信号出力端子48E、48Fを介して信号配線41、42に出力するCMOS差動ドライバであり、このCMOS差動ドライバ50は、図48に示すCMOS差動ドライバ3と同一構成とされている。

また、51は配線基板36に搭載されたICチップであり、ICチップ51は、その信号入力端子51A、51B、51C、51Dをそれぞれ信号配線38、39、41、42の他端に接続されている。

また、ICチップ51において、52は信号配線38、39を伝送されてくる相補送信デジタル信号CS1、/CS1を受信して送信デジタル信号TS1に対応する受信デジタル信号RS1を内部回路(図示せず)に対して出力するCMOS差動レシーバであり、このCMOS差動レシーバ52は、図48に示すCMOS差動レシーバ4と同一構成とされている。

また、53は信号配線41、42を伝送されてくる相補送信デジタル信号CS2、/CS2を受信して送信デジタル信号TS2に対応する受信デジタル信号RS2を内部回路に対して出力するCMOS差動レシーバであり、このCMOS差動レシーバ53は、図48に示すCMOS差動レシーバ4と同一構成とされている。

なお、信号配線ペア37、40の特性インピーダンスは、20〜100[Ω]の間で自由に設定することができるが、CMOS差動レシーバ52、53のゲートがCMOSゲート(CMOSドライバ及びCMOSインバータ)であるため、信号配線ペア37、40をそれぞれ伝送されてきた相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2が反射し、反射された相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2は、それぞれ、信号配線ペア37、40を逆走し、CMOS差動ドライバ49、50に達してしまう。

そこで、CMOS差動ドライバ49、50のオン抵抗をそれぞれ信号配線ペア37、40の特性インピーダンスに整合させ、信号配線ペア37、40をそれぞれ逆走してくる反射相補送信デジタル信号CS1、/CS1及び反射相補送信デジタル信号CS2、/CS2を吸収するように構成することが好適であり、このように構成する場合には、信号配線ペア37、40をそれぞれ逆走してくる反射相補送信デジタル信号CS1、/CS1及び反射相補送信デジタル信号CS2、/CS2がCMOS差動ドライバ49、50側で再度反射することなく、順走相補送信デジタル信号CS1、/CS1及び順走相補送信デジタル信号CS2、/CS2をいかなるタイミングでも乱すことはなくなる。

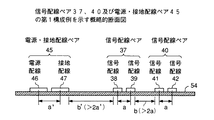

図16は信号配線ペア37、40及び電源・接地配線ペア45の第1構成例を示す概略的断面図であり、この第1構成例では、これら信号配線ペア37、40及び電源・接地配線ペア45がコプレーナ配線構造となるように、配線基板36を構成する絶縁基板54の同一面に、信号配線38、39、41、42と、電源配線46と、接地配線47とが平行に形成されており、信号配線ペア37、40及び電源・接地配線ペア45の周辺には、ペア配線構造ではない、いわゆるベタの電源配線や接地配線は形成されていない。

ここに、信号配線38と信号配線39の幅方向の中心間距離及び信号配線41と信号配線42の幅方向の中心間距離をa、電源配線46と接地配線47の幅方向の中心間距離をa’、信号配線ペア37と信号配線ペア40との間隔をb、信号配線ペア37と電源・接地配線ペア45との間隔をb’とすると、b>2a、b’>2a’とする場合には、信号配線38と信号配線39との間のカップリング係数、信号配線41と信号配線42との間のカップリング係数、及び、電源配線46と接地配線47との間のカップリング係数を共に1に近くすることができ、信号配線ペア37、40及び電源・接地配線ペア45を電磁界がほぼ閉じた伝送線路とすることができる。

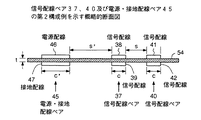

図17は信号配線ペア37、40及び電源・接地配線ペア45の第2構成例を示す概略的断面図であり、この第2構成例では、これら信号配線ペア37、40及び電源・接地配線ペア45がスタック配線構造となるように、絶縁基板54を挟んで、信号配線38と信号配線39とが対向し、信号配線41と信号配線42とが対向し、電源配線46と接地配線47とが対向するように形成されており、信号配線ペア37、40及び電源・接地配線ペア45の周辺には、ペア配線構造ではない、いわゆるベタの電源配線、接地配線は形成されていない。

ここに、絶縁基板54の厚みをt、信号配線38、39、41、42の配線幅をc、電源配線46及び接地配線47の配線幅をc’、信号配線ペア37と信号配線ペア38との間隔をs、信号配線ペア37と電源・接地配線ペア45との間隔をs’とすると、s/(t+c)>2、s’/(t+c’)>2とする場合には、信号配線38と信号配線39との間のカップリング係数、信号配線41と信号配線42との間のカップリング係数、及び、電源配線46と接地配線47との間のカップリング係数をそれぞれ1に近くすることができ、信号配線ペア37、40及び電源・接地配線ペア45を電磁界がほぼ閉じた伝送線路とすることができる。

なお、電源・接地配線ぺア45は、信号配線ペア37、40と等長、かつ、平行である必要はなく、自由な方向に形成することができる。

このように構成された本発明の第2参考例においては、送信デジタル信号TS1がLレベルからHレベルに遷移すると、CMOS差動レシーバ52の正相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがCMOS差動ドライバ49の正相出力端子から信号配線38に供給され、信号配線38上をCMOS差動レシーバ52の正相入力端子に向かって伝送されると共に、CMOS差動レシーバ52の逆相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがCMOS差動ドライバ49の逆相出力端子から信号配線39に供給され、信号配線39上をCMOS差動レシーバ52の逆相入力端子に向かって伝送される。

また、送信デジタル信号TS2がLレベルからHレベルに遷移すると、CMOS差動レシーバ53の正相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがCMOS差動ドライバ50の正相出力端子から信号配線41に供給され、信号配線41上をCMOS差動レシーバ53の正相入力端子に向かって伝送されると共に、CMOS差動レシーバ53の逆相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがCMOS差動ドライバ50の逆相出力端子から信号配線42に供給され、信号配線42上をCMOS差動レシーバ53の逆相入力端子に向かって伝送される。

これに対して、送信デジタル信号TS1がHレベルからLレベルに遷移すると、CMOS差動レシーバ52の正相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがCMOS差動ドライバ49の正相出力端子から信号配線38に供給され、信号配線38上をCMOS差動レシーバ52の正相入力端子に向かって伝送されると共に、CMOS差動レシーバ52の逆相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがCMOS差動ドライバ49の逆相出力端子から信号配線39に供給され、信号配線39上をCMOS差動レシーバ52の逆相入力端子に向かって伝送される。

また、送信デジタル信号TS2がHレベルからLレベルに遷移すると、CMOS差動レシーバ53の正相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがCMOS差動ドライバ50の正相出力端子から信号配線41に供給され、信号配線41上をCMOS差動レシーバ53の正相入力端子に向かって伝送されると共に、CMOS差動レシーバ53の逆相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがCMOS差動ドライバ50の逆相出力端子から信号配線42に供給され、信号配線42上をCMOS差動レシーバ53の逆相入力端子に向かって伝送される。

このように、本発明の第2参考例においては、送信デジタル信号TS1、TS2が遷移すると、相補信号エネルギーが信号配線38、39及び信号配線41、42上をCMOS差動レシーバ52及びCMOS差動レシーバ53に向かって伝送されるが、信号配線38、39及び信号配線41、42はカップリング係数を大とする等長平行配線からなるペア配線構造とされているので、信号配線38、39及び信号配線41、42を電磁界がほぼ閉じた伝送線路とし、信号配線38、39及び信号配線41、42上を伝送される相補信号エネルギーの損失を小さくしてTEM伝送に近いモードで伝送することができる。

また、電源配線46及び接地配線47も、カップリング係数を大とする等長平行配線からなるペア配線構造とされているので、電源・接地配線ペア45を電磁界がほぼ閉じた伝送線路とし、たとえ、電源・接地配線ペア45が長い場合であっても、相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2をCMOS差動レシーバ52及びCMOS差動レシーバ53に伝送するに必要な電源電圧入力端子43及び接地電圧入力端子44からCMOS差動ドライバ49及びCMOS差動ドライバ50への相補信号エネルギーの伝送をTEM伝送に近いモードで行うことができる。

しかも、本発明の第2参考例においては、信号配線ペア37、40の特性インピーダンスをZ0、電源・接地配線ペア45の特性インピーダンスをZ1とすると、Z1=Z0/2とされ、電源・接地配線ペア45は、特性インピーダンス上、信号配線ペア37、40と整合するように構成されているので、信号配線ペア37、40で消費される相補信号エネルギーと、電源電圧入力端子43及び接地電圧入力端子44から電源・接地配線ペア45を介してCMOS差動ドライバ49、50に供給される相補信号エネルギーが整合し、その損失を小さくすることができる。

したがって、本発明の第2参考例によれば、相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の波形変形が実質的になくなり、CMOS差動ドライバ49及びCMOS差動ドライバ50からそれぞれCMOS差動レシーバ52及びCMOS差動レシーバ53への信号配線ペア37及び信号配線ペア40を介しての相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の光の速度に近い速度での伝送を行うことができる。

なお、ICチップ48内のCMOS差動ドライバ49、50に電源電圧及び接地電圧を供給する電源配線及び接地配線も等長平行配線からなるペア配線構造とすることが好適であり、このように構成する場合には、CMOS差動ドライバ49、50からCMOS差動レシーバ52、53への信号配線ペア37、40を介しての相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の伝送の更なる高速化を図ることができる。

また、本発明の第2参考例によれば、ICチップ51は、レシーバとして差動レシーバ52、53を設けているが、差動レシーバ52は、同相ノイズ及び信号配線38、39のどちらか一方に乗ったノイズに対しては動作せず、相補送信デジタル信号CS1、/CS1のみに感知し、差動レシーバ53は、同相ノイズ及び信号配線41、42のどちらか一方に乗ったノイズに対しては動作せず、相補送信デジタル信号CS2、/CS2のみに感知するので、伝送系をノイズマージンが大きい伝送系とすることができる。したがって、信号電圧を低く下げることができる。例えば、現行の回路で最も低い振幅は、0.8V〜1.5Vあたりであるが、0.1V程度まで下げることが可能である。これにより、立ち上がり及び立ち下がり勾配を低くでき、高周波信号の伝送を図ることができると共に、省電力を達成することができる。

(第3参考例・・図18)

図18は本発明の第3参考例の概念図であり、本発明の第3参考例は、1対の信号配線ペアを有し、この1対の信号配線ペアに分岐が存在し、かつ、1方向の信号伝送を行う伝送回路が構成されている場合を例にするものである。

図18中、55は配線基板、56は配線基板55に形成されたカップリング係数を大とする等長平行配線とされた信号配線57、58からなる信号配線ペア、59は信号配線57、58を終端する終端抵抗である。

また、60は配線基板55に形成された正の電源電圧VDDを入力するための電源電圧入力端子、61は配線基板55に形成された接地電圧VSSを入力するための接地電圧入力端子である。

また、62は配線基板55に形成されたカップリング係数を大とする等長平行配線とされた電源配線63及び接地配線64からなる電源・接地配線ペアであり、電源・接地配線ペア62の特性インピーダンスは、信号配線ペア56の特性インピーダンスと同一とされている。

なお、信号配線ペア56及び電源・接地配線ペア62は、図13に示す場合と同様にコプレーナ配線構造としても良いし、図14に示す場合と同様にスタック配線構造としても良い。

また、65は配線基板55に搭載されたICチップであり、ICチップ65は、その電源電圧入力端子65Aを電源配線63に接続され、その接地電圧入力端子65Bを接地配線64に接続され、その信号出力端子65C、65Dをそれぞれ信号配線57、58の一端に接続されている。

また、ICチップ65において、66は内部回路(図示せず)から与えられる送信デジタル信号TSを相補送信デジタル信号CS、/CSに相補信号化し、これら相補送信デジタル信号CS、/CSを信号出力端子65C、65Dを介して信号配線57、58に出力するCMOS差動ドライバであり、このCMOS差動ドライバ66は、図48に示すCMOS差動ドライバ3と同一構成とされている。

また、67−1、67−mは配線基板55に搭載された同種又は異種のICチップであり、これらICチップ67−1、67−mは、その信号入力端子67−1A、67−mAを信号配線57に接続され、その信号入力端子67−1B、67−mBを信号配線58に接続されている。

また、ICチップ67−1、67−mにおいて、68−1、68−mは信号配線57、58を伝送されてくる相補送信デジタル信号CS、/CSを受信する差動レシーバをなすオペアンプである。

なお、オペアンプ68−1は、その正相入力端子を信号入力端子67−1Aに接続され、その逆相入力端子を信号入力端子67−1Bに接続され、オペアンプ68−mは、その正相入力端子を信号入力端子67−mAに接続され、その逆相入力端子を信号入力端子67−mBに接続されている。

このように構成された本発明の第3参考例においては、送信デジタル信号TSがLレベルからHレベルに遷移すると、オペアンプ68−1、68−mの正相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがCMOS差動ドライバ66の正相出力端子から信号配線57に供給され、信号配線57上をオペアンプ68−1、68−mの正相入力端子に向かって伝送されると共に、オペアンプ68−1、68−mの逆相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがCMOS差動ドライバ66の逆相出力端子から信号配線58に供給され、信号配線58上をオペアンプ68−1、68−mの逆相入力端子に向かって伝送される。

これに対して、送信デジタル信号TSがHレベルからLレベルに遷移すると、オペアンプ68−1、68−mの正相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがCMOS差動ドライバ66の正相出力端子から信号配線57に供給され、信号配線57上をオペアンプ68−1、68−mの正相入力端子に向かって伝送されると共に、オペアンプ68−1、68−mの逆相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがCMOS差動ドライバ66の逆相出力端子から信号配線58に供給され、信号配線58上をオペアンプ68−1、68−mの逆相入力端子に向かって伝送される。

なお、オペアンプ68−1、68−mの入力インピーダンスは、通常、信号配線ペア56の特性インピーダンス(20〜100Ω)の1000倍以上のハイインピーダンスとなっているので、信号配線ペア56を伝送されてくる相補信号エネルギーはオペアンプ68−1、68−mでは殆ど吸収されず、そのままのエネルギー状態で終端抵抗59に到達し、ここで全エネルギーが熱となって消費される。したがって、相補信号エネルギーの反射は起こらないため、常に正しい相補送信デジタル信号CS、/CSがオペアンプ68−1、68−mを通過することになる。

このように、本発明の第3参考例においては、送信デジタル信号TSが遷移すると、相補信号エネルギーが信号配線57、58上をオペアンプ68−1、68−mに向かって伝送されるが、信号配線57、58は、カップリング係数を大とする等長平行配線からなるペア配線構造とされているので、信号配線57、58を電磁界がほぼ閉じた伝送線路とし、信号配線57、58上を伝送される相補信号エネルギーの損失を小さくしてTEM伝送に近いモードで伝送することができる。

また、電源配線63及び接地配線64も、カップリング係数を大とする等長平行配線からなるペア配線構造とされているので、電源・接地配線ペア62を電磁界がほぼ閉じた伝送線路とし、たとえ、電源・接地配線ペア62が長い場合であっても、相補送信デジタル信号CS、/CSをオペアンプ68−1、68−mに伝送するに必要な電源電圧入力端子60及び接地電圧入力端子61からCMOS差動ドライバ66への相補信号エネルギーの伝送をTEM伝送に近いモードで行うことができる。

しかも、電源・接地配線ペア62の特性インピーダンスは、信号配線ペア56の特性インピーダンスと同一とされ、電源・接地配線ペア62は、特性インピーダンス上、信号配線ペア56と整合するように構成されているので、この点からも、電源電圧入力端子60及び接地電圧入力端子61から電源・接地配線ペア62を介してCMOS差動ドライバ66に供給される相補信号エネルギーの損失を小さくすることができる。

したがって、本発明の第3参考例によれば、相補送信デジタル信号CS、/CSの波形の変形が実質的になくなり、CMOS差動ドライバ66からオペアンプ68−1、68−mへの信号配線ペア56を介しての相補送信デジタル信号CS、/CSの光の速度に近い速度での伝送を行うことができる。

なお、ICチップ65内のCMOS差動ドライバ66に電源電圧及び接地電圧を供給する電源配線及び接地配線も平行配線からなるペア配線構造とすることが好適であり、このように構成する場合には、CMOS差動ドライバ66からオペアンプ68−1、68−mへの信号配線ペア56を介しての相補送信デジタル信号CS、/CSの伝送の更なる高速化を図ることができる。

また、本発明の第3参考例によれば、ICチップ67−1、67−mは、差動レシーバとしてオペアンプ68−1、68−mを設けているが、オペアンプ68−1、68−mは、同相ノイズ及び信号配線57、58のどちらか一方に乗ったノイズに対しては動作せず、相補送信デジタル信号CS、/CSのみに感知するので、伝送系をノイズマージンが大きい伝送系とすることができる。したがって、信号電圧を低く下げることができる。例えば、現行の回路で最も低い振幅は、0.8V〜1.5Vあたりであるが、0.1V程度まで下げることが可能である。これにより、立ち上がり及び立ち下がり勾配を低くでき、高周波信号の伝送を図ることができると共に、省電力を達成することができる。

(第4参考例・・図19〜図21)

図19は本発明の第4参考例の概念図であり、本発明の第4参考例は、2対の信号配線ペアを有し、これら2対の信号配線ペアに分岐が存在し、かつ、1方向の信号伝送を行う伝送回路が構成されている場合を例にするものである。

図19中、70は配線基板、71は配線基板70に形成されたカップリング係数を大とする等長平行配線とされた信号配線72、73からなる信号配線ペア、75は配線基板70に形成されたカップリング係数を大とする等長平行配線とされた信号配線76、77からなる信号配線ペアである。なお、信号配線ペア71、75は、カップリング係数及び特性インピーダンスをそれぞれ同一とされ、等長、かつ、平行とされている。

また、79は配線基板70に形成された正の電源電圧VDDを入力するための電源電圧入力端子、80は配線基板70に形成された接地電圧VSSを入力するための接地電圧入力端子、81は配線基板70に形成されたカップリング係数を大とする等長平行配線とされた電源配線82及び接地配線83からなる電源・接地配線ペアである。

また、信号配線ペア71、75の特性インピーダンスをZ0、電源・接地配線ペア81の特性インピーダンスをZ1とすると、Z1=Z0/2(但し、2は信号配線ペアの数)とされている。なお、Z1=Z0/2とできない場合には、可能な限りこれに近い値とすることが好適である。

また、信号配線ペア71、75及び電源・接地配線ペア81は、図16に示す場合と同様にコプレーナ配線構造としても良いし、図17に示す場合と同様にスタック配線構造としても良い。

また、84は配線基板70に搭載されたICチップであり、ICチップ84は、その電源電圧入力端子84Aを電源配線82に接続され、その接地電圧入力端子84Bを接地配線83に接続され、その信号出力端子84C、84D、84E、84Fをそれぞれ信号配線72、73、76、77に接続されている。

また、ICチップ84において、85は内部回路(図示せず)から与えられる送信デジタル信号TS1を相補送信デジタル信号CS1、/CS1に相補信号化し、これら相補送信デジタル信号CS1、/CS1を信号出力端子84C、84Dを介して信号配線72、73に出力するCMOS差動ドライバであり、このCMOS差動ドライバ85は、図48に示すCMOS差動ドライバ3と同一構成とされている。

また、86は内部回路から与えられる送信デジタル信号TS2を相補送信デジタル信号CS2、/CS2に相補信号化し、これら相補送信デジタル信号CS2、/CS2を信号出力端子84E、84Fを介して信号配線76、77に出力するCMOS差動ドライバであり、このCMOS差動ドライバ86は、図48に示すCMOS差動ドライバ3と同一構成とされている。

また、87−1、87−mは配線基板70に搭載された同種又は異種のICチップであり、これらICチップ87−1、87−mは、その信号入力端子87−1A、87−mAを信号配線72に接続され、その信号入力端子87−1B、87−mBを信号配線73に接続され、その信号入力端子87−1C、87−mCを信号配線76に接続され、その信号入力端子87−1D、87−mDを信号配線77に接続されている。

また、ICチップ87−1、87−mにおいて、88−1、88−mは信号配線72、73を伝送されてくる相補送信デジタル信号CS1、/CS1を受信する差動レシーバをなすオペアンプ、89−1、89−mは信号配線76、77を伝送されてくる相補送信デジタル信号CS2、/CS2を受信する差動レシーバをなすオペアンプである。

なお、オペアンプ88−1は、その正相入力端子を信号入力端子87−1Aに接続され、その逆相入力端子を信号入力端子87−1Bに接続されており、オペアンプ88−mは、その正相入力端子を信号入力端子87−mAに接続され、その逆相入力端子を信号入力端子87−mBに接続されている。

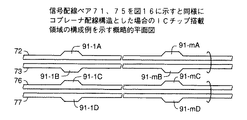

図20は信号配線ペア71、75を図16に示すと同様にコプレーナ配線構造とした場合のICチップ搭載領域の構成例を示す概略的平面図であり、図20中、91−1A、91−1B、91−1C、91−1DはそれぞれICチップ87−1の信号入力端子87−1A、87−1B、87−1C、87−1Dを接続すべきパッド、91−mA、91−mB、91−mC、91−mDはそれぞれICチップ87−mの信号入力端子87−mA、87−mB、87−mC、87−mDを接続すべきパッドである。

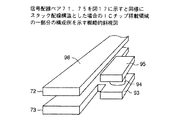

図21は信号配線ペア71、75を図17に示すと同様にスタック配線構造とした場合のICチップ搭載領域の一部分の構成例を示す概略的斜視図であり、配線基板70を構成する絶縁基板は、図示を省略している。

図21中、93は信号配線73から導出されている導電層、94は配線基板70(図示せず)の導電層93の形成領域に設けられたコンタクトホールに形成された導電層、95は絶縁基板の表面に形成され、導電層94に接続された導電層であり、この例では、導電層95がICチップ87−1の信号入力端子87−1Aを接続すべきパッド、信号配線72の導電層95に隣接する部分96がICチップ87−1の信号入力端子87−1Bを接続すべきパッドとされる。

このように構成された本発明の第4参考例においては、送信デジタル信号TS1がLレベルからHレベルに遷移すると、オペアンプ88−1、88−mの正相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがCMOS差動ドライバ85の正相出力端子から信号配線72に供給され、信号配線72上をオペアンプ88−1、88−mの正相入力端子に向かって伝送されると共に、オペアンプ88−1、88−mの逆相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがCMOS差動ドライバ85の逆相出力端子から信号配線73に供給され、信号配線73上をオペアンプ88−1、88−mの逆相入力端子に向かって伝送される。

また、送信デジタル信号TS2がLレベルからHレベルに遷移すると、オペアンプ89−1、89−mの正相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがCMOS差動ドライバ86の正相出力端子から信号配線76に供給され、信号配線76上をオペアンプ89−1、89−mの正相入力端子に向かって伝送されると共に、オペアンプ89−1、89−mの逆相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがCMOS差動ドライバ86の逆相出力端子から信号配線77に供給され、信号配線77上をオペアンプ89−1、89−mの逆相入力端子に向かって伝送される。

これに対して、送信デジタル信号TS1がHレベルからLレベルに遷移すると、オペアンプ88−1、88−mの正相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがCMOS差動ドライバ85の正相出力端子から信号配線72に供給され、信号配線72上をオペアンプ88−1、88−mの正相入力端子に向かって伝送されると共に、オペアンプ88−1、88−mの逆相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがCMOS差動ドライバ85の逆相出力端子から信号配線73に供給され、信号配線73上をオペアンプ88−1、88−mの逆相入力端子に向かって伝送される。

また、送信デジタル信号TS2がHレベルからLレベルに遷移すると、オペアンプ89−1、89−mの正相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがCMOS差動ドライバ86の正相出力端子から信号配線76に供給され、信号配線76上をオペアンプ89−1、89−mの正相入力端子に向かって伝送されると共に、オペアンプ89−1、89−mの逆相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがCMOS差動ドライバ86の逆相出力端子から信号配線77に供給され、信号配線77上をオペアンプ89−1、89−mの逆相入力端子に向かって伝送される。

なお、オペアンプ88−1、88−m、89−1、89−mの入力インピーダンスは、通常、信号配線ペア71、75の特性インピーダンス(20〜100Ω)の1000倍以上のハイインピーダンスとなっているので、信号配線ペア71、75を伝送されてくる相補信号エネルギーはオペアンプ88−1、88−m、89−1、89−mでは殆ど吸収されず、そのままのエネルギー状態で終端抵抗74、78に到達し、ここで全エネルギーが熱となって消費される。したがって、相補信号エネルギーの反射は起こらないため、常に正しい相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2がそれぞれオペアンプ88−1、88−m及びオペアンプ89−1、89−mを通過することになる。

このように、本発明の第4参考例においては、送信デジタル信号TS1、TS2が遷移すると、相補信号エネルギーが信号配線72、73及び信号配線76、77上をオペアンプ88−1、88−m及びオペアンプ89−1、89−mに向かって伝送されるが、信号配線72、73及び信号配線76、77は、カップリング係数を大とする等長平行配線からなるペア配線構造とされているので、信号配線72、73及び信号配線76、77を電磁界がほぼ閉じた伝送線路とし、信号配線72、73及び信号配線76、77上を伝送される相補信号エネルギーの損失を小さくしてTEM伝送に近いモードで伝送することができる。

また、電源配線82及び接地配線83も、カップリング係数を大とする等長平行配線からなるペア配線構造とされているので、電源・接地配線ペア81を電磁界がほぼ閉じた伝送線路とし、たとえ、電源・接地配線ペア81が長い場合であっても、相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2をオペアンプ88−1、88−m及びオペアンプ89−1、89−1mに伝送するに必要な電源電圧入力端子79及び接地電圧入力端子80からCMOS差動ドライバ85、86への電源・接地配線ペア81を介しての相補信号エネルギーの伝送をTEM伝送に近いモードで行うことができる。

しかも、本発明の第4参考例においては、信号配線ペア71、75の特性インピーダンスをZ0、電源・接地配線ペア81の特性インピーダンスをZ1とすると、Z1=Z0/2とされ、電源・接地配線ペア81は、特性インピーダンス上、信号配線ペア71、75と整合するように構成されているので、信号配線ペア71、75で消費される相補信号エネルギーと、電源電圧入力端子79及び接地電圧入力端子80からCMOS差動ドライバ85、86に供給される相補信号エネルギーが整合し、その損失を小さくすることができる。

したがって、本発明の第4参考例によれば、相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の波形の変形が実質的になくなり、CMOS差動ドライバ85及びCMOS差動ドライバ86からそれぞれオペアンプ88−1、88−m及びオペアンプ89−1、89−mへの信号配線ペア71及び信号配線ペア75を介しての相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の光の速度に近い速度での伝送を行うことができる。

なお、ICチップ84内のCMOS差動ドライバ85、86に電源電圧及び接地電圧を供給する電源配線及び接地配線も等長平行配線からなるペア配線構造とすることが好適であり、このように構成する場合には、CMOS差動ドライバ85及びCMOS差動ドライバ86からオペアンプ88−1、88−m及びオペアンプ89−1、89−mへの信号配線ペア71及び信号配線ペア75を介しての相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の伝送の更なる高速化を図ることができる。

また、本発明の第4参考例によれば、ICチップ87−1、87−mは、差動レシーバとしてオペアンプ88−1、89−1、88−m、89−mを設けているが、オペアンプ88−1、88−mは、同相ノイズ及び信号配線72、73のどちらか一方に乗ったノイズに対しては動作せず、相補送信デジタル信号CS1、/CS1のみに感知し、オペアンプ89−1、89−mは、同相ノイズ及び信号配線76、77のどちらか一方に乗ったノイズに対しては動作せず、相補送信デジタル信号CS2、/CS2のみに感知するので、伝送系をノイズマージンが大きい伝送系とすることができる。したがって、信号電圧を低く下げることができる。例えば、現行の回路で最も低い振幅は、0.8V〜1.5Vあたりであるが、0.1V程度まで下げることが可能である。これにより、立ち上がり及び立ち下がり勾配を低くでき、高周波信号の伝送を図ることができると共に、省電力を達成することができる。

(第5参考例・・図22〜図24)

図22は本発明の第5参考例の概念図であり、本発明の第5参考例は、1対の信号配線ペアを有し、この1対の信号配線ペアに分岐が存在し、かつ、双方向の信号伝送を行う伝送回路が構成されている場合を例にするものである。

図22中、98は配線基板、99は配線基板98に形成されたカップリング係数を大とする等長平行配線とされた信号配線100、101からなる信号配線ペア、102は信号配線100、101を終端する終端抵抗である。

また、103は配線基板98に形成された正の電源電圧VDDを入力するための電源電圧入力端子、104は配線基板98に形成された接地電圧VSSを入力するための接地電圧入力端子である。

また、105は配線基板98に形成されたカップリング係数を大とする等長平行配線とされた電源配線106及び接地配線107からなる電源・接地配線ペアであり、電源・接地配線ペア105の特性インピーダンスは、信号配線ペア99の特性インピーダンスと同一とされている。

なお、信号配線ペア99及び電源・接地配線ペア105は、図13に示すと同様にコプレーナ配線構造としても良いし、図14に示すと同様にスタック配線構造としても良い。

また、108は配線基板98に搭載されたICチップであり、このICチップ108は、その電源電圧入力端子108Aを電源配線106に接続され、その接地電圧入力端子108Bを接地配線107に接続され、その信号入出力端子108C、108Dをそれぞれ信号配線100、101に接続されている。

また、ICチップ108において、109は内部回路(図示せず)から与えられる送信デジタル信号TSを相補送信デジタル信号CS、/CSに相補信号化し、これら相補送信デジタル信号CS、/CSを信号入出力端子108C、108Dを介して信号配線100、101に出力するスリーステイトCMOS差動ドライバである。

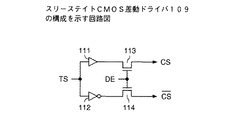

図23はスリーステイトCMOS差動ドライバ109の構成を示す回路図である。図23中、111は図48に示すCMOSドライバ5と同一構成のCMOSドライバ、112は図48に示すCMOSインバータ8と同一構成のCMOSインバータである。

また、113、114はドライバ・イネーブル信号DEによりON、OFFが制御されるnMOSトランジスタであり、ドライバ・イネーブル信号DEは、スリーステイトCMOS差動ドライバ109を活性状態とする場合にはHレベル、スリーステイトCMOS差動ドライバ109を非活性状態とする場合にはLレベルとされる。

また、図22において、116は差動レシーバをなすオペアンプ、117は信号配線100、101に接続されたICチップ108内の信号配線を終端する終端抵抗部であり、オペアンプ116の正相入力端子及び終端抵抗部117の一端117Aは、信号入出力端子108Cに接続され、オペアンプ116の逆相入力端子及び終端抵抗部117の他端117Bは、信号入出力端子108Dに接続されている。

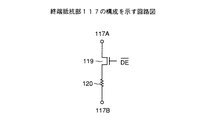

図24は終端抵抗部117の構成を示す回路図である。図24中、119は反転ドライバ・イネーブル信号/DEによりON、OFFが制御されるnMOSトランジスタ、120は終端抵抗である。

また、図22において、122−1、122−mは配線基板98に搭載された同種又は異種のICチップであり、これらICチップ122−1、122−mは、その信号入出力端子122−1A、122−mAを信号配線100に接続され、その信号入出力端子122−1B、122−mBを信号配線101に接続されている。

また、ICチップ122−1において、123−1は差動レシーバをなすオペアンプであり、その正相入力端子を信号入出力端子122−1Aに接続され、その逆相入力端子を信号入出力端子122−1Bに接続されている。

また、124−1はスリーステイトCMOS差動ドライバ109と同様に構成されたスリーステイトCMOS差動ドライバであり、その正相出力端子を信号入出力端子122−1Aに接続され、その逆相出力端子を信号入出力端子122−1Bに接続されている。

また、ICチップ122−mにおいて、123−mは差動レシーバをなすオペアンプであり、その正相入力端子を信号入出力端子122−mAに接続され、その逆相入力端子を信号入出力端子122−mBに接続されている。

また、124−mはスリーステイトCMOS差動ドライバ109と同様に構成されたスリーステイトCMOS差動ドライバであり、その正相出力端子を信号入出力端子122−mAに接続され、その逆相出力端子を信号入出力端子122−mBに接続されている。

このように構成された本発明の第5参考例においては、ICチップ108から発信されるライトイネーブル信号WEが活性状態の下で、送信デジタル信号TSがLレベルからHレベルに遷移すると、オペアンプ123−1、123−mの正相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがスリーステイトCMOS差動ドライバ109の正相出力端子から信号配線100に供給され、信号配線100上をオペアンプ123−1、123−mの正相入力端子に向かって伝送されると共に、オペアンプ123−1、123−mの逆相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがスリーステイトCMOS差動ドライバ109の逆相出力端子から信号配線101に供給され、信号配線101上をオペアンプ123−1、123−mの逆相入力端子に向かって伝送される。

これに対して、送信デジタル信号TSがHレベルからLレベルに遷移すると、オペアンプ123−1、123−mの正相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがスリーステイトCMOS差動ドライバ109の正相出力端子から信号配線100に供給され、信号配線100上をオペアンプ123−1、123−mの正相入力端子に向かって伝送されると共に、オペアンプ123−1、123−mの逆相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがスリーステイトCMOS差動ドライバ109の逆相出力端子から信号配線101に供給され、信号配線101上をオペアンプ123−1、123−mの逆相入力端子に向かって伝送される。

なお、オペアンプ123−1、123−mの入力インピーダンスは、通常、信号配線ペア99の特性インピーダンス(20〜100Ω)の1000倍以上のハイインピーダンスとなっているので、信号配線ペア99を伝送されてくる相補信号エネルギーはオペアンプ123−1、123−mでは殆ど吸収されず、そのままのエネルギー状態で終端抵抗102に到達し、ここで全エネルギーが熱となって消費される。したがって、相補信号エネルギーの反射は起こらないため、常に良好な波形の相補送信デジタル信号CS、/CSがオペアンプ123−1、123−mを通過することになる。

また、ICチップ108から発信されるリードイネーブル信号REが活性状態で、ICチップ108のオペアンプ116が受信状態になると、ICチップ122−1のスリーステイトCMOS差動ドライバ124−1又はICチップ122−mのスリーステイトCMOS差動ドライバ124−mから相補送信デジタル信号が信号配線ペア99に出力され、信号配線ペア99を左右に伝送されることになるが、右方向に伝送される相補送信デジタル信号は、終端抵抗102で吸収され、左方向に伝送される相補送信デジタル信号は、ICチップ108内の終端抵抗部117の終端抵抗120で吸収されるので、相補送信デジタル信号に反射が起こることはなく、オペアンプ116は、常に良好な波形の相補送信デジタル信号を受信することができる。

なお、スリーステイトCMOS差動ドライバ109、124−1、124−mのオン抵抗は、信号配線ペア99の特性インピーダンスの1/2以下の抵抗であることが好ましい。

このように、本発明の第5参考例においては、ICチップ108から発信されるライトイネーブル信号WEが活性状態の下で、送信デジタル信号TSが遷移すると、相補信号エネルギーが信号配線100、101上をオペアンプ123−1、123−mに向かって伝送されるが、信号配線100、101は、カップリング係数を大とする等長平行配線からなるペア配線構造とされているので、信号配線100、101を電磁界がほぼ閉じた伝送線路とし、信号配線100、101上を伝送される相補信号エネルギーの損失を小さくしてTEM伝送に近いモードで伝送することができる。

また、電源配線106及び接地配線107も、カップリング係数を大とする等長平行配線からなるペア配線構造とされているので、電源・接地配線ペア105を電磁界がほぼ閉じた伝送線路とし、たとえ、電源・接地配線ペア105が長い場合であっても、相補送信デジタル信号CS、/CSをオペアンプ123−1、123−mに伝送するに必要な、電源電圧入力端子103及び接地電圧入力端子104から電源・接地配線ペア105を介してのスリーステイトCMOS差動ドライバ109への相補信号エネルギーの伝送をTEM伝送に近いモードで行うことができる。

しかも、電源・接地配線ペア105の特性インピーダンスは、信号配線ペア99の特性インピーダンスと同一とされ、電源・接地配線ペア105は、特性インピーダンス上、信号配線ペア99と整合するように構成されているので、信号配線ペア99で消費される相補信号エネルギーと、電源電圧入力端子103及び接地電圧入力端子104からスリーステイトCMOS差動ドライバ109に供給される相補信号エネルギーが整合し、その損失を小さくすることができる。

したがって、本発明の第5参考例によれば、相補送信デジタル信号CS、/CSの波形の変形が実質的になくなり、スリーステイトCMOS差動ドライバ109からオペアンプ123−1、123−mへの信号配線ペア99を介しての相補送信デジタル信号CS、/CSの光の速度に近い速度での伝送を行うことができる。

なお、ICチップ108内のスリーステイトCMOS差動ドライバ109に電源電圧及び接地電圧を供給する電源配線及び接地配線も等長平行配線からなるペア配線構造とすることが好適であり、このように構成する場合には、スリーステイトCMOS差動ドライバ109からオペアンプ123−1、123−mへの信号配線ペア99を介しての相補送信デジタル信号CS、/CSの伝送の更なる高速化を図ることができる。

また、本発明の第5参考例によれば、ICチップ122−1、122−mは、差動レシーバとしてオペアンプ123−1、123−mを設けているが、オペアンプ123−1、123−mは、同相ノイズ及び信号配線100、101のどちらか一方に乗ったノイズに対しては動作せず、相補送信デジタル信号CS、/CSのみに感知するので、伝送系をノイズマージンが大きい伝送系とすることができる。したがって、信号電圧を低く下げることができる。例えば、現行の回路で最も低い振幅は、0.8V〜1.5Vあたりであるが、0.1V程度まで下げることが可能である。これにより、立ち上がり及び立ち下がり勾配を低くでき、高周波信号の伝送を図ることができると共に、省電力を達成することができる。

(第6参考例・・図25)

図25は本発明の第6参考例の概念図であり、本発明の第6参考例は、2組の信号配線ペアを有し、これら2組の信号配線ペアに分岐が存在し、かつ、双方向の信号伝送を行う伝送回路が構成されている場合を例にしている。

図25中、126は配線基板、127は配線基板126に形成されたカップリング係数を大とする等長平行配線とされた信号配線128、129からなる信号配線ペア、131は配線基板126に形成されたカップリング係数を大とする等長平行配線とされた信号配線132、133からなる信号配線ペアである。なお、信号配線ペア127、131は、カップリング係数及び特性インピーダンスをそれぞれ同一とされ、等長、かつ、平行とされている。

また、135は配線基板126に形成された正の電源電圧VDDを入力するための電源電圧入力端子、136は配線基板126に形成された接地電圧VSSを入力するための接地電圧入力端子、137は配線基板126に形成されたカップリング係数を大とする等長平行配線とされた電源配線138及び接地配線139からなる電源・接地配線ペアである。

また、信号配線ペア127、131の特性インピーダンスをZ0、電源・接地配線ペア137の特性インピーダンスをZ1とすると、Z1=Z0/2(但し、2は信号配線ペアの数)とされている。なお、Z1=Z0/2とできない場合には、可能な限りこれに近い値とすることが好適である。

また、信号配線ペア127、131及び電源・接地配線ペア137は、図16に示すと同様にコプレーナ配線構造としても良いし、図17に示すと同様にスタック配線構造としても良い。

また、140は配線基板126に搭載されたICチップであり、このICチップ140は、その電源電圧入力端子140Aを電源配線138に接続され、その接地電圧入力端子140Bを接地配線139に接続され、その信号入出力端子140C、140D、140E、140Fをそれぞれ信号配線128、129、132、133に接続されている。

また、ICチップ140において、141は内部回路(図示せず)から与えられる送信デジタル信号TS1を相補送信デジタル信号CS1、/CS1に相補信号化し、これら相補送信デジタル信号CS1、/CS1を信号入出力端子140C、140Dを介して信号配線128、129に出力する、図22に示すスリーステイトCMOS差動ドライバ109と同様に構成されたスリーステイトCMOS差動ドライバである。

また、142は内部回路から与えられる送信デジタル信号TS2を相補送信デジタル信号CS2、/CS2に相補信号化し、これら相補送信デジタル信号CS2、/CS2を信号入出力端子140E、140Fを介して信号配線132、133に出力する、図22に示すスリーステイトCMOS差動ドライバ109と同様に構成されたスリーステイトCMOS差動ドライバである。

また、143は差動レシーバをなすオペアンプ、144は図22に示す終端抵抗部117と同様に構成された信号配線128、129に接続されたICチップ140内の信号配線を終端する終端抵抗部であり、オペアンプ143の正相入力端子及び終端抵抗部144の一端144Aは、信号入出力端子140Cに接続され、オペアンプ143の逆相入力端子及び終端抵抗部144の他端144Bは、信号入出力端子140Dに接続されている。

また、145は差動レシーバをなすオペアンプ、146は図22に示す終端抵抗部117と同様に構成された信号配線132、133に接続されたICチップ140内の信号配線を終端する終端抵抗部であり、オペアンプ145の正相入力端子及び終端抵抗部146の一端146Aは、信号入出力端子140Eに接続され、オペアンプ145の逆相入力端子及び終端抵抗部146の他端146Bは、信号入出力端子140Fに接続されている。

また、147−1、147−mは配線基板126に搭載された同種又は異種のICチップであり、これらICチップ147−1、147−mは、その信号入出力端子147−1A、147−mAを信号配線128に接続され、その信号入出力端子147−1B、147−mBを信号配線129に接続されている。

また、ICチップ147−1において、148−1は差動レシーバをなすオペアンプであり、その正相入力端子を信号入出力端子147−1Aに接続され、その逆相入出力端子を信号入力端子147−1Bに接続されている。

また、149−1は差動レシーバをなすオペアンプであり、その正相入力端子を信号入出力端子147−1Cに接続され、その逆相入力端子を信号入出力端子147−1Dに接続されている。

また、150−1はスリーステイトCMOS差動ドライバ141と同様に構成されたスリーステイトCMOS差動ドライバであり、その正相出力端子を信号入出力端子147−1Aに接続され、その逆相出力端子を信号入出力端子147−1Bに接続されている。

また、151−1はスリーステイトCMOS差動ドライバ141と同様に構成されたスリーステイトCMOS差動ドライバであり、その正相出力端子を信号入出力端子147−1Cに接続され、その逆相出力端子を信号入出力端子147−1Dに接続されている。

また、ICチップ147−mにおいて、148−mは差動レシーバをなすオペアンプであり、その正相入力端子を信号入出力端子147−mAに接続され、その逆相入力端子を信号入出力端子147−mBに接続されている。

また、149−mは差動レシーバをなすオペアンプであり、その正相入力端子を信号入出力端子147−mCに接続され、その逆相入力端子を信号入出力端子147−mDに接続されている。

また、150−mはスリーステイトCMOS差動ドライバ141と同様に構成されたスリーステイトCMOS差動ドライバであり、その正相出力端子を信号入出力端子147−mAに接続され、その逆相出力端子を信号入出力端子147−mBに接続されている。

また、151−mはスリーステイトCMOS差動ドライバ141と同様に構成されたスリーステイトCMOS差動ドライバであり、その正相出力端子を信号入出力端子147−mCに接続され、その逆相出力端子を信号入出力端子147−mDに接続されている。

このように構成された本発明の第6参考例においては、ICチップ140から発信されるライトイネーブル信号WEが活性状態の下で、送信デジタル信号TS1がLレベルからHレベルに遷移すると、オペアンプ148−1、148−mの正相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがスリーステイトCMOS差動ドライバ141の正相出力端子から信号配線128に供給され、信号配線128上をオペアンプ148−1、148−mの正相入力端子に向かって伝送されると共に、オペアンプ148−1、148−mの逆相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがスリーステイトCMOS差動ドライバ141の逆相出力端子から信号配線129に供給され、信号配線129上をオペアンプ148−1、148−mの逆相入力端子に向かって伝送される。

また、送信デジタル信号TS2がLレベルからHレベルに遷移すると、オペアンプ149−1、149−mの正相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがスリーステイトCMOS差動ドライバ142の正相出力端子から信号配線132に供給され、信号配線132上をオペアンプ149−1、149−mの正相入力端子に向かって伝送されると共に、オペアンプ149−1、149−mの逆相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがスリーステイトCMOS差動ドライバ142の逆相出力端子から信号配線133に供給され、信号配線133上をオペアンプ149−1、149−mの逆相入力端子に向かって伝送される。

これに対して、送信デジタル信号TS1がHレベルからLレベルに遷移すると、オペアンプ148−1、148−mの正相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがスリーステイトCMOS差動ドライバ141の正相出力端子から信号配線128に供給され、信号配線128上をオペアンプ148−1、148−mの正相入力端子に向かって伝送されると共に、オペアンプ148−1、148−mの逆相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがスリーステイトCMOS差動ドライバ141の逆相出力端子から信号配線129に供給され、信号配線129上をオペアンプ148−1、148−mの逆相入力端子に向かって伝送される。

また、送信デジタル信号TS2がHレベルからLレベルに遷移すると、オペアンプ149−1、149−mの正相入力端子をHレベルからLレベルに遷移させるための負の信号エネルギーがスリーステイトCMOS差動ドライバ142の正相出力端子から信号配線132に供給され、信号配線132上をオペアンプ149−1、149−mの正相入力端子に向かって伝送されると共に、オペアンプ149−1、149−mの逆相入力端子をLレベルからHレベルに遷移させるための正の信号エネルギーがスリーステイトCMOS差動ドライバ142の逆相出力端子から信号配線133に供給され、信号配線133上をオペアンプ149−1、149−mの逆相入力端子に向かって伝送される。

なお、オペアンプ148−1、148−m、149−1、149−mの入力インピーダンスは、通常、信号配線ペア127、131の特性インピーダンス(20〜100Ω)の1000倍以上のハイインピーダンスとなっているので、信号配線ペア127、131を伝送されてくる相補信号エネルギーはオペアンプ148−1、148−m、149−1、149−mでは殆ど吸収されず、そのままのエネルギー状態で終端抵抗130、134に到達し、ここで全エネルギーが熱となって消費される。したがって、相補信号エネルギーの反射は起こらないため、常に良好な波形の相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2がそれぞれオペアンプ148−1、148−m及びオペアンプ149−1、149−mを通過することになる。

また、ICチップ140から発信されるリードイネーブル信号REが活性状態で、ICチップ140のオペアンプ143、145が受信状態になると、ICチップ147−1のスリーステイトCMOS差動ドライバ150−1、151−1又はICチップ147−mのスリーステイトCMOS差動ドライバ150−m、151−mから相補送信デジタル信号が信号配線ペア127、131に出力され、信号配線ペア127、131を左右に伝送されることになるが、右方向に伝送される相補送信デジタル信号は、終端抵抗130、134で吸収され、左方向に伝送される相補送信デジタル信号は、ICチップ140内の終端抵抗部144、146の抵抗で吸収されるので、相補送信デジタル信号に反射が起こることはなく、オペアンプ143、145は、常に良好な波形の相補送信デジタル信号を受信することができる。

なお、スリーステイトCMOS差動ドライバ141、142、150−1、151−1、150−m、151−mのオン抵抗は、信号配線ペア127、131の特性インピーダンスの1/2以下の抵抗であることが好ましい。

このように、本発明の第6参考例においては、ICチップ140から発信されるライトイネーブル信号WEが活性状態の下で、送信デジタル信号TS1、TS2が遷移すると、相補信号エネルギーが信号配線128、129及び信号配線132、133上をオペアンプ148−1、148−m及びオペアンプ149−1、149−mに向かって伝送されるが、信号配線128、129及び信号配線132、133は、カップリング係数を大とする等長平行配線からなるペア配線構造とされているので、信号配線128、129及び信号配線132、133を電磁界がほぼ閉じた伝送線路とし、信号配線128、129及び信号配線132、133上を伝送される相補信号エネルギーの損失を小さくしてTEM伝送に近いモードで伝送することができる。

また、電源配線138及び接地配線139も、カップリング係数を大とする等長平行配線からなるペア配線構造とされているので、電源・接地配線ペア137を電磁界がほぼ閉じた伝送線路とし、たとえ、電源・接地配線ペア137が長い場合であっても、相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2をオペアンプ148−1、148−m及びオペアンプ149−1、149−mに伝送するに必要な、電源電圧入力端子135及び接地電圧入力端子136から電源・接地配線ペア137を介してのスリーステイトCMOS差動ドライバ141、142への相補信号エネルギーの伝送をTEM伝送に近いモードで行うことができる。

しかも、本発明の第6参考例においては、信号配線ペア127、131の特性インピーダンスをZ0、電源・接地配線ペア137の特性インピーダンスをZ1とすると、Z1=Z0/2とされ、電源・接地配線ペア137は、特性インピーダンス上、信号配線ペア127、131に整合するように構成されているので、信号配線ペア127、131で消費される相補信号エネルギーと、電源電圧入力端子135及び接地電圧入力端子136からスリーステイトCMOS差動ドライバ141、142に供給される相補信号エネルギーが整合し、その損失を小さくすることができる。

したがって、本発明の第6参考例によれば、相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の波形の変形が実質的になくなり、スリーステイトCMOS差動ドライバ141及びスリーステイトCMOS差動ドライバ142からオペアンプ148−1、148−m及びオペアンプ149−1、149−mへの信号配線ペア127及び信号配線ペア131を介しての相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の光の速度に近い速度での伝送を行うことができる。

なお、ICチップ140内のスリーステイトCMOS差動ドライバ141、142に電源電圧VDD及び接地電圧VSSを供給する電源配線及び接地配線も等長平行配線からなるペア配線構造とすることが好適であり、このように構成する場合には、スリーステイトCMOS差動ドライバ141及びスリーステイトCMOS差動ドライバ142からオペアンプ148−1、148−m及びオペアンプ149−1、149−mへの信号配線ペア127及び信号配線ペア131を介しての相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の伝送の更なる高速化を図ることができる。

また、本発明の第6参考例によれば、ICチップ147−1、147−mは、差動レシーバとしてオペアンプ148−1、149−1、148−m、149−mを設けているが、オペアンプ148−1、148−mは、同相ノイズ及び信号配線128、129のどちらか一方に乗ったノイズに対しては動作せず、相補送信デジタル信号CS1、/CS1のみに感知し、オペアンプ149−1、149−mは、同相ノイズ及び信号配線132、133のどちらか一方に乗ったノイズに対しては動作せず、相補送信デジタル信号CS2、/CS2のみに感知するので、伝送系をノイズマージンが大きい伝送系とすることができる。したがって、信号電圧を低く下げることができる。例えば、現行の回路で最も低い振幅は、0.8V〜1.5Vあたりであるが、0.1V程度まで下げることが可能である。これにより、立ち上がり及び立ち下がり勾配を低くでき、高周波信号の伝送を図ることができると共に、省電力を達成することができる。

(第7参考例・・図26、図27)

図26は本発明の第7参考例の概念図であり、本発明の第7参考例は、ICチップ29内に設けられているCMOS差動ドライバ30用の電源配線と接地配線との間にコンデンサ153を接続し、その他については、図12に示す本発明の第1参考例と同様に構成したものである。

ここに、例えば、CMOS差動ドライバ30の正相出力端子に出力される正相送信デジタル信号CSの立ち上がり時間が信号配線22の全体をHレベルにするための信号エネルギーを供給する時間(信号配線22の伝送遅延時間)よりも遅い場合には、信号配線22に対する正の信号エネルギーの供給と、CMOS差動レシーバ34に対する信号エネルギーの供給は平行して行われ、CMOS差動レシーバ34に信号配線22の存在を意識させることは、ほぼ無い。

これに対して、CMOS差動ドライバ30の正相出力端子に出力される正相送信デジタル信号CSの立ち上がり時間が信号配線22の全体をHレベルにするための信号エネルギーを供給する時間よりも早い場合には、正相送信デジタル信号CSがCMOS差動レシーバ34に伝送される前に、CMOS差動ドライバ30から出力される正相送信デジタル信号CSをHレベルにしなければ、正相送信デジタル信号CSの伝送の高速化を図ることができない。

当然、反対に、正相送信デジタル信号CSをLレベルに遷移させる場合には、高エネルギー状態の信号配線22のエネルギーを高速に逃がす操作が正相送信デジタル信号CSの伝送の高速化を図るために必要となる。

ここに、良いレシーバとは、微弱な信号エネルギーでも、それを充分関知して、自身の状態を遷移させるものであり、信号立ち上がり時間が信号配線の遅延よりも遅いときは、小さな信号エネルギーの供給で足り、ドライバビリティの小さなドライバ(消費電力の小さなドライバ)が使用できた。

ところが、信号配線の遅延時間より信号の立ち上がり時間が短い高速の信号が出力されることが通常となった現在、レシーバの特性よりも、まず、信号配線への信号エネルギーの供給をどのようにするのかがドライバの設計において重要となってきた。

良いレシーバの特性を見ると、信号の電気エネルギーを消費しない、即ち、入力抵抗の高いものであり、これを、例えば、1KΩであるとすると、これに対して、信号配線の特性インピーダンスは25〜200Ωである。したがって、信号配線は、レシーバより1桁から2桁ものエネルギーを消費するものとなる。

ここに、例えば、信号配線の長さを30cm、信号の伝播速度を2×108m/sとすると、信号配線の伝搬に要する時間は、1.5nsとなり、レシーバがこの信号配線の中間に存在したとしても、この1.5nsの間は、信号配線に信号エネルギーを供給する時間となり、ドライバは、この間、信号エネルギーを供給し続けなければならない。即ち、ドライバのドライバビリティとして、信号配線の特性インピーダンスを負荷と見なした能力がなければならない。

ここに、図27はICチップ内の電源配線の電源電圧と、CMOS差動ドライバ30から出力される正相送信デジタル信号CSとの関係を示す波形図であり、図27(A)はコンデンサ153が存在しない場合、図27(B)はコンデンサ153が存在する場合を示しており、実線P1は電源電圧、実線P2は正相送信デジタル信号CSを示している。

即ち、差動ドライバ30は、基本的にはスイッチ回路であり、そのドライバビリティの源泉は電源・接地配線ペア26となるが、電源・接地配線ペア26の特性インピーダンスZ1が信号配線ペア21の特性インピーダンスZ0よりも大きく、かつ、コンデンサ153が存在していないと、図27(A)に示すように、電源電圧の降下が起き、正相送信デジタル信号CSの立ち上がりは、なだらかになる。

これに対して、本発明の第7参考例においては、ICチップ29内に設けられているCMOS差動ドライバ30用の電源配線と接地配線との間にはコンデンサ153が接続されているので、電源・接地配線ペア26の特性インピーダンスZ1が信号配線ペア21の特性インピーダンスZ0よりも大きい場合であっても、コンデンサ153の電荷が信号配線22に供給され、図27(B)に示すように、差動ドライバ30から出力される正相送信デジタル信号CSは、立ち上がり波形の急峻なものとなる。

ここに、CMOS差動ドライバ30から信号配線22に信号エネルギーが供給される時間、即ち、信号配線22の遅延時間をtpd[s]とし、その間に信号配線22に流れる電流をI[A]とすると、その間に信号配線22に供給される電荷量Q[C]は、Q=It[C]となる。そこで、送信デジタル信号CSの振幅(電圧)をV[V]とすると、この電荷量を蓄えるに必要なコンデンサの容量C[F]は、C=Q/Vとなる。

たとえば、CMOS差動ドライバ30のオン抵抗を50Ω、信号配線ペア21の特性インピーダンスを50Ω、信号の振幅を0.1V、信号配線22の遅延時間tpdを1.5nsとすると、I=1mA、Q=1.5pC、C=15pFとなる。

ここに、信号配線ペア21をスタック配線構造とした場合において、真空誘電率をε0、絶縁基板の誘電率をεr、信号配線22、23間への印加電圧をV、信号配線22の面積をA、信号配線22、23間の距離をdとすると、Q=ε0εrVA/dが成立する。そこで、ε0=8.85×10-12[F/m]、εr=3、Q=1.5pCとすると、A/d=0.564mとなる。また、d=20nmとすると、A=1.13×10-8m2となり、寸法に直すと、A=0.11mm×0.11mmとなる。

この寸法は、とても、ICチップ29のアクティブ領域内には埋め込めないが、電源電圧入力端子29Aをなすボンディングパッド及び接地電圧入力端子29Bをなすボンディングパッドの下方に形成することができる。

このように、本発明の第7参考例によれば、ICチップ29内に設けられているCMOS差動ドライバ30用の電源配線と接地配線との間にコンデンサ153を接続しているので、送信デジタル信号TSが遷移した場合、電源・接地配線ペア26を介してCMOS差動ドライバ30に相補信号エネルギーが供給される前に、コンデンサ153からCMOS差動ドライバ30に相補信号エネルギーを供給することができ、図12に示す本発明の第1参考例以上に相補送信デジタル信号CS、/CSの伝送の高速化を図ることができる。

なお、本発明の第7参考例は、特に、Z1(電源・接地配線ペア26の特性インピーダンス)>Z0(信号配線ペア21の特性インピーダンス)の場合に有効である。

(第8参考例・・図28)

図28は本発明の第8参考例の概念図であり、本発明の第8参考例は、ICチップ48内に設けられているCMOS差動ドライバ49、50用の電源配線と接地配線との間にコンデンサ154を接続し、その他については、図15に示す本発明の第2参考例と同様に構成したものである。

本発明の第8参考例によれば、送信デジタル信号TS1、TS2が遷移した場合、電源・接地配線ペア45を介してCMOS差動ドライバ49、50に相補信号エネルギーが供給される前に、コンデンサ154からCMOS差動ドライバ49、50に相補信号エネルギーを供給することができ、図15に示す本発明の第2参考例以上に相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の伝送の高速化を図ることができる。

なお、本発明の第8参考例は、特に、Z1(電源・接地配線ペア45の特性インピーダンス)>Z0(信号配線ペア37、40の特性インピーダンス)/2の場合に有効である。

(第9参考例・・図29)

図29は本発明の第9参考例の概念図であり、本発明の第9参考例は、ICチップ65内に設けられているCMOS差動ドライバ66用の電源配線と接地配線との間にコンデンサ155を接続し、その他については、図18に示す本発明の第3参考例と同様に構成したものである。

本発明の第9参考例によれば、送信デジタル信号TSが遷移した場合、電源・接地配線ペア62を介してCMOS差動ドライバ66に相補信号エネルギーが供給される前に、コンデンサ155からCMOS差動ドライバ66に相補信号エネルギーを供給することができ、図18に示す本発明の第3参考例以上に相補送信デジタル信号CS、/CSの伝送の高速化を図ることができる。

なお、本発明の第9参考例は、特に、Z1(電源・接地配線ペア62の特性インピーダンス)>Z0(信号配線ペア56の特性インピーダンス)の場合に有効である。

(第10参考例・・図30)

図30は本発明の第10参考例の概念図であり、本発明の第10参考例は、ICチップ84内に設けられているCMOS差動ドライバ85、86用の電源配線と接地配線との間にコンデンサ156を接続し、その他については、図19に示す本発明の第4参考例と同様に構成したものである。

本発明の第10参考例によれば、送信デジタル信号TS1、TS2が遷移した場合、電源・接地配線ペア81を介してCMOS差動ドライバ85、86に相補信号エネルギーが供給される前に、コンデンサ156からCMOS差動ドライバ85、86に相補信号エネルギーを供給することができ、図19に示す本発明の第4参考例以上に相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の伝送の高速化を図ることができる。

なお、本発明の第10参考例は、特に、Z1(電源・接地配線ペア81の特性インピーダンス)>Z0(信号配線ペア71、75の特性インピーダンス)/2の場合に有効である。

(第11参考例・・図31)

図31は本発明の第11参考例の概念図であり、本発明の第11参考例は、ICチップ108内に設けられているスリーステイトCMOS差動ドライバ109用の電源配線と接地配線との間にコンデンサ157を接続し、その他については、図22に示す本発明の第5参考例と同様に構成したものである。

本発明の第11参考例によれば、送信デジタル信号TSが遷移した場合、電源・接地配線ペア105を介してスリーステイトCMOS差動ドライバ109に相補信号エネルギーが供給される前に、コンデンサ157からスリーステイトCMOS差動ドライバ109に相補信号エネルギーを供給することができ、図22に示す本発明の第5参考例以上に相補送信デジタル信号CS、/CSの伝送の高速化を図ることができる。

なお、本発明の第11参考例は、特に、Z1(電源・接地配線ペア105の特性インピーダンス)>Z0(信号配線ペア99の特性インピーダンス)の場合に有効である。

(第12参考例・・図32)

図32は本発明の第12参考例の概念図であり、本発明の第12参考例は、ICチップ140内に設けられているスリーステイトCMOS差動ドライバ141、142用の電源配線と接地配線との間にコンデンサ158を接続し、その他については、図25に示す本発明の第6参考例と同様に構成したものである。

本発明の第12参考例によれば、送信デジタル信号TS1、TS2が遷移した場合、電源・接地配線ペア137を介してスリーステイトCMOS差動ドライバ141、142に相補信号エネルギーが供給される前に、コンデンサ158からスリーステイトCMOS差動ドライバ141、142に相補信号エネルギーを供給することができ、図25に示す本発明の第6参考例以上に相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の伝送の高速化を図ることができる。

なお、本発明の第12参考例は、特に、Z1(電源・接地配線ペア137の特性インピーダンス)>Z0(信号配線ペア127、131の特性インピーダンス)/2の場合に有効である。

なお、第7参考例〜第12参考例に示すように、ICチップ内の電源配線と接地配線との間にコンデンサを接続することは、非差動送信デジタル信号を出力するドライバを備えるICチップを搭載している電子装置にも適用することができ、そのようにする場合には、非差動送信デジタル信号を出力するドライバを備えるICチップを搭載している電子装置において、非差動送信デジタル信号の伝送の高速化を図ることができる。

(第13参考例・・図33、図34)

図33は本発明の第13参考例の概念図であり、本発明の第13参考例は、ICチップ29の近傍の電源配線27と接地配線28との間にコンデンサ159を接続し、その他については、図26に示す本発明の第7参考例と同様に構成したものである。

図34は本発明の第13参考例を説明するためのタイムチャートであり、図34(A)はICチップ29内のCMOS差動ドライバ30用の電源配線にインダクタンスによる電圧降下が存在しない場合の電源電流(破線Y1)及び電圧降下が存在する場合の電源電流(実線Y2)を示している。

また、図34(B)はICチップ29内のCMOS差動ドライバ30用の電源配線にインダクタンスによる電圧降下が存在しない場合の電源電圧(破線Y3)、ICチップ29内にコンデンサ153がない場合においてICチップ29内のCMOS差動ドライバ30用の電源配線にインダクタンスによる電圧降下が存在する場合の電源電圧(実線Y4)、コンデンサ153の容量を15pFとした場合に、信号配線22にコンデンサ153のみから電源電圧を供給した場合のコンデンサ153の電圧変化(実線Y5)、コンデンサ153の容量を1.5pFとした場合に、信号配線22にコンデンサ153のみから電源電圧を供給した場合のコンデンサ153の電圧変化(実線Y6)を示している。

但し、本発明の第7参考例で例を挙げたように、信号配線22の遅延時間は1.5ns、電源電流Iは1mA、送信デジタル信号CSの振幅は0.1Vとし、送信デジタル信号TSの立ち上がり時間trは0.1nsとしている。

ここに、たとえば、送信デジタル信号TSがLレベルからHレベルへの遷移を開始し、0.1ns後にHレベルとなると、コンデンサ153が存在しない場合には、ICチップ29内のCMOS差動ドライバ30用の電源配線にインダクタンスによる電圧降下が存在する場合、電源電圧の電圧降下は0.05Vとなるが、コンデンサ153が存在すれば、この電源電圧の電圧降下が0.05Vとならないようにすることができる。

即ち、例えば、コンデンサ153の容量を15pFとした場合において、信号配線22にコンデンサ153のみから電源電圧を供給した場合、送信デジタル信号TSがLレベルからHレベルに変化を開始した後、1.5nsが経過したとしても、電源電圧(コンデンサ153の電圧)は、0.081Vに降下するにすぎない。

これに対して、コンデンサ153の容量を1.5pFとした場合において、信号配線22にコンデンサ153のみから電源電圧を供給した場合、送信デジタル信号TSがLレベルからHレベルに変化を開始した後、1.5nsが経過した場合には、電源電圧(コンデンサ153の電圧)は、0.013Vに降下してしまうが、送信デジタル信号TSがHレベルとなった後、0.1ns程度の間であれば、電源電圧(コンデンサ153の電圧)の降下を0.06V程度に抑えることができる。

そこで、ICチップ29の近傍の電源配線27と接地配線28との間に容量をコンデンサ153の容量よりも大きくするコンデンサ159を接続すれば、コンデンサ153の容量を小さくすることができ、しかも、相補送信デジタル信号CS、/CSの伝送の高速化を図ることができる。本発明の第13参考例は、これを実現したものであり、パッドが微細化した場合においても、パッドの下方にコンデンサ153を形成することができる。

例えば、信号配線22、23の遅延時間の1/10以下で応答できる距離の電源配線27と接地配線28との間にコンデンサ153の容量の5倍以上の容量を有するコンデンサ159を接続する場合には、コンデンサ153の容量を本発明の第7参考例の場合の容量(15pF)の1/10である1.5pFにしても、相補送信デジタル信号CS、/CSの伝送の高速化を図ることができる。

このように、本発明の第13参考例によれば、送信デジタル信号TSが遷移した場合、電源・接地配線ペア26を介してCMOS差動ドライバ30に相補信号エネルギーが供給される前に、コンデンサ153からCMOS差動ドライバ30に相補信号エネルギーを供給することができると共に、コンデンサ159からコンデンサ153に相補信号エネルギーを供給することができるので、図26に示す本発明の第7参考例と同様に相補送信デジタル信号CS、/CSの伝送の高速化を図ることができると共に、コンデンサ153の小容量化を図ることができ、ICチップ29の微細化に対応することができる。

なお、本発明の第13参考例は、特に、Z1(電源・接地配線ペア26の特性インピーダンス)>Z0(信号配線ペア21の特性インピーダンス)の場合に有効である。

(第14参考例・・図35)

図35は本発明の第14参考例の概念図であり、本発明の第14参考例は、ICチップ48の近傍の電源配線46と接地配線47との間にコンデンサ160を接続し、その他については、図28に示す本発明の第8参考例と同様に構成したものである。

本発明の第14参考例によれば、送信デジタル信号TS1、TS2が遷移した場合、電源・接地配線ペア45を介してCMOS差動ドライバ49、50に相補信号エネルギーが供給される前に、コンデンサ154からCMOS差動ドライバ49、50に相補信号エネルギーを供給することができると共に、コンデンサ160からコンデンサ154に相補信号エネルギーを供給することができるので、図28に示す本発明の第8参考例と同様に相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の伝送の高速化を図ることができると共に、コンデンサ154の小容量化を図ることができ、ICチップ48の微細化に対応することができる。

なお、本発明の第14参考例は、特に、Z1(電源・接地配線ペア45の特性インピーダンス)>Z0(信号配線ペア37、40の特性インピーダンス)/2の場合に有効である。

(第15参考例・・図36)

図36は本発明の第15参考例の概念図であり、本発明の第15参考例は、ICチップ65の近傍の電源配線63と接地配線64との間にコンデンサ161を接続し、その他については、図29に示す本発明の第9参考例と同様に構成したものである。

本発明の第15参考例によれば、送信デジタル信号TSが遷移した場合、電源・接地配線ペア62を介してCMOS差動ドライバ66に相補信号エネルギーが供給される前に、コンデンサ155からCMOS差動ドライバ66に相補信号エネルギーを供給することができると共に、コンデンサ161からコンデンサ155に相補信号エネルギーを供給することができるので、図29に示す本発明の第9参考例と同様に相補送信デジタル信号CS、/CSの伝送の高速化を図ることができると共に、コンデンサ155の小容量化を図ることができ、ICチップ65の微細化に対応することができる。

なお、本発明の第15参考例は、特に、Z1(電源・接地配線ペア62の特性インピーダンス)>Z0(信号配線ペア56の特性インピーダンス)の場合に有効である。

(第16参考例・・図37)

図37は本発明の第16参考例の概念図であり、本発明の第16参考例は、ICチップ84の近傍の電源配線82と接地配線83との間にコンデンサ162を接続し、その他については、図30に示す本発明の第10参考例と同様に構成したものである。

本発明の第16参考例によれば、送信デジタル信号TS1、TS2が遷移した場合、電源・接地配線ペア81を介してCMOS差動ドライバ85、86に相補信号エネルギーが供給される前に、コンデンサ156からCMOS差動ドライバ85、86に相補信号エネルギーを供給することができると共に、コンデンサ162からコンデンサ156に相補信号エネルギーを供給することができるので、図30に示す本発明の第10参考例と同様に相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の伝送の高速化を図ることができると共に、コンデンサ156の小容量化を図ることができ、ICチップ84の微細化に対応することができる。

なお、本発明の第16参考例は、特に、Z1(電源・接地配線ペア81の特性インピーダンス)>Z0(信号配線ペア71、75の特性インピーダンス)/2の場合に有効である。

(第17参考例・・図38)

図38は本発明の第17参考例の概念図であり、本発明の第17参考例は、ICチップ108の近傍の電源配線106と接地配線107との間にコンデンサ163を接続し、その他については、図31に示す本発明の第11参考例と同様に構成したものである。

本発明の第17参考例によれば、送信デジタル信号TSが遷移した場合、電源・接地配線ペア105を介してスリーステイトCMOS差動ドライバ109に相補信号エネルギーが供給される前に、コンデンサ157からスリーステイトCMOS差動ドライバ109に相補信号エネルギーを供給することができると共に、コンデンサ163からコンデンサ157に相補信号エネルギーを供給することができるので、図31に示す本発明の第11参考例と同様に相補送信デジタル信号CS、/CSの伝送の高速化を図ることができると共に、コンデンサ157の小容量化を図ることができ、ICチップ108の微細化に対応することができる。

なお、本発明の第17参考例は、特に、Z1(電源・接地配線ペア105の特性インピーダンス)>Z0(信号配線ペア99の特性インピーダンス)の場合に有効である。

(第18参考例・・図39)

図39は本発明の第18参考例の概念図であり、本発明の第18参考例は、ICチップ140の近傍の電源配線138と接地配線139との間にコンデンサ164を接続し、その他については、図32に示す本発明の第12参考例と同様に構成したものである。

本発明の第18参考例によれば、送信デジタル信号TS1、TS2が遷移した場合、電源・接地配線ペア137を介してスリーステイトCMOS差動ドライバ141、142に相補信号エネルギーが供給される前に、コンデンサ158からスリーステイトCMOS差動ドライバ141、142に相補信号エネルギーを供給することができると共に、コンデンサ164からコンデンサ158に相補信号エネルギーを供給することができるので、図32に示す本発明の第12参考例と同様に相補送信デジタル信号CS1、/CS1及び相補送信デジタル信号CS2、/CS2の伝送の高速化を図ることができると共に、コンデンサ158の小容量化を図ることができ、ICチップ140の微細化に対応することができる。

なお、本発明の第18参考例は、特に、Z1(電源・接地配線ペア137の特性インピーダンス)>Z0(信号配線ペア127、131の特性インピーダンス)/2の場合に有効である。

また、第13参考例〜第18参考例に示すように、ICチップ内の電源配線と接地配線との間にコンデンサを接続すると共に、ICチップの近傍の電源配線と接地配線との間にコンデンサを接続することは、非差動送信デジタル信号を出力するドライバを備えるICチップを搭載している電子装置にも適用することができ、そのようにする場合には、非差動送信デジタル信号を出力するドライバを備えるICチップを搭載している電子装置において、非差動送信デジタル信号の伝送の高速化を図ることができる。

また、第1参考例〜第18参考例において、相補送信デジタル信号を出力する差動ドライバの出力端側に送信デジタル信号の第3高調波以上をカットするローパスフィルタを挿入する場合には、送信デジタル信号として波形の良好なデジタル信号を伝送させることができる。

また、相補送信デジタル信号を出力する差動ドライバの出力端側に送信デジタル信号の第3高調波以上をカットするローパスフィルタを挿入すると共に、差動ドライバの電源電圧入力端子側及び接地電圧入力端子側に送信デジタル信号の第3高調波以上をカットするローパスフィルタを挿入する場合には、送信デジタル信号として更に波形の良好なデジタル信号を伝送させることができる。

また、送信デジタル信号の第3高調波以上をカットするローパスフィルタは、送信デジタル信号の基本周波数成分を通過域とするバンドパスフィルタと、直流成分を通過域とするローパスフィルタとを並列接続して構成しても良い。

また、このようなローパスフィルタは、ICチップの内部に作成しても良いし、配線とICチップとの間に接続させるようにしても良い。

また、このようなローパスフィルタを設けることは、非差動送信デジタル信号を出力するドライバを備えるICチップを搭載している電子装置にも適用することができ、そのようにする場合には、非差動送信デジタル信号を出力するドライバを備えるICチップを搭載している電子装置において、非差動送信デジタル信号として波形の良好なデジタル信号を伝送させることができる。

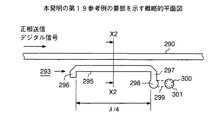

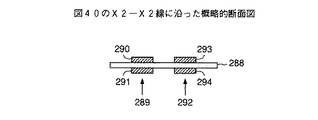

(第19参考例・・図40、図41)

図40は本発明の第19参考例の要部を示す概略的平面図、図41は図40のX2−X2線に沿った概略的断面図であり、図40、図41において、288は絶縁基板、289は等長平行配線とされたカップリング係数を大とする信号配線290、291からなる相補送信デジタル信号を1方向に伝送する信号配線ペアである。

また、292は信号配線290を伝送されてくる正相送信デジタル信号を受信して取り出すための方向性結合器293及び信号配線291を伝送されてくる逆相送信デジタル信号を受信して取り出すための方向性結合器294からなる方向性結合器ペアである。

また、方向性結合器293において、295は信号配線290と平行に形成され、長さを送信デジタル信号の基本周波数成分の波長λの1/4とし、信号配線290を伝送されてくる正相送信デジタル信号の基本周波数成分を受信する配線部である。

また、296、297は配線部295の両端部に信号配線290の電磁界との干渉を避けるために信号配線290と直交する方向に形成された配線部であり、配線部297の先端部298は、配線部295で受信した正相送信デジタル信号を取り出すための正相送信デジタル信号取り出し電極とされている。

また、方向性結合器294は、方向性結合器293が有する配線部295、296、297と対向する配線部を有していると共に、配線部297に対向する配線部の先端から右側に僅かに延長された配線部299を有している。

そして、スルーホール300を介して配線部299に接続された逆相送信デジタル信号取り出し電極301が正相送信デジタル信号取り出し電極298と同一面に設けられている。

なお、方向性結合器293の配線部296の先端及び方向性結合器294の配線部296に対向する配線部の先端は、開放でも良いが、それぞれ、終端抵抗で終端することが好適である。

このように構成された本発明の第19参考例においては、信号配線290を伝送されてくる正相送信デジタル信号の基本周波数成分を方向性結合器293の配線部295で受信し、正相送信デジタル信号取り出し電極298から取り出すことができると共に、信号配線291を伝送されてくる逆相送信デジタル信号の基本周波数成分を方向性結合器293の配線部295と対向する方向性結合器294の配線部で受信し、逆相送信デジタル信号取り出し電極301から取り出すことができる。

したがって、本発明の第19参考例によれば、差動レシーバの正相入力端子及び逆相入力端子をそれぞれ正相送信デジタル信号取り出し電極298及び逆相送信デジタル信号取り出し電極301に接続することにより、信号配線ペア289を1方向に伝送される高速相補送信デジタル信号、たとえば、1GHz以上の高速相補送信デジタル信号の受信を容易に行うことができる。

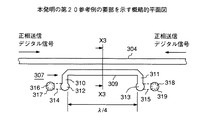

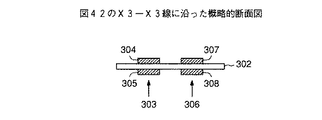

(第20参考例・・図42、図43)

図42は本発明の第20参考例の要部を示す概略的平面図、図43は図42のX3−X3線に沿った概略的断面図であり、図42、図43において、302は絶縁基板、303は等長平行配線とされたカップリング係数を大とする信号配線304、305からなる相補送信デジタル信号を双方向に伝送する信号配線ペアである。

また、306は信号配線304を伝送されてくる正相送信デジタル信号を受信して取り出すための方向性結合器307及び信号配線305を伝送されてくる逆相送信デジタル信号を受信して取り出すための方向性結合器308からなる方向性結合器ペアである。

また、方向性結合器307において、309は信号配線304と平行に形成され、長さを送信デジタル信号の基本周波数成分の波長λの1/4とし、信号配線304を伝送されてくる正相送信デジタル信号の基本周波数成分を受信する配線部、310、311は配線部309の両端部に信号配線304の電磁界との干渉を避けるために信号配線304と直交する方向に形成された配線部である。

そして、配線部310の先端部312は、左方向に伝送されてくる正相送信デジタル信号を取り出すための正相送信デジタル信号取り出し電極とされ、配線部311の先端部313は、右方向に伝送されてくる正相送信デジタル信号を取り出すための正相送信デジタル信号取り出し電極とされている。

また、方向性結合器308は、方向性結合器307が有する配線部309、310、311と対向する配線部を有すると共に、配線部310に対向する配線部の先端から左側に僅かに延長された配線部314及び配線部311に対向する配線部から右側に僅かに延長された配線部315を有している。

そして、スルーホール316を介して配線部314に接続された逆相送信デジタル信号取り出し電極317が正相送信デジタル信号取り出し電極312と同一面に設けられていると共に、スルーホール318を介して配線部315に接続された逆相送信デジタル信号取り出し電極319が正相送信デジタル信号取り出し電極313と同一面に設けられている。なお、図示は省略するが、方向性結合器307、308には受端終端抵抗が接続されている。

このように構成された本発明の第20参考例によれば、信号配線304を左方向に伝送されてくる正相送信デジタル信号の基本周波数成分を方向性結合器307の配線部309で受信し、正相送信デジタル信号取り出し電極312から取り出すことができると共に、信号配線305を左方向に伝送されてくる逆相送信デジタル信号の基本周波数成分を方向性結合器307の配線部309と対向する方向性結合器308の配線部で受信し、逆相送信デジタル信号取り出し電極317から取り出すことができる。

また、信号配線304を右方向に伝送されてくる正相送信デジタル信号の基本周波数成分を方向性結合器307の配線部309で受信し、正相送信デジタル信号取り出し電極313から取り出すことができると共に、信号配線305を右方向に伝送されてくる逆相送信デジタル信号の基本周波数成分を方向性結合器307の配線部309と対向する方向性結合器308の配線部で受信し、逆相送信デジタル信号取り出し電極319から取り出すことができる。

したがって、本発明の第20参考例によれば、差動レシーバの正相入力端子を正相送信デジタル信号取り出し電極312、313に接続すると共に、差動レシーバの逆相入力端子を逆相送信デジタル信号取り出し電極317、319に接続することにより、信号配線ペア303を双方向に伝送される高速相補送信デジタル信号、たとえば、1GHz以上の高速相補送信デジタル信号の受信を容易に行うことができる。

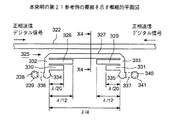

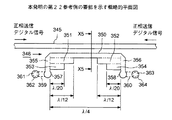

(第21参考例・・図44、図45)

図44は本発明の第21参考例の要部を示す概略的平面図、図45は図44のX4−X4線に沿った概略的断面図であり、図44、図45において、320は絶縁基板、321は等長平行配線とされたカップリング係数を大とする信号配線322、323からなる相補送信デジタル信号を双方向に伝送する信号配線ペアである。

また、324は信号配線322を伝送されてくる正相送信デジタル信号を受信して取り出すための方向性結合器325及び信号配線323を伝送されてくる逆相送信デジタル信号を受信して取り出すための方向性結合器326からなる方向性結合器ペアである。

また、方向性結合器325において、327は信号配線322と平行に形成され、長さを送信デジタル信号の基本周波数成分の波長λの1/4とし、信号配線322を伝送されてくる正相送信デジタル信号の基本周波数成分を受信する配線部である。

また、328、329は信号配線322と平行に形成され、長さを送信デジタル信号の基本周波数成分の波長λの1/12とし、信号配線322を伝送されてくる正相送信デジタル信号の第2高調波を受信する配線部である。

また、330、331は信号配線322と平行に形成され、長さを送信デジタル信号の基本周波数成分の波長λの1/20とし、信号配線322を左方向に伝送されてくる正相送信デジタル信号の第3高調波を受信する配線部である。

また、332、333は配線部327の両端部に信号配線322の電磁界との干渉を避けるために信号配線322と直交する方向に形成された配線部であり、配線部332の先端部334は、左方向に伝送されてくる正相送信デジタル信号を取り出すための正相送信デジタル信号取り出し電極とされていると共に、配線部333の先端部335は、右方向に伝送されてくる正相送信デジタル信号を取り出すための正相送信デジタル信号取り出し電極とされている。

また、方向性結合器326は、方向性結合器325が有する配線部327、328、329、330、331、332、333と対向する配線部を有すると共に、配線部332に対向する配線部の先端から左側に僅かに延長された配線部336及び配線部333に対向する配線部から右側に僅かに延長された配線部337を有している。

そして、スルーホール338を介して配線部336に接続された逆相送信デジタル信号取り出し電極339が正相送信デジタル信号取り出し電極334と同一面に設けられていると共に、スルーホール340を介して配線部337に接続された逆相送信デジタル信号取り出し電極341が正相送信デジタル信号取り出し電極335と同一面に設けられている。なお、図示は省略するが、方向性結合器325、326には受端終端抵抗が接続されている。

このように構成された本発明の第21参考例においては、信号配線322を左方向に伝送されてくる正相送信デジタル信号の基本周波数成分、第2高調波、第3高調波をそれぞれ方向性結合器325の配線部327、328、330で受信し、正相送信デジタル信号取り出し電極334から取り出すことができると共に、信号配線323を左方向に伝送されてくる逆相送信デジタル信号の基本周波数成分、第2高調波、第3高調波を方向性結合器325の配線部327、328、330と対向する方向性結合器326の配線部で受信し、逆相送信デジタル信号取り出し電極339から取り出すことができる。

また、信号配線322を右方向に伝送されてくる正相送信デジタル信号の基本周波数成分、第2高調波、第3高調波をそれぞれ方向性結合器325の配線部327、329、331で受信し、正相送信デジタル信号取り出し電極335から取り出すことができると共に、信号配線323を右方向に伝送されてくる逆相送信デジタル信号の基本周波数成分、第2高調波、第3高調波を方向性結合器325の配線部327、329、331と対向する方向性結合器326の配線部で受信し、逆相送信デジタル信号取り出し電極341から取り出すことができる。

したがって、本発明の第21参考例によれば、差動レシーバの正相入力端子を正相送信デジタル信号取り出し電極334、335に接続すると共に、差動レシーバの逆相入力端子を逆相送信デジタル信号取り出し電極339、341に接続することにより、信号配線ペア321を双方向に伝送される高速相補送信デジタル信号、たとえば、1GHz以上の高速相補送信デジタル信号の受信を容易に行うことができる。

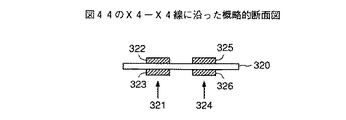

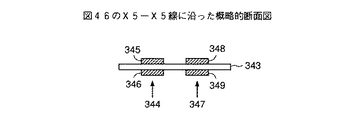

(第22参考例・・図46、図47)

図46は本発明の第22参考例の要部を示す概略的平面図、図47は図46のX5−X5線に沿った概略的断面図であり、図46、図47において、343は絶縁基板、344は等長平行配線とされたカップリング係数を大とする信号配線345、346からなる相補送信デジタル信号を双方向に伝送する信号配線ペアである。

また、347は信号配線345を伝送されてくる正相送信デジタル信号を受信して取り出すための方向性結合器348及び信号配線346を伝送されてくる逆相送信デジタル信号を受信して取り出すための方向性結合器349からなる方向性結合器ペアである。

また、方向性結合器348において、350は信号配線345と平行とされ、長さを送信デジタル信号の基本周波数成分の波長λの1/4とし、信号配線345を伝送されてくる正相送信デジタル信号の基本周波数成分を受信する配線部である。

また、351、352は信号配線345と平行とされ、長さを送信デジタル信号の基本周波数成分の波長λの1/12とし、信号配線345を伝送されてくる正相送信デジタル信号の第2高調波を受信する配線部である。

また、353、354は信号配線345と平行とされ、長さを送信デジタル信号の基本周波数成分の波長λの1/20とし、信号配線345を伝送されてくる正相送信デジタル信号の第3高調波を受信する配線部である。なお、本発明の第22参考例においては、配線部350、351、352、353、354は一体として構成されている。

また、355、356は配線部350の両端部に信号配線345の電磁界との干渉を避けるために信号配線345と直交する方向に形成された配線部であり、配線部355の先端部357は、左方向に伝送されてくる正相送信デジタル信号を取り出すための正相送信デジタル信号取り出し電極とされていると共に、配線部356の先端部358は、右方向に伝送されてくる正相送信デジタル信号取り出し電極とされている。

また、方向性結合器349は、方向性結合器348が有する配線部350、351、352、353、354、355、356と対向する配線部を有していると共に、配線部355に対向する配線部の先端から左側に僅かに延長された配線部359及び配線部356に対向する配線部から右側に僅かに延長された配線部360を有している。

そして、スルーホール361を介して配線部359に接続された逆相送信デジタル信号取り出し電極362が正相送信デジタル信号取り出し電極357と同一面に設けられていると共に、スルーホール363を介して配線部360に接続された逆相送信デジタル信号取り出し電極364が正相送信デジタル信号取り出し電極358と同一面に設けられている。なお、図示は省略するが、方向性結合器348、349には受端終端抵抗が接続されている。

このように構成された本発明の第22参考例においては、信号配線345を左方向に伝送されてくる正相送信デジタル信号の基本周波数成分、第2高調波、第3高調波をそれぞれ方向性結合器348の配線部350、351、353で受信し、正相送信デジタル信号取り出し電極357から取り出すことができると共に、信号配線346を左方向に伝送されてくる逆相送信デジタル信号の基本周波数成分、第2高調波、第3高調波を方向性結合器348の配線部350、351、353と対向する方向性結合器349の配線部で受信し、逆相送信デジタル信号取り出し電極362から取り出すことができる。

また、信号配線345を右方向に伝送されてくる正相送信デジタル信号の基本周波数成分、第2高調波、第3高調波をそれぞれ方向性結合器348の配線部350、352、354で受信し、正相送信デジタル信号取り出し電極358から取り出すことができると共に、信号配線346を右方向に伝送されてくる逆相送信デジタル信号の基本周波数成分、第2高調波、第3高調波を方向性結合器348の配線部350、352、354と対向する方向性結合器349の配線部で受信し、逆相送信デジタル信号取り出し電極364から取り出すことができる。

したがって、本発明の第22参考例によれば、差動レシーバの正相入力端子を正相送信デジタル信号取り出し電極357、358に接続すると共に、差動レシーバの逆相入力端子を逆相送信デジタル信号取り出し電極362、364に接続することにより、信号配線ペア344を双方向に伝送される高速相補送信デジタル信号、たとえば、1GHz以上の高速相補送信デジタル信号の受信を容易に行うことができる。