EP1239603A1 - Circuit d'excitation d'un amplificateur de puissance et procédé d'utilisation - Google Patents

Circuit d'excitation d'un amplificateur de puissance et procédé d'utilisation Download PDFInfo

- Publication number

- EP1239603A1 EP1239603A1 EP01400637A EP01400637A EP1239603A1 EP 1239603 A1 EP1239603 A1 EP 1239603A1 EP 01400637 A EP01400637 A EP 01400637A EP 01400637 A EP01400637 A EP 01400637A EP 1239603 A1 EP1239603 A1 EP 1239603A1

- Authority

- EP

- European Patent Office

- Prior art keywords

- coupled

- signal

- receive

- power

- power amplifier

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000000034 method Methods 0.000 title claims description 7

- 238000001514 detection method Methods 0.000 claims abstract description 38

- 238000006243 chemical reaction Methods 0.000 claims abstract description 23

- 230000005540 biological transmission Effects 0.000 claims description 29

- 230000004044 response Effects 0.000 claims description 6

- 230000010354 integration Effects 0.000 abstract description 2

- 239000003990 capacitor Substances 0.000 description 19

- 238000004891 communication Methods 0.000 description 14

- 101000806846 Homo sapiens DNA-(apurinic or apyrimidinic site) endonuclease Proteins 0.000 description 12

- 101000835083 Homo sapiens Tissue factor pathway inhibitor 2 Proteins 0.000 description 12

- 102100026134 Tissue factor pathway inhibitor 2 Human genes 0.000 description 12

- 239000004020 conductor Substances 0.000 description 12

- 238000010586 diagram Methods 0.000 description 11

- 101100219315 Arabidopsis thaliana CYP83A1 gene Proteins 0.000 description 5

- 101100269674 Mus musculus Alyref2 gene Proteins 0.000 description 5

- 101100140580 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) REF2 gene Proteins 0.000 description 5

- 230000004048 modification Effects 0.000 description 5

- 238000012986 modification Methods 0.000 description 5

- 238000005259 measurement Methods 0.000 description 4

- 238000009877 rendering Methods 0.000 description 4

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 238000001914 filtration Methods 0.000 description 2

- 230000003213 activating effect Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 230000010355 oscillation Effects 0.000 description 1

- 230000010363 phase shift Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04W—WIRELESS COMMUNICATION NETWORKS

- H04W52/00—Power management, e.g. TPC [Transmission Power Control], power saving or power classes

- H04W52/04—TPC

- H04W52/52—TPC using AGC [Automatic Gain Control] circuits or amplifiers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03G—CONTROL OF AMPLIFICATION

- H03G3/00—Gain control in amplifiers or frequency changers

- H03G3/20—Automatic control

- H03G3/30—Automatic control in amplifiers having semiconductor devices

- H03G3/3036—Automatic control in amplifiers having semiconductor devices in high-frequency amplifiers or in frequency-changers

- H03G3/3042—Automatic control in amplifiers having semiconductor devices in high-frequency amplifiers or in frequency-changers in modulators, frequency-changers, transmitters or power amplifiers

- H03G3/3047—Automatic control in amplifiers having semiconductor devices in high-frequency amplifiers or in frequency-changers in modulators, frequency-changers, transmitters or power amplifiers for intermittent signals, e.g. burst signals

Definitions

- the present invention relates in general to power amplifier drivers and, more particularly, to power amplifier drivers for use in wireless circuitry exhibiting high bandwidth at low power consumption.

- the transmitted signal amplitude needs to be accurately controlled to cope with existing standards. Due to manufacturing and environment variations, it is very difficult to control the amplifier's output power without any feedback, therefore, feedback is generally used to provide transmitted power control.

- the feedback may be realized by measuring the output power or any other parameter reflecting the output power level. The measured value is compared to a reference level and an error correction is subsequently applied to the gain control of the power amplifier to adjust the transmitted signal amplitude.

- the negative feedback loop allows an accurate power control as long as the measurement device and the comparison device are accurate too. Furthermore, a high gain should exist to ensure that the measurement result is actually very close to the reference, but low enough such that the control loop maintains stability.

- a power detector connected to the power amplifier output through a directional coupler often realizes the power measurement.

- a differential amplifier realizes the signal comparison and provides the requested high gain.

- the implementation is not sufficient, however, to insure stability.

- the power amplifier, the detector and the differential amplifier are introducing cutoff frequencies and phase shifts, which could cause the system to become unstable. Since it is very difficult to remove cutoff frequencies introduced by the power amplifier, detector and signal comparator, an efficient solution is to create a dominant pole which gives the loop a first order behavior.

- the first order behavior is implemented using a low pass filter or by using an integrator to simultaneously create a very high open-loop gain and a dominant low frequency pole.

- the filter or integrator is commonly realized using operational amplifiers.

- TDMA Time Division Multiple Access

- RF Radio Frequency

- a simple solution is to add a fixed voltage before the transmission time slot to allow the system to quickly close the loop at the beginning of the ramp.

- the fixed voltage can be implemented with an operational amplifier or an acquisition device, which senses the power amplifier emission threshold.

- a TDMA transmission system 10 is illustrated.

- the TDMA communication device 12 generates a radio frequency (RF) signal and delivers the RF signal to power amplifier 14, which is subsequently provided to directional coupler 20.

- Directional coupler 20 provides both an RF signal to the antenna for long distance propagation and an RF signal to terminal RF for feedback information.

- the amplitude of the power provided to terminal RF is generally on the order of 30-40 dB lower than the power provided to the antenna. In other words, the power provided to terminal RF is 1000 to 10,000 times lower than the power provided to the antenna.

- a feedback path therefore, exists from the antenna input to the gain control pin, OUT, of power amplifier 14 via directional coupler 20 and power amplifier driver 16.

- the signal delivered to the antenna is monitored by power amplifier driver 16 and a gain control signal is delivered to power amplifier 14 via the OUT terminal, constituting feedback to control the output power level of power amplifier 14.

- a gain control signal is delivered to power amplifier 14 via the OUT terminal, constituting feedback to control the output power level of power amplifier 14.

- Several control signals are delivered by TDMA communication device 12 to power amplifier driver 16 via the V min , ON/OFF, GAIN and REF2 terminals explained hereinafter.

- Power amplifier driver 16 may be implemented as an integrated circuit, whereby the coupled RF signal is provided as feedback to pin RF via directional coupler 20, and the control voltage responsible for controlling the output power of power amplifier 14 is provided by pin OUT.

- TDMA specifications mandate that communication functions occur at specific time intervals.

- the time intervals are generally several microseconds in duration, for example 577 micro-seconds ( ⁇ s), and are repetitive, such that 8 separate time slots exist within a first data frame before the time slots repeat in subsequent data frames.

- One timeslot is generally allocated for transmission, one timeslot for reception and the remaining time slots allocated for overhead functions.

- TDMA communication device 12 must, therefore, provide control signal ON/OFF to power amplifier driver 16 so that power amplifier 14 is on during the transmission timeslot and off during the remaining 7 timeslots. ON/OFF control is required to keep spurious transmissions, during the remaining 7 timeslots, below a maximum level threshold.

- TDMA communication device 12 provides V min to power amplifier driver 16, which subsequently provides a power amplifier control voltage at terminal OUT such that power amplifier 14 is transmitting at just below the maximum output power allowable, P IDLE , just prior to the transmission timeslot or idle period.

- V min therefore, is said to place a bias on the gain control input to power amplifier 14, such that the output power level of power amplifier 14 is precisely at P IDLE , during idle or non-transmission timeslots.

- Power amplifier 14 exhibits non-linear power output versus input control voltage.

- the non-linear operation of power amplifier 14 presents a difficult problem of non-linear stability over the full range of output power for power amplifier 14.

- Terminal GAIN provides a programming terminal with which the closed loop stability of TDMA transmission system 10 is controlled.

- Terminal REF2 provides a method whereby TDMA communication device 12 can program the output power of power amplifier 14, during non-idle, or transmission timeslots.

- FIG. 2 illustrates the block diagram representation of power amplifier driver 16.

- Power detector 18 receives the RF feedback signal at terminal RF, which is representative of the RF signal sent to the antenna.

- Power detector 18 provides a detected power level at node DET and a reference level at node REF1 to integrator 22.

- the REF2 and GAIN terminals are coupled to integrator 22 to allow for output power control and loop stability performance control, respectively.

- Integrator 22 provides the integrated error signal at node 34 to minimum voltage adder 24.

- Minimum voltage adder 24 is coupled to receive an offset voltage at terminal V min .

- V min represents the voltage required to maintain a minimum operating output power level of power amplifier 14 resulting in a transmitted power level which is just below the maximum allowable transmitted power level, P IDLE , during idle timeslots.

- Buffer 26 provides a unity gain driver coupled to terminal OUT and also receives the ON/OFF control signal from TDMA communication device 12. Buffer 26 is implemented to provide sufficient current drive as required by power amplifier 14 during all timeslots. Control input from terminal ON/OFF allows the voltage at terminal OUT to correct the feedback control loop error signal developed by directional coupler 20 and power amplifier driver 16 when in the "on" state. Control input from terminal ON/OFF allows the control voltage at terminal OUT to effectively set the output power level of power amplifier 14 to zero when in the "off" state.

- FIG. 3 illustrates a detailed schematic of power detector 18.

- Node RF is coupled to receive the feedback signal, which is representative of the RF signal sent to the antenna for long distance transmission, at a first terminal of capacitor 48.

- a second terminal of capacitor 48 is coupled to a first terminal of resistor 42 and the anode of diode 46.

- the cathode of diode 46 is coupled to first terminals of resistor 54 and capacitor 56 at node DET.

- Second terminals of resistor 54 and capacitor 56 are coupled to a first power supply potential, for example, ground potential.

- a second terminal of resistor 42 is coupled to first terminals of resistor 36, resistor 40 and capacitor 38.

- a second terminal of resistor 36 is coupled to a second power supply potential, V cc .

- a second terminal of capacitor 38 is coupled to the first power supply potential, for example, ground potential.

- a second terminal of resistor 40 is coupled to the anode of diode 44.

- the cathode of diode 44 is coupled to first terminals of resistor 50 and capacitor 52 at node REF1.

- Second terminals of resistor 50 and capacitor 52 are coupled to the first power supply potential, for example, ground potential.

- Power detector 18 comprises a two stage detection circuit. The first stage comprising diode 46, resistor 54 and capacitor 56 and the second stage comprising diode 44, resistor 50 and capacitor 52.

- diodes 44 and 46 are implemented either using diode devices or transistors connected as diodes.

- a Field Effect Transistor (FET) for example, is diode connected by coupling the gate electrode to the drain electrode to form the anode of an equivalent diode.

- FET Field Effect Transistor

- power detector 18 receives an RF signal at node RF and performs amplitude demodulation of the RF signal.

- Capacitor 48 provides Alternating Current (AC) coupling to node RF such that no Direct Current (DC) content is allowed to be introduced into power detector 18.

- Diode 46 provides half wave rectification of the input signal present at node RF, thus providing peak detection, or amplitude detection, of the input signal.

- Resistor 54 and capacitor 56 combine to form an RC filter which acts to smooth the amplitude detection signal conducted by diode 46.

- a top rail power supply is coupled to node V cc which acts to properly forward bias diodes 46 and 44.

- Resistor pair 40 and 42, diode pair 44 and 46 and RC filter pair 50,52 and 54,56 are matched, such that the bias signal present at node REF1 is substantially equivalent to the bias signal present at node DET, in the absence of an RF signal present at node RF.

- V bias V cc -I d (R 36 +R 42 )-V 46 , where I 46 is the current conducted by diode 46, R 36 is the resistance value of resistor 36, R 42 is the resistance value of resistor 42 and V 46 is the voltage drop across diode 46 when diode 46 is forward biased. Since the paired components mentioned earlier are matched, V bias is substantially equivalent at nodes DET and REF1 in the absence of an RF signal present at node RF.

- node DET contains two signal components, V bias and V det

- node REF1 contains only the single component, V bias .

- V det is the smoothed, amplitude detection signal produced by diode 46, in combination with resistor 54 and capacitor 56, which is the representation of the peak RF signal present at node RF.

- Power detector 18, therefore, provides an accurate power detection signal representative of the power level present at terminal RF, by providing a differential output signal at terminals DET and REF1.

- the differential output signal at terminals DET and REF1 contain a common mode signal equal to V bias , which can be effectively removed by a differential amplifier, to provide a substantially error free detected output power level signal, V det , at the output of the differential amplifier.

- FIG. 4 illustrates a block diagram representation of integrator 22 as shown in FIG. 2.

- Integrator 22 comprises transconductance differential amplifiers 60 and 62.

- Transconductance differential amplifier 62 receives the detected amplitude of the input signal, V det , as received at node RF from power detector 18 at node DET.

- Transconductance amplifier 62 also receives the common mode signal from power detector 18 at node REF1, V bias .

- the common mode signal received at node REF1 is the DC bias signal produced by power detector 18 with no RF signal present at node RF.

- Transconductance differential amplifier 60 receives a second reference signal, REF2, produced by TDMA communication device 12.

- Programmable current mirrors 64 and 66 are coupled to receive the output of transconductance amplifiers 62 and 60, respectively. Programmable current mirrors 64 and 66 are coupled to node GAIN, which is under the control of TDMA communication device 12.

- the first conductor of capacitor 68 is coupled to the output of programmable current mirrors 64 and 66 and to the output of integrator 22 at node 34.

- the second conductor of capacitor 68 is coupled to the first power supply potential, for example, ground potential.

- the operation of transconductance amplifier 62 is to perform the voltage difference measurement and deliver the result in the form of a current. It can be said, therefore, that amplifier 62 performs in a current mode of operation to provide the voltage difference signal at node 61 in the form of a current signal.

- the output of transconductance amplifier 62 is a current signal, I 62 , which is a function of the difference voltage between V det and V bias , or V diff .

- the second input to transconductance amplifier 60 is coupled to ground potential, therefore, the output current of transconductance amplifier 60, I 60 , is referenced to the input voltage present at node REF2.

- Programmable current mirrors 64 and 66 provide currents at nodes 63 and 67, respectively, according to the current ratio setup within each current mirror.

- integrator 22 The second function of integrator 22 is to provide the operating bandwidth of the power control loop established by power amplifier driver 16. By establishing the correct operating bandwidth of the power control loop, system stability is guaranteed.

- An important feature of integrator 22 is the minimization of the error signal resulting from the comparison of V bias and V det by transconductance amplifier 62, due to the high gain exhibited by transconductance amplifier 62. As a result, power control accuracy is enhanced with minimal sacrifice to stability.

- the output current at node 34 serves to charge capacitor 68, thereby providing an error voltage across capacitor 68.

- the GAIN term represents the binary signal provided by TDMA communication device 12, which allows programming of programmable current mirrors 64 and 66, to change the output current mirror ratio from one ratio to a second ratio. Changing the output current mirror ratio allows modification of the control loop bandwidth without modification of passive device 68. Increasing the current ratio, for example, serves to increase the BW of the control loop providing faster loop operation. Allowing modification of the control loop bandwidth through the GAIN terminal is an important feature of integrator 22. Modification of the control bandwidth can be achieved without causing voltage glitches at the control terminal of power amplifier 14.

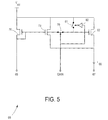

- FIG. 5 illustrates a schematic diagram of PMOS current mirror 66.

- the gate terminals of PMOS transistors 76, 78 and a first conductor of switch 79 are coupled to a first conductor of transistor 76 at node 65.

- a second conductor of switch 79 is coupled to a first conductor of switch 81 and the gate terminal of transistor 82.

- the GAIN node is coupled to the control terminal of switch 79 and to the input to inverter 80.

- a first conductor of transistors 78 and 82 are coupled together at node 67 to provide the output current, I 66 , of PMOS current mirror 66.

- PMOS current mirror 66 receives an input current at node 65 from transconductance amplifier 60.

- a low gain condition is set when GAIN is at a logic low, rendering switch 81 in a closed position and switch 79 in an open position.

- Transistor 82 is rendered non-conductive, therefore, I 66 is a mirrored current generated by transistor 78 in relation to the ratio of geometries between transistor 78 to transistor 76. In other words, if the geometries of transistor 78 and transistor 76 are identical, current I 66 is identical to the current conducted by transistor 76.

- I 66 is set according to the ratio of geometries between transistor 78 and 76 in low gain mode.

- a high gain condition is set when GAIN is at a logic high, rendering switch 81 in an open position and switch 79 in a closed position.

- Transistor 82 is rendered conductive, therefore, I 66 is a mirrored current generated by transistors 78 and 82 in relation to the ratio of geometries between transistors 78 and 82 to transistor 76.

- current I 66 is identical to twice the amount of current conducted by transistor 76.

- I 66 is set according to relative geometries between transistors 78 and 82 to transistor 76 in high gain mode.

- FIG. 6 illustrates a schematic diagram of NMOS current mirror 64.

- the gate terminals of NMOS transistors 84, 86 and a first conductor of switch 87 are coupled to a first conductor of transistor 84 at node 61.

- a second conductor of switch 87 is coupled to a first conductor of switch 89 and to the gate terminal of transistor 90.

- the GAIN node is coupled to the control terminal of switch 87 and the input to inverter 88.

- a first conductor of transistors 86 and 90 are coupled together at node 63 to create the output current, I 64 , of NMOS current mirror 64.

- NMOS current mirror 64 receives an input current at node 61 from transconductance amplifier 62.

- a low gain condition is set when GAIN is at a logic low, rendering switch 89 in a closed position and switch 87 in an open position.

- Transistor 90 is rendered non-conductive, therefore, I 64 is a mirrored current generated by transistor 86 in relation to the ratio of geometries between transistor 86 to transistor 84. In other words, if the geometries of transistor 84 and transistor 86 are identical, current I 64 is identical to the current conducted by transistor 84. I 64 is set according to the ratio of geometries between transistor 84 and 86 in low gain mode.

- a high gain condition is set when GAIN is at a logic high, rendering switch 89 in an open position and switch 87 in a closed position.

- Transistor 90 is rendered conductive, therefore, I 64 is a mirrored current generated by transistors 86 and 90 in relation to the ratio of geometries between transistors 86 and 90 to transistor 84.

- current I 64 is identical to twice the amount of current conducted by transistor 84.

- I 64 is set according to relative geometries between transistors 86 and 90 to transistor 84 in high gain mode.

- Minimum voltage adder 24 receives the output of integrator 22 at node 34, which represents the error voltage of the control loop, as discussed earlier.

- Minimum voltage adder comprises transconductance amplifiers 70 and 72 along with resistor 74.

- Transconductance amplifier 72 receives external control signal V min from TDMA communication device 12. The external control signal V min is then converted to a current by transconductance amplifier 72 and supplied to node 36.

- a first terminal of resistor 74 is coupled to terminal 36 and a second terminal of resistor 74 is coupled to the first power supply potential, for example, ground potential.

- Control signal V min provides a minimum control voltage level to power amplifier 14, such that the output power level of power amplifier 14 is just below the maximum allowable power level during idle timeslots, P IDLE .

- minimum voltage adder 24 receives the error voltage, V error , and the external control voltage, V min , and converts the error voltage and external control voltage to a current .

- the current signals are summed at node 36 and are subsequently converted back into voltage by the operation of resistor 74.

- the voltage at node 36 is characterized by where the summation of voltages, V 1 , represents the summation of V error and V min and 1/R is the transconductance term of transconductance amplifiers 70 and 72.

- R 74 is the resistance value of resistor 74.

- a buffer is required between minimum voltage adder 24 and the control input to power amplifier 14.

- Buffer 26 is therefore placed between the output of minimum voltage adder 24 and the control input of power amplifier 14, so that the current required by the control input of power amplifier 14 can be sourced by buffer 26.

- An input control terminal, ON/OFF, is provided by buffer 26. Terminal ON/OFF is controlled by TDMA communication device 12 in order to control the output power level of power amplifier 14.

- TDMA communication device 12 programs the ON/OFF terminal to the "on" state, thereby allowing buffer 26 to propagate the control voltage from minimum voltage adder 24 at node 36 to the control terminal of power amplifier 14 through node OUT.

- TDMA communication device 12 programs power amplifier 14 to the "off" state by activating the OFF control signal at terminal ON/OFF.

- Programming buffer 26 to the OFF state prohibits the control voltage at node 36 to propagate to power amplifier 14, thereby reducing the output power level of power amplifier 14 to a minimum value.

- a power amplifier driver for a time division multiple access transmission device, the power amplifier driver providing a control signal in response to an error signal, the power amplifier driver comprising a detector having an input coupled to receive a signal representative of a transmission level and coupled to provide a detector signal operating in a first mode; an error generator coupled to receive the detector signal and a reference signal and coupled to provide a difference signal operating in a second mode to control the transmission level.

- the detector comprises a first detection stage having an input coupled to receive the signal representative of the transmission level, a power supply input coupled to receive a first supply potential and an output coupled to provide the detector signal; and a second detection stage having a power supply input coupled to receive the first supply potential and an output coupled to provide a reference signal.

- the first detection stage comprises a rectifier having an input coupled to receive the signal representative of the transmission level; and a filter having an input coupled to an output of the diode and an output coupled to provide the detector signal.

- the second detection stage comprises a rectifier having an input coupled to receive the first supply potential; and a filter having an input coupled to an output of the diode and an output coupled to provide the reference signal.

- the error generator comprises a first conversion device coupled to receive the reference signal and having an output coupled to a first node; a second conversion device coupled to receive the detector signal and having an output coupled to the first node; and a gain control device having an input coupled to the first node, a control input coupled to receive a gain control signal and coupled to provide the difference signal.

- the first conversion device includes a transconductance amplifier having a first input coupled to receive the reference signal, a second input coupled to a first supply potential, a first output coupled to the first node and a second output coupled to the first supply potential.

- the second conversion device includes a transconductance amplifier having a first input coupled to receive the detector signal, a second input coupled to a first supply potential, a first output coupled to the first node and a second output coupled to the first supply potential.

- the gain control device includes a programmable current mirror coupled to receive the gain control signal.

- a power amplifier driver operative to control a transmission level of a power amplifier between first and second levels

- the power amplifier driver comprising a first conversion circuit coupled to receive a first feedback signal in a first mode indicative of the first level and coupled to convert the first feedback signal to a second feedback signal in a second mode; and a second conversion circuit coupled to receive the second feedback signal and a bias signal indicative of the second level and coupled to provide a control signal indicative of the first and second levels at a first node.

- the first conversion circuit comprises a power detector coupled to receive the first feedback signal; and an integrator coupled to receive the first and second outputs of the power detector and coupled to convert the first feedback signal to the second feedback signal.

- the power detector comprises a first detection stage having an input coupled to receive the first feedback signal, a power supply input coupled to receive a first supply potential and an output coupled to provide a detection signal; and a second detection stage having a power supply input coupled to receive the first supply potential and an output coupled to provide a reference signal.

- the first detection stage comprises a rectifier having an input coupled to receive the first feedback signal; and a filter having an input coupled to an output of the diode and an output coupled to provide the detection signal.

- the second detection stage comprises a rectifier having an input coupled to receive the first supply potential; and a filter having an input coupled to an output of the diode and an output coupled to provide the reference signal.

- the integrator comprises a first conversion device coupled to receive the first power detector output and having an output coupled to a first node; a second conversion device coupled to receive the second power detector output and having an output coupled to the first node; and a gain control device having an input coupled to the first node, a control input coupled to receive a gain control signal.

- the first conversion device includes a transconductance amplifier having a first input coupled to receive the first power detector output, a second input coupled to a first supply potential, a first output coupled to the first node and a second output coupled to the first supply potential.

- the second conversion device includes a transconductance amplifier having a first input coupled to receive the second power detector output, a second input coupled to a first supply potential, a first output coupled to the first node and a second output coupled to the first supply potential.

- the gain control device includes a programmable current mirror coupled to receive the gain control signal.

- the second conversion circuit comprises a first transconductance amplifier having a first input coupled to receive a second feedback signal, a second input coupled to a first supply potential, a first output coupled to the first node and a second output coupled to the first supply potential; and a second transconductance amplifier having a first input coupled to receive the bias signal, a second input coupled to the first supply potential, a first output coupled to the first node and a second output coupled to the first supply potential.

- an integrated circuit containing a power amplifier driver receiving a feedback signal at a first pin and providing a control signal at a second pin to control a transmitted power level

- the integrated circuit comprising an integrator having a first input coupled to receive a detection voltage indicative of a first level, a second input coupled to receive a gain voltage and an output coupled to provide a transconductance error signal; and a summing device coupled to receive the transconductance error signal and a bias signal and coupled to provide the control signal in response to the error and bias signals.

- the integrator comprises a conversion device coupled to receive the detection voltage and having an output coupled to a first node; and a gain control device having an input coupled to the first node and a control input coupled to receive the gain voltage.

- the conversion device includes a transconductance amplifier having a first input coupled to receive the detection voltage, a second input coupled to a first supply potential, a first output coupled to the first node and a second output coupled to the first supply potential.

- the gain control device includes a programmable current mirror.

- the summing device comprises a first transconductance amplifier having a first input coupled to receive the transconductance error signal, a second input coupled to a first supply potential, a first output coupled to a first node and a second output coupled to the first supply potential; and a second transconductance amplifier having a first input coupled to receive the bias signal, a second input coupled to a first supply potential, a first output coupled to the first node and a second output coupled to the first supply potential.

- a method of operating a power amplifier driver to generate a drive signal for a power amplifier comprising generating a detection signal in response to a feedback signal; converting the detection signal from a first state to a second state; summing the detection signal with a first bias signal to produce an error signal; and converting the error signal from the second state to the first state to produce the drive signal.

- generating the detection signal comprises generating an amplitude detected signal; and filtering the amplitude detected signal.

- converting the detection signal comprises using a transconductance amplifier to convert the detection signal from a voltage to a current.

- converting the error signal from a current to a voltage using an electric field storage device Preferably, converting the error signal from a current to a voltage using an electric field storage device.

- detecting the output power comprises generating an amplitude detected signal; filtering the amplitude detected signal; and converting the amplitude detected signal to a current using a transconductance amplifier.

- converting the control current to voltage comprises storing the control current in an electric field storage device.

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Amplifiers (AREA)

- Transmitters (AREA)

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE60142427T DE60142427D1 (de) | 2001-03-09 | 2001-03-09 | Treiber für Leistungsverstärker und Betriebsverfahren |

| EP20010400637 EP1239603B1 (fr) | 2001-03-09 | 2001-03-09 | Circuit d'excitation d'un amplificateur de puissance et procédé d'utilisation |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP20010400637 EP1239603B1 (fr) | 2001-03-09 | 2001-03-09 | Circuit d'excitation d'un amplificateur de puissance et procédé d'utilisation |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| EP1239603A1 true EP1239603A1 (fr) | 2002-09-11 |

| EP1239603B1 EP1239603B1 (fr) | 2010-06-23 |

Family

ID=8182652

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| EP20010400637 Expired - Lifetime EP1239603B1 (fr) | 2001-03-09 | 2001-03-09 | Circuit d'excitation d'un amplificateur de puissance et procédé d'utilisation |

Country Status (2)

| Country | Link |

|---|---|

| EP (1) | EP1239603B1 (fr) |

| DE (1) | DE60142427D1 (fr) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009032573A2 (fr) * | 2007-08-28 | 2009-03-12 | Texas Instruments Incorporated | Circuit et procédé de réduction de largeur de bande en mode commun pour des applications différentielles |

| US20160214140A1 (en) * | 2014-03-11 | 2016-07-28 | Texas Instruments Incorporated | Drivers and Methods of Driving Transducers |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5150075A (en) * | 1991-06-03 | 1992-09-22 | Motorola, Inc. | Power amplifier ramp up method and apparatus |

| US5448770A (en) * | 1993-04-05 | 1995-09-05 | Motorola, Inc. | Temperature-coefficient controlled radio frequency signal detecting circuitry |

-

2001

- 2001-03-09 DE DE60142427T patent/DE60142427D1/de not_active Expired - Lifetime

- 2001-03-09 EP EP20010400637 patent/EP1239603B1/fr not_active Expired - Lifetime

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5150075A (en) * | 1991-06-03 | 1992-09-22 | Motorola, Inc. | Power amplifier ramp up method and apparatus |

| US5448770A (en) * | 1993-04-05 | 1995-09-05 | Motorola, Inc. | Temperature-coefficient controlled radio frequency signal detecting circuitry |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009032573A2 (fr) * | 2007-08-28 | 2009-03-12 | Texas Instruments Incorporated | Circuit et procédé de réduction de largeur de bande en mode commun pour des applications différentielles |

| WO2009032573A3 (fr) * | 2007-08-28 | 2009-05-07 | Texas Instruments Inc | Circuit et procédé de réduction de largeur de bande en mode commun pour des applications différentielles |

| US7626458B2 (en) | 2007-08-28 | 2009-12-01 | Texas Instruments Incorporated | Common-mode bandwidth reduction circuit and method for differential applications |

| US20160214140A1 (en) * | 2014-03-11 | 2016-07-28 | Texas Instruments Incorporated | Drivers and Methods of Driving Transducers |

| US10173243B2 (en) * | 2014-03-11 | 2019-01-08 | Texas Instruments Incorporated | Transducer driver attenuating input current frequency at maximum mechanical output |

Also Published As

| Publication number | Publication date |

|---|---|

| DE60142427D1 (de) | 2010-08-05 |

| EP1239603B1 (fr) | 2010-06-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5852770A (en) | Transmission power control device for a portable terminal | |

| US6301486B1 (en) | Radio telephone apparatus | |

| US6784750B2 (en) | Transimpedance amplifier with selective DC compensation | |

| US7091793B2 (en) | Variable decision threshold apparatus | |

| KR19990073978A (ko) | 이동통신 단말기의 전원공급방법 및 장치 | |

| EP2096753A1 (fr) | Switching amplifier | |

| GB2259782A (en) | Detecting RF signals | |

| EP1215816A2 (fr) | Commande de puissance pour modulation d'amplitude | |

| KR100665590B1 (ko) | 전력 증폭기 회로와 안정화기 회로를 구비하는 무선 주파수 장치와, 이러한 장치를 구비하는 이동 트랜시버 단말기 | |

| US7105797B2 (en) | Optical receiving circuit | |

| EP0376555A2 (fr) | Méthode et circuits de réglage d'un laser | |

| WO1998044628A1 (fr) | Circuit et procede d'etalonnage de puissance | |

| JPH06167517A (ja) | コンパレータ回路 | |

| JPH0449298B2 (fr) | ||

| US6744313B2 (en) | Power amplifier driver and method of using | |

| US7782133B2 (en) | Power amplifier with output power control | |

| KR900007034B1 (ko) | 가변전자 임피던스 회로장치 | |

| EP1239603B1 (fr) | Circuit d'excitation d'un amplificateur de puissance et procédé d'utilisation | |

| US6369635B2 (en) | Temperature-compensated diode rectifier circuit for an HF level controller | |

| US7110724B1 (en) | System and method for detecting compression of a power amplifier circuit | |

| AU644544B2 (en) | Amplifier with multiple switched stages and noise suppression | |

| US12068787B1 (en) | Laser signal transmission system | |

| JPH06152288A (ja) | 電力制御装置 | |

| KR20030026897A (ko) | 선형 전력 변환 회로 | |

| JPS6319101B2 (fr) |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PUAI | Public reference made under article 153(3) epc to a published international application that has entered the european phase |

Free format text: ORIGINAL CODE: 0009012 |

|

| AK | Designated contracting states |

Kind code of ref document: A1 Designated state(s): AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE TR |

|

| AX | Request for extension of the european patent |

Free format text: AL;LT;LV;MK;RO;SI |

|

| 17P | Request for examination filed |

Effective date: 20030307 |

|

| AKX | Designation fees paid |

Designated state(s): DE FI FR |

|

| 17Q | First examination report despatched |

Effective date: 20060608 |

|

| GRAP | Despatch of communication of intention to grant a patent |

Free format text: ORIGINAL CODE: EPIDOSNIGR1 |

|

| RIC1 | Information provided on ipc code assigned before grant |

Ipc: H04W 52/52 20090101AFI20100128BHEP |

|

| GRAS | Grant fee paid |

Free format text: ORIGINAL CODE: EPIDOSNIGR3 |

|

| GRAA | (expected) grant |

Free format text: ORIGINAL CODE: 0009210 |

|

| AK | Designated contracting states |

Kind code of ref document: B1 Designated state(s): DE FI FR |

|

| REF | Corresponds to: |

Ref document number: 60142427 Country of ref document: DE Date of ref document: 20100805 Kind code of ref document: P |

|

| PLBE | No opposition filed within time limit |

Free format text: ORIGINAL CODE: 0009261 |

|

| STAA | Information on the status of an ep patent application or granted ep patent |

Free format text: STATUS: NO OPPOSITION FILED WITHIN TIME LIMIT |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: FI Payment date: 20110301 Year of fee payment: 11 Ref country code: FR Payment date: 20110304 Year of fee payment: 11 |

|

| 26N | No opposition filed |

Effective date: 20110324 |

|

| REG | Reference to a national code |

Ref country code: DE Ref legal event code: R097 Ref document number: 60142427 Country of ref document: DE Effective date: 20110323 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: FI Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20120309 |

|

| REG | Reference to a national code |

Ref country code: FR Ref legal event code: ST Effective date: 20121130 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: FR Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20120402 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: DE Payment date: 20140331 Year of fee payment: 14 |

|

| REG | Reference to a national code |

Ref country code: DE Ref legal event code: R119 Ref document number: 60142427 Country of ref document: DE |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: DE Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20151001 |