EP1192786B1 - Adaptable line driver interface for digital telephone systems - Google Patents

Adaptable line driver interface for digital telephone systems Download PDFInfo

- Publication number

- EP1192786B1 EP1192786B1 EP00946779A EP00946779A EP1192786B1 EP 1192786 B1 EP1192786 B1 EP 1192786B1 EP 00946779 A EP00946779 A EP 00946779A EP 00946779 A EP00946779 A EP 00946779A EP 1192786 B1 EP1192786 B1 EP 1192786B1

- Authority

- EP

- European Patent Office

- Prior art keywords

- interface

- pbx

- line driver

- signal

- driver interface

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000000034 method Methods 0.000 claims description 17

- 230000005540 biological transmission Effects 0.000 claims description 7

- 230000008859 change Effects 0.000 claims description 7

- 230000001419 dependent effect Effects 0.000 claims description 4

- 238000012544 monitoring process Methods 0.000 claims 1

- 238000010586 diagram Methods 0.000 description 20

- 239000003990 capacitor Substances 0.000 description 10

- 238000004804 winding Methods 0.000 description 8

- 238000004891 communication Methods 0.000 description 7

- 230000004044 response Effects 0.000 description 6

- 239000011159 matrix material Substances 0.000 description 5

- 230000008901 benefit Effects 0.000 description 4

- 230000003111 delayed effect Effects 0.000 description 4

- 230000008878 coupling Effects 0.000 description 3

- 238000010168 coupling process Methods 0.000 description 3

- 238000005859 coupling reaction Methods 0.000 description 3

- 238000012360 testing method Methods 0.000 description 3

- 238000013459 approach Methods 0.000 description 2

- 238000004364 calculation method Methods 0.000 description 2

- 238000001514 detection method Methods 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- 230000011664 signaling Effects 0.000 description 2

- 238000012935 Averaging Methods 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 238000013519 translation Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/66—Arrangements for connecting between networks having differing types of switching systems, e.g. gateways

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04M—TELEPHONIC COMMUNICATION

- H04M1/00—Substation equipment, e.g. for use by subscribers

- H04M1/24—Arrangements for testing

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04M—TELEPHONIC COMMUNICATION

- H04M3/00—Automatic or semi-automatic exchanges

- H04M3/42—Systems providing special services or facilities to subscribers

- H04M3/42314—Systems providing special services or facilities to subscribers in private branch exchanges

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04M—TELEPHONIC COMMUNICATION

- H04M3/00—Automatic or semi-automatic exchanges

- H04M3/42—Systems providing special services or facilities to subscribers

- H04M3/42314—Systems providing special services or facilities to subscribers in private branch exchanges

- H04M3/42323—PBX's with CTI arrangements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04M—TELEPHONIC COMMUNICATION

- H04M19/00—Current supply arrangements for telephone systems

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04M—TELEPHONIC COMMUNICATION

- H04M3/00—Automatic or semi-automatic exchanges

- H04M3/22—Arrangements for supervision, monitoring or testing

- H04M3/2272—Subscriber line supervision circuits, e.g. call detection circuits

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04M—TELEPHONIC COMMUNICATION

- H04M3/00—Automatic or semi-automatic exchanges

- H04M3/22—Arrangements for supervision, monitoring or testing

- H04M3/26—Arrangements for supervision, monitoring or testing with means for applying test signals or for measuring

- H04M3/28—Automatic routine testing ; Fault testing; Installation testing; Test methods, test equipment or test arrangements therefor

- H04M3/30—Automatic routine testing ; Fault testing; Installation testing; Test methods, test equipment or test arrangements therefor for subscriber's lines, for the local loop

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04M—TELEPHONIC COMMUNICATION

- H04M3/00—Automatic or semi-automatic exchanges

- H04M3/22—Arrangements for supervision, monitoring or testing

- H04M3/26—Arrangements for supervision, monitoring or testing with means for applying test signals or for measuring

- H04M3/28—Automatic routine testing ; Fault testing; Installation testing; Test methods, test equipment or test arrangements therefor

- H04M3/30—Automatic routine testing ; Fault testing; Installation testing; Test methods, test equipment or test arrangements therefor for subscriber's lines, for the local loop

- H04M3/305—Automatic routine testing ; Fault testing; Installation testing; Test methods, test equipment or test arrangements therefor for subscriber's lines, for the local loop testing of physical copper line parameters, e.g. capacitance or resistance

Definitions

- This invention relates to the art of telephone systems, and more particularly to a new and improved system and method for automatically configuring a digital telephone computer/telephony interface.

- PBX private branch exchange

- the PBX is connected between the central office switch and the individual telephone stations.

- a computer/telephony integration a computer is connected to one of the station lines to emulate the telephone terminals with the end result of controlling most of the features offered by the PBX through the computer interface.

- the computer/telephony interface must be configured to meet the characteristics of the PBX.

- this has been accomplished by providing different hardware modules for each type of PBX and selecting the modules by relay systems or the like.

- This approach undesirably is hardware dependent, can require a large number of components if many different types of PBXs are to be accommodated, and typically is restricted to a certain range of loop lengths, i.e. line distance from the PBX.

- the present invention provides a universal line driver interface which enables a digital telephone computer/telephony interface to configure itself automatically or on the fly to accommodate different PBXs.

- the interface is connected to a PBX and to a digital telephone.

- the interface also is connected to network interface logic.

- a microcontroller which is part of the computer in the computer telephony system, is connected in controlling relation to the interface and to the interface logic.

- the microcontroller under program control changes operational parameters in the interface as a function of electrical characteristics of the particular type of PBX to which the interface is connected.

- the changes in operation parameters of the interface are used to configure the interface logic depending upon the type of PBX.

- the universal nature of the interface is achieved by adaptability to different transmission and receiver voltage levels and an ability to match a range of telephone line impedances.

- a PBX 12 stands between a Central/Public Office (CO) switch 14 and the individual stations, two of which are designated 16 and 18 in Fig. 1 .

- the CO trunk 20 connects the CO switch 14 to the PBX 12 and can involve one of several types of communication protocols and/or methods.

- Each station line 22 and 24 is the communication line between the PBX 12 and the individual station telephones 16 and 18, respectively. Each station line also can use one of various communication methods.

- the PBX 12 stands between the CO switch 14 and the telephones 16, 18, it can provide electrical and signaling isolation between the two of them. Because of this, the communication standards between the PBX 12 and the CO switch 14 and those between the telephones 16, 18 and the PBX 12 do not necessarily have to be identical. It is the PBX 12 that performs the "translation" between them. The communication protocols between the CO switch 14 and the PBX 12 are and always have been open standards. On the other hand, the station 16, 18 to PBX 12 communication protocols historically have been proprietary protocols.

- a computer 30 is connected to one of the station lines to emulate the telephone terminals with the end result of controlling most of the features offered by the PBX through the computer interface.

- computer/telephony interface 32 is connected to station line 34 and is connected to a digital telephone set 36 by line 38.

- the computer/telephony interface 32 "opens up" the proprietary signaling protocols of the PBX. By emulating the telephone terminals it is possible to fool the PBX 12' into thinking that it is connected to one of them. Once this is done, it is possible to control most of the features offered by the PBX 12' through the computer/telephony interface 32.

- the computer/telephony interface 32 shown in Fig. 2 is of the type commercially available from Voice Technologies Group of Buffalo, New York under the designation VoiceBridge PC.

- computer/telephony interface 32 uses digital phone emulation to provide a direct digital connection between PBX 12' and computer 30. Once computer/telephony interface 32 convinces PBX 12' that it is a proprietary digital phone, computer/telephony interface 32 accepts all the information the PBX 12' gives it and transforms that information to a standard application program interface (API) command set.that the computer telephony system can understand. This, in term, increases the amount of call information and signals available to the system from PBX 12'.

- API application program interface

- Fig. 3 illustrates one form of arrangement for use in computer telephony systems and including separate line driver/receiver interface analog sections for digital telephones with different formats and specifications.

- the arrangement of Fig. 3 enables a computer telephony system of the type shown in Fig. 2 to operate with different varieties of PBX.

- PBX there are three line driver/receiver interface analog sections, i.e. logic sections, 44, 46 and 48 corresponding to three different types of PBX: A, B and C, respectively.

- types A, B and C could be Lucent, Northern Telecom and Rolm, respectively.

- a PBX 50 similar to PBX 12 of Figs.

- 1 and 2 has a standard digital line 54 which connects PBX 50 to a user's telephone network.

- Line 54 is connected via a standard RJ45 connector 58 to a relay matrix 60 which, in turn, is connected to logic sections 44, 46 and 48.

- a control signal on line 62 or other appropriate command causes relay matrix 60 to connect PBX 50 to the appropriate one of logic sections 44, 46 or 48 depending upon which type PBX 50 is, i.e., type A, B or C in the present illustration Logic, which corresponds to the particular logic section 44, 46 or 48, is downloaded from a controller 68 to a network interface 66 which is a component of the computer/telephony interface 32 in the system of Fig. 2 .

- Network interface 66 also is known as a telephony programmable gate array. Controller 68 controls operation of interface 66.

- a digital telephone 70 similar to phone 36 in Fig. 2 is connected via line 52 to a standard RJ45 connector 56 to the relay matrix 60.

- this telephone line 52 is connected through the matrix 60 to a logic section 44,46 or 48 and to the network interface logic 66.

- the controller 68 controls this connection to the telephone 70 in a similar fashion as it controls the connection to the PBX 50.

- system 86 of the present invention includes a universal line driver interface 82 which enables a digital telephone computer/telephony interface to configure itself automatically or on the fly to accommodate different PBXs.

- Universal line driver interface 82 is connected to PBX 50' and to digital telephone 70'.

- Universal line driver interface 82 also is connected to network interface logic 66'.

- a microcontroller 84 which is part of the computer in the computer telephony system, is connected in controlling relation to Universal line driver interface 82 and to interface logic 66'.

- Microcontroller 84 under program control changes operational parameters in universal line driver interface 82 as a function of electrical characteristics of the particular type of PBX to which universal line drive interface 82 is connected.

- Microcontroller 84 under program control changes the operational parameters in the network interface logic 66' also as a function of electrical characteristics of the particular type of PBX to which universal line driver interface 82 is connected.

- the universal nature of universal line driver interface 82 is achieved by adaptability to different transmission and receiver voltage levels and an ability to match a range of telephone line impedances, all of which will be described in detail presently.

- the system of the present invention shown in Fig. 4 advantageously has fewer components thereby resulting in reduced board size and lower cost.

- PBX 50 is to be changed, i.e. from Lucent to Rolm, for example, the circuit of Fig. 4 advantageously need not be changed.

- the reconfiguration to accommodate the different PBX is done in software via microcontroller 84 rather than by changing or adding hardware.

- the system of Fig. 3 is designed for a given range of loop lengths, i.e. distance to PBX along lines 52

- the system of the present invention shown in Fig. 4 can accommodate significantly different loop lengths.

- Fig. 4 While the system of Fig. 4 is illustrated with a single PBX 50' and a single set 70', it is within the scope of the present invention to employ the system of Fig. 4 with a plurality of switches or PBXs 50', with a plurality of sets 70' and with both a plurality of PBXs 50' and a plurality of sets 70'. There may be situations where the system of the present invention is utilized only with a switch or PBX 50', i.e. with one or more switches or PBXs 50' as shown in Fig. 4 , and with no telephone set.

- the system of the present invention including network interface logic 66', universal line driver interface 82 and microcontroller 84 is represented generally at 86.

- control interface 88 can be another telephone set, a modem or a handset.

- Universal line driver interface 82 includes a pair of transmit/receiver interface sections 92 and 94, one for the PBX side the other for the set side. Each section includes a special purpose analog duplexer for separating transmitted and received signals. In particular, each section includes a receiver portion and a transmitter portion with a nulling circuit in the receiver portion to null the transmitting signal in the receiver portion.

- Microcontroller 84 monitors signals in both interface sections 92 and 94 via paths 96 and 98, respectively, and sends control signals via paths 100 and 102 to interface sections 92 and 94, respectively, to make the appropriate changes in parameters therein depending upon characteristics of the particular PBX to which interface 82 is connected.

- microcontroller 84 monitors analog signals in interface sections 92 and 94 including peak null voltages, peak signal levels, averaged and offset voltages as will be described in detail presently.

- microcontroller 84 sends command signals to interface sections 92 and 94 to control nulling voltages in the receiver nulling sections, to adjust threshold voltages in comparators included in the receiver sections and to adjust transmit signal levels in the transmitter sections, all of which will be described in detail presently.

- microcontroller 84 monitors the signal levels in interface sections 92, 94 and periodically adjusts digital potentiometer or the like in the circuits of interface sections 92, 94 to change the signals to the desired levels in a manner which will be described. Accordingly, the system of the present invention provides automatic matching to a range of line impedances, using nulling circuits in interface sections 92, 94 under control of microcontroller 84. This allows minimization of line return loss and interference between transmitted and received signal. Each nulling signal is adjusted by transmitting a signal with no other receiver signal present and nulling the receiver signal as sensed by peak signal readers, all of which will be described in detail presently.

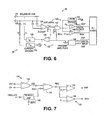

- Fig. 6 is a block diagram of one of the transmit/receiver interface sections, for example interface section 92 on the PBX side, it being understood that the other interface section 94 on the set side is identical.

- Interface 92 includes a receiver and nulling section 120 and a transmitter section 122. Both sections 120 and 122 are connected to PBX 50' by a balanced line pair 124, 126.

- the receiver section 120 has an input coupled to lines 124, 126 and includes an AC-coupled differential amplifier 130. After nulling of the transmitting signal by a duplexer including another difference amplifier 134, the received signal is detected by a pair of comparators 136 and 138.

- One comparator 136 detects positive received pulses above an adjustable threshold, and the other comparator 138 similarly detects the negative pulses.

- a peak reader 140 is operatively associated with comparators 136 and 138 in a manner which will be described.

- the receiver outputs (RXP and RXN) are standard digital levels, as are the corresponding transmit inputs (TXP and TXN).

- the transmit input pulses TXP and TXN are converted to adjustable amplitude positive and/or negative pulses by a bipolar driver 144.

- the signal is sent to current drivers 150 and 152.

- One driver 150 produces a positive current (+I.) for a positive transmitting pulse, and the other driver 152 simultaneously procedures an equal amplitude negative pulse (-I.).

- the pair of + and - current sources 150 and 152 (+I. and -I.) are a balanced transmitting source for the balanced line 124, 126 even though the two current drivers 150, 152 are individually unbalanced or ground-referenced.

- the current drivers 150, 152 are constant current sources that output a current (I.) proportional to the input voltage.

- An ideal current driver produces a constant output current independent of the load impedance or output voltage.

- a current driver has a voltage limit or range (e.g., -10 to +10 volts). It is modeled by a current source with a shunt resistor (e.g. 1K) in parallel.

- Tx/Rx interface 92 for the PBX side and another 94 for the set side.

- interface 94 would be identical to interface 92 but with balanced lines 124, 126 connected to set 70.

- the duplexer or transmit null circuit principle is similar to that described in Appendix A. It is adjusted by transmitting a signal with no other receiver signal present and nulling the receiver signal as sensed by the peak readers 140.

- One advantage of this approach is that the circuit can adapt to actual, rather than just nominal, line impedances over a wide range so that the nulling will be more effective.

- the adjustable operation parameters are implemented by devices such as digital potentiometers in the circuits 92 and 94 controlled by microcontroller 84 in a manner which will be described.

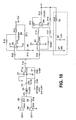

- the receiver and nulling section 120 of interface section 92 is illustrated further in Fig. 7 .

- the circuit includes the input amplifier 130, nulling circuit including transmit null amplifier 160 and difference amplifier 134, and threshold comparators 136, 138.

- the input signals from the line coupler section (impedance or transformer as will be described), labeled LN+ and LN-, are nominally balanced with respect to ground. Typically they are pulses of either polarity in the range of 0.3 to 3 volts peak and 0.5 to 10 ⁇ s wide.

- the line impedance is nominally 100 ohms but may be higher, perhaps up to 200 ohms.

- the receiver and nulling section of interface section 94 is identical to that shown in Fig. 7 except that the input signals LN+ and LN- are from set 70' rather than from PBX 50'.

- the input stage is a differential amplifier 170 which converts the balanced signal to a single-ended signal (pulses) with respect to ground. It may provide gain, as needed for subsequent stages, but in the circuit of Fig. 8 there is unity gain.

- Optional input capacitors 172, 174 (Cl, C2) act as a high pass filter with resistors 176, 178 (R 1 , R 2 ) to limit the low frequency response and block dc if needed.

- An operational amplifier with good high-frequency response is needed (Gain-bandwidth product over 30 Mhz). The output of this stage is labeled SIG.

- the next stage (U2) is the nulling section of the duplexer and includes differential amplifier 186. Its main purpose is to cancel or null the signal on the line, and at the receiver input, due to its own transmitter section. To do this an equal magnitude, but opposite polarity, signal is applied to one input while the signal (SIG) from the input receiver amplifier 170 is applied to the other. The output of the stage (REC) is then the receiver signal (from the external transmitter connected to the line) but without its own transmitted signal (an undesirable interference).

- amplifier 186 sums the inputs applied to the negative input terminal thereof. In the circuit shown, the gain is unity on both inputs but these may be changed to suit the signal levels for the next stage (comparators). Also additional high frequency filtering is provided by the feedback capacitor 190 (C4).

- a second function for this circuit is to provide a positive offset voltage for the comparators. This is needed because the comparators selected do not allow a negative input while the signal has negative-going pulses. For example, the offset may be set to +2.0v with a signal swing from -1.0v (1v negative pulse) to +3.0 (1v positive pulse).

- Two comparators 194, 196 (U3A, U3C) are used, one to detect positive pulses and the other to detect negative pulses.

- Another low pass filter 200, 202 removes more of the high frequency signal, thus removing leading and falling edge transients and leaving only the smoothed pulses. Removal of the high frequency components is necessary because the transmitted signal and null signals do not match exactly in waveshape due to the different frequency response and propagation delay of the amplifier stages involved (especially the transmitter and transformer coupling which will be described presently). Thus the mismatch at the edges resulting in high frequency pulses, or glitches, at the output of nulling amplifier 186 must be removed by the low pass filters described above.

- the high speed comparators 194, 196 have a standard digital output (CMOS, 0 to +5v). Comparator 194 (U3A) produces a positive pulse output when the input pulse is positive (with respect to signal zero). Comparator 196 (U3C) produces a positive pulse output when the input pulse is negative. Both outputs remain low if the signal is at or close to zero (with respect to signal zero). Signal zero is, however, offset be a value V os shown in Fig. 8 (e.g. +v) with respect to analog ground at this point because the comparators do not accept a negative voltage.

- V os shown in Fig. 8 (e.g. +v) with respect to analog ground at this point because the comparators do not accept a negative voltage.

- Comparator threshold voltages can be adjusted via a digital potentiometer 210 (RP4) connected to the microcontroller 84.

- the positive pulse threshold voltage is adjustable relative to the offset voltage (signal zero), to a more positive value approximately equal to the most positive signal expected (e.g. 4v).

- the negative pulse threshold is less positive than the offset voltage by the same magnitude that the positive pulse threshold exceeds the offset voltage. This is done through the inverting amplifier 214 (U4) with the VTH+ as the input but referenced to the offset voltage.

- the positive and negative pulse thresholds track, that is, remain equal in magnitude with respect to the signal zero as the threshold potentiometer 210 (RP4) is adjusted.

- the thresholds are adjusted to be 20% to 80% of the signal peak (with respect to signal zero) depending on the noise level and amplitude variation present. While digital potentiometer 210 is shown by way of example, other devices can be employed.

- the TX-NULL amplifier 218 (U5) conditions the null signal (TNULL) for the null amplifier 186 (U2) discussed above. It does the following: variable gain amplification of the delayed transmit signal; adjustment of the dc level which sets the voltage offset at the null amplifier output (REC) and comparator inputs; and shapes the nulling signal waveform so that it better matches the transmitted signal at the line and this output (SIG) of the input amplifier 170. Voltage offset is required, at least with the components selected, because the digital potentiometers and digital input devices only work with positive voltages while the signals have a negative as well as a positive component with respect to signal zero.

- the delayed transmit signal (TNULL) is produced by the same circuit, i.e. pulse converter, as the transmit signal, which will be described in detail presently, except that it is delayed in the digital section (programmable logic device) by an amount which approximates the propagation delay of the transmit amplifier (typically 50 to 200 ns).

- the signal has an offset of half digital level (+2.5v). For a positive transmitted pulse, the signal becomes +5.0v and for a negative pulse, it becomes zero. Thus the signal is +/-2.5v in amplitude with a +2.5v offset. Since this signal is produced by a resistor divider 220, 222 (R20 and R21), each having a magnitude of about 2 Kohm, the output (Thevenin) resistance is 1 Kohm.

- a zero to 10 Kohm digital potentiometer 224 (RP2) is in series plus resistor 226 (R19) (0.8K), produces a net amplifier input resistance of 1.8 to 11.8 Kohm in series with the 5v signal.

- R19 resistor 226

- NULL nulling voltage

- the waveform of this signal (ac component) must be the same as the transmit signal seen at the output (SIG) of the input amplifier 170, except opposite in sign. While digital potentiometer 224 is shown by way of example, other devices can be employed.

- the DC level or voltage offset of the nulling signal is determined, over a moderate range, by the setting of ZERO potentiometer 236 (RP1).

- ZERO potentiometer 236 RP1

- the ratio of its resistance (0 to 10 Kohm) plus a series resistance 238, (R22) to a resistor 240 (R18) connected to the supply results in a 1.4 DC variation which, when added to the fixed offset produced by resistor 244 (R17) at the inverting input and the zener diode 248 (Z1), produce a DC offset at the null input to amplifier 186 (U2) which, finally, produces the desired signal offset (e.g. +2.9v) at the comparator inputs (REC).

- the software ZERO adjustment feature via potentiometer 236 is not essential to the operation of this device and the digital potentiometer may be replaced by a trimpot adjusted during manufacture or eliminated by the use of close tolerance components.

- the circuit for the receiver and nulling section of interface 94 is identical to that shown in Fig. 8 except that the input signals LN + and LN - are from set 70' rather than from PBX 50'.

- the transmitter section 122 of the Tx/Rx interface 92 of Fig. 6 is illustrated further in Fig. 9 . It has three main components including pulse converter 144, analog pulse amplifier 146 with inverter and a pair of constant current drivers 150 and 152 (one non-inverting and one inverting).

- the transmitter section of interface 94 is identical to that shown in Fig. 9 except that the output signals I + and I - are sent to set 70' rather than to PBX 50'.

- the pulse converter is simply a pair of equal value resistors 260,262 (R101, R102, here 2 Kohm), connected to the outputs of two digital devices 264,266 (U101, U102, here standard CMOS binary logic with logic levels of 0 and 5 volts).

- resistors 260,262 R101, R102, here 2 Kohm

- U101, U102 here standard CMOS binary logic with logic levels of 0 and 5 volts.

- TXP input produces a positive pulse of half logic unit (+2.5v) at the TX output and a TXN input produces a negative pulse (-2.5v) at the converter output (if unloaded).

- the output (Thevenin) impedance from this network is half the resistor value (here 1 Kohm).

- the transmit signal (TX) is then coupled through a capacitor 270 to the next stage 272 (U103).

- the capacitor 270 removes the DC level so that the TX signal at the amplifier output is positive and negative with respect to ground.

- the TX-LEVEL digital potentiometer 280 (RP3). Here it has the range of 0 to 10 Kohm, which is added to the internal impedance. As the resistance is increased the transmit signal voltage level (TX) decreases. The range of adjustment the TX voltage is 1.25v peak (2.5vpp) to 0.12v peak at the amplifier unit 264,266 (U101 and U102). In addition, there is an auxiliary transmit input for externally generated signals of other formats (e.g. Mitel). Also the amplifier 272 has a unity gain analog inverter to produce the proper signal into the current driver with the required inverted signal output. This inverter should have minimal propagation delay and a wide frequency response so that the inverted and non-inverted current driver outputs are closely matched, except for the inversion. While digital potentiometer 280 is shown by way of example, other devices can be employed.

- the current drivers are used to allow the option of a balanced drive with respect to ground (non-inverted signal on one side and inverted signal on the other). This is needed for the impedance load option but is not necessary with a proper transformer. Since the dual drivers will work with nearly any interface, they provide flexibility. Analog drivers are needed because the transmit voltage level is adjustable, as required to adapt to the difference voltage requirements of different digital telephones. By contrast, standard digital drivers have fixed voltage outputs. While either a voltage or current type driver can be used, the current type driver is more flexible in adapting to a variety of line interfaces. Also the output voltage requirements are less, since there is no series output or line matching resistance, a desirable characteristic because of the cost of higher voltage, higher frequency amplifiers. Furthermore the constant current driver would be desirable if dynamic line impedance matching were needed.

- the constant current drivers 284,286 (U105, U106) are identical. Only one of the input signal voltages is inverted by inverter 290 (U104).

- the circuit is a modification of a conventional constant current driver found in electrical engineer texts.

- the current source is deliberately made non-ideal (equivalent shunt resistor in parallel with current generator) so that any DC offset will not charge the output capacitor, if used. This is done by making the negative feedback voltage divide ratio 294/296 (R111/R112).

- the DC feedback compensation provided by resistor 300 and capacitor 302 (R118, C103) may be used.

- the circuit for the transmit section of interface 94 is identical to that shown in Fig. 10 except that the outputs I + and I - go to set 70' rather than to PBX 50'.

- microcontroller 84 under program control changes operational parameters in interface 82 as a function of electrical characteristics of the particular type of PBX to which interface 82 is connected.

- microcontroller 84 controls the circuit adjustments in the circuits of Figs. 8 and 10 and on both the PBX side and the set side.

- Microcontroller 84 has analog inputs so that the external receiver amplitude and null signals can be sensed.

- the microcontroller 84 and analog signal monitor section includes microcontroller/microprocessor 84 with analog/digital converter (A/D) 310, digital signal logic 312, analog signal averager 314, and digital potentiometer driver 316.

- A/D analog/digital converter

- the microcontroller 84 through the A/D 310, monitors the signal levels and periodically adjusts the digital potentiometers or like devices in the circuits of Figs. 8 and 10 and on both the PBX side and set side. In particular, with a complete system including four interface circuits, A/D 310 monitors six voltages and microcontroller 84 controls eight digital potentiometers or like devices.

- the microcontroller 84 is primarily concerned with other functions and the signal level adjustment need be made only upon power-up or when the microcontroller has free time.

- the digital potentiometer driver 316 which is a serial data line communication type, alternatively may be internal to the microcontroller 84.

- Analog signals which are monitored are the peak null voltages, averaged over 10 to 1000 periods, peak signal level, averaged, and zero offset voltage. Diodes 320,322 in signal averager 314 allow the peak AC signals to charge capacitors 324,326. The capacitors 324,326 are slowly discharged, providing a time averaging.

- a simple RC low pass filter 330,332 is used to remove the AC signal components, leaving only the baseline voltage.

- the ZERO pot 236 (RP1) is adjusted to the desired offset value (e.g. +2.0v or +1.6v). Then the signal level is measured with a received signal from an external source only. This may be used to characterize the external transmitter, set the receiver threshold, and chose the transmitter signal level.

- the purpose of the digital signal logic 312 is to provide the proper logic signals to the transmitter (TXP and TXN), to disable the signals for testing, to provide a test signal when needed for the null adjustment process, and to provide a slightly delayed transmit signal (TNULL) for the null section.

- TXP and TXN the proper logic signals to the transmitter

- TXP and TXN to disable the signals for testing

- TULL slightly delayed transmit signal

- This logic is best implemented by a programmable logic device but could be done by a digital signal processor, individual logic devices, or a custom device.

- Fig. 12 illustrates a transformer type arrangement for coupling the digital telephone line on both the set side and the PBX side.

- the circuits of Figs. 7 and 9 are duplicated.

- a first transformer 340 has windings 342 and 344 connected to the positive and negative terminals of the PBX by lines 346 and 348, respectively.

- a second transformer 350 has windings 352 and 354 connected to the positive and negative terminals of the telephone set via lines 356 and 358, respectively.

- Windings 342 and 352 are connected by line 362, windings 344 and 354 are connected by line 364 and lines 362 and 364 are coupled by a capacitor 368.

- Transformer 340 has a winding 370 coupled to windings 342, 344 and connected by lines 372 and 374 to a resistive rollage divider 376. Lines 372 and 374 also are connected to lines 124 and 126, respectively, in the analog interface circuit of Fig. 6 provided for the PBX side as previously described.

- transformer 350 has a winding 380 coupled to windings 352, 354 and connected by lines 382 and 384 to a resistive voltage divider 386. Lines 382 and 384 also are connected to lines 124 and 126, respectively, in the analog interface circuit of Fig. 6 provided for the set side as previously described.

- mismatch is the signal reflection or echo.

- a pulse transmitted from one end is partially reflected from the other end if it is not terminated in a impedance equal to the line impedance.

- the amplitude of the reflected signal increases with the degree of mismatch and the time delay of the signal increases with the line length.

- the automatic null provided by the interface of the present invention will take care of this, but for a long delay the null signal will not match and the null will be ineffective.

- Fig. 13 illustrates a dynamic line impedance matching method according to the present invention for long line/long delay situations.

- a portion ( ⁇ ) of the received signal determined by the setting of potentiometer, is fed back to the transmitter, i.e. to the TX-AUX input of transmitting amplifier 146' (negative feedback).

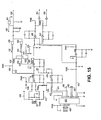

- Figs. 14-18 illustrate a universal interface according to a preferred mode of the present invention.

- the system of Figs. 14-18 includes a universal line driver interface 400, microcontroller 402 and network interface or field programmable gate array 404.

- a relay logic component 406 provides a PBX/set interface. In particular, component 406 determines whether PBX 410 and telephone set 412 are connected to universal line driver interface 400 or set 412 and PBX 410 are connected in a manner bypassing interface 400.

- An ISA interface component 414 provides a host interface to a personal computer (not shown).

- universal line driver interface 400 includes a transmit interface and a receiver interface for both the PBX side and the set side.

- the receiver interface for the PBX side is shown in Fig. 15 .

- Lines 420 and 422 connect the receiver interface for the PBX side (shown in Fig. 16 ) in a manner similar to that of the balanced line pair shown and described in connection with Fig. 6 .

- the input stage includes differential amplifier 426 corresponding to amplifier 130 of Figs. 6 and 7 and amplifier 170 of Fig. 8 .

- the nulling section includes amplifier 428 corresponding to amplifier 134 of Figs. 6 and 7 and amplifier 186 of Fig. 8 .

- Lines 430, 432 and 434 connect analog switches 431, 433 and 435, respectively, of the circuit of Fig. 15 to network interface 404, and lines 436 and 438 connect corresponding portions of the circuit to microcontroller 402.

- the comparator stage includes comparators 440 and 442 corresponding to comparators 136 and 138 of Figs. 6 and 7 and comparators 194 and 196 of Fig. 8 .

- Comparator threshold adjustment is provided by the portion of the circuit of Fig. 15 including inverting amplifier 444 corresponding to inverting amplifier 214 in the circuit of Fig. 8 .

- the threshold adjustment is under control of a digital potentiometer as in the circuit of Fig. 8 , and in the circuit shown in Fig. 15 a quad-type digital potentiometer 450 is provided and is connected via line 452 to the threshold adjustment portion of the circuit.

- the comparator outputs are connected by lines 454 and 456 to network interface 404.

- Digital potentiometer 450 is connected by lines 460 and 462 to network interface 404 and is connected by line 464 to the transmitter interface for the PBX side (shown in Fig. 16 ).

- Lines collectively designated 468 in Fig. 15 show connections between digital potentiometer 450 and microcontroller 402.

- Amplifier 470 in the circuit of Fig. 15 performs functions similar to those of TX-NULL amplifier 218 in the circuit of Fig. 8 .

- Control signals from digital potentiometer 450 are applied to the inputs of amplifier 470 via lines 472 and 474.

- the output of amplifier 470 is provided to the nulling section, and zener diode 476 in the circuit of Fig. 15 functions similar to zener diode 248 in the circuit of Fig. 8 .

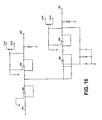

- the transmitter interface for the PBX side is shown in Fig. 16 .

- Lines 480 and 482 connect the transmitter interface to lines 420 and 422, respectively, of the receiver interface circuit of Fig. 15 as previously described and in manner similar to that of the balanced line pair shown and described in connection with Fig. 6 .

- Amplifier 486 corresponds to transmit amplifier 146 of Fig. 9 and amplifier 272 in the circuit of Fig. 10 .

- TX-LEVEL is controlled by a signal on line 490 connected to line 464 from digital potentiometer 450 in the circuit of Fig. 15 .

- Inverter 494 in the circuit of Fig. 16 corresponds to inverter 290 in the circuit of Fig. 10

- current drivers 496 and 498 correspond to current drivers 284 and 286 in the circuit of Fig. 10 .

- the receiver interface for the set side is shown in Fig. 17 .

- Lines 520 and 522 connect the receiver interface for the set side to the transmitter interface for the set side (shown in Fig. 18 ) in a manner similar to that of the balanced line pair shown and described in connection with Fig. 6 .

- the input stage includes a differential amplifier 526 similar to amplifier 426 in Fig. 15 .

- the nulling section includes amplifier 528 similar to amplifier 428 in Fig. 15 .

- Lines 530, 532 and 534 connect portions of the circuit of Fig. 17 to network interface 404 and line 536 connects a portion of the circuit of Fig. 17 to microcontroller 402.

- the comparator stage includes comparators 540 and 542 similar to comparators 440 and 442 in the circuit of Fig. 15 .

- Comparator threshold adjustment is provided by the portion of the circuit of Fig. 17 including inverting amplifier 544 similar to inverting amplifier 440 in the circuit of Fig. 15 .

- the threshold adjustment is under control of a quad-type digital potentiometer 550 similar to digital potentiometer 450 in the circuit of Fig. 15 .

- Line 552 connects potentiometer 550 to the threshold adjustment portion of the circuit.

- the comparator outputs are connected by lines 554 and 556 to network interface 404.

- Digital potentiometer 550 is connected by lines 560 and 562 to network interface 404 and is connected by line 564 to the transmitter interface for the set side (shown in Fig. 18 ).

- Lines collectively designated 568 in Fig. 17 show connection between digital potentiometer 550 and microcontroller 402.

- Amplifier 570 in the circuit of Fig. 17 performs functions similar to those of amplifier 470 in the circuit of Fig. 15 .

- Control signals from digital potentiometer 550 are applied to the inputs of amplifier 570 by lines 572 and 574.

- the output of amplifier 570 is provided to the nulling section, and zener diode 576 is similar to zener diode 476 in the circuit of Fig. 15 .

- the transmitter interface for the set side is shown in Fig. 18 .

- Lines 580 and 582 connect the transmitter interface to lines 520 and 522, respectively, of the receiver interface circuit of Fig. 17 as previously described and in a manner similar to that of the balanced line pair shown and described in connection with Fig 6 .

- Amplifier 586 is similar to amplifier 486 in Fig. 16

- TX-LEVEL is controlled by a signal on line 590 connected to line 564 from digital potentiometer 550 in the circuit of Fig. 17 .

- Inverter 594 in the circuit of Fig. 18 is similar to inverter 494 in the circuit of Fig. 16

- current drivers 596 and 598 are similar to current drivers 496 and 498 in the circuit of Fig. 16 .

- Alternative devices can of course be substituted for the digital potentiometers in the circuits of the system of Figs. 14-18 .

- the algorithm for adjusting the digital potentiometers (pots) in the system of Figs. 14-18 is as follows.

- the system of Figs. 14-18 is designed to provide an interface to PBXs from several manufacturers.

- the circuitry includes eight digital pots (four in each of the quads 450 and 550) and eight analog to digital converters (ADC's) that are used to adjust the circuit and measure signal so that critical circuit parameters can be adjusted to accommodate the various PBX transmission protocols and compensate for component tolerances.

- ADC's analog to digital converters

- circuit loop length can be compensated for. This provides a very robust method of providing error free operation.

- the circuit provides a separate interface to the PBX and the desktop handset, converting from the various proprietary methods that the PBX manufacturers use to communicate with their equipment to a raw digital stream that is fed into the PBX specific (Field Programmable Gate Array (FPGA) to be further decoded into a true digital bitstream.

- PBX specific Field Programmable Gate Array

- the overall concept is to bias the input signal to about 2.5 volts (providing a virtual ground for the signal of 2.5V), determining the voltage swing of the signal and calculate threshold values to isolate the maximum and minimum going peaks relative to virtual ground. From this, the upper and lower signal thresholds that are used for level detection are calculated. Also, some of the PBX systems superimpose the transmitted signal on the received signal so that the transmitted signal needs to be subtracted out before the received signal is decoded. This part of the circuit is called NULL calibration.

- the eight digital pots in the circuit of Figs. 14-18 provide the following functions:

- ADCs There are eight ADCs that will measure various signals in the circuit. In addition, there are four analog switches that allow more than one signal to be measured on each ADC channel.

- the ADC's perform the following functions:

- the PBX and SET peak detect ADC channels have an analog switch that allows them to be used to measure either the transmit signal or the receive signal. This is done by setting or clearing the RS_SEL control bit on lines 432 and 434 in the circuit of Fig.15 and on lines 532 and 534 in the circuit of Fig. 17 .

- the PBX and SET peak detect ADC channels have circuitry associated with them to hold the peak value over an interval so that it can be read later by the ADC.

- This peak detector is cleared by setting the PV_CLR control bit on lines 430 and 530 in the circuits of Figs 15 and 17 , respectively, which controls an analog switch which allows the peak detector to drain to ground.

- the RC constant of this circuit is approximately 10ms so PV_CLR should be held high for at least that long to clear the detector. PV_CLR should be held low for a time sufficient to register a valid peak.

- the following illustrates calculations to determine nominal POTS settings and ADC readings.

- the meaning of the POTS settings and interpretation of the ADC readings is based on various circuit parameters.

- the following will describe the parameters for each POT and ADC to provide meaning for the values from a software point of view.

- the Zero Level ADC channels have associated with them a resistor network comprising the series combination of a 1 M resistor and a 100K resistor with the junction of the resistors connected to Zv ADC Channel, the 1 M resistor connected to the 5 volt supply and the 1 M resistor connected to a point in the circuit at 2.5 volts.

- a resistor network comprising the series combination of a 1 M resistor and a 100K resistor with the junction of the resistors connected to Zv ADC Channel, the 1 M resistor connected to the 5 volt supply and the 1 M resistor connected to a point in the circuit at 2.5 volts.

- Such a network is included in the circuit of Fig. 15 wherein resistors 620 and 622 are connected in series between a 5 volt power terminal and a point in the circuit where a 2.5 volt signal level is present and wherein the junction of the resistors 620 and 622 is connected by line 438 to the Zv ADC channel provided by microcontroller 402.

- a similar network is included in

- the Peak Detect ADC channels have associated with them a resistor network comprising the series combination of a 4.7 K resistor and an 820 ohm resistor with the junction of the resistors connected to the peak detect ADC channel, the 4.7K resistor connected to the 5 volt supply and the 820 ohm resistor connected to a point in the circuit wherein the voltage at the peak detector is present.

- One such network in the circuit of Fig. 15 includes the series combination of resistors 630 and 632 wherein the junction of the resistors is connected by line 634 to analog switch 433.

- Another such network includes the series combination of resistors 636 and 638 wherein the junction of the resistors is connected by line 640 to analog switch 435.

- Similar networks are included in the circuit of Fig. 17 wherein the junction of resistors 644 and 646 is connected by line 648 to analog switch 533 and the junction of resistors 652 and 654 is connected by line 656 to analog switch 535.

- V adc V p + 5.0 - V p ⁇ 820 4700 + 820

- V adc V p + 5.0 - V p ⁇ 820 5520

- V adc V p + 820 ⁇ 5.0 - 820 ⁇ V p 5520

- V adc 4700 5520 ⁇ V p + 4100 5520

- the threshold POT has associated with it a resistor network comprising the series combination of a 5K resistor, a 10K resistor and a 15K resistor with the 10K resistor being connected between the other two, the 5K resistor being connected to the 5 volt supply and the 15K resistor being connected to ground.

- the threshold voltage is taken off the 10K resistor.

- a voltage Va is present at the junction between the 5K resistor and the 10K resistor, and a voltage Vb is present at the junction between the 10K resistor and the 15K resistor.

- the voltage swing for the threshold voltage is 3.5V to 4.1667V

- Table I presents illustrative values for calculating the threshold POT value need to set the threshold for the circuits.

- the operation requires that the peak detector be read.

- the raw value is in the Column labeled "Peak detector ADC value”.

- the next column is the peak voltage that the ADC value represents.

- the next column is the desired threshold voltage.

- the column label "POT value” calculates the value that is needed by the POT to obtain the desired threshold and the following column converts it to hex so can be cut and pasted into a C sources file.

- the Vs, R1 and R2 values are taken from the circuit, and the threshold percentage can be varied depending on desired levels.

- Threshold 5.0 4700 820 60% Peak detector Voltage it Desired POT POT Value

- ADC value represents Threshold Value In Hex 0 -0.8723 0.4766 -311 0x00, 1 -0.8494 0.4904 -309 0x00, 2 -0.8265 0.5041 -307 0x00, 3 -0.8035 0.5179 -304 0x00, 4 -0.7806 0.5316 -302 0x00, 5 -0.7576 0.5454 -300 0x00, 6 -0.7347 0.5592 -298 0x00, 7 -0.7118 0.5729 -296 0x00, 8 -0.6888 0.5867 -294 0x00, 9 -0.6659 0.6005 -292 0x00, 10 -0.6430 0.6142 -290 0x00, 15 -0.5283 0.6830 -279 0x00, 20 -0.4136 0.7519

- FIG. 19 and 20 illustrate the method for adjusting the PBX and SET digital pots 450 and 550, respectively, in the circuits of Figs. 15 and 17 , respectively.

- Standard telephones and some digital telephones transmit signals in both directions along a single pair of wires or balanced line.

- An equivalent circuit is shown in Fig. A1. Both sides have transmitters represented by voltage sources V 1T and V 2T .

- the source resistance R s is equal to the chosen line impedance (600 ohm) for standard, audio range, telephones and perhaps 50 or 100 ohms for digital telephones.

- the transformer load impedance (R L ) and line impedance are the same as the source impedance. By duplex operation it is meant that data can be transmitted (and received) in both directions simultaneously.

- FIG. A2 A simplified circuit for transmission in one direction is shown in Fig. A2 where the impedances are reflected through the transformers and the signal ignores isolation.

- V L is in the range of 0.2 to 3 volts (peak-to-peak) .

- a duplexer circuit separates the transmitted and received signals at one end. One is needed at both ends.

- a "hybrid" circuit which involves transformers performs the same function but a circuit without transformers is desired here.

- the current source (Is) must be capable of producing the required peak signal voltage (V L /2) with the load (R L /2) .

- I S 2 ⁇ V L R L

- the source must have a voltage limit higher than the line signal level (2.5v pk or 5v pp). This implies an operational amplifier with a minimum voltage of +/-5 volts and a minimum current of +/-25 mA (plus that used for other resistors) The total line current will be +/-50 mA peak or 100 mA pp when both drivers are transmitting.

- a +/-6 to 12v op-amp with a +/-40 to 80 mA with output may be needed.

Landscapes

- Engineering & Computer Science (AREA)

- Signal Processing (AREA)

- Computer Networks & Wireless Communication (AREA)

- Interface Circuits In Exchanges (AREA)

- Sub-Exchange Stations And Push- Button Telephones (AREA)

- Telephonic Communication Services (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US327279 | 1999-06-04 | ||

| US09/327,279 US6639983B1 (en) | 1998-01-20 | 1999-06-04 | Adaptable line driver interface for digital telephone systems |

| PCT/US2000/015523 WO2000076180A1 (en) | 1999-06-04 | 2000-06-05 | Adaptable line driver interface for digital telephone systems |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| EP1192786A1 EP1192786A1 (en) | 2002-04-03 |

| EP1192786A4 EP1192786A4 (en) | 2002-07-31 |

| EP1192786B1 true EP1192786B1 (en) | 2009-08-05 |

Family

ID=23275898

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| EP00946779A Expired - Lifetime EP1192786B1 (en) | 1999-06-04 | 2000-06-05 | Adaptable line driver interface for digital telephone systems |

Country Status (8)

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3748723B2 (ja) * | 1998-11-24 | 2006-02-22 | 富士通株式会社 | 共通化パッケージ |

| US7020274B1 (en) * | 2000-04-26 | 2006-03-28 | Agilent Technologies, Inc. | Universal apparatus and method for interfacing signals with telephony networks |

| US6862341B2 (en) * | 2001-04-13 | 2005-03-01 | Intel Corporation | Device and method of interfacing voice data between a switch and a computer system |

| AU2003291864A1 (en) * | 2002-12-04 | 2004-06-23 | Research In Motion Limited | Gain compensation over temperature and frequency variations in wireless transceivers |

| US9032079B2 (en) | 2007-06-26 | 2015-05-12 | Microsoft Technology Licensing, Llc | Management and diagnosis of telephonic devices |

| US7778154B2 (en) * | 2008-03-25 | 2010-08-17 | Freescale Semiconductor, Inc. | Techniques for reducing interference in a communication system |

| US8599726B2 (en) * | 2010-06-03 | 2013-12-03 | Broadcom Corporation | Front end module with a tunable balancing network |

| CN104717371B (zh) * | 2013-12-13 | 2017-12-05 | 北京三希电子科技有限公司 | 一种通用设备及电话通讯系统 |

| CN116645804A (zh) * | 2023-03-02 | 2023-08-25 | 深圳市玩视科技股份有限公司 | 一种支持多种标准的红外接收头电路 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4103118A (en) * | 1977-05-02 | 1978-07-25 | Synanon Foundation, Inc. | Autobalance hybrid circuit |

| US5151935A (en) * | 1989-12-20 | 1992-09-29 | Xel Communications, Inc. | Programmable universal signaling circuit for a telephone network |

| US5333177A (en) * | 1991-10-19 | 1994-07-26 | Cell Port Labs, Inc. | Universal connection for cellular telephone interface |

| US5642410A (en) * | 1994-02-18 | 1997-06-24 | Aurora Systems, Inc. | Call processor for a computer telephone integration system |

| US5649001A (en) * | 1995-03-24 | 1997-07-15 | U.S. Robotics Mobile Communications Corp. | Method and apparatus for adapting a communication interface device to multiple networks |

| US6343126B1 (en) * | 1996-03-27 | 2002-01-29 | Hello Direct, Inc. | Method and apparatus for interfacing analog telephone apparatus to a digital, analog or hybrid telephone switching system |

| US5802169A (en) * | 1996-04-11 | 1998-09-01 | Intervoice Limited Partnership | System and method for transmission system automatic impedance matching |

| US5875242A (en) * | 1996-07-26 | 1999-02-23 | Glaser; Lawrence F. | Telecommunications installation and management system and method |

| US5999593A (en) | 1998-01-20 | 1999-12-07 | Voice Technologies Group, Inc. | System and method for automatic PBX detection |

-

1999

- 1999-06-04 US US09/327,279 patent/US6639983B1/en not_active Expired - Lifetime

-

2000

- 2000-06-05 KR KR10-2001-7015626A patent/KR100432646B1/ko not_active Expired - Fee Related

- 2000-06-05 JP JP2001502332A patent/JP4426142B2/ja not_active Expired - Fee Related

- 2000-06-05 WO PCT/US2000/015523 patent/WO2000076180A1/en active IP Right Grant

- 2000-06-05 DE DE60042689T patent/DE60042689D1/de not_active Expired - Lifetime

- 2000-06-05 EP EP00946779A patent/EP1192786B1/en not_active Expired - Lifetime

- 2000-06-05 AU AU60482/00A patent/AU6048200A/en not_active Abandoned

- 2000-06-05 CN CNB008111197A patent/CN100393079C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| WO2000076180A1 (en) | 2000-12-14 |

| US6639983B1 (en) | 2003-10-28 |

| DE60042689D1 (de) | 2009-09-17 |

| CN100393079C (zh) | 2008-06-04 |

| KR20020044549A (ko) | 2002-06-15 |

| JP4426142B2 (ja) | 2010-03-03 |

| EP1192786A4 (en) | 2002-07-31 |

| KR100432646B1 (ko) | 2004-05-22 |

| CN1372749A (zh) | 2002-10-02 |

| JP2003501960A (ja) | 2003-01-14 |

| AU6048200A (en) | 2000-12-28 |

| EP1192786A1 (en) | 2002-04-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2722213B2 (ja) | 整合装置 | |

| CA2676794C (en) | Automatic equalization of video signals | |

| CA2202311C (en) | Self-monitoring line interface circuit | |

| US6298046B1 (en) | Adjustable balancing circuit for an adaptive hybrid and method of adjusting the same | |

| US20020106012A1 (en) | Loop extender with communications, control, and diagnostics | |

| US20030026391A1 (en) | Single ended line probing in DSL system | |

| US20090067614A1 (en) | Common mode transmission line termination | |

| US4870675A (en) | Remote testing of metallic loops with a trans hybrid signal | |

| US7508218B2 (en) | Apparatus and method for measuring loop insertion loss single-endedly | |

| EP1192786B1 (en) | Adaptable line driver interface for digital telephone systems | |

| US8908752B2 (en) | Line testing | |

| WO2003005598A9 (en) | Single ended line probing in dsl system using transformerless hybrid | |

| JP2562757B2 (ja) | ライン・インタフェース回路 | |

| US7483528B2 (en) | Loop extender with selectable line termination and equalization | |

| US6973183B1 (en) | Method and apparatus for dynamically matching impedance | |

| US6917682B2 (en) | Method and device for echo cancelling | |

| US6400822B1 (en) | Linear, optical coupled line impedance circuit | |

| US5848127A (en) | Two-wire channel unit with loopback test capability | |

| US5644617A (en) | Method and apparatus for testing cables | |

| CA1171565A (en) | Transformerless hybrid circuit | |

| US6522723B1 (en) | Telephony line test unit and method | |

| US5828733A (en) | Method and arrangement for increasing data transmisssion rate over telephone cable | |

| US5917885A (en) | Method and system for testing subscriber circuits and wiring in a cable communication system | |

| US20030076945A1 (en) | Automatic longitudinal balance for solid state DAAs | |

| CN101044745B (zh) | 电话线接口、侧音衰减电路和方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PUAI | Public reference made under article 153(3) epc to a published international application that has entered the european phase |

Free format text: ORIGINAL CODE: 0009012 |

|

| 17P | Request for examination filed |

Effective date: 20011217 |

|

| AK | Designated contracting states |

Kind code of ref document: A1 Designated state(s): AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE |

|

| AX | Request for extension of the european patent |

Free format text: AL;LT;LV;MK;RO;SI |

|

| A4 | Supplementary search report drawn up and despatched |

Effective date: 20020613 |

|

| AK | Designated contracting states |

Kind code of ref document: A4 Designated state(s): AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE |

|

| RIC1 | Information provided on ipc code assigned before grant |

Free format text: 7H 04M 1/00 A, 7H 04M 3/42 B, 7H 04M 7/00 B |

|

| RAP1 | Party data changed (applicant data changed or rights of an application transferred) |

Owner name: INTEL CORPORATION |

|

| RBV | Designated contracting states (corrected) |

Designated state(s): DE DK FI FR GB SE |

|

| 17Q | First examination report despatched |

Effective date: 20040512 |

|

| 17Q | First examination report despatched |

Effective date: 20040512 |

|

| GRAP | Despatch of communication of intention to grant a patent |

Free format text: ORIGINAL CODE: EPIDOSNIGR1 |

|

| GRAS | Grant fee paid |

Free format text: ORIGINAL CODE: EPIDOSNIGR3 |

|

| GRAA | (expected) grant |

Free format text: ORIGINAL CODE: 0009210 |

|

| AK | Designated contracting states |

Kind code of ref document: B1 Designated state(s): DE DK FI FR GB SE |

|

| REG | Reference to a national code |

Ref country code: GB Ref legal event code: FG4D |

|

| REF | Corresponds to: |

Ref document number: 60042689 Country of ref document: DE Date of ref document: 20090917 Kind code of ref document: P |

|

| REG | Reference to a national code |

Ref country code: HK Ref legal event code: WD Ref document number: 1043004 Country of ref document: HK |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: SE Free format text: LAPSE BECAUSE OF FAILURE TO SUBMIT A TRANSLATION OF THE DESCRIPTION OR TO PAY THE FEE WITHIN THE PRESCRIBED TIME-LIMIT Effective date: 20090805 Ref country code: FI Free format text: LAPSE BECAUSE OF FAILURE TO SUBMIT A TRANSLATION OF THE DESCRIPTION OR TO PAY THE FEE WITHIN THE PRESCRIBED TIME-LIMIT Effective date: 20090805 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: DK Free format text: LAPSE BECAUSE OF FAILURE TO SUBMIT A TRANSLATION OF THE DESCRIPTION OR TO PAY THE FEE WITHIN THE PRESCRIBED TIME-LIMIT Effective date: 20090805 |

|

| PLBE | No opposition filed within time limit |

Free format text: ORIGINAL CODE: 0009261 |

|

| STAA | Information on the status of an ep patent application or granted ep patent |

Free format text: STATUS: NO OPPOSITION FILED WITHIN TIME LIMIT |

|

| 26N | No opposition filed |

Effective date: 20100507 |

|

| REG | Reference to a national code |

Ref country code: FR Ref legal event code: ST Effective date: 20110228 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: FR Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20100630 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: GB Payment date: 20160601 Year of fee payment: 17 Ref country code: DE Payment date: 20160601 Year of fee payment: 17 |

|

| REG | Reference to a national code |

Ref country code: DE Ref legal event code: R119 Ref document number: 60042689 Country of ref document: DE |

|

| GBPC | Gb: european patent ceased through non-payment of renewal fee |

Effective date: 20170605 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: GB Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20170605 Ref country code: DE Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20180103 |