EP0438469B1 - Schaltungsanordnung zur digitalen erfassung einer analogen information in der form des zeitabstandes zweiter aufeinanderfolgender zustände eines signals - Google Patents

Schaltungsanordnung zur digitalen erfassung einer analogen information in der form des zeitabstandes zweiter aufeinanderfolgender zustände eines signals Download PDFInfo

- Publication number

- EP0438469B1 EP0438469B1 EP89911553A EP89911553A EP0438469B1 EP 0438469 B1 EP0438469 B1 EP 0438469B1 EP 89911553 A EP89911553 A EP 89911553A EP 89911553 A EP89911553 A EP 89911553A EP 0438469 B1 EP0438469 B1 EP 0438469B1

- Authority

- EP

- European Patent Office

- Prior art keywords

- circuit

- signal

- charge

- time interval

- circuit arrangement

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G04—HOROLOGY

- G04F—TIME-INTERVAL MEASURING

- G04F10/00—Apparatus for measuring unknown time intervals by electric means

- G04F10/10—Apparatus for measuring unknown time intervals by electric means by measuring electric or magnetic quantities changing in proportion to time

- G04F10/105—Apparatus for measuring unknown time intervals by electric means by measuring electric or magnetic quantities changing in proportion to time with conversion of the time-intervals

Definitions

- the invention relates to a circuit arrangement for the digital detection of analog information in the form of the time interval between two successive states of at least one signal or the amplitude of the signal, according to the preamble of claim 1.

- a circuit arrangement for recording time intervals, in particular for measuring small time intervals. in the sub-millisecond range, which cannot be determined with conventional digital interval measuring devices or can only be determined with insufficient resolution, comprises an integration capacitor which has a Charging circuit is chargeable to a voltage representing the analog information, and a charge change circuit that changes the voltage of the integration capacitor at a rate of change less than that of the charging circuit.

- a comparator compares the voltage on the integration capacitor with a predetermined threshold.

- a counter is also provided, which counts periodic clock pulses during the change in the voltage of the integration capacitor by means of the charge change circuit until the predetermined threshold value is reached.

- the charge change circuit changes the voltage at the integration capacitor until the threshold value monitored by the comparator is reached.

- the duration of this voltage change of the integration capacitor by means of the charge change circuit depends on the one hand on predetermined parameters of the circuit arrangement and on the other hand on the value of the integration capacitor voltage representing the analog information.

- the counting result of the counter represents digital information about the duration of the voltage change and thus also about the value of the analog information.

- One possibility of improving the resolution in the time interval measurement without increasing the reference clock frequency is to determine the time intervals at the beginning and at the end of the measurement time interval which cannot be precisely determined due to the asynchronism of the measurement and reference clock signals, using a circuit arrangement of the type described above.

- Such an application of a circuit arrangement for the digital detection of the time interval between two successive states of at least one signal is known from the magazine "Elektronik" volume 7-1988, issue 14 pages 65 to 68.

- the known circuit arrangement works as an analog interpolator of a time interval measuring system and detects the time interval T 1 between the beginning of a time interval T x to be measured and a subsequent predetermined edge of a periodic reference clock signal.

- Another analog interpolator detects the time interval T'1 between End of the time interval to be measured and a subsequent predetermined edge of the reference clock signal.

- the above-mentioned predetermined edges of the reference clock signal include a time interval T m , the length of which corresponds to an integer multiple of the period of the reference clock signal and can therefore be exactly determined by counting the clock periods falling in this clock-synchronous time interval with a counting device. From the information determined with the analog interpolators and the counting device about the time segments. T 1, T 1 and T m , an evaluation device calculates a digital measured value for the measuring time interval T x to be determined, whereby a high time resolution is achieved.

- the known circuit device comprises an integrating capacitor arranged in an integrator circuit, a charging circuit for charging the integrating capacitor with a constant current of a first charge source during the time interval to be detected T 1 or T 1, a charge changing circuit for discharging the integrating capacitor with the current of a second charge source, and a comparator which compares the voltage across the capacitor with a threshold value corresponding to the discharge state of the capacitor.

- the first and second charge sources have opposite polarities.

- the first charge source delivers a constant current that is a thousand times greater than the constant current of the second charge source.

- the voltage changes at the integration capacitor during the charging and discharging phase are linear, but with different signs.

- a counter counts periodic clock pulses of the reference clock signal. After the discharge phase, the counting result of the counter represents information about the time interval T 1 or T 1 to be recorded.

- the known circuit arrangement has in particular the disadvantage that charge sources of opposite polarity are required for charging and discharging the integration capacitor.

- the comparator requires a negative DC voltage to set the threshold value OV. Good constancy is required for the charging current and the discharging current.

- the integration capacitor voltage represents the time interval to be detected only incorrectly after the end of the charging phase, while fluctuations in the discharge current have a disruptive influence on the discharge time and thus on the counting result of the counter.

- the required stabilization of the currents of different signs to predetermined values, which also differ significantly, is associated with a high circuit complexity, which makes the circuit arrangement complicated and expensive.

- a circuit arrangement for digitally detecting the voltage amplitude of an analog signal is known.

- This known circuit arrangement works according to the "dual-slope" analog-digital converter method and comprises one Integration capacitor in an integrator circuit with operational amplifier.

- the input of the integrator circuit is electrically connected to the signal source via a charging circuit during a predetermined integration time interval, as a result of which the integration capacitor is charged to a voltage proportional to the signal voltage to be measured. After the integration time interval has elapsed, the input of the integrator circuit is connected to a reference voltage source with a constant reference voltage in order to discharge the integration capacitor.

- the capacitor voltage changes linearly with time.

- a counter counts periodic clock pulses from a reference clock source.

- a comparator ends the counting process when the voltage on the capacitor has dropped to the value OV. After the discharge phase has expired, the counting result of the counter represents digital information about the signal voltage to be measured.

- a disadvantage of this known analog-digital converter is that a very good constant reference voltage is required for the controlled discharge process of the integration capacitor and thus for a high accuracy of the voltage measurement, the sign of which is opposite to the sign of the measuring voltage.

- the known circuit arrangement therefore requires at least one positive and one negative voltage source, each with a very good constant output voltage, and a switching device which reverses the polarity of the reference voltage.

- the invention has for its object to provide a circuit arrangement for the digital detection of analog information in the form of the time interval between two successive states of at least one signal or the amplitude of the signal, the circuit complexity and susceptibility to interference is low.

- This object is achieved in that the charging circuit and the charge change circuit change the voltage of the integration capacitor in the same direction and are connected to a common charge source.

- the circuit arrangement according to the invention can be implemented with little circuit complexity and is almost insensitive to faults. In particular, only one charge source, for example a DC voltage source, is required to operate the circuit. Another advantage is that the circuit arrangement can be constructed from comparatively inexpensive components without reducing its reliability.

- the charging circuit is only activated during the time interval to be detected in order to charge the integration capacitor to a voltage representing the time interval to be measured . It is also ensured that the voltage change of the integration capacitor takes place immediately after the time interval to be detected by means of the charge change circuit, as a result of which the voltage at the integration capacitor representing the time interval can be evaluated in a fail-safe and comparatively fast manner without being falsified by leakage currents.

- different signal states of a signal can be selected as delimiting marks of a time interval to be measured.

- the signal states can be, for example, rising or falling edges of a measurement signal.

- time intervals between signal states of signals from different sources can be recorded.

- the circuit complexity for the power supply is kept to a minimum.

- the development of the invention according to claim 6, for measuring the amplitude of the signal ensures a constant integration time interval for charging the integration capacitor to a voltage representing the amplitude of the analog signal. By counting periodic clock pulses that fall in the charge change phase that follows the integration time interval, digital information about the analog signal voltage to be detected is obtained.

- a sample-and-hold circuit for temporarily storing signal amplitude values enables the digital detection of amplitude values of time-varying signals.

- the charging circuit can be easily implemented by setting a first resistance value and the charge change circuit by setting a second resistance value of the resistance circuit according to claim 8, the charge and charge change circuit making do with a common charge source.

- Claim 9 specifies a very simple possibility for changing the resistance value of the resistance circuit.

- a particular advantage of the resistance circuit according to claim 9 is that the charge flow to the capacitor during the charging phase and during the Charge change phase essentially depends on passive components that are not susceptible to interference, namely ohmic resistors.

- the proposed resistance circuit ensures, with a very simple structure, an almost interference-free acquisition of the analog information.

- resistors with high precision, temperature independence and long-term stability of their resistance values can be produced with the technologies available today without difficulty and at the same time at low cost, which contributes to the inexpensive implementation of the circuit arrangement.

- the rate of change of the voltage of the integration capacitor during the voltage change by means of the charge change circuit is significantly smaller than the rate of change of the voltage change on the integration capacitor during the charging phase by means of the charge circuit. This is particularly important if time intervals that are approximately the same length or shorter than the period of the periodic clock signal are to be recorded digitally.

- the duration of the charge change phase which is dependent on the duration of the charge phase, can always be chosen by choosing the resistance ratio of the first and second resistors so long that several periodic clock pulses occur during the charge change phase, so that counting these clock pulses provides digital information about the duration of the charge phase becomes.

- the integration capacitor can be short-circuited by a second switch of the control device in order to establish the initial conditions for a new measurement process.

- the circuit arrangement designated 1 in FIG. 1 comprises an analog circuit part 3, a comparator 5, a counter 7 and a control device 9.

- the analog circuit part 3 comprises a resistance circuit 11 with a first resistor connected to the positive pole 6 of a positive DC voltage source 13 in series with a first switch 15 in a first branch 16 and with a second resistor 17 in parallel with the first resistor 13 and the first Switch 15 in a second branch 18, furthermore in series with the resistance circuit 11, a parallel circuit 21 connected to the reference potential 19 (ground) of the DC voltage source, consisting of an integration capacitor 23 in a third branch 25 and a second switch 27 in a fourth branch 29.

- the first switch 15 and the second switch 27 are controlled by the control device 9 and, depending on the switching state, switch a current through the first branch 16 or through the fourth branch 29 on or off.

- An input 31 of the comparator 5 is electrically connected to a first connection 33 of the integration capacitor 23.

- the comparator 5 compares the voltage U c at the integration capacitor 23 with a predetermined threshold value U c2 and changes the state of its comparator output signal when the capacitor voltage U c reaches the threshold value U c2 .

- An output 35 of the comparator 5 carrying the comparator output signal is electrically connected to an input 37 of the control device 9.

- a signal state detector 8 of the control device 9 detects predetermined successive state changes of at least one measurement signal, for example the positive and negative edge of a rectangular pulse of a measurement signal, and the control device 9 controls the first switch 15 or second switch 27 depending on the occurrence of the predetermined state changes of at least one measurement signal or depending on the occurrence of a change in state of the comparator output signal.

- the control device 9 is also electrically connected to a counter enable input 39 of the counter 7 in order to switch the counter readiness of the counter 7 on or off as a function of the occurrence of a predetermined change in state of at least one measurement signal or the comparator output signal. When switched on The counter counts 7 clock pulses of a periodic clock signal Tref of constant clock period Tclk.

- the chronological sequence of different steps in the digital detection of the time interval T 1 between the positive and the subsequent negative edge of a rectangular signal pulse P is described below.

- the second switch 27 is switched on and thus the integration capacitor 23 is short-circuited and discharged via the fourth branch 29 (initial state of the circuit).

- the signal state detector 8 of the control device 9 detects the positive edge A 1 as the start signal of a measurement, and the control device 9 simultaneously switches off the second switch 27 by outputting a control signal, so that no current flows through the fourth branch 29 can flow past the integration capacitor 23.

- a charging phase for charging the integration capacitor 23 to a time interval T 1 between the pulse edges A 1, A 2 of the rectangular pulse P represents voltage U c1 .

- the first switch 15 is switched on, so that the integration capacitor 23 is charged via the first and second resistors 13, 17.

- the analog circuit 3 works as a charging circuit 3 'with a charging time constant ⁇ 1.

- the signal state detector 8 of the control device 9 detects the negative edge A2 as a stop signal for the charging phase, and the control device 9 ends the charging phase by switching off the first switch 15 End of the loading phase a signal to the counter 7 to turn on the readiness of the counter 7, so that this counts clock pulses of the periodic clock signal Tref.

- a charge change phase ⁇ T Immediately following the charging phase is a charge change phase ⁇ T, in which the integration capacitor 23 is only charged via the second resistor 17.

- the analog circuit 3 works as a charge change circuit 3scnies for relieving the voltage U c on the integration capacitor 23 until the threshold value U c2 monitored by the comparator 5 is reached.

- the charge time constant ⁇ 2 of the charge change circuit is significantly greater than the charge time constant ⁇ 1 of the charge circuit, so that the voltage U c at the integration capacitor 23 is changed during the charge change phase ⁇ T with a much smaller rate of change than during the charge phase T 1.

- the time constant ⁇ 2 of the charge change circuit is greater than the time constant ⁇ 1 of the charge circuit, since the total resistance of the resistance circuit 11 during the charge change phase (charge of the integration capacitor 23 via the second resistor 17) is greater than during the charge phase (charge of the integration capacitor 23 via a parallel circuit from the first and second resistor 13, 17).

- Charge and charge change circuit 3 ', 3 ⁇ change the voltage U c on the integration capacitor 23 in the same direction.

- the comparator 5 changes the state of the comparator output signal, whereupon the control device 9 switches off the readiness of the counter 7 and switches on the second switch 27.

- the integration capacitor 23 is then short-circuited and discharged via the second switch 27, as a result of which the circuit arrangement according to the invention is reset to its initial state.

- the counting result X of the counter 7 is read out after the end of the charge change phase by an evaluation device (not shown) and evaluated as digital information for calculating a measured value for the time interval T 1 between the edges A 1, A 2 of the measurement signal.

- the signal state detector 8 of the control device 9 can optionally also react to predetermined signal states other than those described above.

- the signal states for starting and stopping the charging phase of the integration capacitor and thus the measuring time interval can come from different signal sources.

- the circuit arrangement according to the invention is able to carry out self-calibration measurements.

- the first switch 15 is switched off and the second switch 27 is switched on (initial switching state), so that the integration capacitor 23 is discharged.

- the control device 9 starts the calibration measurement by switching off the second switch 27 and switching on the readiness of the counter 7.

- the integration capacitor 23 is then charged only via the second resistor 17 from its discharge state until the threshold value U c2 is reached .

- the comparator 5 changes the state of its output signal, whereupon the control device 9 ends the calibration measurement by switching off the readiness of the counter 7 and switching on the second switch 27.

- the counter 7 counts the clock pulses of the periodic clock signal Tref.

- the counting result XT of the counter 7 is read out by the evaluation device after the calibration measurement and is buffered. This counting result XT of the calibration measurement is included by the evaluation device in the evaluation of one or more time intervals T 1 to be measured.

- the following is a mathematical basis for determining a time interval T 1 between successive states of at least one signal.

- C denotes the charge time constant of the charge change circuit and U c2 denotes the threshold value of the integration capacitor voltage monitored by the comparator 5.

- Equating equations (1) and (4) and resolving the result according to T1 leads to a mathematical description of the duration of the charging phase or the time interval to be recorded between two successive states of at least one signal, which is independent of the unknown voltage U c1 :

- T1 - R1 R2C / (R1 + R2) ln ((U O - U c2 ) / U O ) - R1 / (R1 + R2) X Tclk

- equation (5) the time constants ⁇ 1 and ⁇ 2 are expressed by the resistance values R1 and R2 and by the capacitance C of the integration capacitor 23.

- the symbol ⁇ T for the duration of the charge change phase has been replaced in equation (5) by the equivalent expression: X Tclk.

- X denotes the counting result of the counter 7 after the charge change phase has ended and Tclk the period of the periodic clock signal Tref.

- Equation (5) can be considerably simplified by including the counting result XT of a calibration measurement.

- the time delay T 1 of two successive states of at least one signal is neither the value of the supply voltage U o nor the threshold value U c2 of the comparator 5, nor the capacitance value C of the integration capacitor 23.

- Long-term stability of the above-mentioned variables is therefore not necessary if a time interval measurement or a series of measurements of time interval measurements is carried out with the circuit arrangement according to the invention in each case in connection with a calibration measurement. All that is then required is an easy-to-meet short-term stability of the above-mentioned parameters for one measurement process. Expensive precision components with high long-term stability or complex stabilization circuits can therefore be dispensed with.

- the capacitance value C of the integration capacitor 23 is not included in the equation (8), larger deviations from the nominal capacitance value, for example due to manufacturing tolerances, also play no role.

- the only device parameters included in the evaluation are the resistance values R1 and R2 and the period Tclk of the clock signal. These values are very easy to determine and have good constancy.

- the calibration measurement is very simple to carry out and, instead of requiring additional computational effort, the computational evaluation for determining a measuring time interval is considerably simplified.

- the control device can be constructed from known electronic components such as flip-flops, digital gates, etc.

- the DC voltage source is preferably a DC supply voltage source for all components of the switching device, in particular a 5 V DC voltage source.

- a DC supply voltage source for all components of the switching device, in particular a 5 V DC voltage source.

- MOS field-effect transistors with short switching times are preferably used as the first and second switches 15, 27.

- the comparator 5 should have an input resistance value which is substantially greater than the resistance values R1, R2 of the first and second resistors 13, 17 in order to keep the load on the analog circuit 3 by the comparator negligibly small.

- the comparator threshold U c2 is set to a value of approximately 2/3 of the supply voltage U o of the DC voltage source. It is thereby achieved that the integration capacitor voltage U c does not rise during the measurement up to the flat-ended asymptotic range of the exponential charging function.

- the resistance R2 should be at least a factor of the order of magnitude 100 greater than the resistance value R1 of the first resistor 13, so that the time constant ⁇ 2 of the charge change circuit 3 ⁇ is also large compared to the time constant ⁇ 1 of the charging circuit 3 '.

- a time interval measuring device 2 with a circuit arrangement according to the invention for digital detection of a time interval is described below.

- time intervals Tx between positive edges A+ of a measurement signal TCP with several successive pulses P are to be determined (FIG. 4).

- Time intervals T x are longer than the period Tclk of a reference clock signal Tref, so that several clock pulses of the reference clock signal fall in time in a time interval T x .

- T m denotes a time interval, which is composed of an integer multiple of the period Tclk of the reference clock signal Tref, T1 the error time interval at the beginning of the measuring time interval T x and T'1 the error time interval at the beginning of the measuring time interval beginning with the next positive edge of the measuring signal TCP.

- the clock-synchronous time interval T m is determined by counting the reference clock periods falling in the time interval T m with a counter 41, whereas the error time intervals T 1, T 1 are detected with the circuit arrangement 1 a.

- the time interval measuring device 2 comprises a counting device 41 and a counter enable circuit 43.

- the circuit arrangement 1a is constructed essentially like the circuit arrangement 1 of the previously described exemplary embodiment. Components already described are identified by the letter a after the reference number. Deviations from the previous embodiment are explained below.

- the counting device 41 comprises a pulse pause counter 45 for counting clock pulses of the reference clock signal Tref during a pulse pause between the pulses P of the measurement signal TCP and a pulse length counter 47 for Counting clock pulses of the reference clock signal during the duration of a pulse P.

- a counting device 41 with pulse pause and pulse length counters 45, 47 is advantageous if both pulse durations and pulse pauses are longer than the period duration Tclk of the reference clock signal.

- the advantage lies in the fact that the pulse length counter 47 or the pulse pause counter 45 can be read out alternately by an evaluation device (not shown), while the other counter 45, 47 counts clock pulses. No very high speed requirements with regard to the reading of the counting results of the counters 45, 47 then need be made to the evaluation device in order to register all counting events or clock pulses of the reference clock signal Tref falling within a time interval T m .

- the measurement signal is present at an input 49 of the control device 9a and at an input 50 of the counter enable circuit 43.

- the counter enable circuit 43 controls the readiness to count the counters 45, 47 depending on the occurrence of pulse edges of the measurement signal TCP.

- the periodic reference clock signal Tref is present at the counting inputs of the pulse length counter 47, the pulse pause counter 45 and the counter 7a of the switching device 1a. Furthermore, the reference clock signal Tref is fed to an input 55 of the control device 9a. A takeover signal of the pulse length counter 47 is fed to a control input 57 of the control device 9a.

- the first switch 15a of the circuit arrangement 1a is switched on by the control device 9a and the second switch 27a is switched off.

- the charging phase thus begins, during which the integration capacitor 23a via the first resistor 13a and via the second resistor 17a is loaded.

- the counter enable circuit 43 blocks the readiness for counting of the pulse pause counter 45 and switches on the readiness for counting of the pulse length counter 47.

- the charging phase of the integration capacitor 23a ends with the occurrence of a first negative edge of the reference clock signal Tref counted by the pulse length counter 47 and corresponds to an error time interval T 1 or T 1 to be determined.

- the control device 9a turns off the first switch 15a at the end of the charging phase T1, so that the integration capacitor 23a is further charged during the charge change phase ⁇ T via the second resistor 17a to a voltage threshold U c2 monitored by the comparator 5a.

- the control device 9a monitors the transfer signal from the pulse length counter 47 in order to determine whether the pulse length counter 47 has actually counted the first negative edge of the periodic clock signal Tref after the start of the measuring time interval T 1, and only ends the charging phase T 1 with the occurrence of a negative edge of the reference clock signal. when the edge has been registered by counter 47.

- the counter 7a counts clock pulses or negative edges of the periodic reference clock signal Tref.

- control unit 9a The interaction of the control unit 9a with the counter 7a and the comparator 5a for ending the charge change phase and for controlling the readiness to count (release) of the counter 7a has already been explained in connection with the previously described exemplary embodiment of the invention.

- the circuit arrangement 1a After the charge change phase has elapsed, the circuit arrangement 1a is in its initial state and is so ready for the detection of a next error time interval T1 or T'1.

- the readiness for counting (release) of the pulse length counter 47 is switched off when a negative edge A ⁇ of the measurement signal TCP occurs and that of the pulse pause counter 45 is switched on.

- the counting results of the counters 7a, 45 and 47 are each read out by the evaluation device and temporarily stored after the corresponding counter has come to a standstill.

- the evaluation device calculates a digital value for the measurement time interval Tx to be determined from the temporarily stored count results.

- the counter enable circuit (43) monitors both the measurement signal TCP and the reference signal Tref and only switches the readiness for counting of the pulse length counter 47 or the pulse pause counter 45 on or off when the first positive edge of the reference signal Tref follows the positive or negative edge A+ of the measurement signal TCP (Fig. 4a).

- the triggering a first count event of the pulse length counter negative edge of the reference clock signal Tref which simultaneously ends the charging phase T1 of the integration capacitor 23a, then occurs at the earliest after half a clock period of the reference clock signal Tref after the start of the measuring time interval T x .

- the time interval T 1 or T 1 to be detected with the circuit arrangement 1 a can then be a minimum of half and a maximum of three half period periods Tclk of the reference signal Tref.

- the problem that a first edge of the reference clock signal Tref to be counted by the pulse length counter 47 follows the positive edge A+ of the measurement signal TCP too closely to be registered by the counter 47 is eliminated in this way.

- a typical time behavior of the circuit arrangement 1a is discussed below on the basis of example values for the resistors R1, R2, for the capacitance C of the integration capacitor 23a, for the period Tclk of the reference clock signal Tref and for the comparator threshold U c2 .

- ⁇ T max 98 ⁇ s

- the counter 7a X max 487 count events.

- T 1 300 ns

- the charge change phase then lasts for ⁇ T min - 73 ⁇ s. This corresponds to a counter reading of 364 counter events of the counter 7a, with a reference clock period of 200 ns.

- T x denotes the measurement time interval to be determined between successive positive edges of the measurement signal

- V the count result of the pulse length counter after the pulse duration has expired

- W the counting result of the pause counter after a pulse pause

- X the counting result of the counter 7a after the error time interval T 1 has elapsed

- X 'the counting result of the counter 7a after the error time interval T'1 and Tclk the period of the periodic clock signal Tref.

- Equation (10) is a simple calculation rule for determining the measured value T x from the counting results of the pulse length counter 47, the pulse pause counter 45 and the counter 7a of the circuit arrangement 1a.

- the time interval measurement of successive time intervals with the circuit device 1a according to the invention is even superfluous a calibration measurement.

- the right side of the equation (10) includes the summand Tclk. (V + W), which is measured as an integer multiple of the reference clock period Tclk, and the summand R1 / (R1 + R2) .Tclk (X'-X), which Detection of the error time intervals T1 or T'1 describes.

- the error time intervals T1, T'1 appear to be divided into significantly smaller time quanta than Tclk, as illustrated in the following example:

- the error time intervals are scanned with a time pattern of 200 ns / 101, i.e. the virtual clock period in this example is about 2 ns with a real clock period of 200 ns.

- the reference clock signal Tref can originate, for example, from a system clock source which also clocks a microprocessor unit of the evaluation device.

- a time interval measuring device with a switching device requires only a single supply DC voltage source and also only a single reference clock source.

- the form of the measurement signal required to explain the working principle of the time interval measuring device 2 is not mandatory. In this exemplary embodiment of the invention, too, predetermined signal states other than those described can be selected as delimitation marks of time intervals.

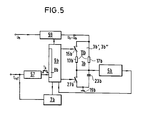

- This further exemplary embodiment is a circuit arrangement for digitally detecting the amplitude of a signal and comprises an analog circuit part 3b, a comparator 5b, a counter 7b, a control device 9b, furthermore a time control circuit 57 and a sample and hold circuit 59.

- the essential principle of the analog circuit part 3b , the comparator 5b, the counter 7b and the control device 9b essentially emerge from the description of the preceding exemplary embodiments; Deviations from this are described below.

- the components already described in the previous exemplary embodiments, which also have the same or similar function in the circuit arrangement 1b for digital detection the amplitude of a signal are used are marked with a b after the corresponding reference number.

- the analog circuit part 3b is connected to a sample and hold circuit 59 which represents the charge source for the integration capacitor 23b.

- the sample and hold circuit 59 samples the unknown signal U m , for example a voltage signal, and outputs a voltage U x which is proportional to a respectively current sample or hold value to the analog circuit 3b.

- the timing control circuit 57 is clocked with the reference clock signal Tref and outputs a timing control signal with signal edges successive at a predetermined time interval Tk to the control device 9b.

- the control device 9b switches the first switch 15b on and the second switch 27b off and thus starts the charging phase of the integration capacitor 23b.

- the integration capacitor 23b is charged during the charging phase via the first and second resistors 13b, 17b to a voltage U c1 which represents the sample hold value of the sample hold circuit applied to the analog circuit.

- the control device switches off the first switch 15b and the readiness to count the counter 7b for counting periodic reference clock pulses, which means that the charge change phase for changing the voltage on the integration capacitor 23b until reaching one predetermined threshold value U c2 monitored by the comparator 5b begins.

- the comparator 5b changes when the Voltage U c2 at the integration capacitor 23b has its output signal, whereupon the control device 9b switches on the second switch 27b and switches off the readiness of the counter 7b to count.

- the control device 9b notifies the sample-and-hold circuit 59 of the readiness for a new measurement cycle via a ready signal, so that the sample-and-hold circuit 59 outputs a new sample value U x for a next measurement cycle.

- an evaluation device (not shown) reads out the counting result of the counter 7b in order to thereby calculate a digital measured value for the signal voltage U x or U m to be detected.

- control device can be provided with delay compensation circuits that take into account different signal delays and switching times or preparation times for components.

- control device in particular include control circuits which ensure that a new measuring cycle can only begin when the previous measuring cycle has been completed.

- the dimensions of the first and second resistors, the integration capacitor, and the period Tclk of the reference clock signal essentially depend on the desired digital resolution of an analog information to be acquired and on the tolerated maximum duration of a measurement cycle.

- the analog circuit 3, 3a, 3b for realizing the charging circuit and the charge change circuit can be replaced by equivalent circuits, for example by a parallel circuit fed by a constant current source, consisting of an integration capacitor, a first and a second resistor with a first switch in series with the first resistor and a second switch in series with the second resistor.

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Measurement Of Unknown Time Intervals (AREA)

Abstract

Description

- Die Erfindung betrifft eine Schaltungsanordnung zur digitalen Erfassung einer analogen Information in der Form des Zeitabstandes zweier aufeinanderfolgender Zustände wenigstens eines Signals oder der Amplitude des Signals,gemäß dem Oberbegriff des Anspruchs 1.

- Eine Schaltungsanordnung zur Erfassung von Zeitabständen, insbesondere zur Messung von kleinen Zeitabständen. im Submillisekundenbereich, die mit konventionellen digitalen Zeitabstandsmeßeinrichtungen nicht oder nur mit unzureichender Auflösung bestimmt werden können, umfaßt einen Integrationskondensator, der über eine Ladeschaltung auf eine die analoge Information repräsentierende Spannung ladbar ist, und eine Ladungsänderungsschaltung, die die Spannung des Integrationskondensators mit einer Änderungsrate kleiner als die der Ladeschaltung ändert. Ein Komparator vergleicht die Spannung an dem Integrationskondensator mit einem vorbestimmten Schwellenwert. Ferner ist ein Zähler vorgesehen, welcher während der Änderung der Spannung des Integrationskondensators mittels der Ladungsänderungsschaltung bis zum Erreichen des vorbestimmten Schwellenwertes periodische Taktpulse zählt.

- Nachdem der Integrationskondensator über die Ladeschaltung auf eine die analoge Information repräsentierende Spannung geladen worden ist, ändert die Ladungsänderungsschaltung die Spannung am Integrationskondensator bis zum Erreichen des durch den Komparator überwachten Schwellenwertes. Die Dauer dieser Spannungsänderung des Integrationskondensators mittels der Ladungsänderungsschaltung hängt einerseits von vorbestimmten Parametern der Schaltungsanordnung und andererseits von dem Wert der die analoge Information repräsentierenden Integrationskondensatorspannung ab. Nach Ablauf der Spannungsänderung am Integrationskondensator stellt das Zählergebnis des Zählers eine digitale Information über die Dauer der Spannungsänderung und damit auch über den Wert der analogen Information dar.

- Bei der konventionellen digitalen Messung von Zeitintervallen auf der Grundlage des Auszählens von Flanken periodischer Taktpulse eines Referenztaktsignals bekannter Periodendauer stellt sich das Problem, daß der Beginn bzw. das Ende des Zeitintervalls im allgemeinen nicht mit einer Flanke des Referenztaktsignals zusammenfällt. Der Zeitabstand zwischen dem Beginn des Meßzeitintervalls und dem Auftreten der ersten, ein Zählereignis auslösenden Flanke des Referenztaktsignals wird nicht richtig erfaßt, da keine vollständige Referenztaktperiode auf diesen Zeitabstand entfällt. Eine entsprechende Situation ergibt sich am Ende des Meßzeitintervalls. Der dadurch entstehende Fehler des digitalen Meßergebnisses wird als +/- 1-Digitalisierungsunsicherheit bezeichnet. Die +/1-Digitalisierungsunsicherheit begrenzt die relative Auflösung einer Zeitabstandsmessung um so stärker, je größer das Verhältnis von Periodendauer des Referenztaktsignals zur Dauer des zu messenden Zeitabstands ist. Zur Erzielung einer hohen Auflösung einer konventionellen Zeitabstandsmessung ist daher eine hohe Referenztaktfrequenz erforderlich. Ein Referenztaktsignal mit sehr hoher konstanter Frequenz erfordert jedoch aufwendige Oszillatorschaltungen und ist störanfällig.

- Eine Möglichkeit der Auflösungsverbesserung bei der Zeitintervallmessung ohne Erhöhung der Referenztaktfrequenz besteht darin, die aufgrund der Asynchronität von Meß-und Referenztaktsignal nicht genau erfaßbaren Zeitabstände am Beginn und am Ende des Meßzeitintervalls mit einer Schaltungsanordnung der oben bezeichneten Art zu bestimmen.

- Eine solche Anwendung einer Schaltungsanordnung zur digitalen Erfassung des Zeitabstandes zweier aufeinanderfolgender Zustände wenigstens eines Signals ist aus der Zeitschrift "Elektronik" Jahrgang 7-1988, Heft 14 Seiten 65 bis 68 bekannt. Die bekannte Schaltungsanordnung arbeitet als Analog-Interpolator eines Zeitintervall-Meßsystems und erfaßt den Zeitabstand T₁ zwischen dem Beginn eines zu messenden Zeitintervalls Tx und einer darauffolgenden vorbestimmten Flanke eines periodischen Referenztaktsignals. Ein weiterer Analog-Interpolator erfaßt den Zeitabstand T′₁ zwischen dem Ende des zu messenden Zeitintervalls und einer darauffolgenden vorbestimmten Flanke des Referenztaktsignals. Die oben genannten vorbestimmten Flanken des Referenztaktsignals schließen ein Zeitintervall Tm ein, dessen Länge einem ganzzahligen Vielfachen der Periodendauer des Referenztaktsignals entspricht und somit durch Auszählen der in dieses taktsynchrone Zeitintervall fallenden Taktperioden mit einer Zähleinrichtung exakt bestimmbar ist. Aus den mit den Analoginterpolatoren und der Zähleinrichtung ermittelten Informationen über die Zeitabschnitte.T₁, T′₁ und Tm berechnet eine Auswerteeinrichtung einen digitalen Meßwert für das zu bestimmende Meßzeitintervall Tx, wodurch eine hohe Zeitauflösung erzielt wird. Die bekannte Schaltungseinrichtung umfaßt einen in einer Integratorschaltung angeordneten Integrationskondensator, eine Ladeschaltung zum Laden des Integrationskondensators mit einem konstanten Strom einer ersten Ladungsquelle während des zu erfassenden Zeitabstandes T₁ bzw. T′₁, eine Ladungsänderungsschaltung zum Entladen des Integrationskondensators mit dem Strom einer zweiten Ladungsquelle, und einen Komparator, der die Spannung am Kondensator mit einem dem Entladezustand des Kondensators entsprechenden Schwellenwert vergleicht. Die erste und zweite Ladungsquelle haben einander entgegengesetzte Polarität. Die erste Ladungsquelle liefert einen konstanten Strom, der um den Faktor tausend größer ist als der konstante Strom der zweiten Ladungsquelle. Die Spannungsänderungen am Integrationskondensator während der Lade-und Entladephase verlaufen linear, jedoch mit unterschiedlichen Vorzeichen. Während der Entladephase zählt ein Zähler periodische Taktimpulse des Referenztaktsignals. Nach Ablauf der Entladephase stellt das Zählergebnis des Zählers eine Information über den zu erfassenden Zeitabstand T₁ bzw. T′₁ dar.

- Die bekannte Schaltungsanordnung hat insbesondere den Nachteil, daß zum Laden und Entladen des Integrationskondensators Ladungsquellen mit entgegengesetzter Polarität erforderlich sind. Darüberhinaus benötigt der Komparator zum Einstellen des Schwellenwertes OV eine negative Gleichspannung. Für den Ladestrom und für den Entladestrom ist eine gute Konstanz zu fordern. Bei Schwankungen des Ladestroms repräsentiert die Integrationskondensatorspannung nach Ablauf der Ladephase das zu erfassende Zeitintervall nur fehlerhaft, während Schwankungen des Entladestromes einen störenden Einfluß auf die Entladezeit und somit auf das Zählergebnis des Zählers haben. Die erforderliche Stabilisierung der Ströme unterschiedlicher Vorzeichen auf jeweils vorbestimmte Werte, die sich darüberhinaus noch wesentlich unterscheiden, ist mit einem hohen Schaltungsaufwand verbunden, der die Schaltungsanordnung kompliziert und teuer macht. Zur Erzielung einer hohen Meßgenauigkeit des bekannten Analog-Interpolators ist eine aufwendige statistische Kalibrierung zur Bestimmung des Verhältnisses von Ladestrom zu Entladestrom nach jedem Meßvorgang erforderlich. Dabei wird jeder der Interpolatoren mit Hilfe von Referenzimpulsen kalibriert, die den Eingängen der Interpolatoren über einen Präzisionsphasenschieber zugeführt werden. Diese Kalibriermethode erfordert neben einem zusätzlichen Schaltungsaufwand einen vergleichsweise großen Rechenaufwand der Auswerteeinrichtung.

- Aus dem Fachbuch: Halbleiterschaltungstechnik, Verfasser: Tietze-Schenk, Dritte Auflage, Springer-Verlag, Heidelberg New York 1980, Seite 662, ist eine Schaltungsanordnung zur digitalen Erfassung der Spannungsamplitude eines analogen Signals bekannt. Diese bekannte Schaltungsanordnung arbeitet nach dem "dual-slope"-Analog-Digital-Wandler-Verfahren und umfaßt einen Integrationskondensator in einer Integratorschaltung mit Operationsverstärker. Der Eingang der Integratorschaltung ist während eines vorbestimmten Integrationszeitintervalls über eine Ladeschaltung mit der Signalquelle elektrisch verbunden, wodurch der Integrationskondensator auf eine der zu messenden Signalspannung proportionale Spannung geladen wird. Nach Ablauf des Integrationszeitintervalls wird der Eingang der Integratorschaltung an eine Referenzspannungsquelle mit konstanter Referenzspannung angeschlossen, um den Integrationskondensator zu entladen. Dabei ändert sich die Kondensatorspannung linear mit der Zeit. Während des Entladevorgangs zählt ein Zähler periodische Taktpulse einer Referenztaktquelle. Ein Komparator beendet den Zählvorgang, wenn die Spannung am Kondensator auf den Wert OV abgesunken ist. Nach Ablauf der Entladephase stellt das Zählergebnis des Zählers eine digitale Information über die zu messende Signalspannung dar.

- Ein Nachteil dieses bekannten Analog-Digital-Wandlers liegt darin, daß für den kontrollierten Entladevorgang des Integrationskondensators und damit für eine hohe Genauigkeit der Spannungsmessung eine sehr gut konstante Referenzspannung erforderlich ist, deren Vorzeichen entgegengesetzt zum Vorzeichen der Meßspannung ist. Die bekannte Schaltungsanordnung erfordert daher wenigstens eine positive und eine negative Spannungsquelle mit jeweils sehr gut konstanter Ausgangsspannung, und eine Schalteinrichtung, die die Referenzspannung umpolt.

- Der Erfindung liegt die Aufgabe zugrunde, eine Schaltungsanordnung zur digitalen Erfassung einer analogen Information in der Form des Zeitanbstandes zweier aufeinanderfolgender Zustände wenigstens eines Signals oder der Amplitude des Signals anzugeben, deren Schaltungsaufwand und Störanfälligkeit gering ist.

- Diese Aufgabe wird erfindungsgemäß dadurch gelöst, daß die Ladeschaltung und die Ladungsänderungsschaltung die Spannung des Integrationskondensators in gleicher Richtung ändern und an eine gemeinsame Ladungsquelle angeschlossen sind.

- Die erfindungsgemäße Schaltungsanordnung ist mit geringem Schaltungsaufwand realisierbar und arbeitet nahezu störungsunanfällig. Insbesondere ist zum Betrieb der Schaltung nur eine Ladungsquelle, zum Beispiel eine Gleichspannungsquelle erforderlich. Ein weiterer Vorteil liegt darin, daß die Schaltungsanordnung ohne Einschränkung ihrer Zuverlässigkeit aus vergleichsweise preiswerten Bauelementen aufgebaut werden kann.

- Mit einer Weiterbildung der Erfindung zur digitalen Erfassung des Zeitabstandes zweier aufeinanderfolgender Zustände wenigstens eines Signals, gemäß Anspruch 2, wird sichergestellt, daß die Ladeschaltung nur während des zu erfassenden Zeitabstandes wirksam geschaltet ist, um den Integrationskondensator auf eine den zu messenden Zeitabstand repräsentierende Spannung zu laden. Ferner ist sichergestellt, daß die Spannungsänderung des Integrationskondensators mittels der Ladungsänderungsschaltung unmittelbar im Anschluß an den zu erfassenden Zeitabstand erfolgt, wodurch die den Zeitabstand repräsentierende Spannung am Integrationskondensator ohne Verfälschung durch Leckströme, störungssicher und vergleichsweise schnell ausgewertet werden kann.

- Gemäß der Weiterbildung der Erfindung nach Anspruch 3 lassen sich verschiedene Signalzustände eines Signals als Begrenzungsmarken eines zu messenden Zeitabstandes auswählen. Die Signalzustände können beispielsweise steigende oder fallende Flanken eines Meßsignals sein.

- Gemäß der Weiterbildung der Erfindung nach Anspruch 4 lassen sich Zeitabstände zwischen Signalzuständen von Signalen aus verschiedenen Quellen erfassen.

- Durch Verwendung einer Gleichspannungsquelle als Ladungsquelle, insbesondere einer Versorgungsgleichspannungsquelle der Schaltungsanordnung wird der Schaltungsaufwand zur Stromversorgung minimal gehalten.

- Die Weiterbildung der Erfindung gemäß Anspruch 6, zur Messung der Amplitude des Signals, gewährleistet ein konstantes Integrationszeitintervall zum Laden des Integrationskondensators auf eine die Amplitude des analogen Signals repräsentierende Spannung. Durch Auszählen von periodischen Taktpulsen, die in die sich an das Integrationszeitintervall anschließende Ladungsänderungsphase fallen, wird eine digitale Information über die zu erfassende analoge Signalspannung erhalten.

- Eine Abtast-Halte-Schaltung zur Zwischenspeicherung von Signalamplitudenwerten ermöglicht die digitale Erfassung von Amplitudenwerten zeitveränderlicher Signale.

- Die Ladeschaltung läßt sich durch Einstellen eines ersten Widerstandswertes und die Ladungsänderungsschaltung durch Einstellen eines zweiten Widerstandswertes der Widerstandsschaltung nach Anspruch 8 einfach realisieren, wobei Lade und Ladungsänderungsschaltung mit einer gemeinsamen Ladungsquelle auskommen.

- Im Anspruch 9 wird eine sehr einfache Möglichkeit zur Änderung des Widerstandswertes der Widerstandsschaltung angegeben. Ein besonderer Vorteil der Widerstandsschaltung nach Anspruch 9 besteht darin, daß der Ladungsfluß zum Kondensator während der Ladephase und während der Ladungsänderungsphase im wesentlichen von störunanfälligen passiven Bauelementen, nämlich Ohm'schen Widerständen, abhängt. Die vorgeschlagene Widerstandsschaltung gewährleistet bei sehr einfachem Aufbau eine nahezu störunanfällige Erfassung der analogen Information. Hinzukommt, daß Widerstände mit hoher Präzision, Temperaturunabhängigkeit und Langzeitstabilität ihrer Widerstandswerte mit den heutzutage vorhandenen Technologien ohne Schwierigkeiten bei gleichzeitig geringen Kosten herstellbar sind, was zur preiswerten Realisierung der Schaltungsanordnung beiträgt.

- Dadurch, daß der zweite Widerstand der Widerstandsschaltung nach Anspruch 9 einen wesentlich größeren Widerstandswert als der erste Widerstand hat, ist die Änderungsrate der Spannung des Integrationskondensators während der Spannungsänderung mittels der Ladungsänderungsschaltung wesentlich kleiner als die Änderungsrate der Spannungsänderung am Integrationskondensator während der Ladephase mittels der Ladeschaltung. Dies ist insbesondere von Bedeutung, wenn Zeitabstände digital erfaßt werden sollen, die etwa gleich lang oder kürzer als die Periodendauer des periodischen Taktsignals sind. Die von der Dauer der Ladephase abhängige Dauer der Ladungsänderungsphase kann durch Wahl des Widerstandsverhältnisses des ersten und zweiten Widerstandes immer so lang gewählt werden, daß mehrere periodische Taktpulse während der Ladungsänderungsphase auftreten, so daß durch Zählen dieser Taktpulse eine digitale Information über die Dauer der Ladephase erhalten wird.

- Entsprechend der Weiterbildung der Erfindung nach Anspruch 11 kann der Integrationskondensator durch einen zweiten Schalter der Steuereinrichtung kurzgeschlossen werden, um die Anfangsbedingungen für einen neuen Meßvorgang herzustellen.

- Ausführungsbeispiele der Erfindung sind in den Zeichnungen dargestellt und werden im folgenden näher beschrieben.

- Es zeigen

- Fig. 1 eine schematische Darstellung einer Schaltungsanordnung nach der Erfindung zur digitalen Erfassung eines Zeitabstandes zwischen aufeinanderfolgenden Zuständen wenigstens eines Signals,

- Fig. 2 ein Signalablaufdiagramm zur Erläuterung der Arbeitsweise der Schaltungsanordnung nach Fig. 1,

- Fig. 3 eine schematische Darstellung einer Zeitintervall-Meßeinrichtung mit einem Ausführungsbeispiel der Erfindung,

- Fig. 4 und Fig. 4a ein Signalablaufdiagramm zur Erläuterung der Arbeitsweise der Zeitintervall-Meßeinrichtung nach Fig. 3 und

- Fig. 5 eine schematische Darstellung eines Ausführungsbeispiels der Erfindung zur digitalen Erfassung der Amplitude eines Signals.

- Die in Fig. 1 mit 1 bezeichnete Schaltungsanordnung nach der Erfindung umfaßt einen analogen Schaltungsteil 3, einen Komparator 5, einen Zähler 7 und eine Steuereinrichtung 9. Der analoge Schaltungsteil 3 umfaßt eine an den Pluspol 6 einer positiven Gleichspannungsquelle angeschlossene Widerstandsschaltung 11 mit einem ersten Widerstand 13 in Serie zu einem ersten Schalter 15 in einem ersten Zweig 16 und mit einem zweiten Widerstand 17 parallel zum ersten Widerstand 13 und zum ersten Schalter 15 in einem zweiten Zweig 18, ferner in Serie zur Widerstandsschaltung 11 eine an das Bezugspotential 19 (Masse) der Gleichspannungsquelle angeschlossene Parallelschaltung 21 aus einem Integrationskondensator 23 in einem dritten Zweig 25 und einem zweiten Schalter 27 in einem vierten Zweig 29.

- Der erste Schalter 15 und der zweite Schalter 27 werden von der Steuereinrichtung 9 gesteuert und schalten je nach Schaltzustand einen Strom durch den ersten Zweig 16 bzw. durch den vierten Zweig 29 ein oder aus. Ein Eingang 31 des Komparators 5 ist mit einem ersten Anschluß 33 des Integrationskondensators 23 elektrisch verbunden. Der Komparator 5 vergleicht die Spannung Uc am Integrationskondensator 23 mit einem vorbestimmten Schwellenwert Uc2 und ändert den Zustand seines Komparatorausgangssignals, wenn die Kondensatorspannung Uc den Schwellenwert Uc2 erreicht. Ein das Komparatorausgangssignal führender Ausgang 35 des Komparators 5 ist mit einem Eingang 37 der Steuereinrichtung 9 elektrisch verbunden. Ein Signalzustandsdetektor 8 der Steuereinrichtung 9 detektiert vorbestimmte aufeinanderfolgende Zustandsänderungen wenigstens eines Meß-, beispielsweise die positive und negative Flanke eines Rechteckpulses eines Meßsignals, und die Steuereinrichtung 9 steuert den ersten Schalter 15 bzw. zweiten Schalter 27 in Abhängigkeit vom Auftreten der vorbestimmten Zustandsänderungen wenigstens eines Meßsignals bzw. in Abhängigkeit vom Auftreten einer Zustandsänderung des Komparatorausgangssignals. Die Steuereinrichtung 9 ist ferner mit einem Zählfreigabeeingang 39 des Zählers 7 elektrisch verbunden, um die Zählbereitschaft des Zählers 7 in Abhängigkeit vom Auftreten einer vorbestimmten Zustandsänderung wenigstens eines Meßsignals bzw. des Komparatorausgangssignals ein- bzw. auszuschalten. Bei eingeschalteter Zählbereitschaft zählt der Zähler 7 Taktpulse eines periodischen Taktsignals Tref konstanter Taktperiodendauer Tclk.

- Anhand eines Beispiels einer Pulslängenmessung mit dem Ausführungsbeispiel der Erfindung wird nachstehend die zeitliche Folge verschiedener Schritte bei der digitalen Erfassung des Zeitabstandes T₁ zwischen der positiven und der darauffolgenden negativen Flanke eines Rechtecksignalpulses P beschrieben. Dazu wird auf Fig. 1 und Fig. 2 Bezug genommen. Vor dem Auftreten des Pulses P ist der zweite Schalter 27 eingeschaltet und damit der Integrationskondensator 23 über den vierten Zweig 29 kurzgeschlossen und entladen (Ausgangszustand der Schaltung). Bei Auftreten der positiven Flanke A₁ des Rechteckpulses P detektiert der Signalzustandsdetektor 8 der Steuereinrichtung 9 die positive Flanke A₁ als Startsignal einer Messung, und die Steuereinrichtung 9 schaltet durch Ausgabe eines Steuersignals gleichzeitig den zweiten Schalter 27 aus, so daß kein Strom über den vierten Zweig 29 an dem Integrationskondensator 23 vorbeifließen kann. Damit setzt eine Ladephase zum Laden des Integrationskondensators 23 auf eine den Zeitabstand T₁ zwischen den Pulsflanken A₁, A₂ des Rechteckpulses P repräsentierende Spannung Uc1 ein. Während der Ladephase ist der erste Schalter 15 eingeschaltet, so daß der Integrationskondensator 23 über den ersten und zweiten Widerstand 13, 17 geladen wird. In der Konfiguration, daß der erste Schalter 15 eingeschaltet und der zweite Schalter 27 ausgeschaltet ist, arbeitet die Analogschaltung 3 als Ladeschaltung 3′ mit einer Ladezeitkonstante τ₁.

- Bei Auftreten der negativen Flanke A₂ des Rechteckpulses P detektiert der Signalzustandsdetektor 8 der Steuereinrichtung 9 die negative Flanke A₂ als Stoppsignal für die Ladephase, und die Steuereinrichtung 9 beendet die Ladephase durch Ausschalten des ersten Schalters 15. Ferner gibt die Steuereinrichtung 9 mit Beendigung der Ladephase ein Signal an den Zähler 7 aus, um die Zählbereitschaft des Zählers 7 einzuschalten, so daß dieser Taktpulse des periodischen Taktsignals Tref zählt. Unmittelbar an die Ladephase schließt sich eine Ladungsänderungsphase ΔT an, in der der Integrationskondensator 23 nur noch über den zweiten Widerstand 17 geladen wird. In der während der Ladungsänderungsphase ΔT vorliegenden Konfiguration, daß erster und zweiter Schalter 15, 27 ausgeschaltet sind, arbeitet die Analogschaltung 3 als Ladungsänderungsschaltung 3˝ zur linderung der Spannung Uc am Integrationskondensator 23 bis zum Erreichen des von dem Komparator 5 überwachten Schwellenwertes Uc2. Die Ladezeitkonstante τ2 der Ladungsänderungsschaltung ist wesentlich größer als die Ladezeitkonstante τ1 der Ladeschaltung, so daß die Spannung Uc am Integrationskondensator 23 während der Ladungsänderungsphase ΔT mit einer wesentlich kleineren Änderungsrate als während der Ladephase T₁ geändert wird. Die Zeitkonstante τ2 der Ladungsänderungsschaltung ist größer als die Zeitkonstante τ1 der Ladeschaltung, da der Gesamtwiderstand der Widerstandsschaltung 11 während der Ladungsänderungsphase (Ladung des Integrationskondensators 23 über den zweiten Widerstand 17) größer ist als während der Ladephase (Ladung des Integrationskondensators 23 über eine Parallelschaltung aus erstem und zweiten Widerstand 13, 17).

- Lade- und Ladungsänderungsschaltung 3′, 3˝ ändern die Spannung Uc am Integrationskondensator 23 in gleicher Richtung. Wenn die Spannung Uc am Integrationskondensator 23 den vorbestimmten Schwellenwert Uc2 erreicht, ändert der Komparator 5 den Zustand des Komparatorausgangssignals, woraufhin die Steuereinrichtung 9 die Zählbereitschaft des Zählers 7 ausschaltet und den zweiten Schalter 27 einschaltet. Der Integrationskondensator 23 wird danach über den zweiten Schalter 27 kurzgeschlossen und entladen, wodurch die Schaltungsanordnung nach der Erfindung in ihren Ausgangszustand zurückversetzt wird. Das Zählergebnis X des Zählers 7 wird nach Ablauf der Ladungsänderungsphase von einer Auswerteeinrichtung (nicht gezeigt) ausgelesen und als digitale Information zur Berechnung eines Meßwertes für den Zeitabstand T₁ zwischen den Flanken A₁, A₂ des Meßsignals ausgewertet.

- Das wesentliche Arbeitsprinzip des Ausführungsbeispiels der Erfindung wurde vorstehend anhand der Erläuterung einer Pulslängenmessung beschrieben. Das Ausführungsbeispiel ist jedoch nicht auf die Messung von Rechteckpulsdauern beschränkt.

- Der Signalzustandsdetektor 8 der Steuereinrichtung 9 kann wahlweise ebenso auf andere vorbestimmte Signalzustände als die oben beschriebenen reagieren. Insbesondere können die Signalzustände zum Starten und Stoppen der Ladephase des Integrationskondensators und damit des Meßzeitintervalls von verschiedenen Signalquellen stammen.

- Die Schaltungsanordnung nach der Erfindung ist in der Lage, Selbstkalibriermessungen auszuführen. Vor Beginn der Kalibriermessung ist der erste Schalter 15 ausgeschaltet und der zweite Schalter 27 eingeschaltet (Ausgangsschaltzustand), so daß der Integrationskondensator 23 entladen ist. Die Steuereinrichtung 9 startet die Kalibriermessung durch Ausschalten des zweiten Schalters 27 und Einschalten der Zählbereitschaft des Zählers 7. Der Integrationskondensator 23 wird daraufhin nur über den zweiten Widerstand 17 von seinem Entladezustand bis zum Erreichen des Schwellenwertes Uc2 geladen. Bei Erreichen des Schwellenwertes Uc2 ändert der Komparator 5 den Zustand seines Ausgangssignals, woraufhin die Steuereinrichtung 9 die Kalibriermessung durch Ausschalten der Zählbereitschaft des Zählers 7 und Einschalten des zweiten Schalters 27 beendet. Während der Kalibriermessung zählt der Zähler 7 die Taktpulse des periodischen Taktsignals Tref. Das Zählergebnis XT des Zählers 7 wird nach Ablauf der Kalibriermessung von der Auswerteeinrichtung ausgelesen und zwischengespeichert. Dieses Zählergebnis XT der Kalibriermessung wird von der Auswerteeinrichtung in die Auswertung eines oder mehrerer zu messender Zeitabstände T₁ einbezogen.

- Nachstehend werden mathematische Grundlagen zur Ermittlung eines gesuchten Zeitabstandes T₁ zwischen aufeinanderfolgenden Zuständen wenigstens eines Signals dargelegt.

-

-

-

-

-

- In Gleichung (5) sind die Zeitkonstanten τ₁ und τ₂ durch die Widerstandswerte R₁ und R₂ und durch die Kapazität C des Integrationskondensators 23 ausgedrückt. Das Symbol ΔT für die Dauer der Ladungsänderungsphase ist in Gleichung (5) durch den äquivalenten Ausdruck: X Tclk ersetzt worden. X bezeichnet das Zählergebnis des Zählers 7 nach Ablauf der Ladungsänderungsphase und Tclk die Periodendauer des periodischen Taktsignals Tref. Mit Gleichung (5) kann der zu erfassende Zeitabstand T₁ aus dem Zählergebnis X und den ansonsten bekannten Parametern der Gleichung (5) bestimmt werden.

- Die Gleichung (5) läßt sich durch Einbeziehen des Zählergebnisses XT einer Kalibriermessung noch wesentlich vereinfachen. Die Spannungsänderung Uc des Integrationskondensators 23 von seinem Entladezustand bis zum Erreichen des Schwellenwertes Uc2 erfolgt bei einer Kalibriermessung in der Zeit T₃, die durch das Produkt aus Zählergebnis XT und Periodendauer Tclk des periodischen Taktsignals Tref beschrieben werden kann:

-

-

- Nach Gleichung (8) wird die Auswertung des Zählergebnisses X zur Bestimmung eines Zeitabstandes T₁ zweier aufeinanderfolgender Zustände wenigstens eines Signals durch Einbeziehung des Zählergebnisses XT einer Kalibriermessung wesentlich vereinfacht.

- In die Auswertungsgleichung (8) für die digitale Erfassung des Zeitabstardes T₁ zweier aufeinanderfolgender Zustände wenigstens eines Signals geht weder der Wert der Versorgungsspannung Uo noch der Schwellenwert Uc2 des Komparators 5, noch der Kapazitätswert C des Integrationskondensators 23 ein. Eine Langzeitstabilität der vorstehend genannten Größen ist daher nicht erforderlich, wenn eine Zeitabstandsmessung oder eine Meßreihe von Zeitabstandsmessungen mit der Schaltungsanordnung nach der Erfindung jeweils im Zusammenhang mit einer Kalibriermessung durchgeführt wird. Es ist dann lediglich eine leicht zu erfüllende Kurzzeitstabilität der oben genannten Größen für jeweils einen Meßvorgang zu fordern. Auf teure Präzisionsbauelemente mit hoher Langzeitstabilität oder auf aufwendige Stabilisierungsschaltungen kann daher verzichtet werden. Da der Kapazitätswert C des Integrationskondensators 23 nicht in die Gleichung (8) eingeht, spielen auch größere Abweichungen vom Nennkapazitätswert, beispielsweise durch Fertigungstoleranzen, keine Rolle. Die einzigen in die Auswertung eingehenden Geräteparameter sind die Widerstandswerte R₁ und R₂ und die Periodendauer Tclk des Taktsignals. Diese Werte sind sehr einfach zu ermitteln und haben eine gute Konstanz.

- Zu diesen ganz wesentlichen Vorteilen der Schaltungsanordnung nach der Erfindung kommt hinzu, daß die Kalibriermessung sehr einfach durchzuführen ist und, statt zusätzlichen Rechenaufwand zu erfordern, die rechnerische Auswertung zur Ermittlung eines Meßzeitintervalls wesentlich vereinfacht.

- Die Steuereinrichtung kann aus an sich bekannten elektronischen Bauteilen wie Flipflops, digitale Gatter usw. aufgebaut werden.

- Die Gleichspannungsquelle ist vorzugsweise eine Versorgungsgleichspannungsquelle für alle Komponenten der Schalteinrichtung, insbesondere eine 5-V-Gleichspannungsquelle. Durch die Verwendung nur einer Spannungsquelle für alle Komponenten der Schaltungseinrichtung nach der Erfindung ist der Schaltungsaufwand für die Stromversorgung gering. Als erster und zweiter Schalter 15, 27 werden bevorzugt MOS-Feldeffekttransistoren mit kurzen Schaltzeiten verwendet. Der Komparator 5 sollte einen Eingangswiderstandswert haben, der wesentlich größer ist als die Widerstandswerte R₁, R₂ des ersten und zweiten Widerstandes 13, 17, um die Belastung der Analogschaltung 3 durch den Komparator vernachlässigbar klein zu halten.

- In einem bevorzugten Ausführungsbeispiel ist die Komparatorschwelle Uc2 auf einen Wert von näherungsweise 2/3 der Versorgungsspannung Uo der Gleichspannungsquelle eingestellt. Dadurch wird erreicht, daß die Integrationskondensatorspannung Uc während einer Messung nicht bis in den flachauslaufenden asymptotischen Bereich der exponentiellen Ladefunktion ansteigt. Für die Erfassung Kleiner Zeitabstände sollte der Widerstand R₂ mindestens um einen Faktor der Größenordnung 100 größer sein als der Widerstandswert R₁ des ersten Widerstandes 13, so daß die Zeitkonstante τ₂ der Ladungsänderungsschaltung 3˝ ebenfalls groß gegenüber der Zeitkonstante τ₁ der Ladeschaltung 3′ ist.

- Nachstehend wird eine Zeitintervallmeßeinrichtung 2 mit einer Schaltungsanordnung nach der Erfindung zu digitalen Erfassung eines Zeitabstandes beschrieben.

- Mit der Zeitintervallmeßeinrichtung 2 sollen beispielsweise Zeitintervalle Tx zwischen positiven Flanken A₊ eines Meßsignals TCP mit mehreren aufeinanderfolgenden Pulsen P bestimmt werden (Fig. 4). Die zu bestimmenden. Zeitintervalle Tx sind länger als die Periodendauer Tclk eines Referenztaktsignals Tref, so daß mehrere Taktpulse des Referenztaktsignals zeitlich in ein Zeitintervall Tx fallen. Wie aus Fig. 4 zu ersehen ist, kann die Länge Tx des zu ermittelnden Zeitintervalls durch die Beziehung:

- Die Zeitintervallmeßeinrichtung 2 umfaßt neben einer Schaltungsanordnung nach der Erfindung 1a eine Zähleinrichtung 41 und eine Zählerfreigabeschaltung 43. Die Schaltungsanordnung 1a ist im wesentlichen wie die Schaltungsanordnung 1 des vorher beschriebenen Ausführungsbeispiels aufgebaut. Bereits beschriebene Komponenten sind mit dem Buchstaben a hinter der Bezugsziffer gekennzeichnet. Abweichungen vom vorhergehenden Ausführungsbeispiel werden nachstehend erläutert.

- Die Zähleinrichtung 41 umfaßt einen Pulspausenzähler 45 zur Zählung von Taktpulsen des Referenztaktsignals Tref während einer Pulspause zwischen den Pulsen P des Meßsignals TCP und einen Pulslängenzähler 47 zur Zählung von Taktpulsen des Referenztaktsignals während der Dauer eines Pulses P. Eine derartige Zähleinrichtung 41 mit Pulspausen- und Pulslängenzähler 45, 47 ist dann von Vorteil, wenn sowohl Pulsdauern als auch Pulspausen länger sind, als die Periodentauer Tclk des Referenztaktsignals. Der Vorteil liegt darin, daß der Pulslängenzähler 47 bzw. der Pulspausenzähler 45 abwechselnd von einer Auswerteeinrichtung (nicht gezeigt) ausgelesen werden können, während der jeweils andere Zähler 45, 47 Taktpulse zählt. An die Auswerteeinrichtung brauchen dann keine sehr hohen Geschwindigkeitsanforderungen bezüglich des Auslesens der Zählergebnisse der Zähler 45, 47 gestellt werden, um alle in ein Zeitintervall Tm fallende Zählereignisse bzw. Taktpulse des Referenztaktsignals Tref zu registrieren.

- Das Meßsignal liegt an einem Eingang 49 der Steuereinrichtung 9a und an einem Eingang 50 der Zählerfreigabeschaltung 43 an. Die Zählerfreigabeschaltung 43 steuert die Zählbereitschaft der Zähler 45, 47 in Abhängigkeit vom Auftreten von Pulsflanken des Meßsignals TCP.

- Das periodische Referenztaktsignal Tref liegt an den Zähleingängen des Pulslängenzählers 47, des Pulspausenzählers 45 und des Zählers 7a der Schalteinrichtung 1a an. Ferner ist das Referenztaktsignal Tref einem Eingang 55 der Steuereinrichtung 9a zugeführt. Ein Übernahmesignal des Pulslängenzählers 47 ist einem Kontrolleingang 57 der Steuereinrichtung 9a zugeführt.

- Tritt eine positive Flanke A₊ des Meßsignals TCP auf, so wird der erste Schalter 15a der Schaltungsanordnung 1a durch die Steuereinrichtung 9a eingeschaltet und der zweite Schalter 27a ausgeschaltet. Damit beginnt die Ladephase, während der der Integrationskondensator 23a über den ersten Widerstand 13a und über zweiten Widerstand 17a geladen wird. Mit Auftreten der positiven Flanke A₊ des Meßsignals TCP sperrt die Zählerfreigabeschaltung 43 die Zählbereitschaft des Pulspausenzählers 45 und schaltet die Zählbereitschaft des Pulslängenzählers 47 ein. Die Ladephase des Integrationskondensators 23a endet mit dem Auftreten einer ersten von dem Pulslängenzähler 47 gezählten negativen Flanke des Referenztaktsignals Tref und entspricht einem zu bestimmenden Fehlerzeitintervall T₁ bzw. T′₁. Die Steuereinrichtung 9a schaltet mit Beendigung der Ladephase T₁ den ersten Schalter 15a aus, so daß der Integrationskondensator 23a während der Ladungsänderungsphase ΔT über den zweiten Widerstand 17a bis zu einem von dem Komparator 5a überwachten Spannungsschwellenwert Uc2 weitergeladen wird. Die Steuereinrichtung 9a überwacht das Übernahmesignal vom Pulslängenzähler 47, um festzustellen, ob der Pulslängenzähler 47 die erste negative Flanke des periodischen Taktsignals Tref nach Beginn des Meßzeitintervalls T₁ tatsächlich gezählt hat, und beendet die Ladephase T₁ mit dem Auftreten einer negativen Flanke des Referenztaktsignals erst dann, wenn die Flanke von dem Zähler 47 registriert wurde. Während der Ladungsänderungsphase ΔT zählt der Zähler 7a Taktpulse bzw. negative Flanken des periodischen Referenztaktsignals Tref.

- Das Zusammenwirken der Steuereinheit 9a mit dem Zähler 7a und dem Komparator 5a zur Beendigung der Ladungsänderungsphase und zur Steuerung der Zählbereitschaft (Freigabe) des Zählers 7a ist bereits in Zusammenhang mit dem vorher beschriebenen Ausführungsbeispiel der Erfindung erläutert worden.

- Nach Ablauf der Ladungsänderungsphase befindet sich die Schaltungsanordnung 1a in ihrem Ausgangszustand und ist damit für die Erfassung eines nächsten Fehlerzeitintervalls T₁ bzw. T′₁ bereit. Die Zählbereitschaft (Freigabe) des Pulslängenzählers 47 wird bei Auftreten einer negativen Flanke A₋ des Meßsignals TCP ausgeschaltet und die des Pulspausenzählers 45 wird eingeschaltet. Die Zählergebnisse der Zähler 7a, 45 und 47 werden jeweils nach dem Stillstand des entsprechenden Zählers von der Auswerteeinrichtung ausgelesen und zwischengespeichert. Die Auswerteeinrichtung berechnet aus den zwischengespeicherten Zählergebnissen einen digitalen Wert für das zu bestimmende Meßzeitintervall Tx.

- In einer vorteilhaften Variante des vorstehend beschriebenen Ausführungsbeispiels überwacht die Zählerfreigabeschaltung (43) sowohl das Meßsignal TCP als auch das Referenzsignal Tref und schaltet die Zählbereitschaft des Pulslängenzählers 47 bzw. des Pulspausenzählers 45 erst dann ein bzw. aus, wenn die erste positive Flanke des Referenzsignals Tref auf die positive bzw. negative Flanke A₊ des Meßsignals TCP folgt (Fig. 4a). Die ein erstes Zählereignis des Pulslängenzählers auslösende negative Flanke des Referenztaktsignals Tref, die gleichzeitig die Ladephase T₁ des Integrationskondensators 23a beendet, tritt dann frühestens nach Ablauf einer halben Taktperiode des Referenztaktsignals Tref nach Beginn des Meßzeitintervalls Tx auf. Der mit der Schaltungsanordnung 1a zu erfassende Zeitabstand T₁ bzw. T′₁ kann dann minimal eine halbe und maximal drei halbe Periodendauern Tclk des Referenzsignals Tref lang sein. Das Problem, daß eine erste vom Pulslängenzähler 47 zu zählende Flanke des Referenztaktsignals Tref zu dicht auf die positive Flanke A₊ des Meßsignals TCP folgt, um vom Zähler 47 registriert zu werden, ist auf diese Weise beseitigt.

- Nachstehend wird anhand von Beispielswerten für die Widerstände R₁, R₂, für die Kapazität C des Integrationskondensators 23a, für die Periodendauer Tclk des Referenztaktsignals Tref und für die Komparatorschwelle Uc2 ein typisches Zeitverhalten der Schaltungsanordnung 1a zu diskutiert.

- Es sei:

- Tclk

- =200 ns,

- R₁

- =820 Ohm,

- R₂

- =100 kOhm,

- C

- =1 nF und

- Uc2

- =2/3 Uo, wobei Uo die Spannung der Gleichspannungsquelle bezeichnet.

- Entsprechend der oben erwähnten Variante der Zeitintervall-Meßeinrichtung nach der Erfindung kann die Dauer eines Fehlerzeitintervalls T₁ zwischen 100 ns und 300 ns liegen, wenn die Referenztaktperiodendauer Tclk = 200 ns zugrunde gelegt wird. Mit den obigen Werten für R₁, R₂ und C ergibt sich für die Ladeschaltung 3a′ die Zeitkonstante τ₁ = 813 ns. Während der Minimaldauer des Zeitabstandes T₁ = 100 ns wird der Integrationskondensator 23a mit einer Ladezeitkonstante τ₁ = 813 ns auf die Spannung Uc1 = 0,11 Uo geladen. Die Ladungsänderungsschaltung 3a˝ benötigt dann eine Zeit von ΔTmax = 98 µs zum Weiterladen des Integrationskondensators 23a bis zum Erreichen der Komparatorschwelle 2/3 Uo. Während der Ladungsänderungsphase ΔTmax = 98 µs summiert der Zähler 7a Xmax = 487 Zählereignisse auf. Während der Maximaldauer des Zeitabstandes T₁ = 300 ns wird der Integrationskondensator 23a mit der Kapazität 1 nF auf Uc1 = 0,3 Uo geladen. Die Ladungsänderungsphase dauert dann ΔTmin - 73 µs lang. Dem entspricht ein Zählerstand von 364 Zählereignissen des Zählers 7a, bei einer Referenztaktperiodendauer von 200 ns.

- Die Auswertungsgleichung zur Berechnung von Tx geht auf Gleichung (9) zurück.

-

- Darin bezeichnet Tx das zu bestimmende Meßzeitintervall zwischen aufeinanderfolgenden positiven Flanken des Meßsignals,

V das Zählergebnis des Pulslängenzählers nach Ablauf der Pulsdauer,

W das Zählergebnis des Pausenzählers nach Ablauf einer Pulspause,

X das Zählergebnis des Zählers 7a nach Ablauf des Fehlerzeitintervalls T₁,

X′ das Zählergebnis des Zählers 7a nach Ablauf des Fehlerzeitintervalls T′₁ und Tclk die Periodendauer des periodischen Taktsignals Tref. - Gleichung (10) ist eine einfache Berechnungsvorschrift zur Bestimmung des Meßwertes Tx aus den Zählergebnissen des Pulslängenzählers 47, des Pulspausenzählers 45 und des Zählers 7a der Schaltungsanordnung 1a.

- Da in die Gleichung (10) nur die Zählergebnisse der Zähler 7a, 45, 47, die bekannten Widerstandswerte R₁ bzw. R₂ und der bekannte Periodendauerwert Tclk des periodischen Taktsignals eingehen, erübrigt sich bei der Zeitintervallmessung aufeinanderfolgender Zeitintervalle mit der Schaltungseinrichtung 1a nach der Erfindung sogar eine Kalibriermessung.

- Auch bei diesem Anwendungsbeispiel einer Schaltungsanordnung nach der Erfindung sind keine hohen Anforderungen an die Kurzzeitstabilität der Versorgungsspannung Uo oder der Komparatorschwelle Uc2 zu stellen.

- Die rechte Seite der Gleichung (10) umfaßt den Summanden Tclk.(V+W), der als ganzzahliges Vielfaches der Referenztaktperiode Tclk abgemessen wird, und den Summanden R₁/(R₁ + R₂).Tclk (X′-X), der die Erfassung der Fehlerzeitintervalle T₁ bzw. T′₁ beschreibt. Die Fehlerzeitintervalle können als Vielfaches einer "virtuellen Taktperiode" Tclkvirtuell dargestellt werden, mit:

- Je nach den Widerstandswerten R₁ und R₂ erscheinen die Fehlerzeitintervalle T₁, T′₁ in wesentlich kleinere Zeitquanten als Tclk unterteilt, wie an nachstehendem Beispiel veranschaulicht wird:

- Es sei:

- Tclk

- = 200 ns,

- R₁

- = 1 kOhm,

- R₂

- = 100 kOhm

- Mit diesen Werten für die Taktperiodendauer Tclk und für die Widerstände R₁, R₂ werden die Fehlerzeitintervalle mit einem Zeitraster von 200 ns/101 abgetastet, d.h., die virtuelle Taktperiodendauer beträgt bei diesem Beispiel etwa 2 ns bei einer realen Taktperiodendauer von 200 ns.

- Aus den vorstehenden Betrachtungen geht hervor, daß mit einer Schaltungsanordnung nach der Erfindung zur digitalen Erfassung von Zeitabständen zweier aufeinanderfolgender Zustände wenigstens eines Signals eine extrem hochauflösende digitale Zeitabstandmessung möglich ist, auch wenn das Referenztaktsignal Tref eine Periodendauer Tclk von lediglich 200 ns hat. Das Referenztaktsignal Tref kann beispielsweise von einer Systemtaktquelle stammen, die auch eine Mikroprozessoreinheit der Auswerteeinrichtung taktet.

- Eine Zeitintervallmeßeinrichtung mit einer Schalteinrichtung nach der Erfindung erfordert nur eine einzige Versorgungsgleichspannungsquelle und ebenfalls nur eine einzige Referenztaktquelle.

- Die zur Erläuterung des Arbeitsprinzips der Zeitintervallmeßeinrichtung 2 vorausgesetzte Form des Meßsignals ist nicht zwingend. Auch bei diesem Ausführungsbeispiel der Erfindung können andere vorbestimme Signalzustände als die beschriebenen als Begrenzungsmarken von Zeitabständen gewählt werden.

- Nachstehend wird bezugnehmend auf die Fig. 5 ein weiteres Ausführungsbeispiel der Erfindung beschrieben. Dieses weitere Ausführungsbeispiel ist eine Schaltungsanordnung zur digitalen Erfassung der Amplitude eines Signals und umfaßt einen analogen Schaltungsteil 3b, einen Komparator 5b, einen Zähler 7b, eine Steuereinrichtung 9b, ferner eine Zeitsteuerschaltung 57 und eine Abtast-Halteschaltung 59. Das wesentliche Prinzip des analogen Schaltungsteils 3b, des Komparators 5b, des Zählers 7b und der Steuereinrichtung 9b geht im wesentlichen aus der Beschreibung der vorhergehenden Ausführungsbeispiele hervor; Abweichungen dazu sind nachstehend beschrieben. Die bereits in den vorhergehenden Ausführungsbeispielen beschriebenen Komponenten, die mit gleicher oder ähnlicher Funktion auch in der Schaltungsanordnung 1b zur digitalen Erfassung der Amplitude eines Signals verwendet werden, sind mit einem b hinter der entsprechenden Bezugsziffer gekennzeichnet.