CN218768139U - 一种基于vpx的嵌入式计算装置 - Google Patents

一种基于vpx的嵌入式计算装置 Download PDFInfo

- Publication number

- CN218768139U CN218768139U CN202222656973.3U CN202222656973U CN218768139U CN 218768139 U CN218768139 U CN 218768139U CN 202222656973 U CN202222656973 U CN 202222656973U CN 218768139 U CN218768139 U CN 218768139U

- Authority

- CN

- China

- Prior art keywords

- vpx

- computing device

- embedded computing

- module

- resistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Power Sources (AREA)

Abstract

本实用新型涉及一种基于VPX的嵌入式计算装置,包括:通过电气连接的处理器、MCU、显示模块、网络模块、电口模块、存储模块、前面板、背板、VPX连接器、显示模块,所述前面板和VPX连接器均设有多个输出接口。通过在VPX连接器上提供了一路PCIE3.0x8数据通道和4路10G光口、4路千兆电口及其它标准接口,实现系统间海量数据交互;通过采用硬件加速协助主处理器工作的方法,分担部分CPU开销,提升处理器的有效计算能力;通过设置集中式硬件平台,采用VPX架构这种分布式计算系统,实现数据通道选择延时低,能进行数据高带宽传输,计算算力强。

Description

技术领域

本实用新型涉及嵌入式计算技术领域,更具体地说,涉及一种基于VPX的嵌入式计算装置。

背景技术

嵌入式计算装置一般是指针对某个特定的应用,如针对网络、针对通信、针对音频、针对视频,针对工业控制等。嵌入式系统是以应用为中心,以计算机技术为基础,并且软硬件可裁剪,适用于应用系统对功能、可靠性、成本、体积、功耗有严格要求的专用计算机系统,它一般由嵌入式微处理器、外围硬件设备、嵌入式操作系统以及用户的应用程序等四个部分组成。

现有的嵌入式计算装置,通常与VPX无关,数据通道选择延时高,数据传输效果不佳,计算算力一般。

实用新型内容

本实用新型要解决的技术问题在于,针对现有技术的上述的缺陷,提供一种基于VPX的嵌入式计算装置,包括:

通过电气连接的处理器、MCU、显示模块、网络模块、电口模块、存储模块、前面板、背板、VPX连接器、显示模块,所述前面板和VPX连接器均设有多个输出接口。

优选地,所述MCU设有扩展模块,所述扩展模块用于对所述基于VPX的嵌入式计算装置的状态的监测与管理。

优选地,所述装置还设有桥片,所述桥片用于所述装置进行IO扩展。

优选地,所述显示模块包括:

CPU D2000与GPU X100之间通过PCIE连接,GPU X100与控制器LT8711V之间通过低压配电屏DP连接,控制器LT8711V与显示接口之间通过VGA连接。

优选地,所述装置还设有RTC供电电路,所述RTC供电电路包括:

电源B1的正极与电阻R420的正极连接,电阻R420的负极分别与二极管D3的正极、电阻R421的一端连接,电阻R421的另一端与三极管Q14的漏极D连接,三极管Q14的栅极G与分别与电阻R422的一端、电阻R423的一端连接,三极管Q14的源极S与电阻R424的一端连接,二极管D3的负极与电容C345的一端连接。

优选地,所述前面板与桥片之间通过USB接口连接,所述桥片与VPX连接器之间通过USB接口或者SATA接口连接,所述桥片与板贴SSD之间通过SATA接口连接,所述桥片与扩展SSD之间通过SATA接口连接。

优选地,所述前面板设有复位按钮。

优选地,所述复位按钮与与门连接,所述与门还与CPLD、处理器连接,所述CPLD还与桥片连接,所述基于VPX的嵌入式计算装置设有软件系统,所述软件系统设有复位信号,所述CPLD处理来自软件系统的复位信号。

优选地,所述电口模块包括:

桥片FT-X100与网络控制器WX1860A4之间通过PCIE连接,网络控制器WX1860A4与以太网收发器PHY-YT8521SH之间通过GMII连接,以太网收发器PHY-YT8521SH与VPX连接器之间通过4路千兆Serdes网口连接。

优选地,所述网络模块包括:

FT-2000+/64核CPU具备33Lane的PCIE通道,其中分出两组X8信号分别接到两片WX1820AL,每片WX1820AL生成2路10G的网络接口引出到VPX连接器。

实施本实用新型的基于VPX的嵌入式计算装置,具有以下有益效果:通过设置通过电气连接的处理器、MCU、显示模块、网络模块、电口模块、存储模块、前面板、背板、VPX连接器、显示模块,所述前面板和VPX连接器均设有多个输出接口的技术方案,在VPX连接器上提供了一路PCIE3.0x8数据通道和4路10G光口、4路千兆电口及其它标准接口,实现系统间海量数据交互;通过采用硬件加速协助主处理器工作的方法,分担部分CPU开销,提升处理器的有效计算能力;通过设置集中式硬件平台,采用VPX架构这种分布式计算系统,实现数据通道选择延时低,能够进行数据高带宽传输,计算算力强。

附图说明

为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图示出的结构获得其他的附图。下面将结合附图及实施例对本实用新型作进一步说明,附图中:

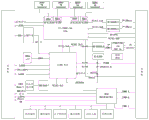

图1是本实用新型基于VPX的嵌入式计算装置的结构示意图;

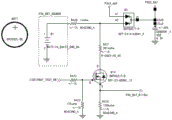

图2是本实用新型基于VPX的嵌入式计算装置中的RTC供电电路原理图;

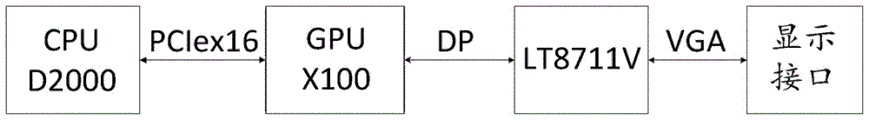

图3是本实用新型基于VPX的嵌入式计算装置中的显示模块结构示意图;

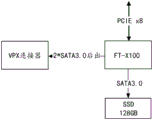

图4是本实用新型基于VPX的嵌入式计算装置中的存储模块结构示意图;

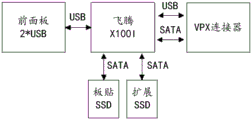

图5是本实用新型基于VPX的嵌入式计算装置中的SATA和USB分配示意图;

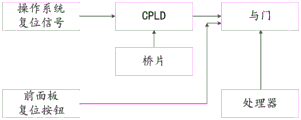

图6是本实用新型基于VPX的嵌入式计算装置中的复位设置结构示意图;

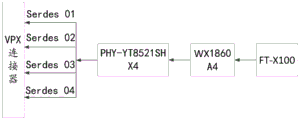

图7是本实用新型基于VPX的嵌入式计算装置中的电口模块结构示意图;

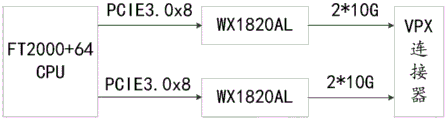

图8是本实用新型基于VPX的嵌入式计算装置中的网络模块结构示意图;

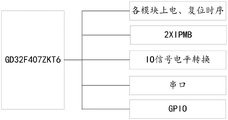

图9是本实用新型基于VPX的嵌入式计算装置中的BMC对外连接示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

需要说明,若本发明实施例中有涉及方向性指示(诸如上、下、左、右、前、后……),则该方向性指示仅用于解释在某一特定姿态(如附图所示)下各部件之间的相对位置关系、运动情况等,如果该特定姿态发生改变时,则该方向性指示也相应地随之改变。

另外,若本发明实施例中有涉及“第一”、“第二”等的描述,则该“第一”、“第二”等的描述仅用于描述目的,而不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。另外,各个实施例之间的技术方案可以相互结合,但是必须是以本领域普通技术人员能够实现为基础,当技术方案的结合出现相互矛盾或无法实现时应当认为这种技术方案的结合不存在,也不在本发明要求的保护范围之内。

请参阅图1,图1是本实用新型基于VPX的嵌入式计算装置的结构示意图。如图1所示,一种基于VPX的嵌入式计算装置,至少包括:通过电气连接的处理器、MCU、显示模块、网络模块、电口模块、存储模块、前面板、背板、VPX连接器、显示模块,前面板和VPX连接器均设有多个输出接口。装置还设有桥片,桥片用于装置进行IO扩展。MCU设有扩展模块,扩展模块用于对基于VPX的嵌入式计算装置的状态的监测与管理。

本实施例中,处理器CPU优选为FT-2000+/64核CPU,当然也可以选择其他型号的能否符合要求的CPU。FT-2000+/64核CPU,用于业务数据的运算和处理,通过前面板输出接口和VPX连接器为外部提供丰富的输入输出接口,接口有SATA3.0、USB2.0、VGA、串口、并口、千兆RJ45网口、管理网口,提供强大的IO扩展功能;使用兆易创新GD32F407ZKT6 MUC模块扩展的管理通道实现对系统的状态监测与管理,管理内容包括开关机控制,电源异常监控,温度监控与风扇控制等;控制通道由2路千兆以太网组成,实现系统间命令交互;在VPX接口提供了一路PCIE3.0 x8数据通道和4路10G光口、4路千兆电口及其它标准接口,实现系统间海量数据无阻塞交互。FT-2000+处理器芯片集成64个自主开发的ARMv8指令集兼容处理器内核FTC662,采用片上并行系统体系结构。通过集成高效处理器核心、基于数据亲和的大规模一致性存储架构、层次式二维Mesh互连网络,优化存储访问延时,提供业界领先的计算性能、访存带宽和IO扩展能力。FT-2000+主要应用于高性能、高吞吐率服务器领域,如对处理能力和吞吐能力要求很高的行业大型业务主机、高性能服务器系统和大型互联网数据中心等。

FT-2000+/64核CPU为本实用新型基于VPX的嵌入式计算装置的核心部件,提供业务计算功能,主频选择2.2GHz,单精度浮点处理能力≥460.8GFLOPS或双精度浮点处理能力≥230.4GFLOPS;CPU通过4个通道连接板载DDR4 32GB内存,内存颗粒可以使用DDR4CXDQ3A8AM-CG。CPU的PCIE资源共33通道,分配如下:

1)一路PCIE 3.0x8用于扩展PCIE总线,直接通过VPX连接器引出;

2)两路PCIE 3.0x8用于板内通过WX1820AL生成4个10G信号,通过VPX引出;

3)一路PCIE3.0 x8连接桥片飞腾X100桥片用于外部接口扩展;

4)一路PCIE3.0 x1连接GP101显卡,输出VGA信号到前面板。

飞腾X100系列是飞腾处理器的配套芯片,可配合飞腾系列处理器,构成台式机、一体机或笔记本的完整解决方案;也可作为显示芯片构建独立显卡,用于各类终端及服务器类应用场景。

飞腾X100桥片为本实用新型的关键IO扩展部件,提供强大的IO资源,上游接飞腾FT-2000+/64核的PCIE 3.0x8,下游主要实现功能包括:

1)飞腾X100桥片下游PCIE x4接1颗国产网讯WX1860 AL4芯片可出4路RGMII信号,再分别接国产裕太微PHY芯片YT8521,生成4路千兆SERDES从VPX连接器引出,其中2路千兆SERDES连接到网络模块,2路千兆SERDES可通过后IO板输出;

2)飞腾X100桥片下游出4路USB2.0,其中2路用于前面板USB调试使用,2路用于背板从VPX连接器引出,USB2.0接口对外提供标准的USB;

飞腾X100桥片下游出4路SATA3.0,其中1路用于板内板贴和扩展SSD,2路用于背板从VPX连接器引出,SATA3.0接口可用于系统盘或其它SATA设备;

3)飞腾X100桥片下游出1路RGMII信号连接到WX1860,产生一路千兆MDI信号输出到前面板作为调试网口。

前面板除了设有复位按钮,还设有多种接口如指示灯、HJ30J连接器、千兆调试网口、USB插座-A型插座、标准VGA连接器等,用于调试、控制和人机交互。前面板可以设有8个LED指示灯,第一个为电源指示灯、第二个为BMC状态指示灯、第三个为系统运行状态指示灯、其余指示灯软件可控,通过指示灯,可以快速定位问题。

背板指的机箱的后面,背板上设有插板的接口,如声卡,网卡,接口都在背板上。

图2是本实用新型基于VPX的嵌入式计算装置中的RTC供电电路原理图。如图2所示,装置还设有RTC供电电路,RTC供电电路包括:电源B1的正极与电阻R420的正极连接,电阻R420的负极分别与二极管D3的正极、电阻R421的一端连接,电阻R421的另一端与三极管Q14的漏极D连接,三极管Q14的栅极G与分别与电阻R422的一端、电阻R423的一端连接,三极管Q14的源极S与电阻R424的一端连接,二极管D3的负极与电容C345的一端连接。

RTC供电电路,实现BIOS掉电恢复功能以及计时功能。选取20ppm精度的晶振,晶振的负载匹配电容选取C0G温度等级,保证RTC电路的精确性。根据晶振的精度,可以达到每天偏差小于1.7S的精度。支持秒以上及秒以下时间获取,秒以下时间获取由交换后插板将秒脉冲差分信号转换为GPIO_1信号,通过背板连接获取GPIO_1信号,通过中断触发的方式,当秒脉冲出现上升沿时,触发校时中断,进入该中断处理函数,在该中断处理函数中,对高精度定时器进行清零操作。

图3是本实用新型基于VPX的嵌入式计算装置中的显示模块结构示意图。如图3所示,显示模块包括:CPU D2000与GPU X100之间通过PCIE连接,GPU X100与控制器LT8711V之间通过低压配电屏DP连接,控制器LT8711V与显示接口之间通过VGA连接。本实用新型基于VPX的嵌入式计算装置采用飞腾X100和LT8711X的方式,GPU为本装置提供3D显示加速功能,且具有较低的功耗,满足一般的显示加速功能需求;视频解码功能,为播放视频提供硬件解码功能,提升解码效率并降低系统功耗。

图4是本实用新型基于VPX的嵌入式计算装置中的存储模块结构示意图。如图4所示,载固态存储器SSD接口为桥片X100提供的SATA3.0接口,可以采用HTUSMU128G-WM,128GB存储容量,板贴,工作温度:-40℃~+85℃。FLASH类型可以是MLC NAND FLASH。除板贴SSD以外,还可以预留SATA3.0接口2个或者根据需要预留接口超过2个,用于随时扩展SSD容量。

图5是本实用新型基于VPX的嵌入式计算装置中的SATA和USB分配示意图。如图5所示,前面板与桥片之间通过USB接口连接,桥片与VPX连接器之间通过USB接口或者SATA接口连接,桥片与板贴SSD之间通过SATA接口连接,桥片与扩展SSD之间通过SATA接口连接。

图6是本实用新型基于VPX的嵌入式计算装置中的复位设置结构示意图。如图6所示,前面板设有复位按钮。复位按钮与与门连接,与门还与CPLD、处理器连接,CPLD还与桥片连接,基于VPX的嵌入式计算装置设有软件系统,软件系统设有复位信号,CPLD处理来自软件系统的复位信号。背板上通过4.7K欧姆电阻上拉至3.3V_AUX,通过背板接到机箱复位按钮。在BIOS setup界面下,可以设置软件系统复位信号起作用或不起作用。

图7是本实用新型基于VPX的嵌入式计算装置中的电口模块结构示意图。如图7所示,电口模块包括:桥片FT-X100与网络控制器WX1860A4之间通过PCIE连接,网络控制器WX1860A4与以太网收发器PHY-YT8521SH之间通过GMII连接,以太网收发器PHY-YT8521SH与VPX连接器之间通过4路千兆Serdes网口连接。

图8是本实用新型基于VPX的嵌入式计算装置中的网络模块结构示意图。如图8所示,网络模块包括:FT-2000+/64核CPU具备33Lane的PCIE通道,其中分出两组X8信号分别接到两片WX1820AL,每片WX1820AL生成2路10G的网络接口引出到VPX连接器。WX1820AL的0.9V和1.8V电源不需要保持一定上电时序,但是为了保证PHY的抖动性能,VP_PE\VP_ETH模拟电源在0.9V输入端串入磁珠,VPH\VDDA18模拟电源需要在1.8V输入端串入磁珠,磁珠型号使用BLM21PG300SN1。电源滤波电容采用10nF\100nF\4.7uF\10uF\47uF组合使用。

图9是本实用新型基于VPX的嵌入式计算装置中的BMC对外连接示意图。如图9所示,BMC芯片GD32F407ZKT6通过串口与CPU相连接,实现与CPU的交互。CPU的状态信息传送给BMC芯片,包括输出电流、电压、主芯片温度、操作系统及版本、固件版本等信息。BMC也将所采集的健康信息传送给CPU。BMC引至VPX插座的信号对外输出2路IPMB(I2C)接口并做隔离处理,通信速率支持100Kbps/400Kbps可配置,支持IPMI2.0标准协议,可通过IPMI命令控制开关电以及上报各个模块如处理器、MCU、显示模块、网络模块、电口模块、存储模块、前面板、背板、VPX连接器、显示模块在位信息。其中槽位号识别PIN、机箱号和机柜号识别PIN接收编码识别(GA0~GA4,GAP)信号和机箱、机柜编码识别(RACK-ID-0~5)信号,实现处理器、MCU、显示模块、网络模块、电口模块、存储模块、前面板、背板、VPX连接器、显示模块状态上报。

BMC具有JTAG外接接口连接到VPX,可以作为被动设备或者主动设备进行通讯调试,作为主动设备时,可以扫描测试作为被动设备的其他板卡上的芯片和其外围电路的工作状态是否正常,并分析其连接状态。

BMC具有开机自检、运行状态自检功能,并将检测到的故障上报;能够检测电路板上的温度、电流、电压等传感器,并将相关检测值上报,通过数据代理,BMC可以得到操作系统及版本等信息,并将相关信息上报。

本实用新型通过以上实施例的设计,其有益效果是:通过设置通过电气连接的处理器、MCU、显示模块、网络模块、电口模块、存储模块、前面板、背板、VPX连接器、显示模块,所述前面板和VPX连接器均设有多个输出接口的技术方案,在VPX连接器上提供了一路PCIE3.0 x8数据通道和4路10G光口、4路千兆电口及其它标准接口,实现系统间海量数据交互;通过采用硬件加速协助主处理器工作的方法,分担部分CPU开销,提升处理器的有效计算能力;通过设置集中式硬件平台,采用VPX架构这种分布式计算系统,实现数据通道选择延时低,能够进行数据高带宽传输,计算算力强。

本实用新型是根据特定实施例进行描述的,但本领域的技术人员应明白在不脱离本实用新型范围时,可进行各种变化和等同替换。此外,为适应本实用新型技术的特定场合,可对本实用新型进行诸多修改而不脱离其保护范围。因此,本实用新型并不限于在此公开的特定实施例,而包括所有落入到权利要求保护范围的实施例。

Claims (10)

1.一种基于VPX的嵌入式计算装置,其特征在于,包括:

通过电气连接的处理器、MCU、显示模块、网络模块、电口模块、存储模块、前面板、背板、VPX连接器、显示模块,所述前面板和VPX连接器均设有多个输出接口。

2.根据权利要求1所述的基于VPX的嵌入式计算装置,其特征在于,所述MCU设有扩展模块,所述扩展模块用于对所述基于VPX的嵌入式计算装置的状态的监测与管理。

3.根据权利要求1所述的基于VPX的嵌入式计算装置,其特征在于,所述装置还设有桥片,所述桥片用于所述装置进行IO扩展。

4.根据权利要求1所述的基于VPX的嵌入式计算装置,其特征在于,所述显示模块包括:

CPU D2000与GPU X100之间通过PCIE连接,GPU X100与控制器LT8711V之间通过低压配电屏DP连接,控制器LT8711V与显示接口之间通过VGA连接。

5.根据权利要求1所述的基于VPX的嵌入式计算装置,其特征在于,所述装置还设有RTC供电电路,所述RTC供电电路包括:

电源B1的正极与电阻R420的正极连接,电阻R420的负极分别与二极管D3的正极、电阻R421的一端连接,电阻R421的另一端与三极管Q14的漏极D连接,三极管Q14的栅极G与分别与电阻R422的一端、电阻R423的一端连接,三极管Q14的源极S与电阻R424的一端连接,二极管D3的负极与电容C345的一端连接。

6.根据权利要求3所述的基于VPX的嵌入式计算装置,其特征在于,所述前面板与桥片之间通过USB接口连接,所述桥片与VPX连接器之间通过USB接口或者SATA接口连接,所述桥片与板贴SSD之间通过SATA接口连接,所述桥片与扩展SSD之间通过SATA接口连接。

7.根据权利要求6所述的基于VPX的嵌入式计算装置,其特征在于,所述前面板设有复位按钮。

8.根据权利要求7所述的基于VPX的嵌入式计算装置,其特征在于,所述复位按钮与与门连接,所述与门还与CPLD、处理器连接,所述CPLD还与桥片连接,所述基于VPX的嵌入式计算装置设有软件系统,所述软件系统设有复位信号,所述CPLD处理来自软件系统的复位信号。

9.根据权利要求1至8任意一项所述的基于VPX的嵌入式计算装置,其特征在于,所述电口模块包括:

桥片FT-X100与网络控制器WX1860A4之间通过PCIE连接,网络控制器WX1860A4与以太网收发器PHY-YT8521 SH之间通过GMII连接,以太网收发器PHY-YT8521 SH与VPX连接器之间通过4路千兆Serdes网口连接。

10.根据权利要求9所述的基于VPX的嵌入式计算装置,其特征在于,所述网络模块包括:

FT-2000+/64核CPU具备33Lane的PCIE通道,其中分出两组X8信号分别接到两片WX1820AL,每片WX1820AL生成2路10G的网络接口引出到VPX连接器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202222656973.3U CN218768139U (zh) | 2022-10-08 | 2022-10-08 | 一种基于vpx的嵌入式计算装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202222656973.3U CN218768139U (zh) | 2022-10-08 | 2022-10-08 | 一种基于vpx的嵌入式计算装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN218768139U true CN218768139U (zh) | 2023-03-28 |

Family

ID=85698195

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202222656973.3U Active CN218768139U (zh) | 2022-10-08 | 2022-10-08 | 一种基于vpx的嵌入式计算装置 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN218768139U (zh) |

-

2022

- 2022-10-08 CN CN202222656973.3U patent/CN218768139U/zh active Active

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN211427190U (zh) | 一种基于飞腾处理器2000+的服务器电路和主板 | |

| US20120047302A1 (en) | Storage system | |

| US10579572B2 (en) | Apparatus and method to provide a multi-segment I2C bus exerciser/analyzer/fault injector and debug port system | |

| CN207232852U (zh) | 一种基于Purley平台的8路服务器计算板 | |

| CN112000501A (zh) | 一种多节点分区服务器访问i2c设备的管理系统 | |

| CN213365380U (zh) | 一种服务器主板及服务器 | |

| CN109033009B (zh) | 一种支持通用和机柜型服务器的电路板及系统 | |

| CN110362511B (zh) | 一种pcie设备 | |

| CN115757236A (zh) | 一种存储扩展池化设备及系统 | |

| CN211427338U (zh) | 基于申威处理器的服务器主板 | |

| CN213276459U (zh) | 一种服务器主板及服务器 | |

| CN218768139U (zh) | 一种基于vpx的嵌入式计算装置 | |

| CN116501678A (zh) | 一种拓扑板卡和板载系统 | |

| CN104484305B (zh) | 一种服务器调试分析接口装置 | |

| CN216352292U (zh) | 服务器主板及服务器 | |

| WO2023016379A1 (zh) | 计算机系统、基于PCIe设备的控制方法及相关设备 | |

| CN111273742A (zh) | 一种基于正交构架的高密度服务模块化系统 | |

| CN211375594U (zh) | 一种基于sw421处理器的接口扩展机构 | |

| CN113434445B (zh) | 一种i3c访问dimm的管理系统和服务器 | |

| CN214311726U (zh) | 一种用于原型验证的适配板 | |

| US20210182110A1 (en) | System, board card and electronic device for data accelerated processing | |

| CN113268445A (zh) | 一种基于vpx架构的国产双控混合存储控制模块实现方法 | |

| CN112000613A (zh) | 一种多单元服务器管理单元及多单元服务器 | |

| CN209132718U (zh) | 一种标准pcie子卡及ocp子卡的供电治具 | |

| CN219916339U (zh) | 基于vpx架构的100ge通用处理模块 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| GR01 | Patent grant | ||

| GR01 | Patent grant |