CN211427190U - 一种基于飞腾处理器2000+的服务器电路和主板 - Google Patents

一种基于飞腾处理器2000+的服务器电路和主板 Download PDFInfo

- Publication number

- CN211427190U CN211427190U CN201921716732.5U CN201921716732U CN211427190U CN 211427190 U CN211427190 U CN 211427190U CN 201921716732 U CN201921716732 U CN 201921716732U CN 211427190 U CN211427190 U CN 211427190U

- Authority

- CN

- China

- Prior art keywords

- bmc

- signal

- rtc

- cpu

- sys

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000006243 chemical reaction Methods 0.000 claims abstract description 28

- 230000008054 signal transmission Effects 0.000 claims abstract description 4

- 230000001133 acceleration Effects 0.000 abstract 1

- 238000010586 diagram Methods 0.000 description 8

- 238000004891 communication Methods 0.000 description 4

- 238000001514 detection method Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 238000000034 method Methods 0.000 description 4

- 230000001360 synchronised effect Effects 0.000 description 4

- 101100498818 Arabidopsis thaliana DDR4 gene Proteins 0.000 description 2

- 238000005034 decoration Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 239000000969 carrier Substances 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

Images

Abstract

本实用新型实施例公开了一种基于飞腾处理器2000+服务器电路和主板,包括第一控制模块、第二控制模块、切换模块、SYS_RTC和BMC_RTC;第一控制模块用于读取SYS_RTC的系统硬件时间,第二控制模块用于读取SYS_RTC的系统硬件时间,第二控制模块还用于将系统硬件时间写入BMC_RTC,切换模块用于第一控制模块通路和第二控制模块通路的切换,切换模块还用于电路信号传输中的电平转换。当电路插入电源和电源线时,BMC从SYS_RTC读到系统硬件时间并作为BMS硬件时间,当按下开机键,电路开机后,CPU读取SYS_RTC系统硬件时间,以此实现系统硬件时间和BMC硬件时间的同步。本实用新型实施例还解决了PCIE资源无法支持较多数量的RAID卡、HCA卡、HBA卡、FPGA加速卡等外部设备的问题。

Description

技术领域

本实用新型涉及服务器主板技术领域,具体涉及一种基于飞腾处理器2000+的服务器电路和主板。

背景技术

随着中美竞争的日趋激烈,为了减小甚至摆脱国内对Intel、AMD等美国公司处理器的依赖,现在国家越来越重视国产CPU的发展,而飞腾作为国产处理器的一员,其最新的处理器已达到业界领先水平,广泛应用于存储、互联网等各个行业。目前飞腾推出的基于ARM64平台的飞腾2000+64核处理器(FT2000+CPU)已经可以支持8通道DDR4内存,集成两组PCIE X16和一组PCIE X1资源,CPU运算性能也大大提高,同时飞腾也发布了基于此处理器的FT2000+CPU公版服务器主板。

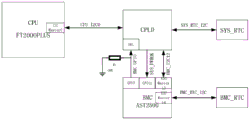

如图1所示,为FT2000+CPU公版的服务器主板设计方案,主要包括FT2000+CPU、DDR4内存、PEX8632PCIE2.0switch、BMC AST2300、CPLD和USB及网口等一些外部接口。

FT2000+CPU和BMC分别有独立的时钟,它们之间无法进行时间的校准和统一,会产生系统硬件时间和BMC硬件时间不同步的问题;FT2000+CPU公版的服务器主板PCIE X8、PCIE X16和PCIE X1资源有限,无法支持较多数量的RAID卡、HCA卡、HBA卡、FPGA加速卡等外部设备。

实用新型内容

本实用新型实施例中提供了一种基于飞腾处理器2000+的服务器电路和主板,以解决现有技术中系统硬件时间和BMC硬件时间不同步的问题,和PCIE资源无法支持较多数量的RAID卡、HCA卡、HBA卡、FPGA加速卡等外部设备的问题。

本实用新型实施例公开了如下技术方案:

本实用新型第一方面提供了一种基于飞腾处理器2000+服务器电路,包括第一控制模块、第二控制模块、切换模块、SYS_RTC和BMC_RTC,所述第一控制模块连接所述切换模块,所述第二控制模块连接所述切换模块,所述切换模块连接所述SYS_RTC和BMC_RTC;

所述第一控制模块用于读取所述SYS_RTC的系统硬件时间,所述第二控制模块用于读取所述SYS_RTC的系统硬件时间,所述第二控制模块还用于将所述系统硬件时间写入所述BMC_RTC,所述切换模块用于所述第一控制模块通路和第二控制模块通路的切换,所述切换模块还用于所述电路信号传输中的电平转换。

进一步地,所述第一控制模块包括CPU,所述CPU的CPU_I2C0信号连接所述切换模块,所述第二控制模块包括BMC,所述BMC的BMC_I2C12信号、BMC_GPIO信号和SYS_PWROK信号连接所述切换模块,所述BMC的BMC_GPIO信号通过电阻R1接地,所述BMC的BMC_RTC_I2C12信号连接所述BMC_RTC。

进一步地,所述切换模块包括CPLD,所述CPLD的输入端连接CPU_I2C0信号、BMC_I2C12信号、BMC_GPIO信号和SYS_PWROK信号,所述CPLD的输出端通过SYS_RTC_I2C信号连接所述SYS_RTC。

进一步地,所述切换模块包括第一电压转换芯片、第二电压转换芯片和I2C切换芯片,所述第一电压转换芯片的输入端连接CPU_I2C0信号,所述第一电压转换芯片的输出端连接CPU_I2C0_3.3V信号,所述第二电压转换芯片的输入端连接BMC_I2C12信号和BMC_GPIO信号,所述第二电压转换芯片的输出端连接BMC_I2C12_3.3V信号,所述I2C切换芯片的输入端连接CPU_I2C0_3.3V信号和BMC_I2C12_3.3V信号,所述I2C切换芯片的输出端通过SYS_RTC_I2C信号连接所述SYS_RTC。

进一步地,所述电路还包括PCIE扩展模块,所述PCIE扩展模块包括第一扩展芯片和第二扩展芯片,所述第一扩展芯片连接所述CPU,所述第二扩展芯片连接所述CPU。

进一步地,所述第一扩展芯片的输入端连接所述CPU PCIE0控制器的lane0-lane7,所述第一扩展芯片的输出端连接PCIE X8 SLOT连接器和/或Slimline连接器,所述PCIE X8 SLOT连接器外插RAID卡、HCA卡或HBA卡,所述Slimline连接器连接NVME硬盘。

进一步地,所述PCIE X8 SLOT连接器的数量为1~5个,所述Slimline连接器的数量为1~2个。

进一步地,所述第二扩展芯片的输入端连接所述CPU PCIE0控制器的lane8-lane15,所述第二扩展芯片的输出端通过PCIE2.0X8总线连接万兆网卡,所述第二扩展芯片的输出端通过PCIE2.0X4总线连接千兆网卡,所述第二扩展芯片的输出端通过PCIE2.0X1总线连接USB控制器或所述BMC,所述第二扩展芯片的输出端通过PCIE2.0X2总线连接RAID控制器。

本实用新型第二方面提供了一种基于飞腾处理器2000+的服务器主板,所述主板根据所述电路实现。

实用新型内容中提供的效果仅仅是实施例的效果,而不是实用新型所有的全部效果,上述技术方案中的一个技术方案具有如下优点或有益效果:

1)本实用新型电路的切换模块用于第一控制模块通路和第二控制模块通路的切换,当电路插入电源和电源线时,BMC从SYS_RTC读到系统硬件时间并作为BMS硬件时间,当按下开机键,电路开机后,CPU读取SYS_RTC系统硬件时间,以此实现系统硬件时间和BMC硬件时间的同步。

2)本实用新型电路通过第一扩展芯片的扩展,使电路最多支持6个板载PCIE槽位,并且支持RAID卡、HCA卡、HBA卡、NVME硬盘接口等功能,电路通过第二扩展芯片的扩展,使电路支持千兆网卡、万兆网卡、USB、SATA等功能,极大扩展了飞腾2000+CPU的PCIE资源,丰富电路的应用。

3)根据本实用新型电路实现的服务器主板,集成了本实用新型电路的所有优点,能够满足市场对服务器接口的多样化需求。

附图说明

为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1为本实用新型所述电路结构框图;

图2为本实用新型所述FT2000+CPU公版的服务器主板电路结构框图;

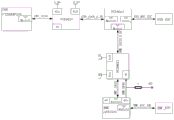

图3为本实用新型实施例所述电路的一种结构框图;

图4为本实用新型实施例所述电路的另一种结构框图;

图5为本实用新型实施例所述PCIE扩展模块的电路结构框图;

图6为本实用新型实施例所述服务器主板的结构框图。

具体实施方式

为了能清楚说明本方案的技术特点,下面通过具体实施方式,并结合其附图,对本实用新型进行详细阐述。下文的公开提供了许多不同的实施例或例子用来实现本实用新型的不同结构。为了简化本实用新型的公开,下文中对特定例子的部件和设置进行描述。此外,本实用新型可以在不同例子中重复参考数字和/或字母。这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施例和/或设置之间的关系。应当注意,在附图中所图示的部件不一定按比例绘制。本实用新型省略了对公知组件和处理技术及工艺的描述以避免不必要地限制本实用新型。

如图1所示,本实用新型实施例提供的服务器电路,基于飞腾2000+CPU公版电路实现,电路包括第一控制模块、第二控制模块、切换模块、SYS_RTC和BMC_RTC(RTC,Real-TimeClock,实时时钟,本实施例中RTC型号为DS3232),第一控制模块连接切换模块,第二控制模块连接切换模块,切换模块连接SYS_RTC和BMC_RTC。

第一控制模块用于读取SYS_RTC的系统硬件时间,第二控制模块用于读取SYS_RTC的系统硬件时间,第二控制模块还用于将系统硬件时间写入BMC_RTC,切换模块用于第一控制模块通路和第二控制模块通路的切换,切换模块还用于电路信号传输中的电平转换。

第一控制模块包括CPU(CPU,Central Processing Unit,中央处理器,本实施例中CPU型号为FT2000+),CPU的CPU_I2C0信号连接切换模块,第二控制模块包括BMC(BMC,Baseboard Management Controller,基板管理控制器),BMC的BMC_I2C12信号(I2C,Inter-Integrated Circuit,一种两线通讯总线)、BMC_GPIO信号(GPIO,General-purpose input/output,通用输入输出接口)和SYS_PWROK信号连接切换模块,BMC的BMC_GPIO信号通过电阻R1接地,BMC的BMC_RTC_I2C12信号连接BMC_RTC。

如图3所示,为电路的一种结构框图,这种连接方式下,切换模块包括CPLD(CPLD,Complex Programmable Logic Device,复杂可编程逻辑器件),CPLD的输入端连接CPU_I2C0信号、BMC_I2C12信号、BMC_GPIO信号和SYS_PWROK信号,CPLD的输出端通过SYS_RTC_I2C信号连接SYS_RTC。

CPU_I2C0信号的输出电平是1.8V,而SYS_RTC_I2C信号的接口电平是3.3V,所以CPU和SYS_RTC通信需要CPLD进行电平转换。本实用新型实施例所采用的CPLD型号是LCMXO2-2000HC-4FTG256I,它的IO可以分为5个Bank,每个Bank有一个VCCIO输入电压pin,本电路中设置Bank3为1.8V Bank(即Bank3的VCCIO接到1.8V电压上),CPU出来的CPU_I2C0信号接到1.8V Bank上;其他Bank设为3.3V Bank(即其他Bank的VCCIO接到3.3V电压上),SYS_RTC_I2C信号接到3.3V Bank上,如此可以实现1.8V到3.3V之间的电平转换。

正常情况下,由CPU去读取SYS_RTC的系统硬件时间,此时CPLD只要将输出的SYS_RTC_I2C信号切换到CPU通路,即可实现CPU的I2C Master0端口和SYS_RTC的通信;当BMC获取系统硬件时间时,CPLD将SYS_RTC_I2C信号切换到BMC通路,即可实现BMC的I2C Master12端口和SYS_RTC的通信。

本实用新型实施例将BMC的一个GPIO端口作为选择pin接到CPLD,并且加一个下拉电阻R1到GND,用于区分CPLD切换到CPU通路或BMC通路的判断信号。

默认BMC_GPIO信号为低,此时CPLD将SYS_RTC_I2C信号切换到CPU通路。

当BMC要读取SYS_RTC的系统硬件时间时,BMC将BMC_GPIO信号拉高,这时CPLD检测到BMC_GPIO信号为高电平,CPLD将SYS_RTC_I2C信号切换到BMC通路,此时BMC就可以获取系统硬件时间,此方式保证了BMC根据系统硬件时间校准BMC硬件时间。

BMC通过I2C Master14端口挂载一个BMC_RTC,当BMC获取到系统硬件时间后,将系统硬件时间写入到BMC_RTC中,由此BMC硬件时间和系统硬件时间同步。

本实用新型实施例将BMC的GPIO 0端口作为SYS_PWROK信号的检测端口,当BMCGPIO 0端口检测到CPLD发出的SYS_PWROK信号后,BMC将BMC_GPIO信号设为低电平,BMC无法读取系统硬件时间,此方式保证系统开机运行时不受BMC的I2C Master12端口读取SYS_RTC的影响。

如图3所示,CPU系统硬件时间和BMC硬件时间同步的具体过程为:

S11,当电路插入电源和电源线时,BMC检测到CPLD发出的SYS_PWROK信号为低电平,此时BMC将发送给CPLD的BMC_GPIO信号拉高;

S12,CPLD收到的BMC_GPIO信号为高电平后,CPLD将SYS_RTC_I2C信号切换到BMC通路,BMC通过I2C Master12端口获取SYS_RTC的系统硬件时间;

S13,BMC将获取到的系统硬件时间通过I2C Master14端口写入到BMC_RTC中,此时BMC硬件时间和系统硬件时间同步;

S14,当按下开机键,电路开机后,BMC检测到CPLD发出的SYS_PWROK信号变为高电平,BMC将BMC_GPIO信号释放,BMC_GPIO信号变为低电平;

S15,CPLD检测到BMC_GPIO信号为低电平后,CPLD将SYS_RTC_I2C信号切换到CPU通路,CPU通过I2C Master0端口读取SYS_RTC的系统硬件时间。

通过上述步骤S11~S15,本实用新型电路的CPU系统硬件时间和BMC硬件时间实现同步。

如图4所示,为电路的另一种结构框图,这种连接方式下,切换模块包括第一电压转换芯片(PCA9617)、第二电压转换芯片(PCA9617)和I2C切换芯片(PCA9541),第一电压转换芯片的输入端连接CPU_I2C0信号,第一电压转换芯片的输出端连接CPU_I2C0_3.3V信号,第二电压转换芯片的输入端连接BMC_I2C12信号和BMC_GPIO信号,第二电压转换芯片的输出端连接BMC_I2C12_3.3V信号,I2C切换芯片的输入端连接CPU_I2C0_3.3V信号和BMC_I2C12_3.3V信号,I2C切换芯片的输出端通过SYS_RTC_I2C信号连接SYS_RTC。

BMC内部有ADC电压检测端口可以检测电路的开机状态,并且BMC_GPIO信号连接第二电压转换芯片的EN pin上。

如图4所示,CPU系统硬件时间和BMC硬件时间同步的具体过程为:

S21,当电路插入电源和电源线时,ADC电压检测端口检测到系统12V电压为0,系统未开机,BMC将BMC_GPIO信号拉高,第二电压转换芯片输出BMC_I2C12_3.3V信号;

S22,BMC的I2C Master12端口通过I2C切换芯片的I2C Master1端口读取系统硬件时间,由于在不开机状态下,CPU不工作,所以CPU无法通过I2C Master0端口读取系统硬件时间;

S23,BMC将获取到的系统硬件时间通过I2C Master14端口写入到BMC_RTC中,此时BMC硬件时间和系统硬件时间同步;

S24,当按下开机键,电路开机后,第一电压转换芯片输出CPU_I2C0_3.3V信号,ADC电压检测端口检测到系统12V电压为12V,BMC将BMC_GPIO信号释放,BMC_GPIO信号变为低电平,此时第二电压转换芯片不输出信号,BMC不能读取系统硬件时间;

S25,CPU的I2C Master0端口通过I2C切换芯片的I2C Master0端口读取SYS_RTC的系统硬件时间。

通过上述步骤S21~S25,本实用新型电路的CPU系统硬件时间和BMC硬件时间实现同步。

图3、图4中,切换模块和其他模块的连接方式电路都可以实现系统硬件时间和BMS硬件时间的同步,图3中的切换模块和图4中的切换模块可以择一使用。

如图5所示,为电路的PCIE扩展模块(PCIE,Peripheral Component InterconnectExpress,外围器件互连接口)结构框图,PCIE扩展模块包括第一扩展芯片和第二扩展芯片,第一扩展芯片连接CPU,第二扩展芯片连接CPU。

第一扩展芯片(PEX8764)的输入端连接CPU PCIE0控制器的lane0-lane7,第一扩展芯片的输出端连接PCIE X8SLOT连接器和/或Slimline连接器,PCIEX8SLOT连接器的数量为1~5个,Slimline连接器的数量为1~2个。

第一扩展芯片和CPU PCIE0控制器下lane0-lane7的连接方式,支持PCIE3.0的扩展,第一扩展芯片共有64条lane。PCIE X8SLOT连接器外插RAID卡(RAID,Redundant Arraysof Independent Disks,磁盘阵列)、HCA卡(HCA,Host Channel Adapter,主机通道适配器)或HBA卡(HBA,Host Bus Adapter,主机总线适配器),用以实现系统的存储和网络扩展;Slimline连接器连接NVME硬盘(NVME,Non-Volatile Memory express,非易失性内存主机控制器接口规范),用以提升系统的存储接口速率。

第二扩展芯片(PEX8733)的输入端连接CPU PCIE0控制器的lane8-lane15,此连接方式支持PCIE3.0的扩展,第二扩展芯片共有33条lane。第二扩展芯片的输出端通过PCIE2.0X8总线连接万兆网卡(Intel 82599),第二扩展芯片的输出端通过PCIE2.0X4总线连接千兆网卡(Intel NHI350AM2),第二扩展芯片的输出端通过PCIE2.0X1总线连接USB控制器(USB,Universal Serial Bus,通用串行总线,本实用新型所用芯片型号为TUSB7340B)或BMC,第二扩展芯片的输出端通过PCIE2.0X2总线连接RAID控制器(Marvell 88SE9230)。

BMC通过NCSI(NCSI,Network Controller Sideband Interface,网络控制器边带接口)切换支持sharelink功能,RAID控制器对外提供4个SATA硬盘接口,USB控制器对外提供4个USB接口,BMC通过集成显卡(ISL59833)对外提供VGA接口显示功能。

CPU PCIE1控制器下的lane0-lane15直连一个PCIE X16SLOT,PCIE X16SLOT可以外插GPU卡或FPGA加速卡等高功耗高带宽设备,PCIE X16SLOT也可以通过PCIE Riser转接卡外接RAID卡或网卡,配置灵活,以满足不同客户的需求。

如图6所示,基于本实用新型电路实现的服务器主板,主板包含电路和具体工作原理不再赘述。

以上所述只是本实用新型的优选实施方式,对于本技术领域的普通技术人员来说,在不脱离本实用新型原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也被视为本实用新型的保护范围。

Claims (9)

1.一种基于飞腾处理器2000+的服务器电路,其特征在于,所述电路包括第一控制模块、第二控制模块、切换模块、SYS_RTC和BMC_RTC,所述第一控制模块连接所述切换模块,所述第二控制模块连接所述切换模块,所述切换模块连接所述SYS_RTC和BMC_RTC;

所述第一控制模块用于读取所述SYS_RTC的系统硬件时间,所述第二控制模块用于读取所述SYS_RTC的系统硬件时间,所述第二控制模块还用于将所述系统硬件时间写入所述BMC_RTC,所述切换模块用于所述第一控制模块通路和第二控制模块通路的切换,所述切换模块还用于所述电路信号传输中的电平转换。

2.根据权利要求1所述的一种基于飞腾处理器2000+的服务器电路,其特征在于,所述第一控制模块包括CPU,所述CPU的CPU_I2C0信号连接所述切换模块,所述第二控制模块包括BMC,所述BMC的BMC_I2C12信号、BMC_GPIO信号和SYS_PWROK信号连接所述切换模块,所述BMC的BMC_GPIO信号通过电阻R1接地,所述BMC的BMC_RTC_I2C12信号连接所述BMC_RTC。

3.根据权利要求1所述的一种基于飞腾处理器2000+的服务器电路,其特征在于,所述切换模块包括CPLD,所述CPLD的输入端连接CPU_I2C0信号、BMC_I2C12信号、BMC_GPIO信号和SYS_PWROK信号,所述CPLD的输出端通过SYS_RTC_I2C信号连接所述SYS_RTC。

4.根据权利要求1所述的一种基于飞腾处理器2000+的服务器电路,其特征在于,所述切换模块包括第一电压转换芯片、第二电压转换芯片和I2C切换芯片,所述第一电压转换芯片的输入端连接CPU_I2C0信号,所述第一电压转换芯片的输出端连接CPU_I2C0_3.3V信号,所述第二电压转换芯片的输入端连接BMC_I2C12信号和BMC_GPIO信号,所述第二电压转换芯片的输出端连接BMC_I2C12_3.3V信号,所述I2C切换芯片的输入端连接CPU_I2C0_3.3V信号和BMC_I2C12_3.3V信号,所述I2C切换芯片的输出端通过SYS_RTC_I2C信号连接所述SYS_RTC。

5.根据权利要求2所述的一种基于飞腾处理器2000+的服务器电路,其特征在于,所述电路还包括PCIE扩展模块,所述PCIE扩展模块包括第一扩展芯片和第二扩展芯片,所述第一扩展芯片连接所述CPU,所述第二扩展芯片连接所述CPU。

6.根据权利要求5所述的一种基于飞腾处理器2000+的服务器电路,其特征在于,所述第一扩展芯片的输入端连接所述CPU PCIE0控制器的lane0-lane7,所述第一扩展芯片的输出端连接PCIE X8 SLOT连接器和/或Slimline连接器,所述PCIE X8 SLOT连接器外插RAID卡、HCA卡或HBA卡,所述Slimline连接器连接NVME硬盘。

7.根据权利要求6所述的一种基于飞腾处理器2000+的服务器电路,其特征在于,所述PCIE X8 SLOT连接器的数量为1~5个,所述Slimline连接器的数量为1~2个。

8.根据权利要求5所述的一种基于飞腾处理器2000+的服务器电路,其特征在于,所述第二扩展芯片的输入端连接所述CPU PCIE0控制器的lane8-lane15,所述第二扩展芯片的输出端通过PCIE2.0 X8总线连接万兆网卡,所述第二扩展芯片的输出端通过PCIE2.0 X4总线连接千兆网卡,所述第二扩展芯片的输出端通过PCIE2.0 X1总线连接USB控制器或所述BMC,所述第二扩展芯片的输出端通过PCIE2.0 X2总线连接RAID控制器。

9.一种基于飞腾处理器2000+的服务器主板,其特征在于,所述主板包括权利要求1-8任一项所述的基于飞腾处理器2000+服务器电路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201921716732.5U CN211427190U (zh) | 2019-10-14 | 2019-10-14 | 一种基于飞腾处理器2000+的服务器电路和主板 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201921716732.5U CN211427190U (zh) | 2019-10-14 | 2019-10-14 | 一种基于飞腾处理器2000+的服务器电路和主板 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN211427190U true CN211427190U (zh) | 2020-09-04 |

Family

ID=72251865

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201921716732.5U Active CN211427190U (zh) | 2019-10-14 | 2019-10-14 | 一种基于飞腾处理器2000+的服务器电路和主板 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN211427190U (zh) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112231145A (zh) * | 2020-10-10 | 2021-01-15 | 苏州浪潮智能科技有限公司 | 一种基于cpld控制bmc重启的切换结构及方法 |

| CN113504877A (zh) * | 2021-07-15 | 2021-10-15 | 中国兵器装备集团自动化研究所有限公司 | 一种基于ft6678控制器的nvme硬盘驱动方法 |

| CN113867648A (zh) * | 2021-10-14 | 2021-12-31 | 浪潮商用机器有限公司 | 一种服务器存储子系统及其控制方法 |

| CN113886290A (zh) * | 2021-09-26 | 2022-01-04 | 苏州浪潮智能科技有限公司 | 一种防止外插卡热插拔时导致线路故障的装置及服务器 |

| CN114063726A (zh) * | 2021-10-15 | 2022-02-18 | 深圳市日海飞信信息系统技术有限公司 | 基于飞腾cpu平台的5g基站服务器及性能提升方法 |

| CN114900914A (zh) * | 2022-06-01 | 2022-08-12 | 北京华电众信技术股份有限公司 | 飞腾主板的led灯启动控制系统及其控制方法 |

-

2019

- 2019-10-14 CN CN201921716732.5U patent/CN211427190U/zh active Active

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112231145A (zh) * | 2020-10-10 | 2021-01-15 | 苏州浪潮智能科技有限公司 | 一种基于cpld控制bmc重启的切换结构及方法 |

| CN112231145B (zh) * | 2020-10-10 | 2022-05-31 | 苏州浪潮智能科技有限公司 | 一种基于cpld控制bmc重启的切换结构及方法 |

| CN113504877A (zh) * | 2021-07-15 | 2021-10-15 | 中国兵器装备集团自动化研究所有限公司 | 一种基于ft6678控制器的nvme硬盘驱动方法 |

| CN113886290A (zh) * | 2021-09-26 | 2022-01-04 | 苏州浪潮智能科技有限公司 | 一种防止外插卡热插拔时导致线路故障的装置及服务器 |

| CN113886290B (zh) * | 2021-09-26 | 2023-07-14 | 苏州浪潮智能科技有限公司 | 一种防止外插卡热插拔时导致线路故障的装置及服务器 |

| CN113867648A (zh) * | 2021-10-14 | 2021-12-31 | 浪潮商用机器有限公司 | 一种服务器存储子系统及其控制方法 |

| CN113867648B (zh) * | 2021-10-14 | 2023-12-29 | 浪潮商用机器有限公司 | 一种服务器存储子系统及其控制方法 |

| CN114063726A (zh) * | 2021-10-15 | 2022-02-18 | 深圳市日海飞信信息系统技术有限公司 | 基于飞腾cpu平台的5g基站服务器及性能提升方法 |

| CN114063726B (zh) * | 2021-10-15 | 2023-07-18 | 成都坦达飞信科技有限公司 | 基于飞腾cpu平台的5g基站服务器及性能提升方法 |

| CN114900914A (zh) * | 2022-06-01 | 2022-08-12 | 北京华电众信技术股份有限公司 | 飞腾主板的led灯启动控制系统及其控制方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN211427190U (zh) | 一种基于飞腾处理器2000+的服务器电路和主板 | |

| CN207367115U (zh) | 一种基于飞腾处理器的服务器主板及服务器 | |

| WO2019062218A1 (zh) | 一种实现多NVMe硬盘背板点灯的设计方法 | |

| CN101470584A (zh) | 硬盘扩展装置 | |

| CN107038139A (zh) | 一种基于ft1500a的国产服务器主板的实现方法 | |

| CN109947682B (zh) | 一种服务器主板及服务器 | |

| CN213365380U (zh) | 一种服务器主板及服务器 | |

| CN110908475A (zh) | 一种申威1621cpu无ich2套片服务器主板 | |

| CN110362511B (zh) | 一种pcie设备 | |

| CN211427337U (zh) | 基于申威处理器的计算机主板 | |

| CN205485799U (zh) | 一种可复用sas、sata信号的硬盘背板 | |

| CN211427338U (zh) | 基于申威处理器的服务器主板 | |

| WO2023016379A1 (zh) | 计算机系统、基于PCIe设备的控制方法及相关设备 | |

| CN101853232B (zh) | 扩展适配卡 | |

| CN203133695U (zh) | 一种基于ast2300 控制芯片的bmc卡 | |

| CN213276462U (zh) | 双路服务器主板及双路服务器 | |

| CN213365381U (zh) | 主板 | |

| CN211149439U (zh) | 一种ocp转接板和支持nvme的ocp转接系统 | |

| CN206021131U (zh) | 一种基于兆芯zx‑c处理器的台式计算机 | |

| CN213365379U (zh) | 服务器主板及单路服务器 | |

| CN204189089U (zh) | 一种服务器 | |

| CN213581897U (zh) | 一种新型显示控制计算模块 | |

| CN101387966A (zh) | 具有基本输入输出系统选择功能的电脑设备 | |

| CN203673396U (zh) | 一种采用ops接口的多功能主板 | |

| CN209132718U (zh) | 一种标准pcie子卡及ocp子卡的供电治具 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| GR01 | Patent grant | ||

| GR01 | Patent grant |