CN1757165A - 译码器内的部件块消息传送 - Google Patents

译码器内的部件块消息传送 Download PDFInfo

- Publication number

- CN1757165A CN1757165A CNA038026554A CN03802655A CN1757165A CN 1757165 A CN1757165 A CN 1757165A CN A038026554 A CNA038026554 A CN A038026554A CN 03802655 A CN03802655 A CN 03802655A CN 1757165 A CN1757165 A CN 1757165A

- Authority

- CN

- China

- Prior art keywords

- decoder

- error

- piece

- code word

- block

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B20/00—Signal processing not specific to the method of recording or reproducing; Circuits therefor

- G11B20/10—Digital recording or reproducing

- G11B20/18—Error detection or correction; Testing, e.g. of drop-outs

- G11B20/1803—Error detection or correction; Testing, e.g. of drop-outs by redundancy in data representation

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B20/00—Signal processing not specific to the method of recording or reproducing; Circuits therefor

- G11B20/10—Digital recording or reproducing

- G11B20/10009—Improvement or modification of read or write signals

- G11B20/10268—Improvement or modification of read or write signals bit detection or demodulation methods

- G11B20/10287—Improvement or modification of read or write signals bit detection or demodulation methods using probabilistic methods, e.g. maximum likelihood detectors

- G11B20/10296—Improvement or modification of read or write signals bit detection or demodulation methods using probabilistic methods, e.g. maximum likelihood detectors using the Viterbi algorithm

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/13—Linear codes

- H03M13/15—Cyclic codes, i.e. cyclic shifts of codewords produce other codewords, e.g. codes defined by a generator polynomial, Bose-Chaudhuri-Hocquenghem [BCH] codes

- H03M13/151—Cyclic codes, i.e. cyclic shifts of codewords produce other codewords, e.g. codes defined by a generator polynomial, Bose-Chaudhuri-Hocquenghem [BCH] codes using error location or error correction polynomials

- H03M13/1515—Reed-Solomon codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/13—Linear codes

- H03M13/15—Cyclic codes, i.e. cyclic shifts of codewords produce other codewords, e.g. codes defined by a generator polynomial, Bose-Chaudhuri-Hocquenghem [BCH] codes

- H03M13/151—Cyclic codes, i.e. cyclic shifts of codewords produce other codewords, e.g. codes defined by a generator polynomial, Bose-Chaudhuri-Hocquenghem [BCH] codes using error location or error correction polynomials

- H03M13/1555—Pipelined decoder implementations

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Probability & Statistics with Applications (AREA)

- Theoretical Computer Science (AREA)

- Signal Processing (AREA)

- Algebra (AREA)

- General Physics & Mathematics (AREA)

- Pure & Applied Mathematics (AREA)

- Error Detection And Correction (AREA)

- Detection And Prevention Of Errors In Transmission (AREA)

- Detection And Correction Of Errors (AREA)

Abstract

描述了一种译码器和译码方法,其中在出错位组生成器(410)中从码字计算出错位组,在错误多项式生成器(420)中根据出错位组生成错误多项式,在错误位置生成器(430)中从错误多项式确定错误位置,在错误大小生成器(440)中从错误多项式计算错误大小,以及由纠错码字生成器(450)根据错误位置和错误大小校正码字。描述了译码器内部块消息传送方案,其中一个或多个部件(410,420,430,440,450)生成不活动消息(640,650),以便发信号告知具有处理相应于下一个码字的能力。描述了双Chien搜索块(930,940)实施方案,其中Chien块(930)被使用来确定相应于特定的码字的错误的数目,这与由Chien/Forney块(940)执行的错误位置与大小的计算是分开的。描述了增强的Chien搜索单元结构,它利用附加的Galois区加法器(1140)来使码字与错误矢量同步,由此减小延时和相应于用LIPO寄存器(952)实施的纠错块(950)的花费。

Description

相关专利申请交叉参考

本发明专利申请涉及到同时提交的、题目为“Dual Chien SearchBloccks in an Error-ccorrecting Deccoder(纠错译码器中的双Chien搜索块)”的、2002年1月23日提交的美国专利申请No.10/055,076(代理人文档号No.PU020003);和题目为“Chien Search Cell foran Error-correcting Deccoder(用于纠错译码器的Chien搜索单元)”的、2002年1月23日提交的美国专利申请No.10/055,470(代理人文档号No.PU020001),这两个专利申请整体地在此引用,以供参考。

发明领域

本发明涉及数字通信系统检错和纠错。

发明背景

任何现代数字通信系统的重要功能是错误控制编码。错误控制编码是通信中涉及数字系统检错和纠错技术的领域。通常,每当希望保证在传输期间或在贮存数字数据时不把错误引入数据中,或替换地,当错误被引入到数据时要纠正引入的错误,于是就要利用检错/纠错方案。检测和/或纠正数据错误的能力是通过给数据添加冗余度而完成的。在传输的或存储的数据中包括冗余比特,可导致编码的信号或区比起原先的未编码的信号或区包括更多的比特。

一种经常使用的、用于检错/纠错的方案是所谓的里德-所罗门(Reed-Solomon)码。里德-所罗门码是非二进制系统循环线性块代码。非二进制码作用于由几个比特组成的码元。诸如里德-所罗门码这样的非二进制码善于纠正突发错误,因为通过这些代码的纠错是在码元级别上完成的。诸如里德-所罗门码这样的系统码生成这样的码字,它们包含未改变形式的消息码元。编码器把可逆的数学函数用于消息码元上,以便生成冗余度或奇偶校验码元。然后通过把奇偶校验码元附加到消息码元而形成码字。里德-所罗门码被看作为循环码,因为任何有效的码字的环形移位也产生另一个有效的码字。循环码是流行的,因为存在有效的和便宜的译码技术来实施循环码。最后,里德-所罗门码被认为是线性的,因为任何两个有效的码字相加会导致另一个有效的码字。

典型的里德-所罗门译码器包括以下的主要部件块:(i)出错位组(syndrome)生成块,(ii)错误多项式块,(iii)错误位置块,(iv)错误大小块,(v)纠错块,以及(vi)延时块。出错位组生成块被使用来接收码字和从码字生成出错位组。出错位组用于在错误多项式块中建立错误多项式。错误多项式被传送到错误位置块和错误大小块,在其中分别确定码字的错误位置和大小。从错误位置和大小生成错误矢量。接收的码字的延时的版本通过纠错块使用与特定的码字相对应的错误矢量而被纠正。延时块包括存储器,以便在执行译码处理以产生错误矢量的同时存储接收的码字。

现有技术译码器使用这些块来形成“传递流水线”。也就是,加到一个块的输入仅仅取决于前一个块的输出,而从一个部件块到以前的或以后的块间没有反馈。所以,一次只有一个码字被处理,以及在以前码字的处理完成之前不开始处理下一个码字。

发明概要

本发明涉及一种用于在码字内执行数据检错的方法和设备,它克服现有技术的低效率。执行数据错误检测的译码器包括:出错位组生成器,用于从码字计算出错位组;错误多项式生成器,用于从出错位组生成错误多项式;错误位置生成器,用于从错误多项式确定错误位置;以及错误大小生成器,用于从错误多项式计算错误大小。该译码器的特征在于,它适合于发送来自包括出错位组生成器、错误多项式生成器、错误位置生成器、和错误大小生成器的一个组中选择出至少一个部件的译码器内不活动消息。

附图简述

现在结合附图参考本发明的以下说明,其中:

图1是含有纠错方案的数字数据传递系统的方框图;

图2是显示典型的纠错方案方法的流程图;

图3是各种纠错方案的分级结构示意图;

图4是里德-所罗门(RS)译码器的方框图;

图5是按照本发明的原理使用的、里德-所罗门(RS)译码器的示例性实施例的方框图;

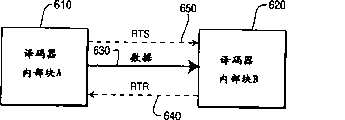

图6是显示按照本发明的原理的、示例的译码器内握手协议的方框图;

图7是显示按照本发明的原理的、在里德-所罗门(RS)译码器的示例性实施例的功能块之间的握手协议的方框图;

图8是按照本发明的原理的、显示与使用译码器内握手有关的效率的、示例性里德-所罗门(RS)译码器的时序图;

图9是按照本发明的原理的、在利用Chien/Forney块以外还利用Chien块的里德-所罗门(RS)译码器的示例性实施例的方框图;

图10是在里德-所罗门(RS)译码器中实施的典型的现有技术Chien搜索单元的方框图;以及

图11是按照本发明的原理的、在其中减小了存储器要求和延时的里德-所罗门(RS)译码器中实施的改进的Chien搜索单元的方框图。

发明详细描述

参照图1,图上显示按照在本发明中体现的原理的、含有检错/纠错方案的数字数据传递系统100的方框图。通常,每当希望保证在传输期间或在贮存数字数据时不把错误引入数据中,或替换地,当错误被引入到数据时要纠正引入的错误,于是就要利用检错/纠错方案。检测和/或纠正数据错误的能力是通过给数据加上冗余度而完成的。在传输的或存储的数据中包括冗余比特,导致编码的信号或区比起原先的未编码的信号或区包括更多的比特。对于容忍这种附加开销的补偿物是检错或检错与纠错的能力。通过使用错误控制编码而得到的性能改进常常用编码增益来测量。假设未编码的通信系统在30dB的信号噪声比(SNR)下达到给定的误码率(BER)。如果具有3dB的编码增益的错误控制编码方案被加到系统,则编码系统能够在27dB的甚至更低的SNR下达到该BER。替换地,如果系统工作在30dB的SNR下,则编码系统达到的BER是未编码系统在33dB的SNR下达到相同的BER。编码增益的能力在于,它允许通信系统(i)以比起未编码时可能达到的更低的SNR下保持想要的BER,或(ii)在给定的SNR下,得到比起未编码系统所能得到的BER更好的BER。

例如,编码器110的功能正是从数据源接受数字数据以及经由信道发送数据或把数据存储在贮存媒体(一起显示为信道或存储装置115)或者再不然就变换或处理该数据。经常是这样的情形,在传输或存储期间,数据可能引入噪声或错误125,因此变为出错或在原先的数字数据的形式上发生改变。译码器120用来检测和纠正,或在替换例中仅仅去检测:数字数据的规定的部分是否出错。

参照图2,图上显示在发射机/信道/接收机环境方面可提供的各种检错/纠错处理过程的流程图。虽然在这一含义上进行描述,但本领域技术人员将会看到,这样的检错/纠错处理过程也同样可应用到广播传输,数字数据存储或其中数字数据(无论是数据区,分组,数据流等的形式)被处理或变换的任何其他处理。作为仅仅是说明性而不是意味着穷举的或排他的例子,以下的技术/设备,可以利用检测/纠错方案来改进性能、整体性和可靠性:(i)各种存储装置,包括但不限于磁带、光盘(CD)、数字通用盘(DVD)、条形码等,(ii)有线或移动通信(包括蜂窝电话、双向收发信机、微波链路等),(iii)卫星通信,(iv)数字无线电、数字电视机(DTV)、数字视频广播(DVB)、等,(v)调制解调器,包括但不限于电缆、V.pcm、ADSL、xDSL等。

按照步骤210,在初始建立链路和协商传输信道参量后,发送源以适合于传输的形式处理数字数据。按照步骤215,在传输之前,该源生成错误码;错误码至少部分地基于要被发送的数字数据的数值,因此提供数据冗余度。按照步骤220,生成的错误码被附加、附着、复接,或以其它方式与数字数据被包括在一起,并从发射机发送到接收机。按照步骤225,数字数据和错误码在接收机处被接收。按照步骤230,在接收机处实施初始信号处理,如果需要的话。按照步骤235,接收机选取错误码冗余比特,和按照所利用的错误控制码方案处理被包含在其中的信息。按照步骤240,如果所处理的冗余的比特对于接收的数字数据的检验是肯定的,则数据被假设为未出错的。按照步骤245,在接收机处继续进行数字信号的信号处理(如果有的话)。

然而,按照步骤250,如果所处理的冗余的比特表示接收的数字数据是出错的(包含至少一个比特错误),则对数据错误进行评估,以确定该错误在所利用的错误控制方案内是否为可纠正的。也就是,某些错误控制方案只能进行检测,但不包括允许对这些错误进行纠正所需的冗余数据的质量和类型。其他错误控制方案可能只利用它们的检错能力,而不管它们可能具有检错和纠错能力。通常,这是在任何特定的数据信号、消息、或分组的准确性不是最重要,而数据的一致的和及时的传递是最重要时所利用的方案。这样的应用的一个例子是用于话音、音频和视频应用的同步流数据。另外,即使当检错方案被利用来检错和纠错时,如果所检测的错误的数目或突发大于纠错能力(也就是,超过了错误码比特所提供的冗余信息),则数据是不可恢复的。按照步骤255,如果数据是可纠错的,则数据错误被纠正,以及在接收机处继续进行另外的信号处理(如果有的话)。然而,按照步骤260,如果错误是不可纠正的,则执行评估以确定数据精度是否必不可少。按照步骤265,如果数据准确性是必不可少的,如在纯数据系统中那样,则很可能单个比特错误就是关键的,以及把重发请求发回到发射源。然而,按照步骤270,如果不可纠正的数据的准确性是不重要的,如同步性质的数据传送(诸如,话音、音频、或视频)的情形,则出错的和不可纠正的数据仅仅被丢弃,而处理下一个接连的数据消息。

参照图3,图上显示用于各种错误码分类和方案的分级结构。错误码310可被划分成两个基本类别:(i)自动重发请求(ARQ)或检错码315,以及(ii)前向纠错(FEC)码320。ARQ是只有检错类型的编码,其中传输中的错误可被接收机检测,但不能纠正。接收机必须请求任何接收的数据,并请求重发收到但已检测到错误的数据。因为这些重发将窃取宝贵的带宽,ARQ码常常被使用于“干净”传输媒体(具有较低的出错概率的传输)。一个最普通的例子是简单的奇偶校验检查325,它常常用于检测RAM中的数据错误。另一个例子是循环冗余检查(CRC)330,它被使用来检测在例如通过以太网传输中的错误。如果检测到错误,消息将被重发。因为以太网主要是通过有线发送的,出错的机会小于对于某些其他媒体的情形。CRC和ARQ仅仅是检错码方案的两个说明性例子;其他检错码方案对于本领域技术人员是已知的。仅仅检测错误而不纠正错误的错误码比起进行纠错的错误码增加少得多的冗余度。而且,检错译码器比起纠错译码器在复杂性上简单得多。利用检错码方案的系统对于由于数据重发引起的附加开销通常在带宽上是能够承受的。也就是,数据重发并不很大地影响总的系统通过量。

由于噪声多的媒体有很大机会把错误引入到给定的传输,ARQ方法的使用意味着经常重发数据,使得系统通过量减小到无法接受的程度。在这些情形下,纠错码(正如其名称暗示的)不单允许在接收端检测错误,也允许纠正错误。这减小了数据重发的需要,它只在错误的数目大于所利用的纠错方法可纠正的错误数目时才需要重发。纠错也被使用于单向通信,其中接收机请求发进者重发的机会是无法得到的。这些单向路径的说明性例子包括某些卫星传输和磁带存储媒体。

纠错码可被划分成两种主要的子类别。第一种是块码335,第二种是卷积码340。块码335是经常使用的纠错码,它作用于确定的有限长度的消息块。块码335所以起这样的名称是因为该子类别利用一个处理消息码元块和然后生成码字码元块的编码器。块码通常可被分类为两种类型:二进制码345和非二进制码355。二进制码345的一个例子是汉明(Hamming)码350,其特征在于每个字符具有四个信息比特和三个检验比特。非二进制码的例子是里德-所罗门码360。

相反,卷积码340编码器作用于连续的消息码元流,以及同时生成连续的编码的输出流。这些码所以得到这样的名称是因为编码过程可被看作为消息码元的卷积和编码器的脉冲响应。卷积码340的两个例子是网格编码调制(TCM)365和二进制卷积编码370。

图4是示例性里德-所罗门(RS)译码器的方框图。如前所述,里德-所罗门码是非二进制系统循环信息块码。非二进制码作用于由几个比特组成的码元。非二进制码的通常的码元大小是8比特或一个字节。非二进制码,诸如里德-所罗门码,善于纠正突发错误,因为这些码的纠错是在码元级别上完成的。通过在译码过程中作用于码元,这些码可以纠正具有8个错误的突发的码元,同它们纠正具有单个比特错误的码元一样容易。系统码,诸如里德-所罗门码,生成包含未改变形式的消息码元的码字。编码器把可逆的数学函数应用于消息码元上,以便生成冗余度或奇偶校验的码元。然后通过把奇偶校验码元附着到消息码元而形成码字。里德-所罗门码被看作为循环码,因为任何有效的码字的环形移位也产生另一个有效的码字。循环码是流行的,因为存在有效的和便宜的译码技术来实施循环码。最后,里德-所罗门码被认为是线性的,因为任何两个有效的码字相加导致另一个有效的码字。

错误控制码的理论利用被称为有限区或Galois区的数学结构。Galois区是包含有限数目的元素的组。对于这个组的加法和乘法运算被定义,以及这些运算相当于通常的算术所预期的结果。例如,相加的单位元素是0,以及相乘的单位元素是1。里德-所罗门码是通过利用Galois区数学实施的,它决定了码的循环和线性性质以及作用于阶数q=pm的Galois区,其中p是正质数,以及m是正数。阶数q的Galois区被表示为GF(q),以及它包含q个不同的元素。

这样来表示已知的里德-所罗门码,即将它称为(n,k)码。参量n代表用码字中的码元数所表示的码字长度。参量k表示码字中的消息码元的数目。因此加上的奇偶校验码元的数目是n-k。该代码的纠错能力是t=(n-k)/2。该代码可检测和纠正T个错误,其中0≤T≤t。码字是基于消息码元的,并由里德-所罗门编码器生成。由于里德-所罗门码是系统码,所以n个消息码元按照其原样发送,而n-k个奇偶校验码元则被附着到消息码元而形成码字。奇偶校验码元的数值取决于消息码元,这些奇偶校验码元增加了发送码字的冗余度。这个冗余度被接收机的译码器利用来检错和纠错。

在接收机的译码器处,码字作为供到出错位组生成块410的输入被接收。由译码器执行的第一步骤是由出错位组生成块410(也经常称为出错位组生成模块,或简称为出错位组生成器)执行的出错位组计算。出错位组由n-k个码元组成,以及它的值从接收的码字计算。出错位组只取决于错误矢量,它与发送的码字无关。也就是说,每个错误矢量具有唯一的出错位组矢量,但许多不同的接收的码字如果它们的错误图案相同,则将具有相同的出错位组。首先计算出错位组的原因是因为,这样做将使得错误矢量的搜索区变窄。首先知道出错位组将能从2n个可能的总的错误矢量减小为2n-k个确切的错误矢量。

出错位组生成块410计算出错位组的一个方法是使用Galois区代数把接收的码字除以生成器多项式。这个除法的余数被称为出错位组多项式s(x)。实际的出错位组矢量S(x)是通过估计s(x)在α到αn-k处的值而被计算的。然而,这个方法从硬件方面看来其效率可能不是最佳,则在硬件上经常使用的替换的方法是直接估计在α到αn-k处的接收的码字R(x)。出错位组生成块410通过估计在α到αn-k处的接收的码字R,也就是R(α)到R(αn-k),而计算出错位组S。在里德-所罗门码中,n-k=2t,因此有2t个出错位组值要计算:[S1 S2S3...S(2t)]。这些数值典型地是并行地计算的,第一出错位组生成器估计在α处的接收的码字,以形成S1,下一个出错位组生成器估计在α2处的接收的码字,以形成S2,等等。

一旦出错位组被出错位组生成块410算出,它的数值就被传送到错误多项式块420。在这里,出错位组被利用来建立错误位置多项式。这个过程牵涉到求解t个未知数的联立方程。几种快速算法可提供用于这些计算,包括Beriekamp-Massey算法,或欧几里得算法。这些算法利用里德-所罗门码的专门的矩阵结构从而大大地减小所需要的计算量。

错误多项式块420把错误位置多项式(一旦被确定)传送到错误位置块430和错误大小块440。错误位置块430求解错误位置多项式的根,以确定错误位置。典型地,这是通过利用Chien搜索算法,或Chien单元而完成的。由错误位置块430确定的错误位置连同以前确定的错误位置多项式一起被传送到错误大小块440。错误大小块440通过求解t个未知数的联立方程而确定错误大小。在实施错误大小块440时使用的快速和广泛使用的算法是Forney算法。

计算的错误位置和错误大小被转发到纠错块450,用于恢复纠正的码字,如果它出错的话。通常,错误位置和错误大小的组合被称为错误矢量。错误矢量是与码字相同的尺寸,以及在相应于错误的位置上包含非零值。所有其他的位置包含零。加到纠错块450的另一个输入是延时块460的输出。延时块460接收所收到的码字,以及输出相同但具有延时的所接收到的码字。在一个实施例中,纠错块450是通过使用Galois区加法器452与LIFO(后进先出)块454而实施的。在接收的码字中的错误通过使用Galois区加法器452把接收的码字加到错误矢量而被纠正。利用LIFO块454是因为错误矢量是以接收的码字的相反的次序生成的,所以必须对接收的码字或错误矢量应用LIFO运算,以便匹配这两个矢量的字节的向上的次序。纠错块450的输出是原先的码字的译码器的估值。

图5是里德-所罗门(RS)译码器的示例性实施例的方框图。该输入是转发到出错位组生成块510而接收到的码字。一旦出错位组S(x)被出错位组生成块510计算,它的数值就被传送到欧几里得算法块520。欧几里得算法处理出错位组S(x),以便生成错误位置多项式Λ(x)和错误大小多项式Ω(x)。也就是,它求解被称为关键方程的以下的方程:

Λ(x)[1+S(x)]=Ω(x)modx2t+1 公式1

在里德-所罗门译码时使用的算法是基于欧几里得算法,用于找到两个多项式的最大公因子(GCD)。欧几里得算法是熟知的迭代多项式除法算法。

一旦错误位置多项式Λ(x)被计算,就需要对它进行估值以找出它的根。Chien搜索算法被使用来找出这些根。Chien搜索是一种强力算法,它对多项式的所有可能的输入值都要计算,然后确定哪些输出等于零。如果在位置i出现错误,则以下的方程等于零:

Chien搜索对i和j的所有的数值都计算公式(2),并将该公式等于零的次数计数。零的位置是错误的位置,而零的数目是出错的码元的数目。

在示例性实施例中,具有(t+1)级用硬件实施的Chien搜索。这些级的每级(其中一级由一个乘法器、一个复接器和一个寄存器组成)代表在以上的Chien搜索方程中对于j的不同的数值。搜索运行n个时钟循环(每个时钟循环代表在以上方程中i的不同的数值),以及查看加法器的输出是否等于零。如果它等于零,则零检测块将输出一个1,否则,它输出1个0。Chien搜索块的输出因此是具有’0’或’1’数值的n比特的一个串。每个’1’代表出错码元的位置。

对于第一时钟循环,复接器把错误位置多项式系数发送到寄存器。对于剩余的(n-1)时钟循环,乘法器的输出经由复接器被发送到寄存器。乘法器的指数具有负的数值。然而,这些数值可以通过使用取模算子预先进行计算。α-1的指数等于(-i模n)=(-i模255)。例如,α-1等于α254,α-2等于α253,等等。

Forney算法用来计算错误值Yi。为了计算这些值,Forney算法使用错误位置多项式Λ(x)和错误大小多项式Ω(x)。用于错误值的公式是,

对于x=α-1,其中α-1是Λ(x)的根。

形式导数Λ’(x)的计算实际上相当简单。例如,假设Λ(x)=

α4X3+α3X2+αX+α2。Λ’(x)因此等于

Λ′(x)=3α4X2+2α3X+α 公式4

=(α4+α4+α4)X2+(α3+α3)X+α

=α4X2+α

该导数是通过取X的奇次幂的系数,以及把它们指派给X的接着的较低的幂(它将是偶次幂),而形成的。

然后通过使用与Chien搜索所使用的相同的类型的硬件来估计Ω(x)多项式和Ω’(x)多项式。为了估计Ω(x),把Ω0系数加上Ω1乘以α-1,Ω2乘以α-2,等等直至Ωt乘以α-t。这些乘法器的输出然后被相加。

然后把分子与使用逆乘法的分母相乘。逆乘法包含一个查找表,它找出分母的倒数。例如,如果分母是α3,倒数是α-3。这可表示为:

α-1=α(-1modn)=α(-3mod255)=α252。 公式5

由于对于Chien搜索和Forney算法需要相同的类型的硬件,这两个功能可被组合在同一个块,被显示为Chien/Forney块530。在本实施方案中,在Chien搜索的输出端使用了两个加法器。第一加法器相加偶数级的数值,以及另一个加法器相加奇数级的数值。为了形成最后的Chien搜索输出,这两个加法器的输出然后相加,以及零检测块检测根的位置。奇数级加法器的输出也用于Forney算法。奇数级的和值代表Forney公式的分母。对这个和值计算倒数,然后把它与计算错误大小多项式所形成的分子值相乘。该输出和零检测输出进行’与’运算,因为错误值只对于实际的错误位置是有效的(不然它们应当被设置为零)。

因此,Chien/Forney块530使用错误位置多项式和错误大小多项式来生成错误矢量,并把它转发到纠错块540。错误矢量是与码字相同的大小,以及在相应于错误的位置上包含非零值。所有其他的位置包含零。加到纠错块540的另一个输入是延时块550的输出。延时块550取接收的码字,以及输出经延时的相同的接收的码字。在本实施例中,纠错块540是用Galois区加法器544与LIFO块542而实施的。在接收的码字中的错误通过使用Galois区加法器544把接收的码字加到错误矢量而被纠正。利用LIFO块542是因为错误矢量是以接收的码字的相反的次序生成的,所以必须对接收的码字或错误矢量应用LIFO运算,以便使这两个矢量的字节的次序同步。纠错块540的输出是原先的码字的译码器的估值。

译码器内部部件块的消息传送

如前所述,里德-所罗门译码器具有至少四个主部件或功能块。它们是出错位组生成器,错误多项式块,错误位置块,和错误大小块。如果译码器除了检测错误以外还纠正错误,则译码器还包括纠错块。在现有技术的译码器中,这些块形成“传递流水线”,因为,加到一个块的输入只取决于以前块的输出。也就是,从一个块到以前的块没有反馈。里德-所罗门译码器在对特定的码字(由图4和5的延时块表示)执行译码过程时也需要存储器或缓存器块的实施方案以存储接收的码字。在完成译码过程时,错误位置/大小块产生错误矢量,以及这个错误矢量与存储在存储器中的接收的码字进行“异或”运算,以便形成译码器输出。典型地,所使用的存储器的大小等于一个码字,因此,译码器一次只能处理单个码字。

图6是显示按照本发明的原理的译码器内握手协议的示例性实施例的方框图。译码器内部块A610和译码器内部块B620代表里德-所罗门译码器内任何两个块(根据上述的功能块而选择的),它们利用块之间的反馈或通信。译码“传递流水线”是数据信道630,它代表在里德-所罗门译码器的功能块之间的任何现有技术的单向信道。另外,按照本发明,也显示反馈信道。反馈信道可被看作为一个功能块把它的现在的和将来的不活动性输送到上游或下游功能块的手段。例如,假设译码器内部块A610对特定的码字完成了它的处理功能。译码器内部块A610发送不活动消息到译码器内部块B620,表示它准备好把它对于特定的码字实施的计算功能的结果转发到译码器内部块B620。因此,这种类型的不活动消息被称为“准备好发送”(RTS)消息650。相反,假设译码器内部块B620对特定的码字完成了它的处理功能。译码器内部块B620发送不活动消息到译码器内部块A610,表示它准备好接收。因此,这种类型的不活动消息被称为“准备好接收”(RTR)消息640。

本发明的这个实施例--带有在功能块之间的反馈或握手的译码器实施方案--具有这样的优点,即它使得用户可配置的结构能够适用于智能特性(IP)核心,它允许用户根据他希望使用的、用来实施译码器的存储器的大小来定制译码器的性能。

图7是显示在里德-所罗门(RS)译码器的示例性实施例的功能块之间的握手协议的方框图。出错位组生成块410、错误多项式块420、错误位置块430、错误大小块440、纠错块450(包括Galois区相加器452和LIFO块454)和延时块460的功能等的目的和运行已参照图4作了充分描述,所以这里不再重复。图7上显示新包括的部分,即,上述的不活动消息(或握手信号)。握手信号(例如,RTS和RTR消息)被处理块使用来表示它们何时发送数据和/或它们何时准备好接收数据。所以,出错位组生成块410和错误多项式块420能够经由RTS信道710交换RTS消息或经由RTR信道712交换RTR消息。错误多项式块420和错误位置块430能够经由RTS信道718交换RTS消息或经由RTR信道720交换RTR消息。错误多项式块420和错误大小块440能够经由RTS信道724交换RTS消息或经由RTR信道726交换RTR消息。错误多项式块420和纠错块450能够经由RTS信道724交换RTS消息或经由RTR信道726交换RTR消息。出错位组生成块410也适配于通过经由RTR信道740发送RTR消息而请求下一个接收的码字。纠错块450也适配于经由RTS信道760发送RTS消息到输出处理级。另外,取决于所选择的本发明的实施方案,可能必须发送任何的RTR或RTS消息到延时块460(经由消息传送信道750),以用于适当地调节延时,使得被检验的和被纠正的接收的码字在纠错块450处与错误矢量正确地同步。

从本发明得出的有利的功效在于,通过使得在译码器内部功能块之间能进行握手,功能块能够在它成为不活动时(也就是,它完成它的上一个程序过程)请求接收更多的要处理的数据。类似地,一个功能块能够发信号通知下游功能块:它已完成它的程序过程,以及无论何时下游功能块能够接收该结果时它就转发该结果。例如,虽然典型地,出错位组生成块410利用固定的(和已知的)数目的时钟周期来生成对于特定的长度的接收码字的出错位组,但错误多项式块420是一个执行时间可以变化的迭代过程。另外,典型地,错误位置块430和错误大小块440将花费固定的(和已知的)数目的时钟周期,但如果确定了在码字内存在太多的错误以使得它是不可纠正的,则对于该码字可停止进一步的处理,以及错误位置块430和错误大小块440可以通过经由适当的RTR信道720,726发送RTR消息到错误多项式块420而请求开始为下一个码字工作。所以,错误位置块430和错误大小块440也可花费可变的数目的时钟周期来完成。

应当指出,图7所示的本发明的实施例仅仅是可以不背离本发明的精神和范围而被实施的几个实施例中的一个实施例。例如,译码器的每个功能块不必都有发送RTS和RTR消息的配备。而是,作为设计的选择,可能希望只在出错位组生成块410与错误多项式块420之间能够进行握手。多个其他变例也是可能的。而且,虽然RTS和RTR消息被显示和描述为通过RTS和RTR信道传送的,但这样的说明仅仅是逻辑说明,以及消息传送信道可被合并到与数据信道分开的一个公共物理层消息传送信道,或替换地,消息传送信道可被合并到与数据信道本身相同的物理层。

按照本发明的原理,用户可通过改变存储器分配的大小而定制译码器的性能。所以,具有已分配的存储器大小等于一个码字的长度的实施例将具有硬件和功率上都经济的设计,但它一次只能处理一个码字。具有已分配的存储器大小大于一个码字的长度的实施例可以在处理一个码字时同时开始装载第二码字。具有已分配的存储器大小为两个码字的长度的实施例将能够同时处理两个码字,等等。当然,增加所含有的存储器的大小,相应地导致在硬件和功率方面更多的花费,但好处是译码处理的速度的相应的增加,和等待时间减小,因为在给定的时间量内可以处理更大数目的码字。握手信号使得处理完全自动化,这样,用户只需要输入译码器所利用的存储器大小。通过控制这个单独的参量,用户可定制译码器在速度、功率和尺寸方面的性能(门计数)。

图8是按照本发明的原理的示例性里德-所罗门(RS)译码器的时序图,它显示与译码器使用块内握手有关的效率。时序图810的上部显示在不带块内握手的典型译码器中处理所需要的时间。在这个方案下,码字1(CW1)的处理在时间t0开始。在时间t1生成CW1出错位组,以及其结果被传送到错误多项式块。错误多项式块在时间t2完成CW1,等等,直至在时间t4完成CW1的处理。码字2(CW2)的处理所以在时间t4开始。对于CW2继续进行单功能顺序处理,直至在时间t8,对于CW2的错误位置和错误大小计算完成为止。应当指出,在不带块内握手时处理两个码字总共花费(t8-t0)个单位的时间。

时序图820的下部显示在具有块内握手的译码器中的处理时间。应当指出,通过实施存储器足够大到用于三个码字,译码器可以一次同时处理三个码字。由于每个块在它完成处理的时刻时能够接收更多的数据,这个效率被达到,因为它通知以前的块:它已准备好。在这个说明性例子中,码字3(CW3)的处理有时在时间t6和t7之间完成。

在纠错译码器中的双Chien搜索块

本发明的一个示例性实施例使用双Chien搜索块来实施纠错过程。利用本发明的这个实施例的原理的译码器同时减小译码器等待时间与对译码器存储装置/存储器的需要。

图9是按照本发明的原理的、利用双Chien搜索块的里德-所罗门(RS)译码器的示例性实施例的方框图。输入是被转发到出错位组生成块910的接收码字。一旦出错位组S(x)被出错位组生成块910计算出来,该出错位组就被转发到欧几里得算法块920。欧几里得算法被使用来处理出错位组S(x),以便生成错误位置多项式Λ(x)和错误大小多项式Ω(x)。

在本发明的本实施例中,新的Chien块930被包含进来以便用来确定码字中的错误的数目。一旦错误位置多项式Λ(x)被计算,Chien块930就应用Chien搜索算法来估计它的根。Chien搜索是一种强力算法,它计算多项式的所有可能的输入值,然后确定哪些输出等于零。如果在位置i出现错误,则以下的方程等于零:

Chien块930计算以上公式的i和j的所有的数值,并对该方程等于零的出现的次数计数。最终得到的数目是检测到的错误数目。

如前所述,错误多项式必须同时为错误位置和错误大小而进行计算。由于对于实施Chien搜索个Forney算法需要相同的类型的硬件,两种功能可被组合到同一个块,被显示为Chien/Forney块940。在本实施方案中,在Chien搜索的输出端处使用了两个加法器。第一加法器相加偶数级的数值,以及另一个加法器相加奇数级的数值。为了形成最后的Chien搜索输出,这两个加法器的输出然后进行相加,以及零检测块检测根的位置。用于奇数级的加法器的输出也被用于Forney算法。奇数级的和值代表Forney公式的分母。对这个和值计算其倒数,然后把它与通过计算错误大小多项式所形成的分子值相乘。该输出和该零检测的输出进行’与’运算,因为错误值只对于实际的错误位置是有效的(否则它们应当被设置为零)。

因此,Chien/Forney块940使用错误位置多项式和错误大小多项式来生成错误矢量,并把它转发到纠错块950。错误矢量与码字有相同的大小,以及在相应于错误的位置上包含非零值。所有其他的位置包含零。加到纠错块950的另一个输入是延时块960的输出。延时块960取接收的码字,以及输出经延时的相同的接收的码字。在本实施例中,纠错块950是通过一起使用Galois区加法器954与LIFO块952而实施的。在接收的码字中的错误通过使用Galois区加法器954把接收的码字加到错误矢量而被纠正。利用LIFO块952是因为错误矢量是以接收的码字相反的次序而生成的,所以必须对接收的码字或错误矢量应用LIFO运算,以使这两个矢量的向上的字节的次序匹配。纠错块950的输出是原先的码字的译码器的估值。

里德-所罗门译码器只能纠正多达t个错误,其中所包括的奇偶校验字节数是2t。如果检测到大于t的个数的错误,则通常希望把接收的码字不改变和不纠正地转发到译码器输出端,因为如果检测到的错误数大于t,则码字是无法纠正的。在现有技术Chien/Forney实施方案中,整个码字必须在错误数目被确定之前处理。因此,运算要花费N个时钟周期,其中N是码字的长度。一旦完成了Chien/Forney计算,就确定错误的数目以及把它与t的数值进行比较。如果错误数小于或等于t,则来自Chien/Forney块的错误值与接收的码字进行“异或”(XOR)运算,以执行纠错,从而生成最后的译码器输出。然而,如果错误数大于t,则接收的码字不改变地作为译码器输出被转发。因此,现有技术方法需要存储整个接收的码字,直至由Chien/Forney块进行的处理完成为止。这样的方案也引入等待时间延时,因为在块的整个N个时钟循环完成之前译码器不能转发输出。

相反,本发明的本实施例把码字提交到Chien算法两次;第一次确定错误的数目,以及第二次确定错误的位置。因此,当Chien块930检测到错误数目大于阈值t时,接收的码字作为译码器输出被传送,以及存储器被释放。相反,当错误数目小于或等于阈值t时,数据被传送到Chien/Forney块,以便确定实际的错误位置和大小。这样的实施方案当结合图6-8所示的本发明的握手实施例被利用时,将得到最佳化。这样的组合使得Chien/Forney块940能够在Chien块930正在确定下一个码字的错误的数目的同时计算错误。因此,Chien/Forney块940的输出可被立即发送以及相应的存储器被释放。

用于纠错译码器的增强的Chien搜索单元

如前所述,Chien/Forney块接收两个多项式作为输入:错误位置和错误大小多项式;以及生成错误矢量作为输出。错误矢量是N字节的矢量,它代表译码器对接收的码字中的错误的估值。错误矢量与接收的码字进行“异或”(XOR)运算,以便纠错而形成译码器对原先的码字的估值。使用Chien/Forney块以确定错误矢量的现有技术译码器以相对于码字矢量相反的次序产生错误矢量。也就是,码字和错误矢量在错误矢量(或相反地,码字)没有经过进一步处理时,不能进行XOR运算。典型地,这个进一步处理是对错误矢量或接收码字执行LIFO(后进先出)运行,目的是颠倒输入的次序,使得码字和错误矢量可进行XOR运算。不幸地,这引入N个时钟周期的延时,其中N是码字中的字节数目。另外,某些现有技术实施方案使用的存储器的大小大于单个码字的长度,因此需要存储器分解成两个或多个分开的LIFO时钟。这样做会造成寻址的复杂性,而且也限制了存储器尺寸为码字长度的整数倍。

本发明的一个示例性实施例是新的Chien搜索单元,它产生与码字正确地同步的输出。也就是,错误矢量或码字矢量在进行XOR运算之前都不需要颠倒,因此消除了对于LIFO块或其他倒相装置的需要。所以,得到较短的等待时间间隔,因为不需要N时钟周期的延时。而且,本发明的本实施例简化了寻址方案(相对于现有技术),以及支持仅为码字长度整倍数之外的其它存储器大小。例如,可以使用具有码字长度的两倍半的存储器,它允许译码器在下一个码字的一部分被装载的同时处理两个码字。

图10是典型的现有技术Chien搜索单元1000的方框图,它是用于Chien搜索和Chien/Forney块的基本构建块。Chien搜索块用来计算错误位置多项式Λ,以便找到它的根。根的位置相应于接收的码字中出错的位置。图10的Chien搜索单元被使用来实施以下方程:

方程7的计算导致码字中的相应于错误的字节位置处的零值。Chien搜索单元1000是用来实施以上方程的单个级的硬件结构。每个级处理错误位置多项式Λ的单个系数,因此总共有(t+1)级(因为错误位置多项式能够具有的最大阶数为t,而阶数为t的多项式具有(t+1)个系数)。

Chien搜索单元1000以迭代方式处理错误位置多项式系数。在第一迭代中,复接器1020接收相应于正在被处理的码字的适当的多项式系数1010,以及把多项式系数发送到寄存器1030。在以后的时钟周期,寄存器的输出首先被转发到乘法器1040,在其中它被乘以α-j,然后被复接器1020发送回寄存器而被存储。这个处理过程在全部N个时钟周期内执行。回过来参照方程7,下标i表示迭代数,以及下标j表示Chien搜索单元的级。也就是,j的数值从0增加到t,因此总共有以硬件实施的(t+1)个Chien搜索单元的级。

作为说明的例子,假设该单元代表第二级(j=1)。因此,在每个时钟周期,寄存器输出被乘以α-1,以及结果被存储回寄存器。这产生以下的序列:

λ+λα-1X+(λα-1)α-1X2+((λα-1)α-1)α-1X3+...

其中Xn代表n个时钟周期的延时。

通过合并项目,产生的最后的序列是:

λ+λα-1X+λα-2X2+λα-3X3+...+λα-(N-1)XN-1

与这个实施方案有关的问题是,错误位置是以相应的码字字节的颠倒的次序产生的,因此,它们在加到码字用于纠错之前需要由LIFO块进行颠倒。LIFO块是包含多个寄存器的硬件存储单元。一旦所有的寄存器被填满,LIFO块就发送出它的输出。在输入中的最后的元素成为输出中的第一元素,等等。对于使用LIFO块有两个问题。一个问题是,它是大的存储装置/存储器元件,因此它增加门计数和IC的功耗。另一个问题是,LIFO块引入N时钟周期的等待时间。这个等待时间的发生是因为LIFO块初始填满时要花费N个时钟周期,而在最后一个元素读到LIFO之前不产生输出。

图11是按照本发明的原理的改进的Chien搜索单元1100的方框图,在其中对存储器的要求和延时都减小了。本发明的本实施例的基本原理是使得Chien搜索块能够产生一个序列,它在数学上等价于通过标准Chien搜索生成的序列,但是具有以相反的次序生成的系数(此后称为“正常化的次序”)。本实施例实现以下两个方程(方程10和11),用来生成用于码字纠正的正常化次序的错误位置。

回想起图10的现有技术Chien搜索单元1000以迭代方式处理错误位置多项式系数,从’0’的α指数值开始,并在每个时钟周期从’0’递减,直至指数减小到-j(N-1)的数值为止。对于图11的Chien搜索单元1100的本实施例,从α指数的数值从-j(N-1)的数值开始,并在每个时钟周期加增量,直至指数达到0为止。

所以,在第一时钟周期期间,多项式系数1110由预乘法器1150乘以α-j(N-1)(其中j是级数),被转发到复接器1120,以及被发送到寄存器1130以用于存储。在以后的各时钟周期,寄存器1130的输出被转发到乘法器1140,在其中它被乘以αj,然后被复接器1120发送回寄存器。

作为说明例,假设该单元代表第二级(j=1)。这产生以下序列:

λα-(N-1)X+(λα-(N-1))αX2+((λα-(N-1))α)αX3+...

合并项目,产生以下序列:

λα-(N-1)+λα-(N-2)X+λα-(N-3)X2+...+λα-1XN-2+λXN-1

应当指出,在这个序列中产生的系数是与图10的标准Chien搜索单元1000产生的系数相同的,除了它们现在是以颠倒的次序(正如由延时系数的颠倒次序表示的)。图11的Chien搜索单元1100确实利用额外的Galois区乘法器(不是一个而是两个),但它们是小的,以及用硬件实施是便宜的。从不再需要LIFO块用于颠倒和从避免由于填充LIFO所需要的延时所得到的优点和功效超过了提供附加的Galois区乘法器给每个Chien搜索单元的缺点。

在单个块内组合Chien搜索和Forney算法是共同的设计实践,因为这两个算法都需要执行类似的功能。结合图11显示的和描述的本发明的本实施例的原理也同样应用到Forney块,因为Forney算法通过使用极其类似的硬件处理错误大小多项式。本领域技术人员将会看到,本发明的原理可以扩展到Forney块单元和Chien/Forney块单元的设计。

许多现有的系统使用“现成的”集成电路,这些电路对里德-所罗门码进行编码和译码。这些IC往往支持一定程度的可编程性(例如,RS(255,k)其中t=1到16码元)。最新的趋势是趋向于VHDL或Verilog设计(逻辑核心或智能特性核心)。它们比起标准IC具有多个优点。逻辑核心可以与其他的VHDL或Verilog部件集成在一起,以及被合成为FPGA(现场可编程门阵列)或ASIC(专用集成电路)--这使能进行所谓的“芯片上的系统”设计,其中多个模块可被组合在单个IC中。取决于生产规模,逻辑核心可提供比起“标准”IC常常花费低得多的系统成本。

虽然本发明是在硬件实施方案方面描述的,但本发明的原理不应当被看作为限于这一点。迄今为止,实时的软件实施方案即使对最简单的里德-所罗门码(即,具有小的t的码)都需要太多的计算能力。用软件实施里德-所罗门码的主要的困难在于,通用处理器不支持Galois区算术运算。例如,用软件实施Galois区乘法需要一次对于0的测试,两个对数查找表,模加法和反对数查找表。然而,仔细的设计连同处理器性能的提高,意味着软件实施方案可以以相当高的数据速率运行。

虽然本发明是藉助于示例性实施例和/或配置被描述的,但本发明可被进一步修改而不背离揭示内容的精神和范围。所以,本专利申请打算覆盖通过使用本发明的一般原理所作出的本发明的任何变化、使用、或调整。而且,本专利申请打算覆盖像来自于本发明涉及到的已知的或传统的实践的以及属于附属权利要求的范围的这样一类不同于本揭示内容的部分。

Claims (20)

1.在具有至少四个块的循环线性块码纠错译码器中的一种用于执行码字的数据纠错的方法,所述的块包括出错位组生成块(410)、错误多项式块(420)、错误位置块(430)、和错误大小块(440),所述方法包括以下步骤:

在所述出错位组生成块(410)中从所述码字计算出错位组;

在所述错误多项式块(420)中从所述出错位组生成错误多项式;

在所述错误位置块(430)中从所述错误多项式确定错误位置;以及

在所述错误大小块(440)中从所述错误多项式计算错误大小,

所述方法的特征在于,所述至少四个块中的至少一个块适合于把不活动消息(640,650)发送到所述至少四个块中的另外的块。

2.权利要求1的方法,还包括以下步骤:

根据所述错误位置和所述错误大小校正所述码字。

3.权利要求1的方法,其中所述不活动消息是一个准备好接收的消息(640)。

4.权利要求1的方法,其中所述不活动消息是一个准备好发送的消息(650)。

5.权利要求1的方法,其中所述错误多项式块是欧几里得算法块。

6.权利要求1的方法,其中所述错误多项式块是Berlekamp-Massey算法块。

7.权利要求1的方法,其中所述错误位置块是Chien搜索块。

8.权利要求1的方法,其中所述错误大小块是Forney算法块。

9.权利要求1的方法,其中与所述错误位置块和所述错误大小块相关联的动作是在组合的Chien/Forney块内执行的。

10.权利要求1的方法,其中所述循环线性块码纠错译码器是里德-所罗门译码器。

11.一种用于在码字内执行数据检错的译码器,所述译码器包括:

用于从所述码字计算出错位组的装置(410);

用于从所述出错位组生成错误多项式的装置(420);

用于从所述错误多项式确定错误位置的装置(430);以及

用于从所述错误多项式计算错误大小的装置(440),

所述译码器的特征在于,为了发送译码器内的不活动消息(640,650)而作的适配是包含在由下述一组部件中选出的至少一个部件中的,该组包括:用于计算所述出错位组的装置(410)、所述用于生成所述错误多项式的装置(420)、所述用于确定所述错误位置的装置(430)、和所述用于计算所述错误大小的装置(440)。

12.权利要求11的译码器,还包括用于响应于作为输入而接收所述码字、所述错误位置、和所述错误大小来校正所述码字的装置(450)。

13.权利要求11的译码器,其中所述译码器是里德-所罗门译码器。

14.权利要求11的译码器,其中所述译码器内的不活动消息是一个准备好接收的消息(640)。

15.权利要求11的译码器,其中所述译码器内的不活动消息是一个准备好发送的消息(650)。

16.权利要求11的译码器,其中所述生成错误多项式块的装置(420)是欧几里得算法块。

17.权利要求11的译码器,其中所述生成错误位置块的装置(430)是Chien搜索块。

18.权利要求11的译码器,其中所述计算错误大小的装置(440)是Forney算法块。

19.一种用于在码字内执行数据检错的译码器,所述译码器包括:

出错位组生成器(410),用于从所述码字计算出错位组;

错误多项式生成器(420),用于从所述出错位组生成错误多项式;

错误位置生成器(430),用于从所述错误多项式确定错误位置;以及

错误大小生成器(440),用于从所述错误多项式计算错误大小,

所述译码器的特征在于,为了发送译码器内不活动消息(640,650)而作的适配是包含在由下述一组部件中选出的至少一个部件中的,该组包括:所述出错位组生成器(410)、所述错误多项式生成器(420)、所述错误位置生成器(430)、和所述错误大小生成器(440)。

20.权利要求19的译码器,还包括纠错码字发生器(450),用于响应于作为输入而接收所述码字、所述错误位置、和所述错误大小来校正所述码字。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/055,114 US7020826B2 (en) | 2002-01-23 | 2002-01-23 | Intra-decoder component block messaging |

| US10/055,114 | 2002-01-23 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN1757165A true CN1757165A (zh) | 2006-04-05 |

Family

ID=21995704

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNA038026554A Pending CN1757165A (zh) | 2002-01-23 | 2003-01-22 | 译码器内的部件块消息传送 |

Country Status (9)

| Country | Link |

|---|---|

| US (1) | US7020826B2 (zh) |

| EP (1) | EP1468499A4 (zh) |

| JP (1) | JP2005516458A (zh) |

| KR (1) | KR20040075952A (zh) |

| CN (1) | CN1757165A (zh) |

| BR (1) | BR0302820A (zh) |

| MX (1) | MXPA04007076A (zh) |

| MY (1) | MY132105A (zh) |

| WO (1) | WO2003063363A1 (zh) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103444114A (zh) * | 2011-02-04 | 2013-12-11 | 马维尔国际贸易有限公司 | 用于wlan的控制模式phy |

| CN108886369A (zh) * | 2016-02-26 | 2018-11-23 | 阿尔特拉公司 | 用于执行里德-所罗门编码的方法和装置 |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7225391B1 (en) * | 2002-12-17 | 2007-05-29 | Altera Corporation | Method and apparatus for parallel computation of linear block codes |

| KR100906474B1 (ko) * | 2003-01-29 | 2009-07-08 | 삼성전자주식회사 | 저밀도 부가정보 발생용 매트릭스를 이용한 에러 정정방법 및그 장치 |

| US7206993B2 (en) * | 2003-03-12 | 2007-04-17 | Matsushita Electric Industrial Co., Ltd. | Method and device for decoding Reed-Solomon code or extended Reed-Solomon code |

| US7693928B2 (en) * | 2003-04-08 | 2010-04-06 | Analog Devices, Inc. | Galois field linear transformer trellis system |

| FR2861474B1 (fr) * | 2003-10-24 | 2007-04-27 | Atmel Corp | Procede et appareil pour une periode de traitement variable dans un circuit integre |

| US7581155B2 (en) * | 2003-12-18 | 2009-08-25 | Electronics And Telecommunications Research Institute | Apparatus for FEC supporting transmission of variable-length frames in TDMA system and method of using the same |

| US8161207B1 (en) | 2006-06-22 | 2012-04-17 | Marvell International Ltd. | Common block interface for data and control with handshake protocol |

| US8312345B1 (en) * | 2006-09-29 | 2012-11-13 | Marvell International Ltd. | Forward error correcting code encoder apparatus |

| US20080140740A1 (en) * | 2006-12-08 | 2008-06-12 | Agere Systems Inc. | Systems and methods for processing data sets in parallel |

| JP4313391B2 (ja) * | 2006-12-13 | 2009-08-12 | 株式会社日立コミュニケーションテクノロジー | 光集線装置および光加入者装置 |

| US8223628B2 (en) * | 2007-01-10 | 2012-07-17 | Lantiq Deutschland Gmbh | Data transmission method, transmitter, receiver, transceiver and transmission system |

| US9686045B2 (en) * | 2007-04-04 | 2017-06-20 | Lantiq Beteiligungs-GmbH & Co. KG | Data transmission and retransmission |

| JP4672743B2 (ja) * | 2008-03-01 | 2011-04-20 | 株式会社東芝 | 誤り訂正装置および誤り訂正方法 |

| KR101489827B1 (ko) * | 2008-03-25 | 2015-02-04 | 삼성전자주식회사 | 낸드 플래시 메모리와 컨트롤러 간의 효율적인 프로토콜을사용하는 반도체 메모리 장치 |

| JP4780158B2 (ja) * | 2008-08-26 | 2011-09-28 | ソニー株式会社 | 符号化装置および方法 |

| JP4823349B2 (ja) | 2009-11-11 | 2011-11-24 | パナソニック株式会社 | 三次元映像復号装置及び三次元映像復号方法 |

| KR101154923B1 (ko) * | 2010-12-09 | 2012-06-14 | 한국과학기술원 | 비씨에이치 디코더, 이를 포함하는 메모리 시스템 및 비씨에이치 디코딩 방법 |

| US8924828B2 (en) * | 2012-08-30 | 2014-12-30 | Kabushiki Kaisha Toshiba | Memory controller, semiconductor storage device, and memory control method for error correction using Chien search |

| TWI500038B (zh) * | 2012-09-28 | 2015-09-11 | Univ Nat Chiao Tung | 記憶體系統之全套平行編碼方法與全套平行解碼方法 |

| CN105024707B (zh) * | 2015-07-31 | 2018-05-11 | 福建联迪商用设备有限公司 | 一种rs纠错解码方法 |

| US11750222B1 (en) * | 2022-06-29 | 2023-09-05 | Synopsys, Inc. | Throughput efficient Reed-Solomon forward error correction decoding |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4875211A (en) * | 1986-12-10 | 1989-10-17 | Matsushita Electric Industrial Co., Ltd. | Galois field arithmetic logic unit |

| US5099482A (en) * | 1989-08-30 | 1992-03-24 | Idaho Research Foundation, Inc. | Apparatus for detecting uncorrectable error patterns when using Euclid's algorithm to decode Reed-Solomon (BCH) codes |

| JPH04315332A (ja) | 1991-04-15 | 1992-11-06 | Hitachi Ltd | 誤り訂正装置 |

| US5373511A (en) * | 1992-05-04 | 1994-12-13 | Motorola, Inc. | Method for decoding a reed solomon encoded signal with inner code and apparatus for doing same |

| JP3255386B2 (ja) | 1993-12-27 | 2002-02-12 | キヤノン株式会社 | 誤り訂正符号の復号器 |

| JP3328093B2 (ja) * | 1994-07-12 | 2002-09-24 | 三菱電機株式会社 | エラー訂正装置 |

| JP3310185B2 (ja) * | 1996-11-21 | 2002-07-29 | 松下電器産業株式会社 | 誤り訂正装置 |

| US5905740A (en) * | 1997-04-08 | 1999-05-18 | Seagate Technology, Inc. | Apparatus and method for error correction |

| JP3850511B2 (ja) * | 1997-05-07 | 2006-11-29 | 日本テキサス・インスツルメンツ株式会社 | リードソロモン復号装置 |

| JPH1131977A (ja) * | 1997-07-10 | 1999-02-02 | Sony Corp | 誤り訂正符号演算器 |

| US6154868A (en) * | 1997-07-18 | 2000-11-28 | International Business Machines Corporation | Method and means for computationally efficient on-the-fly error correction in linear cyclic codes using ultra-fast error location |

| US6061826A (en) * | 1997-07-29 | 2000-05-09 | Philips Electronics North America Corp. | Hardware-optimized reed-solomon decoder for large data blocks |

| US6058500A (en) * | 1998-01-20 | 2000-05-02 | 3Com Corporation | High-speed syndrome calculation |

| US6415413B1 (en) * | 1998-06-18 | 2002-07-02 | Globespanvirata, Inc. | Configurable Reed-Solomon controller and method |

| US6347389B1 (en) * | 1999-03-23 | 2002-02-12 | Storage Technology Corporation | Pipelined high speed reed-solomon error/erasure decoder |

| US6374383B1 (en) * | 1999-06-07 | 2002-04-16 | Maxtor Corporation | Determining error locations using error correction codes |

| US6487692B1 (en) * | 1999-12-21 | 2002-11-26 | Lsi Logic Corporation | Reed-Solomon decoder |

| US6735737B2 (en) * | 2000-02-18 | 2004-05-11 | Texas Instruments Incorporated | Error correction structures and methods |

-

2002

- 2002-01-23 US US10/055,114 patent/US7020826B2/en not_active Expired - Fee Related

-

2003

- 2003-01-22 WO PCT/US2003/001913 patent/WO2003063363A1/en active Application Filing

- 2003-01-22 BR BR0302820-8A patent/BR0302820A/pt not_active IP Right Cessation

- 2003-01-22 EP EP03732044A patent/EP1468499A4/en not_active Withdrawn

- 2003-01-22 CN CNA038026554A patent/CN1757165A/zh active Pending

- 2003-01-22 MY MYPI20030217A patent/MY132105A/en unknown

- 2003-01-22 MX MXPA04007076A patent/MXPA04007076A/es active IP Right Grant

- 2003-01-22 JP JP2003563105A patent/JP2005516458A/ja not_active Withdrawn

- 2003-01-22 KR KR10-2004-7011352A patent/KR20040075952A/ko not_active Application Discontinuation

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103444114A (zh) * | 2011-02-04 | 2013-12-11 | 马维尔国际贸易有限公司 | 用于wlan的控制模式phy |

| CN103444114B (zh) * | 2011-02-04 | 2017-07-14 | 马维尔国际贸易有限公司 | 用于wlan的控制模式phy |

| CN108886369A (zh) * | 2016-02-26 | 2018-11-23 | 阿尔特拉公司 | 用于执行里德-所罗门编码的方法和装置 |

| CN108886369B (zh) * | 2016-02-26 | 2022-11-08 | 阿尔特拉公司 | 用于执行里德-所罗门编码的方法和装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1468499A4 (en) | 2005-12-14 |

| MY132105A (en) | 2007-09-28 |

| EP1468499A1 (en) | 2004-10-20 |

| WO2003063363A1 (en) | 2003-07-31 |

| KR20040075952A (ko) | 2004-08-30 |

| JP2005516458A (ja) | 2005-06-02 |

| MXPA04007076A (es) | 2004-10-29 |

| US20030140301A1 (en) | 2003-07-24 |

| BR0302820A (pt) | 2004-03-09 |

| US7020826B2 (en) | 2006-03-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1623280A (zh) | 纠错译码器中的双chien搜索块 | |

| CN1757165A (zh) | 译码器内的部件块消息传送 | |

| US11201695B2 (en) | Forward error correction with compression coding | |

| JP5329239B2 (ja) | 通信システムのための多体ベース符号の生成器および復号化器 | |

| JP2009171540A (ja) | 送信装置および方法、受信装置および方法、並びにプログラム | |

| CN1198422C (zh) | 检测带逆序校验位的循环冗余校验码中的错误的装置和方法 | |

| CN1146116C (zh) | 截短法尔码的差错捕获译码方法和装置 | |

| CN1636324A (zh) | 纠错解码器的钱搜索单元 | |

| KR100192795B1 (ko) | 리드 솔로몬 복호기의 에러 위치 다항식 계산 장치 | |

| Naik et al. | A NOVEL DESIGN AND SIMULATION OF CYCLIC REDUNDANCY CHECK ENCODER AND DECODER |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |