CN1282060C - 将时钟信号用于移动用户台的处理器以管理功耗的方法和设备 - Google Patents

将时钟信号用于移动用户台的处理器以管理功耗的方法和设备 Download PDFInfo

- Publication number

- CN1282060C CN1282060C CNB018226752A CN01822675A CN1282060C CN 1282060 C CN1282060 C CN 1282060C CN B018226752 A CNB018226752 A CN B018226752A CN 01822675 A CN01822675 A CN 01822675A CN 1282060 C CN1282060 C CN 1282060C

- Authority

- CN

- China

- Prior art keywords

- processor

- clock signal

- clock

- power

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000000034 method Methods 0.000 title claims abstract description 34

- 230000002093 peripheral effect Effects 0.000 claims abstract description 41

- 238000010438 heat treatment Methods 0.000 claims description 11

- 230000005055 memory storage Effects 0.000 claims description 8

- 230000004044 response Effects 0.000 claims description 8

- 238000001514 detection method Methods 0.000 claims 3

- 230000001360 synchronised effect Effects 0.000 abstract description 10

- 238000005516 engineering process Methods 0.000 abstract description 7

- 230000005611 electricity Effects 0.000 description 11

- 230000006870 function Effects 0.000 description 11

- 230000006399 behavior Effects 0.000 description 9

- 238000006243 chemical reaction Methods 0.000 description 9

- 238000010586 diagram Methods 0.000 description 8

- 230000000630 rising effect Effects 0.000 description 8

- 230000000712 assembly Effects 0.000 description 3

- 238000000429 assembly Methods 0.000 description 3

- 230000014509 gene expression Effects 0.000 description 3

- 238000011084 recovery Methods 0.000 description 3

- 206010000117 Abnormal behaviour Diseases 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 230000009466 transformation Effects 0.000 description 2

- LHMQDVIHBXWNII-UHFFFAOYSA-N 3-amino-4-methoxy-n-phenylbenzamide Chemical compound C1=C(N)C(OC)=CC=C1C(=O)NC1=CC=CC=C1 LHMQDVIHBXWNII-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 230000036755 cellular response Effects 0.000 description 1

- 230000009849 deactivation Effects 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000003708 edge detection Methods 0.000 description 1

- 230000008676 import Effects 0.000 description 1

- 230000001788 irregular Effects 0.000 description 1

- 230000002035 prolonged effect Effects 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

- 238000000638 solvent extraction Methods 0.000 description 1

- GOLXNESZZPUPJE-UHFFFAOYSA-N spiromesifen Chemical compound CC1=CC(C)=CC(C)=C1C(C(O1)=O)=C(OC(=O)CC(C)(C)C)C11CCCC1 GOLXNESZZPUPJE-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3867—Concurrent instruction execution, e.g. pipeline or look ahead using instruction pipelines

- G06F9/3869—Implementation aspects, e.g. pipeline latches; pipeline synchronisation and clocking

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/08—Clock generators with changeable or programmable clock frequency

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/10—Distribution of clock signals, e.g. skew

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3206—Monitoring of events, devices or parameters that trigger a change in power modality

- G06F1/3228—Monitoring task completion, e.g. by use of idle timers, stop commands or wait commands

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/3237—Power saving characterised by the action undertaken by disabling clock generation or distribution

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30076—Arrangements for executing specific machine instructions to perform miscellaneous control operations, e.g. NOP

- G06F9/30083—Power or thermal control instructions

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D30/00—Reducing energy consumption in communication networks

- Y02D30/50—Reducing energy consumption in communication networks in wire-line communication networks, e.g. low power modes or reduced link rate

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Software Systems (AREA)

- Microcomputers (AREA)

- Mobile Radio Communication Systems (AREA)

- Power Sources (AREA)

Abstract

提供了将时钟信号应用于诸如蜂窝电话的移动用户台内所用的流水线精简指令集计算(RISC)处理器的技术。本文所提供的专门技术适当于通过确保断电前处理器当前流水线各级的完成,在提供处理器和外围组件之间同步的同时,使RISC处理器断电。在避免由RISC处理器内不可预测的性能所产生的同步伪信号时,使用其它专门技术来实现在同步或异步时钟信号间转换。描述所述技术的方法和设备的实施例。

Description

发明背景

发明领域

本发明主要涉及移动用户台,诸如移动电话,尤其涉及将时钟信号应用于移动台的处理器以减少功耗同时避免时序问题的方法和设备。

相关技术描述

移动用户台,诸如蜂窝电话,正变得越来越精致并常常在提供常规的蜂窝语音电话能力的同时还提供许多功能。一些先进的移动台可收发寻呼消息、提供因特网接入或提供诸如记事和日程功能之类的个人数字助理(PDA)功能。为适应附加功能,移动台装配功能强大和精致的处理器及越来越多的数据存储存储器。由此,移动台的功耗很大,需频繁充电。因此,需要降低移动台的功耗。

降低移动台的功耗的一种技术是,根据组件的当前需求有选择地将具有不同频率的各种时钟信号应用于不同的移动台组件。时钟信号由不同的时钟源提供,因而通常彼此不同步。不同的时钟源功耗不同且提供不同精确度的时钟信号。对移动台的每个内部组件和每个工作模式而言,移动台的时钟控制组件选择适用该组件的最好的时钟信号以在提供足够的时钟速度和精度的同时功耗最小。例如,当移动台不工作时,可选择使用来自较低功率、低频率时钟源的慢时钟以运行跟踪日期和时间所需的组件。当移动台工作时,选择较高频率且较精确时钟信号用于移动台的处理器和其他主要组件。在需要最佳性能的时间段,诸如在电话交谈期间,可以使用更高频率的时钟信号。总言之,每当不需要时钟源输出所对应的时钟信号时,较佳地关掉各种时钟信号的各个时钟源。

为更省电,有选择地再频分各个异步时钟信号的频率以提供功耗更小的各种较慢版本的时钟信号。例如,可以将来自单个源的单个时钟信号分频提供彼此同步且不同频率的一组不同时钟信号。为此,按因数2、4、8、16等或按不是2的幂的其他除数分频单个时钟信号。照此,时钟控制电路配备更大的可用时钟信号集,从中可选择出适用于每个组件和每个工作模式的最好时钟信号以降低功耗。

另一降低功耗的技术是,当处理器不需要工作时,完全使移动台的处理器不工作,即使另外移动台工作着。为此,传统移动台通常使用具有上电和掉电能力的内部电源管理电路的复杂指令集计算(CISC)处理器。为省电,处理器启动关电程序,其中,处理器执行各种用来存储表示处理器最终状态的信息的功能。一旦完成各种功能,将时钟信号从处理器断开而关掉处理器。然后提供处理器的电源也不工作。当再需要处理器工作时,执行上电程序,其中处理器执行用来将处理器重新设置为其关闭前状态的各种功能。通常,在处理器再次进入完全工作前需要加温时段。

不幸的是,在实现功率节省之前,处理器常需花费大量时钟周期来完成掉电程序。处理器在进入工作之前也要花费相当长的时间来完成上电程序,因而,要求远在真正需要其服务程序之前重新使处理器工作。因此,未实现最佳的省电。而且,在根据码分多址(CDMA)协议实现的移动台中,处理器需在周期性寻呼时隙(通常每隔26.7毫秒出现)期间工作。若如此,处理器只能在寻呼时隙间的时段期间不工作。为在每一对连续寻呼时隙间不工作,处理器首先要在每个寻呼时隙后执行掉电程序,然后在每个后续寻呼时隙之前执行上电程序。因此,实际关掉处理器的寻呼时隙间的可用时间是最少的,导致节电不充分。

提出的一种解决方案是,使用精简指令集计算(RISC)处理器(仅通过选择性地连接或去连接时钟信号与处理器来对处理器上电或掉电)工作于移动台。换言之,使用不需要潜在长的上电和掉电程序的处理器。这类RISC处理器的一例是ARM公司提供的ARM7TDMI。有采用这类处理器,可实现增强的节电,因为对处理器上电或掉电快得多,从而可延长使处理器不工作的时间。这对CDMA移动台(在使用期间只能在寻呼时隙间使处理器不工作)尤其有益。

尽管这类RISC处理器很适于实现改进的节电,但当处理器安装于一些移动台中时就会出现问题,特别是移动台使用一组通常彼此异步并能有选择地再频的不同时钟信号。例如,如果在时钟信号的有效阶段期间将时钟信号从处理器分开就会出现问题。在此情况下,处理器只接收时钟信号的有效阶段中的毛刺部分,这会使没有足够的长度来允许处理器的各个内部组件正常工作,尤其是取样保持电路。结果,处理器执行出错或不能预知的功能,有可能导致引起掉话、丢失寻呼消息等的故障。在掉电期间保持处理器的状态也是重要的。否则,时钟的伪信号会使处理器进入出错状态。

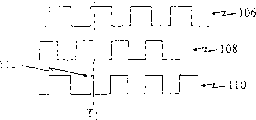

图1示出在有效阶段期间的时间T1断开的时钟信号100。可以看出,产生了有效阶段中的毛刺102。因为该毛刺在持续时间上比所有其他有效阶段的信号成份短得多,该毛刺会导致前述处理器出现故障。事实上,作为电子信号处理效应的结果,处理器的内部组件实际上可视为一种波形,其中时钟的毛刺可作为振荡、衰变信号峰值序列出现。根据处理器电路,每个一单个体峰值可理解为极有可能导致处理器故障的一个新的有效阶段信号。本文将短的有效阶段时钟信号的毛刺称之为时钟的“伪信号”。

相同地,输入到处理器的时钟信号不能简单地从一异步信号切换到第二异步信号而不具出故障的可能性,因为它会在掉电之前和之后干扰处理器所保留的状态,也不能仅仅对时钟信号分频以产生较慢时钟信号而无出故障的潜在性。图2示出输入到处理器的时钟信号在异步时钟信号间切换的情况。可以看出,时钟信号106在时间T1切换到异步时钟信号108时,处理器实际输入的时钟波形110可以包括也可能引起时钟伪信号的非有效阶段段的毛刺112。图3示出分频时钟信号以产生较低频率的同步时钟信号的情况。可以看出,在时间T1再分频时钟信号114以产生有两倍频率的第二时钟信号116导致处理器实际输入的波形118具有时钟伪信号120。

此外,一些先进的RISC处理器,包括前述ARM7TDMI处理器,是能同时处理多条指令的流水线处理器。在ARM7TDMI处理器的情况下,处理器能在在输入第一条指令的同时解码第二条指令和执行第三条指令。当处理器在执行流水线操作时,如果应用于处理器的时钟信号不工作、切换或划分,都会出现问题,因为处理器的随后状态不容易得到保证。换言之,如果在指令执行期间时钟信号随意不工作、切换或划分,则外围组件难于或不可能判断在掉电前指令是否得到完全执行。结果,连接处理器的外围组件与处理器不同步,导致不能预测的或出错的行为,还有可能导致诸如掉话、丢失寻呼消息等之类的故障。图4示出三级流水线122和相对应定的时钟信号124。指令A于第一时钟周期输入、在第二时钟周期得到解码并在第三时钟周期得到执行。指令B于第二时钟周期输入、在第三时钟周期得到解码并在第四时钟周期得到执行,以此类推。如果在时间T1使时钟信号不工作,此时正在进行输入、解码和执行的指令可以已经完成或可以尚未完成。结果,当随后再通过应用时钟信号重新使处理器工作时,连接处理器的外围组件,诸如系统总线等,不容易判断出处理器的重新工作的状态。因而,或者需要执行更长的程序来判断处理器状态并使所有的外围组件与之同步,或者出现有故障这样一相当大的冒险。对使用PDA功能的移动台,所产生的故障会引起日程功能等使用的存储单元中错误存储不正确信息。呈现给用户的是不正确信息,可能导致错过约会等等。

因此,非常需要提供一种控制将时钟信号应用于移动台内的处理器的方法和设备,其中处理器是不包括内部功率管理和时钟管理电路且只需断开输入的时钟信号便允许不工作的类型。尤其是,需要提供适用于这类处理器掉电及后续上电同时即避免时钟伪信号又能确保处理器与外围组件的可靠同步的方法和设备。

发明内容

根据本发明的第一方面,提供一种通过使用外围电路将时钟信号从处理器断开而使移动台的处理器不工作的方法。处理器执行将处理器的外部预定设备置于预定状态中的指令。所述指令只施加于外部设备,作为掉电操作的一部分。外围电路检测置于预定状态的外部设备,并且,作为响应,在处理器的当前流水线阶段期间所执行的操作完成后而在处理器的后续流水线阶段的操作启动前,将时钟信号从处理器断开。

在一示例实施例中,处理器是没有内部时钟管理电路的流水线RISC处理器。由处理器执行用来启动掉电操作的指令是存储外围电路内的一独特寄存器的指令。该存储指令在存储寄存器中首先存储一二进制1再存储一二进制0。外围电路监视存储寄存器以检测1后跟0的存储并开始将时钟信号从处理器分离。当时钟信号在低或非活动状态中且在当前流水线阶段执行的指令完成后而在启动后续的流水线阶段的指令前断开时钟信号。通过只响应1后跟0的存储的检测器使处理器不工作,基本上降低无意使处理器不工作的风险。通过在时钟的有效阶段将时钟从处理器分开,可以确认,处理器未接收可能导致引起处理器中潜在不可预知行为的时钟伪信号的时钟信号的有效阶段中的毛刺。通过只在当前流水线阶段执行的指令完成后而在启动后续的流水线阶段的指令前才断开时钟,外围电路和处理器的所有其他外部组件都能确定掉电时系统的最终状态。相反,假如关闭信号是在处理器的流水线阶段的指令执行期间不工作的,则外部组件就不容易判断该流水线阶段的操作是否完成并因此不能容易判断掉电时处理器的状态。如有必要,在当前流水线阶段期间对处理器断言一等待信号,以扩展流水线来提供完成流水线级操作的时间。断言等待信号直到时钟信号已进入非有效阶段且时钟信号在非有效阶段被分开。

根据本发明的另一方面,提供一种使用也接收时钟信号的外围电路在用于流水线处理器的同步时钟信号间切换的方法。当第一时钟信号在非有效阶段时推迟连接第一时钟信号与处理器。然后,选择与第一时钟信号相关同步的第二时钟信号。外围组件等到第二时钟信号也在非有效阶段时将第二时钟信号用于处理器。

在一示例实施例中,处理器也是没有内部时钟管理电路的流水线RISC处理器。外围电路包括有选择地用诸如2、4、8、16、32或64之类的整数因数分频时钟信号的组件。处理器和外围电路用于时钟信号分频的移动台内,以使时钟信号在降低功耗的同时还能提供足够处理速度的最佳频率。通过只在信号于非有效阶段时才分频时钟信号及只在所分频的时钟信号于非有效阶段时将所分频的时钟信号用于处理器,防止时钟伪信号且避免不可预测的处理器行为。

根据本发明的另一方面,提供一种在用于移动台流水线处理器的从第一时钟信号向第二时钟信号(彼此异步)切换的时钟信号切换方法。所述方法由连接处理器的外围电路执行。根据该方法,当处理器接收第一时钟信号时,通过控制处理器执行将处理器的外部预定设备置于预定状态中的指令启动掉电操作,所述指令用于外部设备只是掉电操作的一部分。接着,

外围电路检测置于预定状态的外部设备,并且,作为响应,等到当前流水线阶段的指令完成后时钟信号转换到非有效阶段。外围电路在后续流水线阶段的指令启动前将时钟信号从处理器断开。然后,控制外围电路等到第二时钟信号在非有效阶段,外围电路将第二时钟信号用于处理器。

当时钟信号在非有效阶段时通过推迟第一时钟信号及在非有效阶段时通过应用第二时钟信号,可避免时钟伪信号。通过只在处理器的流水线级间切换时钟信号,确保在切换时钟信号之前及执行后续流水线级之前当前流水线阶段的操作全部完成,从而可避免处理器的不可预测的行为。如有必要,向处理器断言等待信号,以扩展当前流水线阶段,扩展量足以保证在将第一时钟信号从处理器断开之前完成流水线阶段的全部操作。

这样,本发明提供于管理用于移动台处理器(尤其是缺少内部时钟管理电路的处理器)的时钟信号的各种技术,以在基本防止不可预测的处理器行为(否则会出现时钟伪信号等导致的结果)的同时允许最佳的省电。还提供本发明的设备实施例。本发明的其他目的、特点和优点在下面结合附图的详述中变得明显。

附图简述

图1是说明由在时钟信号的有效阶段期间使时钟信号不工作能引起的时钟伪信号的时序图。

图2是说明在从一时钟信号向第二异步时钟信号切换期间出现的时种伪信号的时序图。

图3是说明在时钟信号向第二同步时钟信号分频时出现的时钟伪信号的时序图。

图4是说明流水线处理器的级并进一步说明在一流水线级期间将时钟信号从处理器断开的时序图。

图5是说明根据本发明的一示例实施例所构成的具有流水线RISC处理器和时钟/功率控制器的移动台的相关组件的框图。

图6是说明图5的时钟/功率控制器的相关组件的框图。

图7是说明扩展图5的RISC处理器的流水线级以允许处理器掉电而不失去与外围组件的同步的方法的时序图。

图8是说明采用图5的时钟/功率控制器在基本上保证无伪信号操作的同时在同步时钟信号间切换的方法的时序图。

图9是说明图5的时钟/功率控制器在保证无伪信号操作的同时在异步时钟信号间切换的方法的时序图。

图10A-C是说明图6的时钟/功率控制器的特殊实现的电路示意图。

图11是说明结合图10A-C的电路使用的特定信号用于同步时钟信号间切换的时序图。

图12是说明结合图10A-C的电路使用的特定信号用于掉电和后续上电的时序图。

图13是说明结合图10A-C的电路使用的特定信号复位后的时序图。

示例实施例详述

参考余图,现描述本发明的较佳和示例实施例。实施例涉及无线移动台,诸如蜂窝电话,但发明原理也适用其他系统。

图5说明CDMA无线系统的移动台200的相关组件。移动台包括RISC处理器(在其中,仅将时钟信号用于处理器便上电,而仅将时钟信号从微处理器分开便掉电)。在较佳实施中,RISC处理器包括ARM公司的ARM7TDMI核心及AMBA总线主线。处理器202通过系统总线204连接时钟/功率控制器206、存储器映射解码器208、总线尺寸控制器210、外部存储器子系统212、复位和暂停单元214及外围桥芯216。外围桥芯216通过外围总线2 18提供对包括CDMA电路220、声码器222、数字频率调制器(DFM)224、通用同步收发单元(UART)226和系统总线接口(SBI)228的接入。其它组件互连包括图5所示的专用存储器总线230和各种其它专用互连线。

简言之,时钟/功率控制器206包括用来控制用于处理器202的时钟信号以在保持处理器与外围组件的同步的同时允许处理器的掉电和随后的上电。另外,时钟/功率控制器包括在异步时钟信号(单个时钟信号的分频版本)间切换以在保证无伪信号操作的同时节电的组件。而且,时钟/功率控制器包括在异步时钟信号间切换以在保证无伪信号操作的同时进一步节电的组件。

图6示出时钟/功率控制器206的相关组件和RISC处理器。时钟/功率控制器206包括一组时钟发生器2321-232N(各自提供通常彼此异步的时钟信号)。各种时钟信号具有不同的频率、不同的精确度,且通常在工作期间功耗也不同。时钟控制单元234选择一时钟信号用于RISC处理器。选择该时钟信号以提供足够的时钟速度和精度来适应处理器的当前需要。运行于处理器中的软件确定合适的时钟信号。从处理器向时钟控制单元(经未特别示出的控制信号线)发送控制信号以触发从一异步时钟信号向另一信号的切换。(保证无伪信号工作的同时切换时钟信号的方法在下文有详述。)如果处理器未工作,时钟控制单元根据掉电前从处理器接收的控制信号或根据默认值工作。所选时钟信号从时钟控制单元234经时钟分频单元236(分频所选时钟信号)传输,并且在处理器202的控制下,来提供与所选时钟信号同步的较慢时钟信号。可按因数2、4、8、16、32和64来分频任一由时钟发生器所发生的时钟信号。也可选地使用不一定是2的幂的其他分子。照此,有一大组时钟速率、精确度和功耗各异的时钟信号可用于处理器及移动台的各种其他组件。对于时钟控制单元而言,时钟分频单元响应处理器所提供(经未特别示出的控制信号线)的控制信号或使用默认值。如下文还要详述,时钟分频单元236根据确保用于处理器的信号无伪信号转换的方式将时钟信号切换到该时钟信号的分割版本。

时钟/功率控制器206还包括掉电控制器238,该控制器通过使用开关237选通时钟分频单元输出的时钟信号来实现对RISC处理器掉电。由微处理器202的时钟输入端接收开关237的时钟信号输出。其次,与时钟/功率控制器的其它组件一样,掉电控制器工作以避免时钟伪信号。掉电控制器还工作以确保能知道RISC处理器的最终掉电状态,使得一旦有后续上电,外围组件能与处理器保持适当的同步。作为组件之一,掉电控制器包括用来检测何时启动掉电操作的掉电内存寄存器240。

现参考图6及图7的时序图较详细地描述执行掉电操作的方法。掉电操作由RISC处理器启动,它向掉电内存寄存器240执行一对预定承载操作。寄存器只存放一个比特且起先设定为二进制0。在预定承载操作中,处理器首先向掉电内存寄存器写入一二进制1,然后写入一二进制0。掉电控制器238监视掉电内存寄存器,并且,如果检测到从二进制1到0的转变,控制器开始将时钟信号从处理器断开的操作。

定义掉电内存寄存器的专门地址是处理器只在掉电操作期间接入和在任何其它期间不能接入的独特地址。由此,读写处于外部存储器子系统内的存储位置的程序(图5)不影响掉电内存寄存器240的内容及掉电内存寄存器内从0到1的转变,从而提供已由处理器启动掉电操作的可靠表示。然而,为保证软件差错或其它异常不会触发不受欢迎的掉电操作,处理器执行将掉电内存寄存器切换回0的第二承载操作。如上所述,掉电控制器只响应掉电内存寄存器内承载1之后承载0。因此,特别不可能的是,处理器或移动台的其它组件的软件差错或其他异常行为不注意地触发不受欢迎的掉电操作。

一旦检测到掉电内存寄存器240内承载1之后承载0,掉电控制器238执行将时钟分频单元236输出的时钟信号从微处理器202分开的掉电操作。当时钟信号在预期的处理器的当前流水线阶段完成之后的低或非有效阶段时,执行时钟信号的断开。通过在低阶段断开时钟信号,避免时钟伪信号。为保证完成与当前流水线阶段相关的所有操作,掉电控制器238在断开时钟信号以扩展当前流水线级的一另外时钟周期之前,向处理器提供一等待信号。照此,处理器的当前状态设定为已知状态。假如只在流水线级期间的任意时间使时钟信号不工作,则可完成或可以未完成相应指令。结果,预期处理器已在时钟信号重新工作之前完成了操作的外围组件,此后就与微处理器不再同步。可以理解的是,断开时钟信号的精确时间及流水线阶段的扩展的精确量取决于系统的特定特点,因而根据本发明的一般原理因系统而各异。

图7说明了扩展图5的RISC处理器的流水线级以允许处理器掉电而不失去与外围组件的同步的方法。更具体地,图7说明当前时钟信号242、处理器接收的时钟信号243及处理器的流水线244。于时间T1提供等待信号以将下一流水线级延迟到时间T3以保证完成流水线阶段248内的所有操作。照此,等待信号扩展当前流水线级。在时间T1和T3之间的时间T2断开时钟信号242。然后,微处理器接收时钟信号243(时间T2之后起初为低)。

参考图8,现描述图6的时钟控制单元234控制时钟信号分频的方法。起初,将每秒N周期的定时频率的时钟信号250施加至处理器。为切换到有频率为N/2的第二时钟信号252,时钟控制单元首先在时间T1和T3间将时钟信号250从RISC处理器选通或断开,然后于时间T2的起始阶段切换到时钟信号252。最终输入RISC处理器的时钟信号由时钟信号254表示。可以看出,输入到处理器的时钟信号至少在时间T1和T3间保持为低或非有效。通过在低阶段期间断开第一时钟信号并还在低阶段期间施加第二分频时钟信号,确保无伪信号的操作。或者,第二时钟信号快于第一时钟信号。在任一情况下,假如第一和第二时钟信号间的转换出现于任意时间,可能会出现时钟伪信号,从而导致处理器的异常或不可预测的行为。

现在参考图9,现描述时钟控制单元234在异步时钟信号之间切换的方法。起初,时钟信号260施加于处理器。为节电或其他原因,时钟控制单元尽力切换到第二异步时钟信号262。时钟信号264是真正输入处理器的时钟信号。转换是通过首先控制处理器下载一1及一0到掉电内存寄存器240中而启动掉电操作(图6)来完成的。掉电指令起初输入于266、解码于268然后执行于270。同上述掉电操作一样,在时间T1将等待信号施加于处理器以扩展处理器的流水线级272到T3。于时间T1将时钟信号260从处理器断开。微处理器关闭至时间T3。经过了在T1和T3间任意数目的时钟260和262的时钟周期。注意,在流水线阶段272内,微处理器在时钟信号264的第一完全时钟周期期间完成输入、解码和执行指令,然后保持非有效至T3。当于时间T3将时钟信号262施加于处理器时,执行上电操作。处理器的流水线使用新的输入时钟信号开始再次运行。

照此,实现从时钟信号260到异步时钟信号262的转换,同时避免任何时种伪信号并保证处理器的流水线的可靠运行。假如在两异步时钟信号间进行任意转换,时钟伪信号会引起处理器的异常或不可预知的行为。而且,异步时钟信号间的切换可导致当前流水线级期间执行的操作可能完成或可能未完成的情况。还是在此情形下,执行完全的关闭程序,后跟上电程序,以保证时钟得到正确加温以稳定的频率来运行。如果新时钟信号的速率来自如石英晶振或谐振器的外部组件,这是尤其需要的。若如此,紧接着的从第一时钟信号向快得多的时钟信号的切换会导致异常行为。更具体地说,如果外部时钟未加温(或难以到达稳定状态),可出现有不稳定幅频行为的不规则时钟脉冲(也称为蠕动脉冲)。蠕动脉冲有与时钟伪信号一样的作用,例如,可将微处理器置于未知状态。通过执行给时钟加温时间的上电程序,就可避免这样的问题。在图9中,第二时钟信号并不快于第一时钟信号,因此未特地显示加温时段。

于是,图9说明执行掉电操作以允许从一时钟信号切换到第二异步时钟信号。扩展掉电和上电间的时间段以节电也是需要的,诸如CDMA系统中的寻呼时隙间。由此,在T1和T3之间经过任意量的时间以允许睡眠模式。在睡眠模式期间,生成高频时钟信号(诸如时钟信号260和262)的所有时钟发生器较佳地置于低功率模式以再节电。例如,通过断开与时钟发生器有关的振荡器电路内的反馈信号路径可实现低功率模式。照此在普通CDMA移动台内将石英晶体振荡器置于低功率模式可节省大约4.5mA电。一旦上电,必须使能或允许水晶振荡器在所发生的时钟施加于处理器前得到稳定。提供加温计时器对用来允许振荡器稳定的加温时段计时。实际睡眠时段较佳地由低频、低功率时钟信号发生器计时。

图10A-C是说明图6的示例掉电控制器和时钟控制单元的相关电路组件的电路示意图。标号300标识的组件涉及掉电操作的控制。标号302标识的组件涉及上电操作并特别包括用来允许处理器加温到新时钟信号速率的加温计时器。标号304标识的组件涉及从一时钟信号切换到另一同步时钟信号。图11是给出由图10A-C的电路使用的用来切换从4分频信号至1分频信号的用于处理器的信号的特定信号的时序图。图12是说明结合图10A-C的电路使用的特定信号首先通过将时钟信号从处理器掉开来掉电和后续对处理器上电的时序图。图13是说明结合图10A-C的电路使用的特定信号复位后的时序图。如上所述,执行掉电和后续对处理器上电的程序以节电是通过在不需要电的时段期间去激活处理器实现的。而且,使用该程序从第一时钟信号切换到与第一时钟信号异步的第二时钟信号。在图12的特殊举例中,提供上电和掉电只是为节电且施加于处理器的时钟信号的时钟速率上电后与掉电前相同。在施加于处理器的时钟信号是在异步时钟信号间切换的情况下,掉电前的时钟信号与上电后的时钟信号异步。

现提供关于用于向处理器(称为ARM)切换的时钟速率的图11中所说明的特定信号的有关细节。向处理器切换时钟速率是通过uP-CLK-CTL2寄存器的写入比特[2∶0]执行的。写入该寄存器在MCLK的低阶段(阶段1)停止MCLK输入至ARM。切换时钟速率并随后使能对ARM的MCLK。这样,提供一种离合切换(clutch-and-shift)机制。写入uP-CLK-CTL2寄存器后,禁止对ARM的时钟,切换速率并随后使能时钟。

信号描述

sel-up-clk-ctl2:这是写至uP-CLK-CTL2寄存器的phi2半锁存解码。

sel-up-clk-ctl2-ff:在时钟源的上升沿对sel-up-clk-ctl2采样以产生sel-up-clk-ctl2-ff。该信号用来切换时钟速率选择复用器(图10C的306)。

res-mclk-en-fall:在时钟源的下降沿对sel-up-clk-ctl2-ff采样产生res-mclk-en-fall。该信号用来在sel-up-clk-ctl2-ff已切换时钟速率选择后去断言的res-mclk-en-。

sel-up-clk-ctl2-lat:这是sel-up-clk-ctl2的延迟版,用来断言res-mclk-en-(禁止对ARM的MCLK)。不用sel-up-clk-ctl2做这些,因为在关闭MCLK前写至uP-CLK-CTL2应已完成(clkctl2-cal得到写入的数据值)。

switch-mclk-rate:该信号断言在sel-up-clk-ctl2-ff的下降沿检测且其持续时间是一时钟源周期。该信号用于改变已复用了新uP-CLK-CTL2数值的时钟速率。

set-mclk-en:在时钟源的下降沿对switch-mclk-rate采样以产生该信号。用来使能对ARM的MCLK。

res-mclk-en:这是在sel-up-clk-ctl2的下降沿后断言的,用来禁止对ARM的MCLK。

res-cntr-clkctl2:switch-mclk-rate和set-mclk-en的“或”操作以生res-cntr-clkctl2。它用来在时钟速率切换期间复位按n分频的计数器。或者,本可用switch-mclk-rate复位计数器,但安全起见,用set-mclk-en用于提供适用于按n分频电路的较长复位脉冲。这就保证了在切换速率期间无时钟,且只有在速率得到可靠切换之后才能使能时钟。

复位的产生

resin-n断言后,BnRES变低。信号schmitt-out选作电路的时钟源。在复位时,保持6比特async-ff计数器,“与”门(Gl)在mclk-src上输出schmitt-out。此时,史密特触发输出可能不稳定,但这在断言BnRES时不影响微处理器。当resin-n去断言时,BnRES在BCLK_phi2上的两或三周期后变高。现在,BCLK_phi2的上升沿是schmitt-out的下降沿的结果。因此,当BnRES去断言时保证schmitt-out为低,从而保证G1上的无伪信号转换。6比特async-ff计数器开始产生分频的时钟,6∶1复用器在mclk-src上选择按2分频的时钟。这在图13中也是已知的。

操作

发出变位后,mclk-src是振荡器按2分频且mclk-en高。写至uP-CLK-CTL2寄存器后,sel-up-clk-ctl2是phi2信号。在时钟源的下一上升沿断言sel-up-clk-ctl2-ff。这使res-mclk-en-fall在时钟源的下一下降沿上变高。

写完成是phi2信号且去断言sel-up-clk-ctl2。

这引起:

断言sel-up-clk-ctl2-lat。

Clkctl2-val得到写至uP-CLK-CTL2的数值,这是要切换到的新时钟速率。

断言res-mclk-en,这使mclk-en变低。mclk-src现因此保持为低,因而关闭对ARM的MCLK。由于这发生于phi2期间,当mclk-en关闭mclk-src时,保证mclk-src为低。

在时钟源的下一上升沿,去断言sel-up-clk-ctl2-ff。switch-mclk-rate变高,mclk-rate-sel得到写至uP-CLK-CTL2的数值。时钟速率现在切换,此时,由于mclk-en保持为低,mclk-src未看见切换导致的伪信号。此时也用res-cntr-clkctl2复位按n分频(6比特async-ff计数器)电路。

在时钟源的下一下降沿,去断言res-mclk-en-fall。这使res-mclk-en变低。此时set-mclk-en变高,因之mclk-en变高。继续断言switch-mclk-rate时,按n分频电路仍保持在复位中。

在时钟源的下一上升沿,去断言switch-clk-rate。

在时钟源的下一下降沿,去断言set-mclk-en,这使res-cntr-clkctl2去断言,按n分割电路开始计数。至止clk-ctl2-val是稳定的,新时钟速率可用于mclk-src上。

适用于BCLK的2阶段发生器曾生成mclk-src的两阶段,在phi2期间,去断言sel-up-clk-ctl2-lat,从而完成时钟切换机制。

图10A-C的电路也允许四种不同的源作为时钟源。这些是由uP-CLK-CTL1寄存器的写至比特[5∶4]后续掉电操作选择的。一旦从掉电中恢复,新时钟源用作是uP-CLK-CTL2寄存器的比特规定的速率的时钟源。

掉电操作由uP-CLK-CTL1寄存器的比特0控制。进入掉电模式是向该比特的连续两次写(1后续0)的结果。从掉电恢复是nIRQ或nFIQ上的不屏蔽中断的结果。中断后加温计时器开始倒计数,计数器持续时间由uP-CLK-CTL1的比特[3∶1]规定。

pd-en:这是uP-CLK-CTL1的写至比特0的解码,用来进入掉电和从掉电恢复。

up-osc-en:在掉电期间,up-osc-en低,用来禁止振荡器。一旦有中断断言,up-osc-en进行0到1的转换,这用来使能振荡器和加温计时器。

osc-ok:用来表示何时振荡器得到加温并准备好由ARM使用。是slpctl-clk信号。

osc-ok-delay:这是osc-ok的单周期延迟版。

osc-ok-sync:osc-ok-delay与时钟源同步便是osc-ok-sync。

outof-pd-en:这用来控制中断断言后的电路的复苏操作。

wutimer-done:这表示加温计时器的失效。

re s-cntr-pd:这用来在加温计时器失效后复位按n分频的计数器电路,以允许对ARM的无伪信号mclk-src。

下面给出图12所示的用于执行掉电操作及后续上电操作的特定信号的细节:

BnRES断言和去断言后,pd-en低。Up-osc-en高,使能振荡器。

写入uP-CLK-CTL1后产生结果如下:

pe-en变高,这使up-osc-en变低。关闭振荡器,如果voc-osc-en也低。

osc-ok-sync变低并关闭mclk-src。当mclk-src在低阶段并因而无伪信号时,出现该mclk-src关闭。

osc-ok因up-osc-en低而在slpctl-clk-phil上变低。在下一slpctl-clk-phil上,osc-ok-delay变低。由于osc-ok、osc-ok-delay、osc-ok-sync基本上相同,由pd-en复位时钟源同步器链中的全部async-ff。因而,osc-ok、osc-ok-delay、osc-ok-sync有相同的行为,尽管osc-ok-sync在osc-ok和osc-ok-delay进行1到0的转换(因为osc-ok和osc-ok-delay是slpctl-clk信号)前变低。

在掉电中保持着振荡器,直到不屏蔽中断出现。中断断言使pd-en变低。我们得保证:如果中断在osc-ok-delay变低前断言,它在osc-ok-delay进行1到0的转换后才改变pd-en。这是需要的,因为如果在osc-ok-delay变低前pd-en变低,会出现osc-ok-sync上的未知值(因为时钟源同步器链上的复位项是pd-en)。为实现这一点,使用out of-pd-en。中断断言之前,out of-pd-en低,因为断言了async-ff上的复位项。当中断断言时,有两种可能情况:

osc-ok-delay低:在此情况,断言async-ff的设置项,因为osc-ok-delay低。但是outof-pd-en低,因为也断言了复位项且复位控制了整个async-ff集。现在,中断断言使async-ff上的复位项去断言。outof-pd-en变高,因为设置项控制着async-ff。结果,pd-en变低。

osc-ok-delay高:在此情况,不断言async-ff的设置项。outof-pd-en低,且当中断断言时也去断言设置项。outof-pd-en低到osc-ok-delay进行1到0的转换(设置使outof-pd-en变高的async-ff)。结果,pd-en变低。

up-osc-en因pd-en低而变高。然后与slpctl-clk和检测到的上升沿同步以产生加温计时器的下载信号。加温计时器开始倒计时,其持续时间是写至uP-CLK-CTL2的比特[3∶1]的值。

当计时器数值到0x1时,检测到加温持续时间的结束。此时,断言wutimer-done。这使osc-ok和osc-ok-delay断言。osc-ok-delay与时钟源同步,同步版是检测到用来在时钟源的下降沿产生res-cntr-pd的上升沿。这使按n分频计时器就在mclk-src使能前得到复位,从而消除使能过程期间mclk-src上的伪信号。

在时钟源的下一上升沿,osc-ok-sync变高且mclk-src现在使能。仍断言res-cntr-pd。

在时钟源的下一下降沿,去断言res-cntr-pd且相应按n分频时钟在mclk-src使能。

中断在上电后由中断服务程序清除。这将去断言outof-pd-en并完成掉电和加温序列。

已描述将时钟信号用于RISC处理器(此类处理器中,推迟操作仅需将时钟信号与处理器断开随后重新连接来实现)的各种方法和装置。发明原理也适用于其他系统。此处所述示例实施例只是说明本发明而非限制本发明的范围,应按以下权利要求理解本发明的范围。

Claims (13)

1.一种通过使用外围电路将时钟信号从处理器断开而使流水线处理器不工作的方法,所述方法包括的步骤有:

通过控制处理器执行将处理器外部预定设备置于预定状态中的指令启动掉电操作,所述指令用于外部设备只是掉电操作的部分;

用外围电路检测置于预定状态的外部设备,并且,作为响应,在处理器于处理器的当前流水线级期间执行的操作完成后而在处理器的后续流水线阶段的操作启动前,用外围电路将时钟信号从处理器断开。

2.如权利要求1所述的方法,其特征在于,在将时钟信号从处理器断开前,外围设备进行等待,直到时钟信号已转换到低状态。

3.如权利要求2所述的方法,其特征在于,处理器配置成响应于等待信号的断言来延迟操作,并且至少到时钟信号到达低状态时外围电路在当前流水线级期间断言等待信号。

4.如权利要求1所述的方法,其特征在于,所述指令是承载操作而外部设备是预定存储寄存器。

5.如权利要求4所述的方法,其特征在于,存储寄存器存储单个比特,承载操作在该比特中存储一逻辑1再存储一逻辑0。

6.如权利要求1所述的方法,其特征在于,还包括通过在完成睡眠期后时钟信号重新连接于处理器而随后重新使处理器工作的步骤。

7.如权利要求6所述的方法,其特征在于,在完成睡眠期后时钟信号重新连接处理器的步骤包括在时钟信号重新连接时间之前重新使时钟信号工作以允许产生时钟信号的设备在时钟信号的重新连接之前加温从而使一旦重新连接到处理器时钟信号便稳定这样一个步骤。

8.如权利要求7所述的方法,其特征在于,重新连接时钟信号的步骤是在时钟信号处于非有效状态中时完成的。

9.一种通过将时钟信号从处理器断开而使流水线处理器不工作的系统,所述系统包括:

提供时钟信号的装置;

在处理器外部的存储状态指示的装置;

执行将存储装置置于预定状态中的指令的装置,所述指令用于存储装置只是掉电操作的部分;

检测置于预定状态的存储装置,并且,作为响应,在处理器于处理器的当前流水线级期间执行的操作完成后而在处理器的后续流水线级的操作启动前将时钟信号从处理器断开的处理器外部的设备。

10.一种通过将时钟信号从处理器断开而使流水线处理器不工作的系统,所述系统包括:

处理器外部产生时钟信号的时钟发生器;

处理器外部的存储寄存器;

执行将所述寄存器置于预定状态中的指令的处理器,所述指令用于寄存器只是掉电操作的部分;

检测置于预定状态的寄存器,并且,作为响应,在处理器于处理器的当前流水线级期间执行的操作完成后而在处理器的后续流水线级的操作启动前将时钟发生器从处理器断开的处理器外部的掉电控制器。

11.一种使用也接收时钟信号的外围电路在用于流水线处理器的异步时钟信号间切换的方法,所述方法包括的步骤有:

控制外围电路将第一时钟信号与处理器相连接;

通过控制处理器执行将处理器外部预定设备置于预定状态中的指令启动掉电操作,所述指令用于外部设备只是掉电操作的部分;

用外围电路检测置于预定状态的外部设备,并且,作为响应,在处理器于处理器的当前流水线级期间执行的操作完成后而在处理器的后续流水线级的操作启动前,用外围电路将时钟信号从处理器断开;及

控制外围电路等到第二时钟信号在非有效阶段然后将第二时钟信号用于处理器。

12.如权利要求11所述的方法,其特征在于,控制外围电路等到第二时钟信号在非有效阶段然后将将第二时钟信号用于处理器的步骤包括的步骤有:

检测中断信号;

启动加温计时器;

一旦完成加温时段并且在第二时钟信号的非有效阶段期间将第二时钟信号用于处理器。

13.一种使用也接收时钟信号的外围电路在用于流水线处理器的异步时钟信号间切换的系统,所述系统包括:

将第一时钟信号与处理器相连接的装置;

处理器外部的存储状态指示的装置;

执行将存储装置置于预定状态中的指令的装置,所述指令用于存储装置只是掉电操作的部分;

检测置于预定状态的存储装置,并且,作为响应,在处理器于处理器的当前流水线级期间执行的操作完成后而在处理器的后续流水线级的操作启动前将时钟信号从处理器断开的处理器外部的设备。

控制外围电路等到第二时钟信号在非有效阶段然后将第二时钟信号用于处理器的装置。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/US2001/003986 WO2002063452A1 (en) | 2001-02-07 | 2001-02-07 | Method and apparatus for applying clock signals to the processor of mobile subscriber station to manage power consumption |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1502072A CN1502072A (zh) | 2004-06-02 |

| CN1282060C true CN1282060C (zh) | 2006-10-25 |

Family

ID=21742321

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB018226752A Expired - Lifetime CN1282060C (zh) | 2001-02-07 | 2001-02-07 | 将时钟信号用于移动用户台的处理器以管理功耗的方法和设备 |

Country Status (6)

| Country | Link |

|---|---|

| EP (1) | EP1358538B1 (zh) |

| CN (1) | CN1282060C (zh) |

| AT (1) | ATE477526T1 (zh) |

| DE (1) | DE60142799D1 (zh) |

| HK (1) | HK1063674A1 (zh) |

| WO (1) | WO2002063452A1 (zh) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1573490A2 (en) * | 2002-12-04 | 2005-09-14 | Koninklijke Philips Electronics N.V. | Software-based control of microprocessor power dissipation |

| WO2009044308A2 (en) * | 2007-10-01 | 2009-04-09 | St-Nxp Wireless (Holding) Ag | Clock signal distribution circuit, mobile device and method for operating a clock signal distribution circuit |

| KR102478114B1 (ko) * | 2016-08-05 | 2022-12-16 | 에스케이하이닉스 주식회사 | 전류 차단 회로, 이를 포함하는 반도체 장치 및 이의 동작 방법 |

| CN106793043A (zh) * | 2017-01-17 | 2017-05-31 | 广州市建设工程质量安全检测中心 | 一种用于监测无线终端的唤醒电路和方法 |

| US11579650B2 (en) | 2019-12-19 | 2023-02-14 | Advanced Micro Devices, Inc. | Method and apparatus for synchronizing the time stamp counter |

| CN113157079B (zh) * | 2020-01-07 | 2024-05-24 | 上海寒武纪信息科技有限公司 | 用于控制处理器的方法、装置及其处理器 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4855616A (en) * | 1987-12-22 | 1989-08-08 | Amdahl Corporation | Apparatus for synchronously switching frequency source |

| US4870299A (en) * | 1988-03-28 | 1989-09-26 | Chen Ben W | Dynamic switching circuit for multiple asynchronous clock sources |

| US5099140A (en) * | 1990-08-31 | 1992-03-24 | Advanced Micro Devices, Inc. | Synchronous clock source selector |

| JPH04288607A (ja) * | 1991-03-18 | 1992-10-13 | Sharp Corp | クロック信号切り換え回路 |

| US5842029A (en) * | 1991-10-17 | 1998-11-24 | Intel Corporation | Method and apparatus for powering down an integrated circuit transparently and its phase locked loop |

| JPH06295243A (ja) * | 1993-04-08 | 1994-10-21 | Mitsubishi Electric Corp | データ処理装置 |

| US5623223A (en) * | 1994-10-12 | 1997-04-22 | National Semiconductor Corporation | Glitchless clock switching circuit |

| US5745375A (en) * | 1995-09-29 | 1998-04-28 | Intel Corporation | Apparatus and method for controlling power usage |

-

2001

- 2001-02-07 EP EP01908942A patent/EP1358538B1/en not_active Expired - Lifetime

- 2001-02-07 AT AT01908942T patent/ATE477526T1/de not_active IP Right Cessation

- 2001-02-07 CN CNB018226752A patent/CN1282060C/zh not_active Expired - Lifetime

- 2001-02-07 WO PCT/US2001/003986 patent/WO2002063452A1/en active Application Filing

- 2001-02-07 DE DE60142799T patent/DE60142799D1/de not_active Expired - Lifetime

-

2004

- 2004-08-27 HK HK04106447A patent/HK1063674A1/xx not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| EP1358538A1 (en) | 2003-11-05 |

| HK1063674A1 (en) | 2005-01-07 |

| ATE477526T1 (de) | 2010-08-15 |

| CN1502072A (zh) | 2004-06-02 |

| DE60142799D1 (de) | 2010-09-23 |

| EP1358538B1 (en) | 2010-08-11 |

| WO2002063452A1 (en) | 2002-08-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100527045C (zh) | 为低功率设计的动态时钟系统与方法 | |

| KR101412676B1 (ko) | 무선 송수신기에서 슬립 모드들의 제어 | |

| CN101395584B (zh) | Jtag功率降级调试 | |

| CN101893926B (zh) | 控制双处理器切换的方法、装置及终端 | |

| CN1202457C (zh) | 处理器控制电压的系统中提供决定开启电压的方法及装置 | |

| TWI574148B (zh) | 嵌入式控制器及其省電控制方法 | |

| US20060107077A1 (en) | Programmable power transition counter | |

| CN1637683A (zh) | 用于减少空闲模式下的功率消耗的处理器系统和方法 | |

| WO2004093370A2 (en) | Distributed power management | |

| CN104024980A (zh) | 连接的待机睡眠状态 | |

| CN101876847A (zh) | 微控制器中的功率降低 | |

| CN1550070A (zh) | 用于无线系统中的时钟及电源控制的方法和设备 | |

| JP2015043225A (ja) | ネットワークアクセスモジュールの電源管理方法及び装置 | |

| CN1645955A (zh) | Td-scdma手机系统电源管理及省电的方法 | |

| JP2009514308A (ja) | 無線通信ネットワークまたはモバイル・ポイント・ツー・ポイント接続における装置のスリープモードの制御方法およびシステム | |

| CN101930279A (zh) | 用于计算机主机板的节电电子装置及其计算机主机板 | |

| CN101539797A (zh) | 一种动态时钟与电源的控制方法、系统及装置 | |

| US6674821B1 (en) | Method and apparatus for reducing power consumption | |

| CN102385531A (zh) | 定时器管理装置与方法 | |

| CN1282060C (zh) | 将时钟信号用于移动用户台的处理器以管理功耗的方法和设备 | |

| CN101150811B (zh) | 一种移动终端中控制待机的装置和方法 | |

| CN101452337A (zh) | 一种外接设备的控制方法和装置 | |

| CN101677477A (zh) | 一种精确控制多模单待手机待机时间低功耗的系统及方法 | |

| CN1258942C (zh) | 带有时间日期自动校准功能的移动通信终端 | |

| US6954872B2 (en) | Registering events while clocking multiple domains |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| REG | Reference to a national code |

Ref country code: HK Ref legal event code: DE Ref document number: 1063674 Country of ref document: HK |

|

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CX01 | Expiry of patent term |

Granted publication date: 20061025 |

|

| CX01 | Expiry of patent term |