CN108885660B - 用于元数据处理的技术 - Google Patents

用于元数据处理的技术 Download PDFInfo

- Publication number

- CN108885660B CN108885660B CN201680081293.8A CN201680081293A CN108885660B CN 108885660 B CN108885660 B CN 108885660B CN 201680081293 A CN201680081293 A CN 201680081293A CN 108885660 B CN108885660 B CN 108885660B

- Authority

- CN

- China

- Prior art keywords

- metadata

- tag

- instruction

- processing

- rule

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000012545 processing Methods 0.000 title claims abstract description 457

- 238000000034 method Methods 0.000 title claims abstract description 380

- 230000015654 memory Effects 0.000 claims description 904

- 230000008569 process Effects 0.000 claims description 171

- 230000004044 response Effects 0.000 claims description 38

- 239000003550 marker Substances 0.000 description 201

- 238000012546 transfer Methods 0.000 description 118

- 230000004224 protection Effects 0.000 description 106

- 238000005516 engineering process Methods 0.000 description 75

- 238000013475 authorization Methods 0.000 description 60

- 238000003860 storage Methods 0.000 description 53

- 239000002131 composite material Substances 0.000 description 47

- 230000001960 triggered effect Effects 0.000 description 42

- 230000009471 action Effects 0.000 description 38

- 230000006399 behavior Effects 0.000 description 38

- 230000007246 mechanism Effects 0.000 description 38

- 238000004040 coloring Methods 0.000 description 33

- 238000005457 optimization Methods 0.000 description 33

- 238000010200 validation analysis Methods 0.000 description 31

- 238000001193 catalytic steam reforming Methods 0.000 description 27

- 239000003086 colorant Substances 0.000 description 26

- 238000013507 mapping Methods 0.000 description 26

- 230000002829 reductive effect Effects 0.000 description 26

- 238000012795 verification Methods 0.000 description 24

- 150000001875 compounds Chemical class 0.000 description 22

- 230000000694 effects Effects 0.000 description 21

- 230000006870 function Effects 0.000 description 20

- 238000013519 translation Methods 0.000 description 20

- 230000014616 translation Effects 0.000 description 20

- 239000004744 fabric Substances 0.000 description 19

- 230000003068 static effect Effects 0.000 description 19

- 239000013598 vector Substances 0.000 description 19

- 238000013461 design Methods 0.000 description 18

- 238000003780 insertion Methods 0.000 description 18

- 230000037431 insertion Effects 0.000 description 18

- 238000010586 diagram Methods 0.000 description 17

- 238000002955 isolation Methods 0.000 description 17

- 101100138677 Arabidopsis thaliana NPF8.1 gene Proteins 0.000 description 16

- 101150059273 PTR1 gene Proteins 0.000 description 16

- 101100262635 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) UBR1 gene Proteins 0.000 description 16

- 238000012986 modification Methods 0.000 description 16

- 230000004048 modification Effects 0.000 description 16

- 238000004088 simulation Methods 0.000 description 16

- 238000004422 calculation algorithm Methods 0.000 description 13

- 239000000203 mixture Substances 0.000 description 13

- 230000008901 benefit Effects 0.000 description 12

- 238000011068 loading method Methods 0.000 description 12

- 101100031674 Arabidopsis thaliana NPF8.3 gene Proteins 0.000 description 11

- 101100235787 Schizosaccharomyces pombe (strain 972 / ATCC 24843) pim1 gene Proteins 0.000 description 11

- 230000006835 compression Effects 0.000 description 11

- 238000007906 compression Methods 0.000 description 11

- 238000011156 evaluation Methods 0.000 description 11

- 101150114015 ptr-2 gene Proteins 0.000 description 11

- 230000007704 transition Effects 0.000 description 11

- 108091006146 Channels Proteins 0.000 description 10

- 230000008859 change Effects 0.000 description 10

- 238000000926 separation method Methods 0.000 description 10

- 230000001133 acceleration Effects 0.000 description 9

- 238000002372 labelling Methods 0.000 description 9

- 230000000670 limiting effect Effects 0.000 description 9

- 230000000644 propagated effect Effects 0.000 description 9

- 239000000243 solution Substances 0.000 description 8

- 238000004458 analytical method Methods 0.000 description 7

- 238000009826 distribution Methods 0.000 description 7

- 230000014509 gene expression Effects 0.000 description 7

- 238000002347 injection Methods 0.000 description 7

- 239000007924 injection Substances 0.000 description 7

- 230000001404 mediated effect Effects 0.000 description 7

- 230000002123 temporal effect Effects 0.000 description 7

- 230000001419 dependent effect Effects 0.000 description 6

- 238000002474 experimental method Methods 0.000 description 6

- 239000012634 fragment Substances 0.000 description 6

- 230000002265 prevention Effects 0.000 description 6

- 238000013459 approach Methods 0.000 description 5

- 238000004364 calculation method Methods 0.000 description 5

- 230000015556 catabolic process Effects 0.000 description 5

- 230000001186 cumulative effect Effects 0.000 description 5

- 238000006731 degradation reaction Methods 0.000 description 5

- 239000000284 extract Substances 0.000 description 5

- 101000686491 Platymeris rhadamanthus Venom redulysin 1 Proteins 0.000 description 4

- 238000003491 array Methods 0.000 description 4

- DGLFSNZWRYADFC-UHFFFAOYSA-N chembl2334586 Chemical compound C1CCC2=CN=C(N)N=C2C2=C1NC1=CC=C(C#CC(C)(O)C)C=C12 DGLFSNZWRYADFC-UHFFFAOYSA-N 0.000 description 4

- 230000000977 initiatory effect Effects 0.000 description 4

- 239000003607 modifier Substances 0.000 description 4

- 239000002574 poison Substances 0.000 description 4

- 231100000614 poison Toxicity 0.000 description 4

- 230000008093 supporting effect Effects 0.000 description 4

- 238000012360 testing method Methods 0.000 description 4

- 238000012549 training Methods 0.000 description 4

- 101100264195 Caenorhabditis elegans app-1 gene Proteins 0.000 description 3

- 101150089655 Ins2 gene Proteins 0.000 description 3

- 101100445488 Neurospora crassa (strain ATCC 24698 / 74-OR23-1A / CBS 708.71 / DSM 1257 / FGSC 987) ptr-2 gene Proteins 0.000 description 3

- 101100072652 Xenopus laevis ins-b gene Proteins 0.000 description 3

- 238000013329 compounding Methods 0.000 description 3

- 239000000470 constituent Substances 0.000 description 3

- 238000001514 detection method Methods 0.000 description 3

- VPWFPZBFBFHIIL-UHFFFAOYSA-L disodium 4-[(4-methyl-2-sulfophenyl)diazenyl]-3-oxidonaphthalene-2-carboxylate Chemical compound [Na+].[Na+].[O-]S(=O)(=O)C1=CC(C)=CC=C1N=NC1=C(O)C(C([O-])=O)=CC2=CC=CC=C12 VPWFPZBFBFHIIL-UHFFFAOYSA-L 0.000 description 3

- 230000006872 improvement Effects 0.000 description 3

- 238000009434 installation Methods 0.000 description 3

- 238000005192 partition Methods 0.000 description 3

- 238000011084 recovery Methods 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- VLCQZHSMCYCDJL-UHFFFAOYSA-N tribenuron methyl Chemical compound COC(=O)C1=CC=CC=C1S(=O)(=O)NC(=O)N(C)C1=NC(C)=NC(OC)=N1 VLCQZHSMCYCDJL-UHFFFAOYSA-N 0.000 description 3

- 102100030154 CDC42 small effector protein 1 Human genes 0.000 description 2

- 101000794295 Homo sapiens CDC42 small effector protein 1 Proteins 0.000 description 2

- 206010027476 Metastases Diseases 0.000 description 2

- 230000003213 activating effect Effects 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 238000011109 contamination Methods 0.000 description 2

- 230000007123 defense Effects 0.000 description 2

- 230000004069 differentiation Effects 0.000 description 2

- 238000007667 floating Methods 0.000 description 2

- 230000003116 impacting effect Effects 0.000 description 2

- 239000003999 initiator Substances 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 238000012005 ligant binding assay Methods 0.000 description 2

- 230000000873 masking effect Effects 0.000 description 2

- 230000009401 metastasis Effects 0.000 description 2

- 230000008450 motivation Effects 0.000 description 2

- 230000001902 propagating effect Effects 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 238000010926 purge Methods 0.000 description 2

- 238000011002 quantification Methods 0.000 description 2

- 238000007789 sealing Methods 0.000 description 2

- 238000000638 solvent extraction Methods 0.000 description 2

- 230000006886 spatial memory Effects 0.000 description 2

- 235000020042 tonto Nutrition 0.000 description 2

- 230000001052 transient effect Effects 0.000 description 2

- 239000002699 waste material Substances 0.000 description 2

- UKGJZDSUJSPAJL-YPUOHESYSA-N (e)-n-[(1r)-1-[3,5-difluoro-4-(methanesulfonamido)phenyl]ethyl]-3-[2-propyl-6-(trifluoromethyl)pyridin-3-yl]prop-2-enamide Chemical compound CCCC1=NC(C(F)(F)F)=CC=C1\C=C\C(=O)N[C@H](C)C1=CC(F)=C(NS(C)(=O)=O)C(F)=C1 UKGJZDSUJSPAJL-YPUOHESYSA-N 0.000 description 1

- BYHQTRFJOGIQAO-GOSISDBHSA-N 3-(4-bromophenyl)-8-[(2R)-2-hydroxypropyl]-1-[(3-methoxyphenyl)methyl]-1,3,8-triazaspiro[4.5]decan-2-one Chemical compound C[C@H](CN1CCC2(CC1)CN(C(=O)N2CC3=CC(=CC=C3)OC)C4=CC=C(C=C4)Br)O BYHQTRFJOGIQAO-GOSISDBHSA-N 0.000 description 1

- 101150053844 APP1 gene Proteins 0.000 description 1

- 241000219357 Cactaceae Species 0.000 description 1

- 101100434927 Caenorhabditis elegans prmt-5 gene Proteins 0.000 description 1

- 102100035431 Complement factor I Human genes 0.000 description 1

- 101100391182 Dictyostelium discoideum forI gene Proteins 0.000 description 1

- 101100189105 Homo sapiens PABPC4 gene Proteins 0.000 description 1

- 244000035744 Hura crepitans Species 0.000 description 1

- 206010021703 Indifference Diseases 0.000 description 1

- 241001024304 Mino Species 0.000 description 1

- 101100215778 Neurospora crassa (strain ATCC 24698 / 74-OR23-1A / CBS 708.71 / DSM 1257 / FGSC 987) ptr-1 gene Proteins 0.000 description 1

- 102100039424 Polyadenylate-binding protein 4 Human genes 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000002159 abnormal effect Effects 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 230000002776 aggregation Effects 0.000 description 1

- 238000004220 aggregation Methods 0.000 description 1

- 230000003190 augmentative effect Effects 0.000 description 1

- 230000033228 biological regulation Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- ONTQJDKFANPPKK-UHFFFAOYSA-L chembl3185981 Chemical compound [Na+].[Na+].CC1=CC(C)=C(S([O-])(=O)=O)C=C1N=NC1=CC(S([O-])(=O)=O)=C(C=CC=C2)C2=C1O ONTQJDKFANPPKK-UHFFFAOYSA-L 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 230000002301 combined effect Effects 0.000 description 1

- 238000004590 computer program Methods 0.000 description 1

- 238000012790 confirmation Methods 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000000593 degrading effect Effects 0.000 description 1

- 238000005315 distribution function Methods 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 230000007717 exclusion Effects 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 238000010304 firing Methods 0.000 description 1

- 239000000796 flavoring agent Substances 0.000 description 1

- 235000019634 flavors Nutrition 0.000 description 1

- 238000011010 flushing procedure Methods 0.000 description 1

- 230000002068 genetic effect Effects 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 238000011835 investigation Methods 0.000 description 1

- 238000000146 jump and return pulse sequence Methods 0.000 description 1

- 230000009191 jumping Effects 0.000 description 1

- 230000005291 magnetic effect Effects 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 238000006386 neutralization reaction Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000008520 organization Effects 0.000 description 1

- 230000008447 perception Effects 0.000 description 1

- 230000000750 progressive effect Effects 0.000 description 1

- 230000035755 proliferation Effects 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- WPPDXAHGCGPUPK-UHFFFAOYSA-N red 2 Chemical compound C1=CC=CC=C1C(C1=CC=CC=C11)=C(C=2C=3C4=CC=C5C6=CC=C7C8=C(C=9C=CC=CC=9)C9=CC=CC=C9C(C=9C=CC=CC=9)=C8C8=CC=C(C6=C87)C(C=35)=CC=2)C4=C1C1=CC=CC=C1 WPPDXAHGCGPUPK-UHFFFAOYSA-N 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 238000012552 review Methods 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 239000004576 sand Substances 0.000 description 1

- 238000005201 scrubbing Methods 0.000 description 1

- 239000010865 sewage Substances 0.000 description 1

- 239000004432 silane-modified polyurethane Substances 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 230000002459 sustained effect Effects 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

- 238000000844 transformation Methods 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/50—Monitoring users, programs or devices to maintain the integrity of platforms, e.g. of processors, firmware or operating systems

- G06F21/52—Monitoring users, programs or devices to maintain the integrity of platforms, e.g. of processors, firmware or operating systems during program execution, e.g. stack integrity ; Preventing unwanted data erasure; Buffer overflow

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30098—Register arrangements

- G06F9/30101—Special purpose registers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0875—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches with dedicated cache, e.g. instruction or stack

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/14—Protection against unauthorised use of memory or access to memory

- G06F12/1408—Protection against unauthorised use of memory or access to memory by using cryptography

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/14—Protection against unauthorised use of memory or access to memory

- G06F12/1458—Protection against unauthorised use of memory or access to memory by checking the subject access rights

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/78—Architectures of general purpose stored program computers comprising a single central processing unit

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/60—Protecting data

- G06F21/62—Protecting access to data via a platform, e.g. using keys or access control rules

- G06F21/6218—Protecting access to data via a platform, e.g. using keys or access control rules to a system of files or objects, e.g. local or distributed file system or database

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30072—Arrangements for executing specific machine instructions to perform conditional operations, e.g. using predicates or guards

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30098—Register arrangements

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3867—Concurrent instruction execution, e.g. pipeline, look ahead using instruction pipelines

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F16/00—Information retrieval; Database structures therefor; File system structures therefor

- G06F16/20—Information retrieval; Database structures therefor; File system structures therefor of structured data, e.g. relational data

- G06F16/23—Updating

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/10—Providing a specific technical effect

- G06F2212/1052—Security improvement

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/40—Specific encoding of data in memory or cache

- G06F2212/402—Encrypted data

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/45—Caching of specific data in cache memory

- G06F2212/452—Instruction code

Abstract

描述了可以用来编码在处理器上运行的代码的任意数目的安全性策略的元数据处理的技术。元数据可以添加到系统中的每个字且可以使用与数据流并行工作以推行任意策略集合的元数据处理单元。在一个方面中,元数据可以特性化为无限制的和软件可编程的以可应用于各种元数据处理策略。技术和策略具有各种用途,例如包括安全、安全性和同步。另外,描述了关于在基于RISC‑V架构的实施例中的元数据处理的方面和技术。

Description

相关申请的交叉引用

本申请要求于2016年5月31日提交的美国申请No.15/168,689的优先权,该美国申请No.15/168,689要求于2015年12月17日提交的美国临时申请序号62/268,639,“SOFTWAREDEFINED METADATA PROCESSING”和于2015年12月21日提交的美国临时申请序号62/270,187,“SOFTWARE DEFINED METADATA PROCESSING”的优先权,将其全部通过引用包括于此。

背景技术

本申请总的来说关于数据处理,且更具体地,涉及用于元数据处理的可编程单元。

当今的计算机系统非常难以保护。例如,现有的处理器架构允许违反较高级抽象(abstraction)的比如缓存溢出、指针伪造等各种行为。关闭编程语言和硬件之间的间隙可能留给软件,而推行严密抽象的成本通常认为过高。

一些近来的努力已经表明在执行期间传播(propagate)元数据以推行(enforce)在安全性违规(violation)和恶意攻击发生时抓住它们的策略(policy)的价值。这些策略可以以软件推行,但是典型地导致高的不必要的开销,比如在性能和/或成本方面,这阻碍它们的部署,或者另外鼓励了提供较少保护的粗糙近似。用于固定策略的硬件支持可以将开销减小到可接受的水平且防止大部分不期望的代码违规,比如可以由恶意代码或者恶意软件攻击执行的。例如,Intel近来公布了用于边界检查和隔离的硬件。虽然这缓解了许多当今的攻击,完全安全的系统将需要多于存储器安全性和隔离。攻击快速地演变以利用任何剩余形式的易损性。

发明内容

因此,存在可以快速地适用于该不断变化的场景的灵活的安全性架构。将期望这种架构提供用于以最小开销的软件定义的元数据处理的支持。期望这种架构可扩展以广泛地支持和推行任意数目和类型的策略而不用对分配给元数据的位的数目设置可见的、硬的边界。可以在执行期间传播元数据以推行策略和抓住例如通过恶意代码或者恶意软件攻击的对这些策略的违反。

根据在这里描述的技术的一个方面,是处理指令的方法,包括:对于元数据处理,接收具有关联的元数据标记的当前指令,所述元数据处理在与包括当前指令的代码执行域相隔离的元数据处理域中执行;在元数据处理域中和根据元数据标记和当前指令,确定规则(rule)是否存在于当前指令的规则高速缓存中,所述规则高速缓存包括关于由所述元数据处理使用以定义允许的操作的元数据的规则;和响应于确定没有规则存在于用于当前指令的规则高速缓存中,在元数据处理域中执行规则高速缓存未命中(miss)处理,包括:确定是否允许当前指令的执行;响应于确定允许在代码执行域中执行当前指令,生成用于当前指令的新规则;写入到寄存器;和响应于写入到寄存器,将新规则插入到规则高速缓存中。用于选择当前指令的规则的第一元数据可以存储在由元数据处理使用的多个控制状态寄存器的第一部分中,且其中,多个控制状态寄存器的第一部分可以用于将用于当前指令的多个元数据标记传递到元数据处理域,其中,所述多个元数据标记可以用作元数据处理域中的数据。寄存器可以是由元数据处理使用的多个控制状态寄存器的第一控制状态寄存器,且其中,多个控制状态寄存器的第一部分可以用于将多个元数据标记从元数据处理域传递到规则高速缓存。多个元数据标记可以用于当前指令。新规则可以响应于将另一元数据标记写入到第一控制状态寄存器而插入到规则高速缓存中,其中,可以在当前指令的结果上放置该另一元数据标记,且该结果可以是任意目的地寄存器或者存储器位置。多个控制状态寄存器可以包括以下的任何一个或多个:包括所有其他生成的元数据标记从其推导出的初始元数据标记的自举(bootstrap)标记控制状态寄存器;指定默认元数据标记的默认标记控制状态寄存器;指定用于标记分类为公共和不可信的指令和数据的公共不可信元数据标记的公共不可信控制状态寄存器;包括写入到包括关于操作组(opgroup)的信息和用于不同操作码(opcode)的维护(care)信息的表的数据的操作组值控制状态寄存器;指定操作组值控制状态寄存器的数据写入到的表中的位置的操作组地址控制状态寄存器;和其中到泵清空(pumpflush)控制状态寄存器的写入触发规则高速缓存的清空(flush)的泵清空控制状态寄存器。多个控制状态寄存器可以包括指示元数据处理的当前模式的标记模式控制状态寄存器。标记模式控制状态寄存器可以指示何时脱离元数据处理由此不由元数据处理推行一个或多个定义的策略的规则。标记模式控制状态寄存器可以设置为定义的一组允许状态之一以指示元数据处理的当前模式。允许状态可以包括以下的任意一个:关闭状态,由此元数据处理在所有结果上写入默认标记的状态,和指示当以一个或多个指定特权级别在代码域中执行指令时参启用了元数据处理且元数据处理可操作的状态。规则高速缓存未命中处理可以在脱离元数据处理的定义的一组允许状态的第一个中执行。这些允许状态可以包括指示仅当以用户特权级别在代码域中指令执行时启用元数据处理的第一状态;指示仅当以用户或者管理程序(supervisor)特权级别在代码域中指令执行时启用元数据处理的第二状态;指示仅当以用户、管理程序或者系统管理程序(hypervisor)特权级别在代码域中指令执行时启用元数据处理的第三状态;和指示当以用户、管理程序、系统管理程序或者机器特权级别在代码域中指令执行时启用元数据处理的第四状态。可以根据标记模式控制状态寄存器的当前标记模式结合在代码域中执行的代码的当前特权级别来确定启用或者脱离元数据处理,其中,当脱离元数据处理时可以不推行一个或多个定义的策略的规则,且其中,当启用元数据处理时可以推行规则。表可以包括将指令集的操作码映射到相应的操作组的信息和位向量信息。操作组可以指示由元数据处理域类似地处理的关联的操作码的组。位矢量信息可以指示是否与处理操作码关联地使用相对于元数据处理域的特定输入和输出。可以使用小于可允许操作码位的最大数目的操作码位的第一部分来索引该表,且最大数目可以指示指令集的操作码的位数的上限。多个控制状态寄存器的第一部分可以包括扩展的操作码控制状态寄存器,该扩展的操作码控制状态寄存器包括用于当前指令的附加操作码位(如果有的话),其中,当前指令可以包括在具有可变长度操作码的指令集中,且其中,指令集的每个操作码可以可选地包括附加操作码位,且扩展的操作码控制状态寄存器包括用于当前指令的附加操作码位(如果有的话)。对于使用该表映射的每个操作码,存在与所述每个操作码对应的结果位向量,该结果位向量可以指示以用于元数据处理的所述每个操作码使用扩展的操作码控制状态寄存器的附加操作码位的什么部分(如果有的话)。当前指令可以是与单个元数据标记相关联的存储器的单个字中存储的多个指令之一,且所述单个元数据标记可以与单个字中包括的多个指令相关联。多个控制状态寄存器可以包括指示单个字中存储的多个指令中的哪个是当前指令的子指令控制状态寄存器。单个元数据标记可以是指向包括用于单个字中的多个指令中的每一个的不同元数据标记的第一存储器位置的第一指针。至少用于多个指令的第一指令的第一存储器位置中存储的第一元数据标记可以包括指向包括用于第一指令的元数据标记信息的第二存储器位置的第二指针。用于第一指令的元数据标记信息可以包括复杂结构。该复杂结构可以包括至少一个标量数据字段和指向第三存储器位置的至少一个指针字段。

根据在这里的技术的另一方面,是在其上包括代码的非瞬时计算机可读介质,该代码当执行时实现处理指令的方法,包括:对于元数据处理,接收具有关联的元数据标记的当前指令,所述元数据处理在与包括当前指令的代码执行域相隔离的元数据处理域中执行;在元数据处理域中和根据元数据标记和当前指令,确定规则是否存在于当前指令的规则高速缓存中,所述规则高速缓存包括关于由所述元数据处理使用以定义允许的操作的元数据的规则;和响应于确定没有规则存在于用于当前指令的规则高速缓存中,在元数据处理域中执行规则高速缓存未命中处理,包括:确定是否允许当前指令的执行;响应于确定允许在代码执行域中执行当前指令,生成用于当前指令的新规则;写入到寄存器;和响应于写入到寄存器,将新规则插入到规则高速缓存中。

根据在这里的技术的另一方面,是系统,包括:处理器;和存储器,包括在其上存储的代码,该代码当由处理器执行时实现处理指令的方法,包括:对于元数据处理,接收具有关联的元数据标记的当前指令,所述元数据处理在与包括当前指令的代码执行域相隔离的元数据处理域中执行;在元数据处理域中和根据元数据标记和当前指令,确定规则是否存在于当前指令的规则高速缓存中,所述规则高速缓存包括关于由所述元数据处理使用以定义允许的操作的元数据的规则;和响应于确定没有规则存在于用于当前指令的规则高速缓存中,在元数据处理域中执行规则高速缓存未命中处理,包括:确定是否允许当前指令的执行;响应于确定允许在代码执行域中执行当前指令,生成用于当前指令的新规则;写入到寄存器;和响应于写入到寄存器,将新规则插入到规则高速缓存中。处理器可以是精简指令集计算架构中的流水线处理器。

根据在这里的技术的另一方面,是处理指令的方法,包括:接收用于在与包括当前指令的代码执行域相隔离的元数据处理域中执行的元数据处理的当前指令;和通过与用于当前指令的元数据相关的元数据处理域,根据一个或多个策略的集合来确定是否允许当前指令的执行,其中,当前指令访问第一例程的堆栈帧的第一位置,其中,当前指令和堆栈帧的位置具有关联的元数据标记,且一个或多个策略的集合包括提供堆栈保护和防止对包括第一例程的堆栈帧的存储位置的堆栈存储位置的非法(improper)访问的堆栈保护策略。堆栈保护策略可以包括访问第一例程的堆栈帧的第一位置的当前指令的元数据处理中使用的第一规则。如果第一位置具有指示其是第一例程的堆栈位置的元数据且当前指令包括在第一例程中,则第一规则可以允许当前指令的执行。当前指令可以由第一例程的特定起用(invocation)实例使用,且其中,堆栈保护策略可以包括在当前指令的元数据处理中使用的第一规则。如果当前指令包括在第一例程中且也由第一例程的特定起用实例使用,则第一规则可以允许当前指令的执行。第一规则可以包括检查与程序计数器相关联和指示任意授权和能力(capability)的元数据以确定是否允许第一例程的特定起用实例的当前指令的执行。堆栈保护策略可以提供其中单个堆栈帧中的不同对象具有不同颜色的元数据标记的对象级别保护和用于其中单个堆栈帧的多个子对象中的每一个具有不同元数据标记的包括多个子对象的分层对象的分层对象保护中的任意一个。该方法可以包括创建用于新例程调用的新堆栈帧;和根据严格对象初始化或者懒惰对象着色来标记或者着色新堆栈帧的存储器位置,其中,严格对象初始化包括执行初始化处理,该初始化处理执行触发在将信息存储到新堆栈帧之前最初标记新堆栈帧的每个存储器位置的一个或多个规则的元数据处理的一个或多个指令,且其中,懒惰对象着色结合响应于将数据存储到特定存储器位置的指令而触发的规则的元数据处理来标记新堆栈帧的特定存储器位置。该一个或多个策略可以包括规则的集合,用于推行保证仅当在特定调用之后做出时到特定返回位置的返回是有效的动态控制流量完整性策略。第一位置可以包括对包括返回指令的调用例程的调用指令转移控制,且第二位置可以包括第二指令,其中所述第二位置可以指示作为执行调用例程的返回指令的结果,控制被转移到的返回目标位置。该方法可以包括以第一代码标记来标记包括调用指令的第一位置;以第二代码标记来标记指示返回目标位置的第二位置;执行用于以第一代码标记来标记的调用指令的集合的第一规则的元数据处理,其中,用于以第一代码标记来标记的调用指令的第一规则的元数据处理包括以指示返回地址寄存器包括用于第二位置的有效返回地址的有效返回地址标记来标记返回地址寄存器,其中,调用指令的执行更新关于返回地址寄存器的标记以指示返回到第二位置的能力;执行用于调用例程的返回指令的集合的第二规则的元数据处理,如果以有效返回地址能力标记来标记返回地址寄存器,则该调用例程允许返回指令的执行以将控制转移到返回地址寄存器中存储的返回地址,其中,第二规则将返回地址寄存器的有效返回地址性能标记传播到用于在返回指令的运行时间执行之后的下一指令的程序计数器标记;和执行用于在返回指令的运行时间执行之后的用于第二指令的集合的第三规则的元数据处理,其中,如果第二指令具有等于第二代码标记的代码标记且如果程序计数器标记是有效返回地址能力标记,则该第三规则的元数据处理允许第二指令的执行,其中,第三规则清除用于在第二指令的运行时间执行之后的下一指令的程序计数器标记。

根据在这里的技术的另一方面,是处理指令的方法,包括:接收用于在与包括当前指令的代码执行域隔离的元数据处理域中执行的元数据处理的当前指令;和通过与用于当前指令的元数据相关的元数据处理域,根据一个或多个策略的集合来确定是否允许当前指令的执行,其中,该一个或多个策略包括推行从完全序列的第一指令到完全序列的最后指令的以特定次序的指令的完全序列的执行的规则的集合。该方法可以包括将第一共享物理页映射到第一进程(process,处理)的第一虚拟地址空间中;和将第一共享物理页映射到用于第二进程的第二虚拟地址空间中,所述第一共享物理页包括多个存储器位置,其中,多个存储器位置中的每一个与元数据处理域中的规则处理关联地使用的多个全局元数据标记之一相关联。多个全局元数据标记可以指示由至少包括第一进程和第二进程的多个进程共享的元数据标记的集合,且其中,可以对于第一进程和第二进程两者由元数据处理域推行相同策略。由元数据处理域推行相同策略可以使用元数据来允许第一进程执行操作,该操作在另外的情况(otherwise)就不被用于第二进程的相同策略所允许,且其中,程序计数器可以具有关联的程序计数器标记,且关联的程序计数器标记的不同值可以由相同策略的规则使用以允许第一进程执行所述操作,该操作在另外的情况就不被用于第二进程的相同策略所允许。该方法可以包括由应用(application)的分配例程来执行第一处理以使用应用的当前颜色生成用于应用的下一颜色,其中,应用的当前颜色指示用于应用的应用专用(application-specific)颜色序列的当前状态,下一颜色指示用于应用的应用专用颜色序列的下一状态,且当前颜色存储在第一原子单元(atom)上的第一元数据标记中。第一处理可以包括执行第一组一个或多个指令,其中,第一组一个或多个指令触发由元数据处理域使用一个或多个规则的元数据处理,其中,由元数据处理域使用一个或多个规则的元数据处理使用当前颜色生成下一颜色,且通过在第一原子单元的第一元数据标记中存储下一颜色来更新应用的应用专用颜色序列的当前状态。第一组一个或多个指令可以包括在应用的分配例程中,且第一原子单元可以是任意的寄存器和存储器位置。应用专用颜色序列可以是可用于由应用使用的不同颜色的无限制(unbounded)序列,且下一颜色可以存储为由应用使用的一个或多个存储器位置中的每一个的标记值,其中,一个或多个存储器位置可以由分配例程分配。规则的集合可以包括第一规则和第二规则,且其中,指令的完全序列可以包括第一指令和第二指令,且其中,第二指令可以在第一指令之后立即执行。该方法可以包括执行用于第一指令的第一规则的元数据处理,其中,第一规则的元数据处理包括将用于第一指令的运行时间执行之后的下一指令的程序计数器的程序计数器标记设置为特殊标记值;和执行用于第二指令的第二规则的元数据处理,其中,第二规则的元数据处理包括保证仅当用于第二指令的程序计数器的程序计数器标记等于特殊标记时允许第二指令的执行。

根据本发明的另一方面,是包括在其上存储的代码的非瞬时计算机可读介质,所述代码当执行时实现处理指令的方法,包括:接收用于在与包括当前指令的代码执行域相隔离的元数据处理域中执行的元数据处理的当前指令;和通过与用于当前指令的元数据相关的元数据处理域,根据一个或多个策略的集合来确定是否允许当前指令的执行,其中,当前指令访问第一例程的堆栈帧的第一位置,其中,当前指令和堆栈帧的位置具有关联的元数据标记,且一个或多个策略的集合包括提供堆栈保护和防止对包括第一例程的堆栈帧的存储位置的堆栈存储位置的非法访问的堆栈保护策略。

根据在这里的技术的另一方面,是一种系统,包括:处理器;和包括在其上存储的代码的存储器,所述代码当由处理器执行时实现处理指令的方法,包括:接收用于在与包括当前指令的代码执行域相隔离的元数据处理域中执行的元数据处理的当前指令;和通过与用于当前指令的元数据相关的元数据处理域,根据一个或多个策略的集合来确定是否允许当前指令的执行,其中,当前指令访问第一例程的堆栈帧的第一位置,其中,当前指令和堆栈帧的位置具有关联的元数据标记,且一个或多个策略的集合包括提供堆栈保护和防止对包括第一例程的堆栈帧的存储位置的堆栈存储位置的非法访问的堆栈保护策略。

根据在这里的技术的另一方面,是包括在其上存储的代码的非瞬时计算机可读介质,所述代码当执行时实现处理指令的方法,包括:接收用于在与包括当前指令的代码执行域相隔离的元数据处理域中执行的元数据处理的当前指令;和通过与用于当前指令的元数据相关的元数据处理域,根据一个或多个策略的集合来确定是否允许当前指令的执行,其中,该一个或多个策略包括推行从完全序列的第一指令到完全序列的最后指令的以特定次序的指令的完全序列的执行的规则的集合。

根据在这里的技术的另一方面,是一种系统,包括:处理器;和包括在其上存储的代码的存储器,所述代码当由处理器执行时实现处理指令的方法,包括:接收用于在与包括当前指令的代码执行域相隔离的元数据处理域中执行的元数据处理的当前指令;和通过与用于当前指令的元数据相关的元数据处理域,根据一个或多个策略的集合来确定是否允许当前指令的执行,其中,该一个或多个策略包括推行从完全序列的第一指令到完全序列的最后指令的以特定次序的指令的完全序列的执行的规则的集合。

根据在这里的技术的另一方面,是生成和使用元数据标记的方法,包括:在与代码执行域相隔离的元数据处理域中使用的多个指定寄存器的第一指定寄存器中存储自举标记;和执行第一处理以从自举标记推导出一个或多个附加元数据标记,其中,所述第一处理包括执行触发元数据处理域中的一个或多个规则的元数据处理的代码执行域中的一个或多个指令。自举标记可以用作从其推导出由元数据处理域使用的所有其他元数据标记的初始种子标记。自举标记可以硬布线或者存储在只读存储器的一部分中。存储和第一处理可以包括在通过当引导(boot)包括元数据处理域和代码执行域的系统时执行自举程序的第一代码部分而执行的处理中。该方法可以包括从第一指定寄存器中存储的自举标记推导出默认标记;在多个指定寄存器的第二指定寄存器中存储默认标记;和执行触发从第二指定寄存器写入默认标记作为用于由代码执行域使用的多个存储器位置中的每一个的元数据标记的元数据处理域中的规则的元数据处理的指令序列。第一处理可以包括生成从自举标记推导出的元数据标记的初始集合,其中,初始集合的每一个元数据标记可以通过执行触发元数据处理域中的规则高速缓存未命中处理的代码执行域中的当前指令而生成,由此没有规则存在于当前指令的规则高速缓存中,规则高速缓存包括关于由元数据处理域使用以定义允许操作的元数据的规则。规则高速缓存未命中处理可以包括由元数据处理域中执行的规则高速缓存未命中处理器(handler,处理程序)来计算当前指令的新规则,其中,该新规则包括元数据标记的初始集合的结果元数据标记。初始集合的每个元数据标记可以是可以进一步用于推导出其他元数据标记的标记发生器。一个或多个指定指令的第一集合的执行可以触发规则和生成每个元数据标记的元数据处理域中的规则高速缓存未命中处理,该每个元数据标记指示为用于生成一个或多个其他元数据标记的序列的标记发生器,且其中,一个或多个指定指令的第二集合的执行可以触发规则和生成每个元数据标记的元数据处理域中的规则高速缓存未命中处理,该每个元数据标记指示为不能用于进一步生成附加元数据标记的非生成标记。自举程序可以进一步包括触发在元数据处理域中的处理的规则的指令,该规则写入关于指定代码部分的一个或多个指令的一个或多个特殊元数据代码标记以向标记的一个或多个指令提供扩展的特权、能力或者授权。指定代码部分可以包括一个或多个内核程序(kernel)代码和加载器(loader)代码。一个或多个特殊元数据代码标记从元数据标记的初始集合的第一元数据标记推导出,其中,第一元数据标记是特殊指令标记发生器。元数据标记的初始集合可以包括以下的任何一个或多个:作为用于生成用于标记指令的一个或多个代码标记的序列的标记发生器的初始指令元数据标记;作为用于生成一个或多个其他存储分配(malloc)标记发生器的序列的标记发生器的初始存储分配元数据标记,其中,一个或多个其他存储分配标记发生器中的每一个用于生成用于不同应用的一个或多个其他元数据标记的序列,其关于着色任意分配的存储器单元(memory cell)和指向由该不同应用使用的存储器单元的指针;作为用于生成一个或多个其他控制流完整性标记发生器的序列的标记发生器的起始控制流完整性标记,其中,一个或多个其他控制流完整性标记发生器中的每一个用于生成用于不同应用的一个或多个其他元数据标记的序列,其关于标记该不同应用的控制转移目标;和作为用于生成一个或多个其他污点标记发生器的序列的标记发生器的初始污点标记,其中,一个或多个其他污点标记发生器中的每一个用于生成用于不同应用的一个或多个其他元数据污点标记的序列,其关于用元数据污点标记来标记由该不同应用使用的的数据项,其中元数据污点标记基于产生了或者修改了这些数据项的代码。可以通过执行触发元数据处理域中的规则的其他处理的指令来生成元数据标记的序列。其他处理可以包括使用序列中的当前元数据标记来生成序列中的下一元数据标记,其中,当前元数据标记指示序列的当前状态且存储为与原子单元相关联的元数据标记,其中,原子单元是任意的寄存器或者存储器位置;和通过保存下一元数据标记为与原子单元相关联的元数据标记而更新序列的当前状态。

根据在这里的技术的另一方面,是获得用于应用的控制流信息的方法,包括:执行加载用于由处理器的执行的应用的加载器,其中,所述执行加载器包括执行包括触发元数据处理域中的一个或多个规则的第一集合的元数据处理的一个或多个指令的第一代码部分,其中,所述一个或多个规则的第一集合的元数据处理包括收集和存储用于应用的控制流信息作为对元数据处理域可访问和对代码执行域不可访问的应用元数据;和执行代码执行域中的应用的指令,其中,所述执行所述应用的指令触发使用控制流信息的至少一部分以确定是否允许应用中的控制从第一源位置转移到第一目标位置的控制流策略的规则的第二集合的元数据处理。第一目标位置可以具有允许将控制转移到第一目标位置的一个或多个可允许源位置的集合。收集和存储用于应用的控制流信息为应用元数据可以进一步包括执行其他处理的元数据处理域。其他处理可以包括以标识一个或多个可允许源位置的集合的第一元数据来标记第一目标位置,其中,第一元数据存储为应用元数据的控制流信息的一部分。应用的第一指令可以将控制从第一源位置转移到第一目标位置,且第一指令可以触发使用第一元数据以通过确定第一源位置是否包括在允许将控制转移到第一目标位置的一个或多个可允许源位置的集合中而确定是否允许第一指令的执行的控制流策略的一个或多个规则的元数据处理。其他处理还可以包括以唯一源元数据标记来标记集合的每个可允许源位置。每个可允许源位置的每个唯一源元数据标记可以包括在应用的源元数据标记的第一序列中,其中,第一序列可以是从控制流发生器标记生成的源元数据标记的唯一序列。控制流发生器标记可以从由初始自举标记推导出的初始控制流发生器标记生成。初始控制流发生器标记可以用于生成多个附加控制流发生器标记,且其中,每一个附加控制流发生器标记可以用于生成用于不同应用的唯一源元数据标记的序列。

根据在这里的技术的另一方面,是包括在其上存储的代码的非瞬时计算机可读介质,所述代码当执行时实现生成和使用元数据标记的方法,包括:在与代码执行域相隔离的元数据处理域中使用的多个指定寄存器的第一指定寄存器中存储自举标记;和执行第一处理以从自举标记推导出一个或多个附加元数据标记,其中,所述第一处理包括执行触发元数据处理域中的一个或多个规则的元数据处理的代码执行域中的一个或多个指令。

根据在这里的技术的另一方面,是一种系统,包括:处理器;和包括在其上存储的代码的存储器,所述代码当执行时实现生成和使用元数据标记的方法,包括:在与代码执行域相隔离的元数据处理域中使用的多个指定寄存器的第一指定寄存器中存储自举标记;和执行第一处理以从自举标记推导出一个或多个附加元数据标记,其中,所述第一处理包括执行触发元数据处理域中的一个或多个规则的元数据处理的代码执行域中的一个或多个指令。

根据在这里的技术的另一方面,是包括在其上存储的代码的非瞬时计算机可读介质,所述代码当执行时,执行获得用于应用的控制流信息的方法,包括:执行加载用于由处理器的执行的应用的加载器,其中,所述执行加载器包括执行包括触发元数据处理域中的一个或多个规则的第一集合的元数据处理的一个或多个指令的第一代码部分,其中,所述一个或多个规则的第一集合的元数据处理包括收集和存储用于应用的控制流信息为对元数据处理域可访问和对代码执行域不可访问的应用元数据;和执行代码执行域中的应用的指令,其中,所述执行所述应用的指令触发使用控制流信息的至少一部分以确定是否允许应用中的控制从第一源位置转移到第一目标位置的控制流策略的规则的第二集合的元数据处理。

根据在这里的技术的另一方面,是一种系统,包括:处理器;和包括在其上存储的代码的存储器,所述代码当执行时,实现获得用于应用的控制流信息的方法,包括:执行加载用于由处理器执行的应用的加载器,其中,所述执行加载器包括执行包括触发元数据处理域中的一个或多个规则的第一集合的元数据处理的一个或多个指令的第一代码部分,其中,所述一个或多个规则的第一集合的元数据处理包括收集和存储用于应用的控制流信息为对元数据处理域可访问和对代码执行域不可访问的应用元数据;和执行代码执行域中的应用的指令,其中,所述执行所述应用的指令触发使用控制流信息的至少一部分以确定是否允许应用中的控制从第一源位置转移到第一目标位置的控制流策略的规则的第二集合的元数据处理。

根据在这里的技术的另一方面,是用于在标记和未标记数据源之间执行处理器调解(processor-mediated)数据转移的方法,包括:在处理器上执行从未标记数据源加载第一数据的第一指令,所述未标记数据源包括不具有关联的元数据标记的存储器位置;由第一硬件以指示第一数据不可信并且来自公开数据源的第一元数据标记来标记第一数据,其中,具有第一元数据标记的第一数据存储在第一缓存中;和在处理器上执行触发使用第一组一个或多个规则的元数据处理的第一代码,其中,使用第一组一个或多个规则的元数据处理来执行重新标记,所述重新标记重新标记第一数据以具有第二元数据标记,指示第一数据是可信的。第二元数据标记可以另外指示第一数据来自公共源。具有第二元数据标记的第一数据可以存储在作为包括每个具有关联的元数据标记的存储器位置的标记的数据源的存储器中。存储器可以是包括来自一个或多个可信数据源的数据的可信存储器。元数据处理可以在与包括第一代码的代码执行域相隔离的元数据处理域中执行。第一组一个或多个规则可以是关于由元数据处理使用以定义允许操作的元数据的规则。第一代码可以包括一个或多个指令,且该一个或多个指令中的每一个可以具有指示所述每个指令具有起用重新标记第一数据以具有第二元数据标记的一个或多个规则的授权的特殊指令标记。具有第一元数据标记的第一数据可以加密,且该方法可以包括:通过在处理器上执行一个或多个指令来解密具有第一元数据标记的第一数据并生成具有第一元数据标记的第一数据的解密形式;和通过在处理器上执行一个或多个附加指令来执行验证(validation)处理,所述验证处理使用数字签名以保证第一数据的解密形式有效,其中,所述重新标记在第一数据的成功验证处理之后执行。具有第二元数据标记的第一数据可以以解密形式存储在标记存储器的第一存储器位置,且该方法包括加密第一数据以产生以加密形式的第一数据并根据第一数据生成数字签名,其中,所述加密和所述生成通过在处理器上执行附加代码来执行;和在处理器上执行将第一数据的加密形式从标记存储器的第一存储器位置存储到未标记存储器的目的地位置的第二指令,其中,第一数据的加密形式存储在目的地位置中而没有关联的元数据标记,且其中,在目的地位置中存储第一数据的加密形式之前由第二硬件除去第二元数据标记。在第一时间点,第一数据可以存储在未标记存储器部分的第一位置中,且在第二时间点,具有指示第一数据不可信并且来自公开数据源的第一元数据标记的第一数据可以存储在标记存储器部分的第二位置中。未标记存储器部分和所述标记存储器部分可以包括在由同一存储器控制器服务的同一存储器中,且其中,第二元数据处理规则可以仅允许处理器执行将具有指示数据是公共的关联的元数据标记的数据写入到未标记存储器部分的操作,且其中,可以仅允许来自外部未标记源的对未标记数据操作的直接存储器操作来访问同一存储器的未标记存储器部分。第二元数据处理规则的至少一部分可以进一步仅允许处理器执行将具有指示数据是公共的且另外不可信的关联的元数据标记的数据写入到未标记存储器部分的操作。未标记数据源可以连接到仅包括未标记数据源的第一互连结构(interconnect fabric),其中,具有第二元数据标记的第一数据可以存储在连接到仅包括标记数据源的第二互连结构的存储器的位置中。第二处理器可以连接到第一互连结构且可以使用来自未标记数据源的未标记数据来执行其他指令。可以执行其他指令而不执行元数据处理和不使用关于元数据的规则来推行可允许操作,其中,由所述第二处理器执行所述其他指令可以包括执行包括以下任意的一个或多个操作:从第一互连结构的未标记数据源读取数据,和将数据写入到第一互连结构的未标记数据源。

根据在这里的技术的另一方面,是一种系统,包括:处理器;和一个或多个标记存储器,其中,一个或多个标记存储器的每个存储器位置具有关联的元数据标记;包括第一未标记存储器的一个或多个未标记存储器,其中,一个或多个未标记存储器的存储器位置不具有关联的元数据标记;包括关于在执行元数据处理以定义关于指令的允许操作时使用的元数据的规则的规则高速缓存,其中,在由处理器执行当前指令之前,执行使用规则高速缓存的一个或多个规则的元数据处理以确定是否允许当前指令的执行;第一指令,当由处理器执行时,将第一数据从第一未标记存储器加载到由处理器使用的数据高速缓存中,其中,数据高速缓存中存储的第一数据具有关联的第一元数据标记;第二指令,当由处理器执行时,将第二数据从数据高速缓存存储到第一未标记存储器,其中,数据高速缓存中存储的第二数据具有关联的第二元数据标记;第一硬件部件,将未标记数据转换为由处理器在系统中使用的标记数据,其中,响应于第一指令的执行,第一硬件部件从第一未标记存储器接收没有任何关联的元数据标记的第一数据,并输出具有关联的第一元数据标记的第一数据;和第二硬件部件,将标记数据转换为未标记数据,其中,响应于第二指令的执行,第二硬件部件接收具有关联的第二元数据标记的第二数据并输出没有任何关联的元数据标记的第二数据。可以加密没有任何关联的元数据标记的第一数据,且第一硬件部件可以将第一数据转换为解密形式,可以使用数字签名执行第一数据的验证处理,且在成功的验证处理时,可以标记第一数据为具有指示第一数据被可信的关联的第一元数据标记。具有第二关联的元数据标记的第二数据可以以解密形式,且第二硬件部件可以将第二数据转换为加密形式并根据第二数据生成数字签名。第一硬件部件可以标记第一数据为具有指示第一数据被可信且还标识第一数据来自公共源的关联的第一元数据标记。一个或多个密码密钥集合可以是以硬件编码的和存储在存储器中的任何方式。一个或多个密码密钥集合可以由第一硬件部件用于执行解密和验证处理,且可以由第二硬件部件用于执行加密和创建数字签名。第一数据可以标识由第一硬件部件使用以解密第一数据的密码密钥集合中特定的一个,且其中,第二数据的关联的第二元数据标记可以标识由第二硬件部件使用以加密和签名第二数据的密码密钥集合中特定的一个。

根据在这里的技术的另一方面,是处理当前指令的方法,包括:对于元数据处理接收当前指令;和在与包括当前指令的代码执行域相隔离的元数据处理域中执行用于当前指令的元数据处理,所述当前指令参考具有在元数据处理中使用的第一元数据标记的第一存储器位置,所述用于当前指令的元数据处理包括:执行处理以从存储器提取第一元数据标记;在从存储器接收用于第一存储器位置的第一元数据标记之前,确定第一存储器位置的第一元数据标记的预测值;使用第一存储器位置的第一元数据标记的预测值,确定当前指令的结果操作数的第一结果元数据标记;和从存储器接收第一元数据标记;确定第一元数据标记是否匹配第一元数据标记的预测值;和响应于确定第一元数据标记匹配第一元数据标记的预测值,使用第一结果元数据标记作为结果操作数的最终结果元数据标记。用于当前指令的元数据处理可以包括根据当前指令和用于当前指令的输入元数据标记的集合来确定当前指令的第一规则,其中,所述第一规则包括第一存储器位置的第一元数据标记的预测值且包括第一结果元数据标记,所述第一规则包括在用于元数据处理域中的元数据处理的规则高速缓存中;和响应于确定第一元数据标记不匹配第一元数据标记的预测值,执行用于当前指令的元数据处理域中的规则高速缓存未命中处理。用于当前指令的元数据处理域中的规则高速缓存未命中处理可以包括确定是否允许代码执行域中的当前指令的执行;响应于确定允许代码执行域中的当前指令的执行,生成当前指令的新规则,其中,根据当前指令、输入元数据标记的集合和第一元数据标记生成所述新规则;和将新规则插入到用于元数据处理域中的元数据处理的规则高速缓存中。其他输入元数据标记的集合可以包括用于当前指令的多个其他元数据标记,其中所述其他元数据输入标记的集合可以包括用于以下任意的元数据标记:程序计数器、当前指令和当前指令的输入操作数。结果操作数可以是存储执行当前指令的结果的目的存储器位置或者目的地寄存器。可以根据包括第一级和第二级的多个级来处理指令,其中,第一级可以在第二级之前发生。可以在第一级中确定第一存储器位置的第一元数据标记的预测值,且第二级可以包括执行所述确定第一元数据标记是否匹配第一元数据标记的预测值,且第二级还可以包括响应于确定第一元数据标记不匹配第一元数据标记的预测值而执行所述用于当前指令的元数据处理域中的规则高速缓存未命中处理。规则高速缓存可配置为根据预测选择模式以预测模式或者正常处理模式操作。规则高速缓存可配置为当执行用于当前指令的所述元数据处理时以预测模式操作。当规则高速缓存配置为以所述预测模式操作时,规则高速缓存可以根据第一规则生成第一输出。第一输出可以包括用于下一指令的程序计数器的元数据标记,用于当前指令的结果操作数的第一结果元数据标记,和第一元数据标记的预测值作为第一级的输出。当规则高速缓存配置为以所述正常处理模式操作时,规则高速缓存可以根据与第一规则不同的第二规则生成第二输出,其中,第二输出可以不包括第一元数据标记的预测值,且第二输出可以包括用于当前指令的结果操作数和用于下一指令的程序计数器的元数据标记。规则高速缓存可以在以预测模式操作时使用第一策略的规则的第一版本和否则在以正常处理模式操作时可以使用第一策略的规则的第二版本,且其中,第一规则可以包括在规则的第一版本中且第二规则可以包括在规则的第二版本中。

根据在这里的技术的另一方面,是一种系统,包括:包括多个流水线级的流水线处理器,所述多个级包括存储器级和写回级;用于在存储器级的完成之前操作存储器级的集成的元数据处理的可编程单元(PUMP),其中,PUMP执行参考具有在元数据处理中使用的第一元数据标记的第一存储器位置的用于当前指令的元数据处理,其中,PUMP接收包括用于当前指令的第一元数据标记的第一输入,再其中,PUMP生成作为到写回级的输入提供的第一输出,该第一输出包括第一存储器位置的第一元数据标记的预测值和用于当前指令的结果操作数的第一结果元数据标记,其中,第一结果元数据标记由PUMP根据用于第一存储器位置的第一元数据标记的预测值确定;且所述写回级的硬件部件确定用于第一存储器位置的第一元数据标记是否匹配第一元数据标记的预测值,并且当第一元数据标记匹配第一元数据标记的预测值时使用第一结果元数据标记作为用于结果操作数的最终结果元数据标记。PUMP可以是与存储器级同时操作且进一步以预测模式操作,且可以确定第一存储器位置的第一元数据标记的预测值的第一PUMP,且其中,该系统可以包括以正常、非预测模式操作,且可以不确定第一存储器位置的第一元数据标记的任何预测值的第二PUMP。第二PUMP可以集成为存储器级和写回级之间的另一级。第一PUMP可以使用第一策略的规则的第一版本用于当以预测模式操作时使用,且第二PUMP可以使用第一策略的规则的第二版本用于当以正常、非预测模式操作时使用。第一PUMP可以根据来自第一版本的第一规则确定第一输出,且第二PUMP可以根据来自第二版本的第二规则确定第二输出。第二输出可以包括用于第一存储器位置的第二结果元数据标记且所述第二输出可以作为到写回级的输入而提供。写回级的硬件部件可以在第一元数据标记不匹配预测值时另外使用第二结果元数据标记作为用于结果操作数的最后结果元数据标记。

根据在这里的技术的另一方面,是包括在其上存储的代码的非瞬时计算机可读介质,所述代码当执行时实现在标记和未标记数据源之间的处理器调解数据转移的方法,包括:在处理器上执行从未标记数据源加载第一数据的第一指令,所述未标记数据源包括不具有关联的元数据标记的存储器位置;由第一硬件以指示第一数据不可信和来自公开数据源的第一元数据标记来标记第一数据,其中,具有第一元数据标记的第一数据存储在第一缓存中;和在处理器上执行触发使用第一组一个或多个规则的元数据处理的第一代码,其中,使用第一组一个或多个规则的元数据处理执行重新标记,所述重新标记重新标记第一数据以具有第二元数据标记,指示第一数据是可信的。

根据在这里的技术的另一方面,是包括在其上存储的代码的非瞬时计算机可读介质,所述代码当执行时实现处理当前指令的方法,包括:对于元数据处理接收当前指令;和在与包括当前指令的代码执行域相隔离的元数据处理域中执行用于当前指令的元数据处理,所述当前指令参考具有在元数据处理中使用的第一元数据标记的第一存储器位置,所述用于当前指令的元数据处理包括:执行处理以从存储器提取第一元数据标记;在从存储器接收用于第一存储器位置的第一元数据标记之前,确定第一存储器位置的第一元数据标记的预测值;使用第一存储器位置的第一元数据标记的预测值,确定当前指令的结果操作数的第一结果元数据标记;和从存储器接收第一元数据标记;确定第一元数据标记是否匹配第一元数据标记的预测值;和响应于确定第一元数据标记匹配第一元数据标记的预测值,使用第一结果元数据标记作为结果操作数的最终结果元数据标记。

附图说明

在这里的技术的特征和优点将从以下结合附图进行的其示例性实施例的详细说明变得更明显,在附图中:

图1是示出了集成为处理器流水线中的流水线级的PUMP高速缓存的实例的示意图;

图2是示出了PUMP评估框架的示意图;

图3A是示出了具有使用图2示出的评估框架的简单实现的单个运行时间策略的性能结果的图;

图3B是示出了具有简单实现的单个能量策略的性能结果的图;

图4A是示出了具有64b标记的简单实现的合成策略运行时间开销的一系列条形图,其中,合成策略同时推行以下策略(i)空间和时间存储器安全,(ii)污点跟踪,(iii)控制流完整性和(iv)代码和数据分离;

图4B是示出了具有64b标记的简单实现的合成策略能量开销的一系列条形图;

图4C是示出了与基线相比具有简单实现的功率上限的一系列条形图;

图5A是没有操作组优化和具有操作组优化的PUMP规则的数目的比较条形图;

图5B是示出了基于PUMP性能的不同操作组优化的未命中比率的影响的一系列图;

图6A是用于具有复合策略的gcc基准点的每个DRAM转移的唯一标记的分布的图,示出了大多数的字具有相同标记;

图6B是示出了主存储器标记压缩的图;

图7A是示出了16b L2标记和12b LI标记之间的转化的示意性图;

图7B是示出了12b L1标记和16b L2标记之间的转化的示意性图;

图8A是示出了L1标记长度关于L1 PUMP清空(flush)(log10)的影响的示意性图;

图8B是示出了L1标记长度关于L1 PUMP未命中比率的影响的示意性图;

图9A是示出了不同策略的未命中比率的一系列条形图;

图9B是示出四个示例性微架构优化的高速缓存命中比率的线图;

图9C是示出未命中服务性能的线图;

图9D是示出基于性能的未命中处理器命中率的线图;

图9E是示出用于复合策略的优化的影响的一系列条形图;

图10A是示出了优化实现的运行时间开销的一系列图;

图10B是示出了优化实现的能量开销的一系列条形图;

图10C是示出了与基线相比的优化实现的绝对功率的一系列条形图;

图11A是示出不同代表性基准点的标记位长和UCP-高速缓存($)性能的运行时间开销影响的一系列阴影图;

图11B是示出不同代表性基准点的标记位长和UCP-$性能的能量开销影响的一系列阴影图;

图12A是示出了关于代表性的基准点的优化的运行时间影响的一系列图,其中A:简单;B:A+操作分组;C:B+DRAM压缩;D:C+(10b LI,14b,L2)短标记;E:D+(2048-UCP;512-CTAG));

图12B是示出了关于代表性的基准点的优化的能量影响的一系列图,其中A:简单的;B:A+操作分组;C:B+DRAM压缩;D:C+(10b LI,14b,L2)短标记;E:D+(2048-UCP;512-CTAG));

图13A是示出了在代表性基准点的组成中的运行时间策略影响的一系列图;

图13B是示出了在组成中的能源策略影响的一系列图;

图14是提供研究的策略的概况的标为“表1”的第一表;

图15是提供标记方案的分类法的概况的标为“表2”的第二表;

图16是提供对于基线和简单PUMP扩展处理器的存储器资源估计的概况的标为“表3”的第三表;

图17是提供实验中使用的PUMP参数范围的概况的标为“表4”的第四表;

图18是提供PUMP优化处理器的存储器资源估计的概况的标为“表5”的第五表;

图19是提供污点跟踪错误处理器的概况的标为“算法1”的第一算法;

图20是提供N策略未命中处理器的概况的标为“算法2”的第二算法;

图21是提供具有HW支持的N策略未命中处理器的概括的标为“算法3”的第三算法;

图22是PUMP规则高速缓存数据流和微架构的示意图;

图23是PUMP微架构的示意图;

图24是与图1类似的示出了集成为处理器流水线中的流水线级的示例性PUMP高速缓存及其操作组转化、UCP和CTAG高速缓存的示意图;

图25是在根据在这里的技术的实施例中的控制状态寄存器(CSR)的实例;

图26是在根据在这里的技术的实施例中的标记模式的实例;

图27是图示在根据在这里的技术的实施例中的具有单独处理器的单独的元数据处理子系统/域的实例;

图28图示在根据在这里的技术的实施例中的PUMP输入和输出;

图29图示在根据在这里的技术的实施例中的关于操作组表的输入和输出;

图30图示在根据在这里的技术的实施例中由PUMP执行的处理;

图31和图32提供关于在根据在这里的技术的实施例中的PUMP输入和输出的控制和选择的附加细节;

图33是图示在根据在这里的技术的实施例中的6级处理流水流水线的实例;

图34到图38是图示在实施例中的子指令和关联技术的实例;

图39到图42是图示实施例中的字节级标记和关联技术的实例;

图43是图示在根据在这里的技术的实施例中的可变长度操作码的实例;

图44是图示在根据在这里的技术的实施例中的操作码映射表的实例;

图45是图示在根据在这里的技术的实施例中的共享页的实例;

图46是图示在根据在这里的技术的实施例中的控制点转移的实例;

图47是图示在根据在这里的技术的实施例中的调用堆栈的实例;

图48到图49是图示在根据在这里的技术的实施例中的存储器位置标记或者着色的实例;

图50是图示在根据在这里的技术的实施例中的setjmp和longjmp的实例;

图51、图52和图53是在根据在这里的技术的实施例中的不同运行时间行为和关联的防止动作和用于实现防止动作的机制的表;

图54、图55和图56是图示在根据在这里的技术的实施例中可以执行以学习或者确定策略规则的处理的实例;

图57、图58、图59和图60是图示关于数据的外部版本和内部标记版本之间的转换的实施例中的组件的实例;

图61、图62和图63是图示在根据在这里的技术的实施例中的执行标记预测的方面的实例;

图64到图65图示具有实施例中的分配的存储器的在这里的着色存储器位置技术的使用;

图66到图67图示在根据在这里的技术的实施例中的提供硬件规则支持的不同组件;

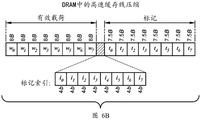

图68到图70是图示PUMP返回值的实施例中在这里的技术的使用的实例;

图71是图示具有指令序列的实施例中的在这里的技术的使用的实例;

图72是在根据在这里的技术的实施例中可以关于引导(boot)系统执行的处理步骤的流程图;

图73是在根据在这里的技术的实施例中关于标记生成的树标记分级的实例;

图74、图75、图76和图77是图示在根据在这里的技术的实施例中关于I/O PUMP的方面和特征的实例;

图78、图79、图80、图81和图82是图示在根据在这里的技术的实施例中关于存储和确定标记值使用的分级的实例;和

图83和图84是图示在根据在这里的技术的实施例中的控制流完整性和关联处理的实例。

具体实施方式

以下段落描述将元数据标记UI系统的主存储器、高速缓存和寄存器中的每个字不可分割地关联的用于元数据处理的可编程单元(PUMP)的各种实施例和方面。为支持无限制的元数据,标记足够大以对存储器中的数据结构是间接的。关于每个指令,输入的标记用于确定是否允许操作,且如果允许操作则计算结果的标记。在一些实施例中,以软件定义标记检查和传播规则。但是,为最小化性能影响,这些规则高速缓存在硬件结构中,即PUMP规则高速缓存,其与处理器的运算逻辑单元(ALU)部分并行操作。在一些实施例中,比如可以使用软件和/或硬件实现的未命中处理器可以用于基于当前生效的策略来服务高速缓存未命中。

在使用四个不同策略的组成的至少一个实施例中,可以以不同方式强调PUMP来度量(参见图14)PUMP的性能影响和图示安全性属性的范围,例如,(1)使用标记区分来自存储器中的数据的代码和提供相对简单代码注入攻击的保护的非可执行数据和非可写代码(NXD+NWC)策略;(2)检测堆分配存储器中的所有空间和时间侵害的存储器安全策略,以实际上无限的(260)颜色的数目(“污点记号”)扩展;(3)限制仅到程序的控制流图中的允许的边缘的间接控制转移的控制流完整性(CFI)策略,防止面向返回的编程风格攻击(推行细粒度CFI,不是对攻击潜在地脆弱的粗粒度的近似);和(4)细粒度的污点跟踪策略(一般化),其中每个字可以潜在地同时由多个源(库和IO流)污染。

前述是可以在根据在这里的技术的实施例中使用的公知策略的实例。对于这种其保护性能已经在文献中建立的公知策略,在这里的技术可以用于推行这种策略同时还减小使用PUMP推行它们的性能影响。除了NXD+NWC之外,这些策略中的每一个需要区分实质上无限数目的唯一项;相反,具有有限数目的元数据位的解决方案最好也仅可以支持粗略简化的近似。

如在这里的其他地方所示和所述的,根据在这里的技术的一个实施例可以利用PUMP的简单的直接实现,其使用指针大小(64b或者字节)的标记到64b字由此至少将系统中的所有存储器的大小和能量使用翻倍。规则高速缓存在此之上添加面积和能量。对于该特定实施例,测量到190%(参见图16)的面积开销和大约220%,的几何平均(geomean)能量开销。此外,在一些应用上运行时间开销可以在300%以上。这种高开销可能阻碍采用,如果它们是可以做到的最好的话。

但是,如以下更详细地描述的,大多数的策略展现对于标记和在其上定义的规则两者的空间和时间局部性。因此,根据在这里的技术的实施例可以通过在一组类似的(或甚至相同的)指令上定义唯一规则,减小强制性未命中和增加规则高速缓存的有效容量而显著地减小唯一规则的数目。可以通过利用标记中的空间局部性减小离片(off-chip)存储器业务量。可以通过使用少量位表示在某一时间使用中的指针大小的标记的子集来最小化片上面积和能量开销。可以通过提供用于高速缓存部件策略的硬件支持来减小复合策略未命中处理器的运行时间成本。因此,根据在这里的技术的实施例可以包括这种优化以由此允许PUMP实现较低开销而不牺牲其丰富的策略模型。

根据在这里的技术的实施例可以用可用于编码任意数目的安全性策略的元数据来增强存储器字和内部处理器状态,所述安全性策略可以隔离地或者同时地推行。根据在这里的技术的实施例可以通过将与数据流并行工作以推行任意策略集合的元数据处理单元(PUMP)添加到“传统的”处理器(例如,RISC-CPU、GPU、向量处理器等)来实现前述;本公开的技术具体地使得元数据无限制和软件可编程,以使得在这里的技术可以被采用和应用于各种各样的元数据处理策略。例如,PUMP可以集成为传统的(RISC)处理器的新/分开的流水线级,或者可以集成为与“主机”处理器并行地工作的分立硬件。对于前一情况,可能有指令级模拟器、精致策略、实现优化和资源估计,和特性化设计的大范围模拟。

尝试以精细(即,指令)粒度级别推行策略的现有解决方案不能推行任意策略集合。通常,仅可以在指令级别推行少量的固定策略。在较高粒度级别(即线程)推行策略不能防止某些类别的面向返回的编程攻击,因此使得该类型的推行在其有用性上有限。相反,根据在这里的技术的实施例允许可以单独地或者同时地在指令级别推行的无限数目的策略的表达(唯一限制是大小地址空间,因为关于可以指向任何任意数据结构的地址指针来表示元数据)。

应当注意,在以下段落中描述的各个图图示在这里描述的技术的各个方面的各种实例、方法及其他示例实施例。将理解在这种图中,图示的元素边界(例如,框、框的组或者其他形状)通常表示边界的一个实例。本领域技术人员将理解在某些实例中,一个元素可以设计为多个元素或者多个元素可以设计为一个元素。在某些实例中,示为另一元素的内部组件的元素可以实现为外部组件,反之亦然。此外,元素可以不按比例描绘。

参考图1,用于元数据处理的可编程单元(PUMP)10集成到现有的精简指令集计算或者计算机(RISC)处理器12中,其具有依序实现和适于能耗敏感(energy-conscious)应用的5-级流水线,其实际上以PUMP 10的附加转换为6-级流水线。第一级是读取级14,第二级是解码级16,第三级是执行级18,第四级是存储器级20,且第五级是写回级22。PUMP 10介入存储器级20和写回级22之间。

各种实施例可以使用作为提供策略推行和元数据传播的机制的电子逻辑来实现PUMP 10。PUMP 10的实施例可以由以下表征:(i)关于在四个不同策略及其组合下的基准点的标准集合的PUMP 10的简单实现的运行时间、能量、功率上限和面积影响的经验评估;(ii)微架构的优化的集合;和(iii)来自这些优化的增益的量度,示出了在10%以下的典型的运行时间开销,10%的功率上限影响,和典型地通过使用片上存储器结构的110%附加面积在60%以下的能量开销。

在计算中,基准设置可以表征为通常通过对其运行多个标准测试和试验而运行计算机程序、程序的集合或者其他操作的动作,以评估对象的相对性能。在这里使用的术语“基准点(benchmark)”指的是基准设置程序本身。贯穿本申请和附图使用的基准点程序的类型是GemsFDTD、astar、bwaves、bzip2、cactusADM、calculix、deall、gamess、gcc、gobmk、gromacs、h264ref、hmmer、Ibm、leslie3d、libquantum、mcf、mile、namd、omnetpp、perlbench、sjeng、specrand、sphinx3、wrf、zeusmp和mean。例如,参见图10A、图10B和图10C。

如在此使用的,“逻辑”包括但不限于执行一个或多个功能或者一个或多个动作,和/或导致来自另一逻辑、方法和/或系统的功能或者动作的硬件、固件、软件和/或每个的组合。例如,基于期望应用或者需要,逻辑可以包括软件控制微处理器、类似处理器(例如,微处理器)的离散逻辑,专用集成电路(ASIC)、编程逻辑器件、包括指令的存储器装置、具有存储器的电气设备等。逻辑可以包括一个或多个门,门的组合或者其他电路组件。逻辑还可以完全具体实现为软件。在描述多个逻辑时,可以将多个逻辑包括在一个物理逻辑中。类似地,在描述单个逻辑时,可以在多个物理逻辑之间分布单个逻辑。

在根据在这里的技术的至少一个实施例中,PUMP 10可以表征为对现有的RISC处理器12的扩展。以下段落提供构成可以在根据在这里的技术的实施例中使用的PUMP的10硬件接口层、基本微架构改变和伴随底层软件的ISA(指令集架构)级别扩展的更多细节。

在根据在这里的技术的实施例中,充实了PUMP的系统中的每个字可以与指针-大小标记相关联。这些标记在硬件级是未解释的。在软件级别,如策略所定义的,标记可以表示无限制大小和复杂性的元数据。仅需要较少位的元数据的较简单策略可以直接在标记中存储元数据;如果需要更多位,则间接(indirection)用于存储元数据为存储器中的数据结构,其中该结构的地址用作标记。值得注意,这些指针-大小标记是本公开的一个示例性方面且不被考虑为限制。基本可访问存储器字是以标记不可分割地扩展,使得包括存储器、高速缓存和寄存器的所有值隙(value slot)适当地更宽。还标记程序计数器(PC)。该软件定义元数据的概念(notion)及其作为指针-大小标记的表示扩展了先前的标记方法,其中仅较少位用于标记和/或它们是硬布线到固定的解释。标记方案的一些示例性分类法在图15中再现的表2中表示。

元数据标记不可由用户程序寻址。而是,元数据标记由关于如以下详述的根据规则高速缓存未命中调用的策略处理器来寻址。通过PUMP 10规则实现对标记的所有更新。

除无限制的元数据之外,根据在这里的技术的PUMP 10的实施例的另一特征是用于关于元数据的单循环公共情况计算的硬件支持。关于形式操作码的规则来定义这些计算:(PC,CI,OP1,OP2,MR)=>(PCnew,R),其应该读为:“如果当前操作码是操作码,关于程序计数器的当前标记是PC,关于当前指令的标记是CI,关于其输入操作数(如果有的话)的标记是OP1和OP2,且关于存储器位置的标记(在加载/存储的情况下)是MR,则在下一机器状态中关于程序计数器的标记应该是PCnew,且关于指令结果的标记(目的地寄存器或者存储器位置,如果有的话)应该是R”。该规则格式允许从多达五个输入标记计算两个输出标记,显著地比在先前工作中考虑的更灵活,先前工作典型地从多达两个输入计算一个输出(参见图15中的表2)。超出仅跟踪数据标记(OP1、OP2、MR、R)的先前解决方案,本公开提供可以用于跟踪和推行代码块的出处(provenance)、完整性和使用的当前指令标记(CI);以及可以用于记录包括隐含信息流的执行历史、环境授权和“控制状态”的PC标记。CFI策略利用用于记录间接跳转(jump)的源的PC标记和用于标识跳转目标的CI标记,NXD+NWC平掌控(leverge)CI以推行该数据不可执行,且污点跟踪使用CI以基于生产其的代码来污染(taint)数据。

为解析公共情况中的单个周期中的规则,根据在这里的技术的实施例可以使用最近使用的规则的硬件高速缓存。取决于指令和策略,可以不使用给定规则中的一个或多个输入隙(input slot)。为避免以用于未使用的隙的所有可能值的规则破坏高速缓存,规则高速缓存查找逻辑参考包括用于每个输入隙-操作码对的“不关心”(参见图1)位的位向量,其确定在规则高速缓存查找表(lookup)中是否实际上使用了相应标记。为高效地处理这些“不关心”输入,在向PUMP 10呈现输入之前将它们掩盖。该不关心位矢量由作为未命中处理器安装的一部分的特权指令来设置。

图1总地图示根据在这里的技术的一个实施例,其具有包括PUMP 10硬件的修改的5-级处理器12流水线。添加规则高速缓存查找表作为附加级并独立地旁路标记和数据,以使得PUMP 10级不在处理器流水线中创建附加的停顿(stall)。

放置PUMP 10作为单独的级(在存储器级20和写回级22之间)针对将关于从存储器读取(加载),或者要在存储器中重写(存储)的字的标记作为到PUMP 10的输入提供的需要而提出的。因为允许规则取决于正在写入的存储器位置的现有标记,写入操作成为读取-修改-写入操作。类似读取规则在存储器级20期间读取现有标记,在PUMP 10级中检查读取规则,且在也可以被称为写回级22的提交(commit)级期间执行写入。如任何高速缓存方案那样,多级高速缓存可以用于PUMP 10。如以下更详细地描述的,根据在这里的技术的实施例可以利用二级高速缓存。对多级高速缓存的扩展是对本领域技术人员显而易见的。

在一个非限制实例中,当在写回级22中的规则高速缓存中发生最后级未命中时,如下处理:(i)仅用于该目的的处理器寄存器的(新)集合中保存当前操作码和标记,和(ii)控制转移到策略未命中处理器(以下更加详细地描述),其(iii)决定是否允许操作和如果允许操作则生成适当的规则。当未命中处理器返回时,硬件(iv)将该规则安装到PUMP 10规则高速缓存中,且(v)重新发布故障指令。为提供特权未命中处理器和系统软件和用户代码中的其余之间的隔离,未命中处理器操作模式被添加到处理器,由关于规则高速缓存未命中设置和当未命中处理器返回时复位的在处理器状态中的位来控制。为避免关于每个规则高速缓存未命中保存和恢复寄存器的需要,可以以仅可用于未命中处理器的16个附加寄存器来扩展整数(integer)寄存器文件。另外,规则输入和输出在未命中处理器模式时表现为寄存器(对比的,寄存器窗口),允许未命中处理器(但是不允许别的)将标记操纵为普通值。再次,这些都是写回级22的非限制实例。

添加新未命中-处理器-返回指令以结束将规则安装到PUMP 10规则高速缓存中和返回到用户代码。在该特定的非限制实例中,该指令可以仅当在未命中-处理器模式下时发布。当在未命中-处理器模式时,忽略规则高速缓存且代替地PUMP 10应用单个硬布线的规则:由未命中处理器接触的所有指令和数据必须以预定义的MISSHANDLER(未命中处理器)标记来标记,且给所有指令结果以相同标记。以这种方式,PUMP 10架构防止用户代码破坏由策略提供的保护。替代地,PUMP可以用于推行关于未命中-处理器访问的灵活规则。标记不是可分的、可寻址的或者可由用户代码替代的;元数据数据结构和未命中处理器代码不能由用户代码接触;且用户代码不能直接将规则插入到规则高速缓存中。

参考图19,算法1图示对于污点跟踪策略的未命中处理器的操作。为最小化不同标记(且因此规则)的数目,未命中处理器通过“规范化(canonicalizing)”其建造的任何新数据结构来使用用于逻辑等效元数据的单个标记。

不是强迫用户选择单个策略,而是同时推行多个策略且之后添加新的策略。对这些“无限制”标记的示例性优点是它们可以同时推行任意数目的策略。这可以通过让标记是指向来自几个组成策略的标记的元组(tuple)的指针来实现。例如,为组合NXD+NWC策略与污点跟踪策略,每个标记可以是指向元组(s,t)的指针,其中s是NXD+NWC标记(DATA(数据)或者CODE(代码))且t是污点标记(到污点的集合的指针)。规则高速缓存查找表是类似的,但是当发生未命中时,分开地评估两个组成策略:仅当两个策略都允许操作时才允许操作,且产生的标记是来自两个组成策略的结果对。但是,在其他实施例中,可以表示要怎样组合策略(不是简单地是所有组成部分之间的AND(与))。

参考图20,算法2示出对于任何N个策略的复合未命中处理器的通用行为。取决于元组中的标记怎样关联,这可能导致标记且由此规则的数目的大的增加。为了表明同时支持多个策略和度量其关于工作集大小的效果的能力,通过实验实现复合策略(“复合(composite)”),且复合策略包括上面描述的所有四个策略。复合策略表示以下进一步详细描述的支持的策略工作负荷的种类。如在图4A和图20中看到的,复合策略同时推行以下策略(i)空间和时间存储器安全,(ii)污点跟踪,(iii)控制流完整性和(iv)代码和数据分离。

大多数策略在操作码上分派以选择适当的逻辑。类似NXD+NWC的某些策略将仅检查是否允许操作。其他的可以查阅数据结构(例如,CFI策略查阅允许的间接调用的图和返回id)。存储器安全检查地址颜色(即,指针颜色)和存储器区域颜色之间的相等性。污点跟踪通过组合输入标记(Alg 1)计算新鲜的结果标记。必须访问大的数据结构(CFI)或者跨越大的集合(污点跟踪,复合)规范化的策略可以做出将在片上高速缓存中未命中的许多存储器访问并去到DRAM。在跨越全部基准点的平均上,NXD+NWC的服务未命中需要30个循环,存储器安全需要60个循环,CFI需要85个循环,污点跟踪需要500个循环,且复合需要800个循环。

如果策略未命中处理器确定不允许操作,则其调用适当的安全性故障处理器。该故障处理器做什么取决于运行时间系统和策略;典型地,它将关闭违规处理,但是在有些情况下它可以代替地返回适当的“安全值”。对于以UNIX-风格操作系统的增加的部署,每个进程(process)应用假定的策略,允许每个进程得到不同的策略集合。每个进程应用的叙述是非限制的而是示例性的,且本领域技术人员认可这一点。它还允许我们将标记、规则和未命中处理支持放置到进程的地址空间中,避免OS-级别上下文切换的需要。长期来讲,可能的PUMP策略也可以用于保护OS。

以下使用图1示出的128b字(64b有效载荷和64b标记)和修改的流水线处理器12,详述用于测量运行时间、能量、面积和功率开销的评估方法,且将其应用在PUMP硬件和软件的简单实现上。首先描述和测量多个PUMP实现是有用的,即使优化实现是开销(相对于基线处理器)最终期望的版本。描述两者,因为其详述在变成更多复杂的版本之前的关键机制的基本版本。

为估计PUMP的物理资源影响,主要地聚焦于存储器成本,因为存储器是在简单的RISC处理器和在PUMP硬件扩展中的主要的面积和能量消费者。对于L1存储器(参见图1)考虑32nm低工作功率(LOP)处理,且对于L2存储器考虑低备用功率(LSTP),且32nm低工作功率(LOP)处理使用CACTI 6.5用于建模主存储器和处理器片上存储器的面积、访问时间、每个访问的能量和静态(泄漏)功率。

基线处理器(没有-PUMP)具有用于数据和指令的单独的64KB L1高速缓存和统一的512KB L2高速缓存。使用延迟优化的L1高速缓存和能量优化的L2高速缓存。所有高速缓存使用写回纪律。基线L1高速缓存具有大约880ps的等待时间;假定它可以在一个循环返回结果且将其时钟设置为1ns,给定可与现代的嵌入式和蜂窝电话处理器相比的1GHz周期目标。在图16中的表3中呈现用于该处理器的参数。

PUMP规则高速缓存10硬件实现的一个实施例可以包括两个部分:以标记在级14、16、20扩展所有架构状态,和将PUMP规则高速缓存添加到处理器12。以64b标记扩展片上存储器中的每64b字增加它们的面积和每个访问的能量并恶化它们的访问等待时间。这对于L2高速缓存是潜在地可容忍的,L2高速缓存已经具有多周期访问等待时间且不是每个周期都使用。但是添加额外周期的等待时间给访问L1高速缓存(参见图1)可能导致流水线中的停顿。为避免此,在该简单实现中,L1高速缓存的有效容量减小到在基线设计中的一半且然后添加标记。这给出对L1高速缓存的相同的单周期访问,但是可能由于增加的未命中而恶化性能。

在根据在这里的技术的实施例中,与传统的高速缓存地址密钥(小于地址宽度)相比,PUMP规则高速缓存10利用长匹配密钥(5个指针-大小标记加指令操作码,或者328b),并返回128b结果。在一个实施例中,可以使用完全关联的L1规则高速缓存,但是将导致高能量和延迟(参见图16中的表3)。作为替代,根据在这里的技术的实施例可以利用以四个散列(hash,哈希)函数激发的多散列高速缓存方案,如图22所示。L1规则高速缓存设计用于在单个周期中产生结果,在第二周期中检查假命中,当L2规则高速缓存设计用于低能量时,给出多周期访问等待时间。再次,图16中的表3示出了简单实现中使用的的1024-项L1和4096-项L2规则高速缓存的参数。当这些高速缓存达到容量时,使用简单先入先出(FIFO)替换策略,其看来对当前工作负荷实际上工作良好(这里FIFO在LRU的6%之内)。

参考图2,PUMP的性能影响的估计标识ISA、PUMP和地址-轨迹模拟器的组合。gem5模拟器24生成关于64位Alpha基线ISA的SPEC CPU2006程序的指令轨迹(省略在其上gem5失败的xalancbmk和tonto)。每个程序模拟以上列出的四个策略中的每一个和用于IB指令的预热时段的复合策略且然后评估下一500M指令。在gem5模拟器24中,每个基准点在基线处理器上运行而没有标记或者策略。产生的指令轨迹26然后运行通过执行每个指令的元数据计算的PUMP模拟器28。该“调相的”模拟策略对于失败-停止策略是精确的,在失败-停止策略中PUMP的结果不能导致程序的控制流偏离其基线执行。当地址-轨迹模拟可能对于高度流水线的和非依序(out-of-order)的处理器是不精确的时,它们对于简单的依序(in-order)5和6-级流水线是相当精确的。关于基线配置,之后是地址模拟器32中的定制地址-轨迹模拟和记账的gem5指令模拟和地址轨迹生成30在gem5的周期-精确模拟的1.2%之内。

PUMP模拟器28包括实现每个策略的未命中-处理器代码(以C语言写的),且取决于策略给初始存储器分配元数据标记。PUMP模拟器28允许在PUMP 10规则高速缓存中捕获访问模式和估计关联的运行时间和能量成本,说明需要长的等待周期来访问L2规则高速缓存。因为具有未命中处理器代码的PUMP模拟器28还在处理器上运行,用于关于gem5的未命中处理器的单独的模拟捕获其动态行为。因为未命中-处理器代码潜在地影响数据和指令高速缓存,创建合并的地址轨迹,其包括来自用户和未命中-处理器代码两者的适当地交织的存储器访问,该未命中-处理器代码最终地址-轨迹模拟以估计存储器系统的性能影响。

在以下段落中,与非-PUMP基线相比提供单PUMP的评估。

作为评估的一点,应当注意在基线处理器之上的PUMP 10的总的面积开销是190%(参见图16中的表3)。该面积开销的主要部分(110%)来自PUMP 10规则高速缓存。统一的L2高速缓存贡献大部分的剩余面积开销。L1 D/I高速缓存保持大致相同,因为它们的有效容量被减半。该高存储器面积开销大致为三倍静态功率,贡献24%的能量开销。

评估的另一点涉及运行时间开销。对于关于大多数基准点的所有单个策略,即使该简单实现的平均运行时间开销也仅是10%(参见图3A和图3B;读箱型图:条是中值,箱型覆盖以上和以下各一个四分位数(中间50%的情况),点表示每个单独的数据点,须线指示除了非正常值(多于1.5×各个四分位数)之外的全范围),其中主要的开销来自将标记位转移到处理器和从处理器转移需要的附加DRAM业务量。对于存储器安全策略(图3A和图3B),存在展现高未命中处理器开销的几个基准点,由于关于新分配的存储器块的推行未命中,推动它们的总和开销多达40-50%。对于复合策略运行时间(在附图中标为“CPI”或者“CPI开销”),五个基准点遭受未命中处理器中的非常高的开销(参见图4A),其中最坏情况在GemsFTDT中接近780%,且几何平均达到50%。对于在图4B中示出的复合策略能量(在附图中标为“EPI”或者“EPI开销”),三个基准点(即,GemsFTDT、astar、omnetpp)遭受未命中处理器中的非常高的开销,其中最坏情况在GemsFTDT中接近于1600%,在astar中接近于600%,且在omnetpp中接近于520%。

两个因素贡献于该开销:(1)解析最后级别规则高速缓存未命中需要的大量周期(因为必须查询每个组成未命中处理器),和(2)扩展工作集合大小和增加规则高速缓存未命中率的规则的数目的激增。在最坏情况下,唯一复合标记的数目可以是每个组成策略中的唯一标记的积。但是,总的规则在最大单个策略,存储器安全之上增大3x-5x的因数。

评估的另一点是能量开销。由于更宽的字移动更多位,和由于未命中处理器代码执行更多指令,两者都贡献能量开销,影响单个和复合策略两者(图3B和图4B)。CFI和存储器安全策略且因此复合策略访问通常需要耗费能量的DRAM访问的大的数据结构。最坏情况的能量开销对于单个策略接近400%,且对于复合策略是大约1600%,其中几何平均开销大约是220%。

对于许多平台设计,最坏情况功率,或者相等地,每个周期的能量是限制器。该功率上限可以由平台可以从电池汲取的最大电流或者在移动装置或者具有环境冷却的有线装置中的最大维持操作温度来驱动。图4C示出了简单实现以在基线和单PUMP实现两者中驱动最大功率的lbm将最大功率上限提升76%。注意到,该功率上限增加低于最坏情况能量开销,部分地因为某些基准点多于它们耗费的额外能量地减慢,且部分地因为具有高能量开销的基准点是在基线设计中每个周期消耗最少绝对能量的基准点。典型地这些能量高效程序的数据工作集合适配片上高速缓存,这样它们很少付出DRAM访问的高成本。

包括上面描述的前述实现的实施例关于大多数基准点实现合理的性能,关于它们中的某些的复合策略的运行时间开销和关于所有策略和基准点的能量和功率开销看来不可接受地高。为解决这些开销,可以引入一系列目标微架构优化且包括在根据在这里的技术的实施例中。在图17的表4中,关于总成本对于与PUMP组件相关联的架构参数的影响来检查这些优化。具有相同规则的操作码的分组用于增加PUMP规则高速缓存的有效容量,标记压缩用于减小DRAM转移的延迟和能量,短标记用于减小片上存储器中的面积和能量,和统一组件策略(UCP)和组成标记(CTAG)高速缓存用于减小未命中处理器中的开销。

现在将描述的是可以在根据在这里的技术的实施例中使用的“操作组”。在实际策略中,对于几个操作码定义类似规则是普遍的。例如,在污点跟踪策略中,用于Add(加)和Sub(减)指令的规则相同(参见图19中的算法1)。但是,在简单实现中,这些规则占用规则高速缓存中的单独的项(entry)。基于该观察,将指令操作码(“操作码”)以相同规则分组为“操作组”,减小需要的规则的数目。哪些操作码可以被分组在一起取决于策略;因此在执行级18(图1)扩展“不关心”SRAM以在规则高速缓存查找之前将操作码转译为操作组。对于复合策略,300以上的Alpha操作码减小为14个操作组,且规则总数减小因数1.1×-6×。平均是1.5×(图5A测量跨越所有SPEC基准点的效果)。这有效地增加了硅面积中给定投资的规则高速缓存容量。操作组还减小强制性未命中的数目,因为关于组中的单个指令的未命中而安装应用于组中的每个指令操作码的规则。图5B概述对于具有和没有操作分组的复合策略的不同L1规则高速缓存大小的跨越所有SPEC基准点的未命中率。图5B示出了由操作分组减小的未命中率的范围和平均两者。特别地,在操作组优化之后的1024-项规则高速缓存具有比没有它的4096-项规则高速缓存更低的未命中率。较低的未命中率自然地减小了在未命中处理器中花费的时间和能量(参见图12A和图12B),且较小的规则高速缓存直接减小面积和能量。

根据在这里的技术的实施例可以利用现在将描述的主存储器标记压缩。使用关于64b字的64b标记加倍离片存储器业务量且因此近似地加倍关联的能量。虽然典型地,标记展现空间局部性-许多相邻字具有相同标记。例如,图6A绘出具有复合策略的gcc基准点的每个DRAM转移的唯一标记的分布,示出了大多数字具有相同标记:平均起来8字高速缓存线的每个DRAM转移仅有大约1.14个唯一标记。利用该空间标记局部性来压缩必须转移到离片存储器和从离片存储器转移的标记位。因为在高速缓存线中转移数据,高速缓存线用作该压缩的基础。在主存储器中分配每个高速缓存线128B以保持寻址简单。

但是,如图6B所示,不是直接存储128b标记的字,而是存储八个64b字(有效载荷),后面是八个4b索引,且然后多达八个60b标记。索引标识哪个60b标记与关联的字一起。标记被缩减到60b以容纳索引,但是这并不牺牲标记作为指针的使用:假定字节寻址和16B(两个64b字)对准的元数据结构,64b指针的低4b可以填充为零。结果,在转移索引的4B之后,所有剩余的是需要在高速缓存线中转移唯一7.5B标记。例如,如果由高速缓存线中的所有字使用相同标记,则在第一读取中存在64B+4B=68B的转移,然后第二读取中是8B,总共76B代替128B。该4b索引可以是直接索引或者特殊值。定义特殊索引值以表示默认标记,以使得在该情况下不需要转移任何标记。通过以该方式压缩标记,每个DRAM转移的平均能量开销从110%减小到15%。

例如,由于其在减小离片存储器能量方面的简单性和有效性的组合,可以在根据在这里的技术的实施例中使用以上呈现的压缩方案。本领域技术人员清楚地认可用于细粒度存储器标记的附加的替换巧妙方案存在-包括多级标记页表、变量-粒度TLB-类结构和范围高速缓存-且这些也可以用于减小在根据在这里的技术的实施例中的DRAM占用空间(footprint)。

现在将描述的是怎样在根据在这里的技术的实施例中执行标记转译。再次参考图1,简单PUMP规则高速缓存很大(添加110%面积),因为每个高速缓存规则是456b宽。支持PUMP 10还需要以64b标记扩展基线片上存储器(RF和L1/L2高速缓存)。这里使用用于每个64b字的完全64b(或者60b)标记导致重的面积和能量开销。但是,64KB Ll-D$仅保存8192字且由此至多保存8192个唯一标记。与64KB Ll-I$一起,在L1存储器子系统中可能有至多16384个唯一标记;这些可以仅以14b标记表示,减小系统中的延迟、面积、能量和功率。高速缓存(L1、L2)存在以利用时间局部性,且该观察提出可以利用局部性以减小面积和能量。如果标记位减小到14b,则PUMP规则高速缓存匹配密钥从328b减小到78b。

为获得前述节省优点而不损失完全指针大小标记的灵活性,不同宽度标记可以用于不同片上存储器子系统和按照需要在这些之间转译。例如,一个可以在L1存储器中使用12b标记和在L2存储器中使用16b标记。图7A详述可以在L1和L2存储器子系统之间执行的标记转译。将字从L2高速缓存34移动到L1高速缓存36需要将其16b标记转译为相应的12b标记,如果需要创建新的关联。对于L2-标记到L1-标记转译的简单SRAM 38具有指示是否存在用于L2标记的L1映射的额外位。图7B详述使用L1标记作为地址的以SRAM 39查找表执行的L1标记40到L2标记42(关于写回或者L2查找表)的转译。类似的转译在60b主存储器标记和16b L2标记之间发生。

当长标记不在长短转译表中时,分配新的短标记,潜在地收回不再使用中的先前分配的短标记。存在丰富的设计空间来研究确定何时收回短标记,包括无用单元收集和标记使用计数。为简单起见,短标记被顺序地分配和当短标记空间耗尽时在给定级别以上(指令,数据和PUMP)清空(flush)所有高速缓存,避免跟踪何时特定短标记可用于收回的需要。可以以使得高速缓存便宜地清空的适当的技术设计高速缓存。例如,在根据在这里的技术的实施例中,可以以轻量群组清除(lightweight gang clear)明确设计所有高速缓存,如本领域已知的,和例如在K.Mai,R.Ho,E.Alon,D.Liu,Y.Kim,D.Patil和M.Horowitz,Architecture and Circuit Techniques for a 1.1GHz 16-kb Reconfigurable Memoryin 0.18um-CMOS.IEEE J.Solid-State Circuits,40(1):261-275,2005年1月中描述的,将其通过引用包括在这里。

与表3(在图16中再现)相比,其中每个L1规则高速缓存访问成本51pJ,提供在这里的技术用于以8b L1标记减小到10pJ或者以16b L1标记减小到18pJ,其中能量随着这些点之间的标记长度线性地缩放。能量对L1指令和数据高速缓存的影响很小。类似地,对于16bL2标记,L2 PUMP访问成本120pJ,从以64b标记的173pJ下降。瘦L1标记也允许我们恢复L1高速缓存的容量。对于12b标记,全容量(76KB,有效的64KB)高速缓存将满足单循环定时要求,减小了简单实现由减小的L1高速缓存容量导致的性能代价。结果,L1标记长度研究限于12位或者更少。虽然即使短标记也减小能量,但是它们也增加清空的频率。

图8A和图8B示出清空怎样随增加L1标记长度而减少,以及对L1规则高速缓存未命中率的影响。

现在将描述的是可以关于未命中处理器加速使用的各种技术。根据在这里的技术的实施例可以将四个策略组合为单个复合策略。参考图20,在算法2中,N-策略未命中处理器的每个调用必须拆开标记的元组,且复合策略需要的规则增加规则高速缓存未命中率,这在图9A中标识。即使污点跟踪和CFI策略单独地具有低未命中率,来自存储器安全策略的较高未命中率也驱动复合策略的未命中率高。单独策略的较低未命中率提示它们的结果可以是可缓存的,即使当复合规则不是可缓存的。

关于比如图23中图示的PUMP微架构的各个方面,可以使用硬件结构以优化复合策略未命中处理。根据在这里的技术的实施例可以利用统一组件策略(UCP;参见图21中的算法3)高速缓存(UCP$),其中高速缓存最近的组件策略结果。在这种实施例中,修改用于合成策略的一般未命中处理器以当解析组件策略(例如,参见图21的算法3,这种在线3)时在该高速缓存中执行查找。当该高速缓存对于组件策略未命中时,以软件执行其策略计算(且在该高速缓存中插入结果)。

也在图24中图示,可以以与常规PUMP规则高速缓存相同的硬件体系结构实现UCP高速缓存,具有附加的策略标识符字段。FIFO替换策略可以用于该高速缓存,但是可以通过使用比如用于组件策略的重新计算成本的量度来优先化空间而实现最好的结果。对于适度容量,该高速缓存滤出大多数策略重新计算(图9B;存储器安全的低命中率由与新存储器分配相关联的强制性未命中驱动)。结果,未命中处理器周期的平均数对于最有挑战的基准点减小因数5(图9E)。当在L2 PUMP中存在未命中时,对于每个策略可以在UCP高速缓存中命中,因为需要的复合规则可能是少量组件策略规则的积。对于GemsFDTD,三个或更多组件策略在大约96%的时间命中。

也包括在图23和图24中,可以添加高速缓存以将结果标记的元组转译为其规范的复合结果标记。前述高速缓存可以被称为组成标记(CTAG)高速缓存(CTAG$),因为其对于几个组件策略规则返回结果标记的相同元组是共同的,所以其是有效的(图9D)。例如,在多数情况下,PCtag将是相同的,即使结果标记不同。此外,许多不同规则输入可能导致相同输出。例如,在污点跟踪中,执行集合联合,且许多不同联合将具有相同结果;例如,(蓝色,{A,B,C})是{A}∪{B,C}和{A,B}∪{B,C}(污点跟踪)两者的结果写入到蓝色隙(blue slot)(存储器安全)中的复合答案。FIFO替换策略用于该高速缓存。CTAG高速缓存将平均未命中处理器周期减小另一因数2(参见图9E)。

合起来,2048-项UCP高速缓存和512-项CTAG高速缓存将在每个L2规则高速缓存未命中上花费的平均时间从800周期减小到80周期。

根据在这里的技术的实施例还可以通过预取在包括规则的一个或多个高速缓存中存储的一个或多个规则来改进性能。因此,另外可以以近期可能需要的预先计算的规则减小强制性未命中率。示例性实例具有用于存储器安全规程的高价值。例如,当分配新存储器标记时,将需要用于该标记的新规则(初始化(1),添加偏移到指针和移动(3),标量加载(1),标量存储(2))。因此,所有这些规则可以一次性添加到UCP高速缓存。对于单一策略存储器安全情况,规则可以直接添加到规则高速缓存中。这将存储器安全未命中处理器调用的数目减小2x。

关于总的评估和参考图11A,架构参数单调地影响特定成本,提供能量、延迟和面积的折衷,但不定义单个成本标准内的最小值。存在阈值效应,即一旦标记位足够小,则L1D/I高速缓存可以恢复到基线的容量,以使得采用基线作为上限以用于L1标记长度,但是在该点以外,减小标记长度会减小能量,对性能影响小。

图11B示出减小标记长度是大多数基准点程序(例如Ieslie3d,mcf)的主要能量效应,其中几个程序示出了由增加UCP高速缓存容量(例如,GemsFDTD,gcc)带来的相等或者较大益处。忽略其他成本关心,为减小能量,选择大的未命中处理器高速缓存和少的标记位。运行时间开销(参见图11A)也以较大的未命中处理器高速缓存最小化,但是受益于多于更少的标记位(例如GemsFDTD,gcc)。这些益处的大小跨越基准点和策略而变化。跨越所有基准点,超出10b L1标记的益处对于SPEC CPU2006基准点是小的,所以10b用作能量和延迟之间的折中,并当变得接近于关注的架构参数的空间内的最低能量级时,使用2048-项UCP高速缓存和512-项CTAG高速缓存以减小面积开销。

图12A和图12B示出应用优化对运行时间和能量开销的总体影响。每个优化对于某些基准点是主要的(例如,对于astar是操作组,对于lbm是DRAM标记压缩,对于h264ref是短标记,对于GemsFDTD是未命中处理器加速),且某些基准点看起来受益于所有优化(例如gcc),其中每个优化连续地除去一个瓶颈和暴露下一个。来自基准点的不同行为遵循如下详述的它们的基线特性。

具有较低局部性的应用具有由于高主存储器业务量而由DRAM驱动的基线能量和性能。这种基准点(例如,lbm)中的开销趋于DRAM开销,所以DRAM开销的减小直接影响运行时间和能量开销。具有更多局部性的应用在基线配置方面更快,消耗更少能量,且受DRAM开销影响更少。结果,这些基准点由减小的L1容量和L1 D/I和规则高速缓存中的标记能量更重地影响。DRAM优化对这些应用具有较少效果,但是使用短标记对能量具有大的效果且除去了L1 D/I高速缓存容量代价(penalty)(例如h264ref)。

具有重的动态存储器分配的基准点由于强制性未命中而具有较高的L2规则高速缓存未命中率,因为新创建的标记必须安装在高速缓存中。这以简单实现驱动了几个基准点(GemsFDTD,omnetpp)的高开销。如在这里描述的未命中处理器优化减小这种未命中的公共情况成本,且操作组优化减小容量未命中率。对于简单实现,GemsFDTD每200个指令取得L2规则高速缓存未命中,且用800个周期以服务每个未命中,驱动它的780%运行时间开销的大部分(参见图4A)。通过优化,GemsFDTD基准点每400个指令服务L2规则高速缓存未命中,且每个未命中平均仅用140个周期,将其运行时间开销减小到大约85%(参见图10A)。

总的来说,这些优化对于除了GemsFDTD和omnetpp之外的所有基准点使得运行时间开销到10%以下(参见图10A),这在存储器分配上是高的。该平均能量开销接近60%,仅具有4个基准点超过80%(参见图10B)。

为了图示,可以使用以以不同方式应对的PUMP的四个不同策略的组成(参见在图14的表1)来测量PUMP的性能影响,并图示安全性属性的范围:(1)使用标记区分存储器中的代码与数据并提供对于简单代码注入攻击的保护的不可执行数据和非可写代码(NXD+NWC)策略;(2)检测堆分配存储器中的所有空间和时间违规的存储器安全策略,以实际上无限的(260)颜色的数目(“污点记号”)扩展;(3)限制仅到程序的控制流图中的允许的边缘的间接控制转移的控制流完整性(CFI)策略,防止面向返回的编程风格攻击(推行细粒度CFI,不是对攻击潜在地脆弱的粗晶粒的近似);和(4)细粒度的污点跟踪策略(一般化),其中每个字可以潜在地同时由多个源(库和10个流)污染。如在这里其他地方注意到的,这些是其保护性能已经在文献中建立的已知策略,且在这里的描述可以聚焦于测量和减小使用PUMP推行它们的性能影响。除了NXD+NWC之外,这些策略中的每一个区分实质上无限数目的唯一项;相反,具有有限数目的元数据位的解决方案最好也仅可以支持粗略简化的近似。也如以上注意到的,PUMP的简单、直接实现可能是昂贵的。例如,将指针大小(64b)标记添加到64b字至少加倍系统中的所有存储器的大小和能量使用。规则高速缓存添加面积和在其上的能量。对于该简单实现,测量的面积开销大约是190%,且geomean能量开销是大约220%;此外,运行时间开销关于某些应用是失望的(在300%以上)。这种高开销将阻碍采用,如果它们是能够做到的最好的话。

比如在这里描述的微架构优化可以包括在根据在这里的技术的实施例中以将关于功率上限的影响减小到10%(参见图10C),提出优化的PUMP将对平台的操作包络线有很少影响。DRAM压缩将lbm的能量开销减小到20%;因为它也减慢9%,其功率需要仅增加10%。

与简单设计的190%相比(例如,参见图16的表3),优化的设计的面积开销是大约110%(例如,参见图18的表5)。短标记显著地减小L1和L2高速缓存(现在在基线以上仅添加5%)和规则高速缓存(仅添加26%)的面积。相反地,优化设计花费某些面积以减小运行时间和能量开销。UCP和CTAG高速缓存添加33%面积开销,同时短标记的转译存储器(L1和L2两者)添加另外的46%。虽然这些附加的硬件结构添加面积,它们提供能量的净减小,因为不经常访问它们,且UCP和CTAG高速缓存也实质上减小未命中处理器周期。

如在这里描述的模型和优化的一个目标是使得其对于实施例添加同时推行的附加策略是相对简单的。由于未命中处理器运行时间的大的增加,关于简单PUMP设计的复合策略导致对于几个基准点的多于递增的成本,但是这些由未命中处理器优化得以减少。

图13A(对于CPI开销)和图13B(对于EPI开销)通过首先示出每个单个策略的开销,然后示出添加策略到存储器安全的复合体(最复杂的单个策略),来图示递增的策略添加怎样影响运行时间开销。与添加较高开销策略相反地,该渐进方式使得什么开销简单地来自添加任何策略更清楚。为了得到缩放超出这里的四个策略的感受,CFI策略(返回和计算的跳转/调用)和污点跟踪策略(代码污染和I/O污染)每个被分为两部分。示出附加的策略的运行时间开销递增地跟踪第一复杂策略(存储器安全)以上,对非离群值(non-outliers)没有可感知的运行时间影响(最坏情况非离群值从9%上升到10%开销)和在两个离群值中的较大的增加(20-40%),因为主要由于增加的未命中处理器解析复杂性而添加每个新种类的策略。能量遵循类似的趋势,对非离群值策略有适度的影响(geomean从60%上升到70%),这对于除了GemsFDTD之外的所有情况都是这样。

在图15再现的表2中标识有关工作的概要。

按照根据在这里的技术的策略编程模型,PUMP策略与操纵这些标记的规则的集合一起包括标记值的集合以实现某些期望的标记传播和推行机制。规则以两个形式:系统的软件层(符号规则)或者硬件层(具体规则)。

例如,为图示PUMP的操作,考虑用于在程序执行期间限制返回点的简单示例策略。该策略的动机来自于已知为面向返回编程(ROP)的一类攻击,其中攻击者识别出受到攻击的程序的二进制可执行中的“小配件(gadget)”的集合,并通过构造每个包括指向某个小配件的返回地址的堆栈帧的适当序列来使用这些"小配件"的集合来组成复杂的恶意行为;然后利用缓存溢出或者其他脆弱性来以期望序列重写堆栈的顶部,导致依序执行片段(snippet)。限制ROP攻击的一个简单方式是将返回指令的目标限制到明确定义的返回点。这是通过以元数据标记目标标记作为有效返回点的指令来使用PUMP。每次执行返回指令,PC上的元数据标记设置为检查指示刚刚发生返回。在下一指令,检查PC标记,验证关于当前指令的标记是目标,且如果关于当前指令的标记不是目标则以信号通知安全性违规。通过使得元数据更丰富,可以精确地控制哪些返回指令可以返回到哪些返回点。通过使得其更丰富,可以实现完全CFI检查。

从PUMP 10的策略设计者和软件部分的观点,可以使用以微小域-专用语言所写的符号规则来紧凑地描述策略。示例性符号规则及其程序语言例如在标题为“PROGRAMMINGTHE PUMP,Hardware-Assisted Micro-Policies for Security(编程PUMP,硬件辅助的安全性微策略)”的部分中描述。

符号规则可以紧凑地编码多种多样的元数据跟踪机制。但是,在硬件级,规则需要调节为有效率的解释的表示以避免减慢初级计算。为此,可以引入较低级规则格式,称为具体规则。直观地,给定策略的每个符号规则可以扩展为具体规则的等效集合。但是,因为单个符号规则总的来说可能生成无限制数目的具体规则,所以缓慢地执行该工作,当系统执行时按照需要生成具体规则。

对于具有元数据标记(例如,比ROP更丰富的)的策略,从符号到具体规则的转译遵循相同的总的路线,但是细节变得有点复杂。例如,污点跟踪策略取得要作为指向存储器数据结构的指针的标记,每个描述任意地大小的污点集合(表示可能贡献于给定条数据的数据源或者系统组件)。加载操作组的符号规则叙述加载值上的污点应该是在指令本身上的污点、负载的目标地址和在该地址的存储器的并集。符号规则及其程序语言通过从先前标识的标题为“PROGRAMMING THE PUMP,Hardware-Assisted Micro-Policies forSecurity”的论文引用而包括于此且可用于公开检查。

为减小不同标记的数目(且因此,对规则高速缓存的压力),可以以规范形式内部存储元数据结构,且因为标记不变,完全地利用共享(例如,给予集合元素规范次序以使得这些集合可以紧凑地表示,共享公共前缀子集)。当不再需要时,可以收回(例如,由无用单元收集)这些结构。

实施例可以利用复合策略。可以通过令标记为指向来自几个组件策略的标记的元组的指针来同时推行多个正交策略。(一般来说,多个策略可以不正交)。例如,为构成具有污点跟踪策略的第一返回操作组(ROP)策略,令每个标记为指向元组(r;t)的表示的指针,其中r是ROP-标记(代码位置标识符)且t是污点标记(到污点的集合的指针)。高速缓存查找处理也是完全一样的,但是当发生未命中时未命中处理器提取元组的组件且分派到评估符号规则的两个集合的例程。仅当两个策略都具有应用的规则时允许操作;在该情况下,产生的标记是到包括来自两个子策略的结果的对的指针。

关于策略系统和保护,策略系统作为每个用户进程内的存储器的分隔区域存在。策略系统例如可以包括用于未命中处理器的代码、策略规则和表示策略的元数据标记的数据结构。在该进程中放置策略系统最小地侵入现有的Unix处理模型,且便于策略系统和用户代码之间的轻量切换。策略系统使用接下来描述的机制与用户代码隔离。

清楚地,如果攻击者可以重写元数据标记或者改变它们的解释,则由PUMP提供的保护将是无用的。在这里描述的技术设计用于防止这种攻击。内核程序、加载器和(对于某些策略)编译器是可信的。具体来说,编译器被依赖以向字分配初始标记,且当需要时,向策略系统传递规则。加载器将保存由编译器提供的标记,且例如使用加密签名保护从编译器到加载器的路径免于篡改(tamper)。

根据在这里的技术的实施例可以使用对于每个进程建立初始存储器图像的标准Unix风格内核程序。(可以使用微策略以消除这些假定中的一些,进一步减小TCB的大小)。进一步假定在这些实施例中,正确地实现规则高速缓存未命中处理软件。这很小,因此是用于形式验证的好目标。一个关切是防止在进程中运行的用户代码推翻由进程的策略提供的保护。用户代码应该不能够(i)直接地操纵标记--所有标记改变应该根据当前生效的一个或多个策略执行;(ii)操纵由未命中处理器使用的数据结构和代码;(iii)在硬件规则高速缓存中直接插入规则。

关于寻址,为防止由用户代码对标记的直接操纵,附加到每个64b字的标记本身不是分开地可寻址的。具体来说,不可以指定仅与标记或者标记的一部分对应的地址以读取或者写入它。所有用户可访问指令在作为原子单元的(数据,标记)对上操作—对值部分操作的标准ALU和对标记部分操作的PUMP。

关于在根据在这里的技术的实施例中的未命中处理器架构,可以仅关于对PUMP高速缓存的未命中来激活策略系统。为提供策略系统和用户代码之间的隔离,未命中处理器操作模式被添加到处理器。整数寄存器文件以仅可用于未命中处理器的16个附加寄存器来扩展,以避免保存和恢复寄存器。注意到,16个附加寄存器的使用是说明性的且实际上可能需要扩展整数寄存器文件到更少/更多寄存器。故障指令的PC,规则输入(操作组和标记)和规则输出当在未命中处理器模式下时作为寄存器出现。添加未命中处理器返回指令,其结束将具体规则安装到高速缓存中并返回到用户代码。

在根据在这里的技术的实施例中,当处理器12处于未命中处理器模式时脱离PUMP10的正常行为。代替地,应用单个硬布线规则:由未命中处理器接触的所有指令和数据必须以与由任何策略使用的标记不同的预定义的未命中处理器标记来标记。这保证相同地址空间中的未命中处理器码和数据与用户代码之间的隔离。用户代码不能接触或者执行策略系统数据或者代码,且未命中处理器不能无意地接触用户数据和代码。未命中处理器返回指令可以仅在未命中处理器模式下发布,防止用户代码将任何规则插入到PUMP中。

当先前工作已经使用更聪明的方案来紧凑地表示或者近似安全和安全性策略时,这通常是关于想要策略的折衷,且它可以平衡复杂性和紧凑性。如在这里描述的,可以包括以很少或者没有附加运行时间开销而更完全地和更自然地捕获安全性策略的需要的更丰富的元数据。不是施加对元数据表示和策略复杂性的固定限制,而是PUMP 10提供性能上的适度退化。这允许策略在需要时使用更多数据而不影响通常情况的性能和大小。它进一步允许策略的增加的精细化和性能调节,因为即使复杂策略也可以容易地表示和执行。

通过安装用于基于元数据值的策略推行的证据,本公开定义用于软件定义的元数据处理的架构并标识加速器以除去大部分运行时间开销。在这里引入和描述的架构没有关于元数据位的数目或者与四个微架构优化一起同时支持的策略的数目的限制(即,没有任何限制),该四个微架构优化(操作组、标记压缩、标记转译和未命中处理器加速)实现可与专用硬件元数据传播解决方案相比的性能。软件定义的元数据策略模型及其加速将可应用于除这里图示的那些以外的大范围的策略,包括声音信息-流控制、细粒度访问控制、完整性、同步、竞态检测(race detection)、调试(debug)、应用专用策略和动态代码的受控生成和执行。

在这里描述的各种方面和实施例的某些非限制优点提供(i)编程模型和支持用于紧凑地和精确地描述由该架构支持的策略的接口模型;(ii)策略编码和使用四个不同类别的充分研究的策略的组成的具体实例;和(iii)这些策略的需要、复杂性和性能的量化。

如在这里描述的实施例的编程模型可以编码许多其他策略。信息-流控制比这里的简单的污点跟踪模型更丰富,但是可以以RIFLE-风格二进制转译或者通过与来自编译器的某些支持一起使用PC标记来跟踪隐含流。微策略可以支持轻量访问控制和划分(compartmentalization)。标记可以用于区分不可伪造的资源。唯一的生成的令牌可以作为用于密封和签署数据的密钥,其然后可以用于强抽象-保证数据仅由授权的代码组件创建和解构。微策略规则可以推行数据不变性质,比如不变性和线性。微策略可以支持并行性,如用于同步原语的带外元数据,比如用于数据或者未来的完全/空位,或者如检测关于锁定的竞态条件的状态。系统设计师可以向现有的代码应用专用微策略而不用核查或者重写每一行。

如在这里描述的设计的PUMP 10提供灵活性和性能的吸引人的组合,在以当规则复杂性增长时最得体的性能下降支持更丰富和复合策略的同时,以在多数情况下可与专用机制相比较的单个策略性能来支持不同集合的低级、细粒度安全性策略。另外,由PUMP提供的机制可以用于保护它自己的软件结构。根据在这里的技术的实施例可以通过使用PUMP10实现“划分”微策略和使用其保护未命中-处理器代码而代替特殊未命中处理器操作模式。最终,如在这里描述的,可以组合策略的正交集合,其中由每个策略提供的保护与其他的完全独立。但是策略通常交互:例如,信息-流策略可能需要在由存储器安全策略分配的新鲜区域放置标记。策略组成需要关于表达和有效率的硬件支持两者方面的分析。

现在将描述的是图示在根据在这里的技术的实施例中的存储器安全策略的实现的另一实例,其标识堆-分配存储器中的所有时间和空间违规。在至少一个实施例中,对于每个新分配,可以执行处理以构成新鲜颜色-id的,c,并写入c作为关于新创建的存储器块(例如,比如经由memset)中的每个存储器位置的标记。到新块的指针也标记为c。之后,当执行处理以解参考指针时,处理可以包括检查指针的标记与关于指针参考或者指向的存储器单元的标记相同。当释放块时,关于块的全部单元的标记可以修改为表示闲置存储器的常数F。堆最初可以标记为F。特殊标记⊥可以用于非指针。因此,通常,实施例可以对于颜色c或者⊥的存储器位置写入标记t。

因为存储器单元可以包括指针,总的来说存储器中的每个字可以与两个标记相关联。在这种实施例中,关于每个存储器单元的标记是到对(c,t)的指针,其中c是分配该单元的存储器块的id且t是关于该单元中存储的字的标记。一个实施例可以使用基于用于就符号规则而言指定策略的在这里其他地方描述的规则功能的域专用语言。与检查每个存储器访问有效(即,访问的单元在由该指针指向的块内)一起,用于加载和存储的规则负责封装和解封这些对:

加载(load):(-,-,c1,-,(c2,t2))

如果c1=c2,则→(-,t2)

存储(store):(-,-,t1,c2,(c3,t3))

如果c2=c3,则→(-,(c3,t1))

在前述及其他规则中执行的检查揭示符号规则有效的条件(例如,在存储规则中c2=c3以上)。符号“-”指示规则中的不关心字段。

地址运算操作保存指针标记:

add:(-,-,c,⊥,-)→(-,c)

为维持关于指针的标记仅可以来源于分配的不变性质,从抓取创建数据的操作(例如,加载常数)将其标记设置为⊥。

在实现存储器安全策略的实施例中,比如malloc和释放的操作因此可以使用标记的指令和短暂(ephemeral)规则修改为标记存储器区域(例如,一旦它们被使用就可以从高速缓存删除)。关于malloc,处理可以经由短暂规则生成用于到新区域的指针的新鲜标记。例如,用于移动的规则可以是比如以下的短暂规则:

移动(move):(-,tmalloc,t,-,-)→1(-,tnewtag)

具有上标1的箭头(例如,→1)可以指示短暂规则。新标记的指针然后可以用于使用特殊存储规则写入零到分配区域中的每个工作,特殊存储规则为:

store:(-,tmallocinit,t1,c2,F)→(-,(c2,t1))

之后,返回标记指针。在之后的时间点,释放可以使用修改的存储指令以重新标记区域为未分配的:

store:(-,tfreeinit,t1,c2,(c3,t4))→(-,F)

之后,该区域返回到释放列表。

在这种使用存储器安全策略的实施例中,操作组可以用于描述如下的规则集合:

(1)nop,cbranch,ubranch,ijump,return:(-,-,-,-,-)→(-,-)

(2)ar2sld:(-,-,⊥,⊥,-)→(-,⊥)

(3)ar2sld:(-,-,c,⊥,-)→(-,c)

(4)ar2sld:(-,-,⊥,c,-)→(-,c)

(5)ar2sld:(-,-,c,c,-)→(-,⊥)

(6)ar1sld:(-,-,t,-,-)→(-,t)

(7)ar1ld,dcall,icall,flags:(-,-,-,-,-)→(-,⊥)

(8)load:如果c1=c2,则(-,-,c1,-,(c2,t2))→(-,t2)

(10)store:(-,tmallocinit,t1,c2,F)→(→,(c2,t1))

(11)store:(-,tfreeinit,t1,c2,(c3,t4))→(→,F)

(12)move:(-,tmalloc,t,-,-,)→1(-,tnewtag)

用于策略说明的以上使用的符号规则可以使用变量来写,允许几个符号规则描述不同值的无限制全域之上的策略。但是,规则高速缓存中存储的具体规则参考特定的具体标记值。例如,如果23和24是有效的存储器块颜色,则实施例可以使用具有用于c=23和c=24的PUMP规则高速缓存中的符号规则(3)以上的具体实例的具体规则。例如,假定实施例编码⊥为0,且标明不关心字段为0,则用于以上符号规则(3)的具体规则是:

ar2sld:(0,0,23,0,0)→(0,23)

ar2sld:(0,0,24,0,0)→(0,24)

与在这里其他地方的讨论一致,在至少一个实施例中,未命中处理器可以获得从符号规则编译的具体输入标记和执行代码以产生关联的具体输出标记,以将规则插入到PUMP规则高速缓存中。当符号规则识别处违规时,控制转移到错误处理器,且没有新的具体规则插入到PUMP规则高速缓存中。

现在将描述的是基于RISC-V架构的根据在这里的技术的实施例进一步以元数据标记和PUMP扩展以支持按照在这里的讨论的软件定义的元数据处理(SDMP)。RISC-V可以特性化为精简指令集计算(RISC)指令集架构(ISA)的开源实现。在这种实施例中,元数据标记位于每个字的指令和数据两者上。在RISC-V架构中,字是64位。RISC-V架构提供不同字长变化-具有64位的字长的RV64和具有32位的字长的RV32。寄存器和用户地址空间的宽度或者大小可以随字长而变。标记大小或者宽度可以独立于字长或者宽度,但是在实施例中可能典型地相同。如现有技术中已知的,RISC-V架构具有32位指令且因此使用64位字长支持和操作的实施例可以在单个标记的字中存储2个指令。关于与扩展用于与元数据标记、PUMP和SDMP一起使用的RISC-V架构相关的不同技术和特征的使用,在这里其他地方讨论RISC-V架构的前述及其他方面。

例如,在"The RISC-V Instruction Set Manual Vol.1,User-Level ISA,Version 2.0",2014年5月6日,Waterman,Andrew等,(也称为"RISC-V user level ISA")中描述包括用户级指令的RISC-V架构,上述文件通过引用包括于此,且例如在RISCV.ORG网站,且通过加州大学伯克利作为技术报告UCB/EECS-2014-54公开可得到。RISC-V架构还包括特权架构,该特权架构包括特权指令和运行操作系统、附加外部装置等需要的附加功能性,例如如在“The RISC-V Instruction Set Manual Volume II:PrivilegedArchitecture,Version 1.7”,2015年5月9日,也称为“RISC-V privileged ISA”)中描述的,该文件通过引用包括于此,且例如在RISCV.ORG网站且通过加州大学伯克利作为技术报告UCB/EECS-2015-49公开可用得到。

RISC-V架构的实施例可以具有如下的四个RISC-V特权级别:用于用户/应用(U)特权级别的级别0,用于管理程序(S)特权级别的级别1,用于系统管理程序(H)特权级别的级别2,和用于机器(M)特权级别的级别3。在前述中,RISC-V特权级别可以从最高到最低从0到3分级,其中级别0指示最高或者最大特权级别,且级别3指示最低或者最小特权级别。这种特权级别可以用于提供不同组件之间的保护,且对执行当前特权级别或者模式不允许的操作的代码的执行的尝试将导致产生例外,比如到下层执行环境中的陷阱。机器级别具有最高特权,且是RISC-V硬件平台的唯一强制性特权级别。以机器模式(M-模式)运行的代码是固有地可信的,因为它具有对机器实现的低级访问。用户模式(U-模式)和管理程序模式(S-模式)意在分别用于现有的应用和操作系统使用,而系统管理程序模式(H-模式)意在支持虚拟机器监控程序。每个特权级别具有具有可选扩展和变型的特权ISA扩展的核心集合。应当注意,RISC-V架构的实现必须至少支持M-模式,且大多数实现至少支持U-模式和M-模式。可以添加S-模式以提供管理程序级别操作系统的代码与M-模式中执行其他更多特权代码之间的隔离。用户或者应用代码可以典型地在U-模式下执行直到发生陷阱(例如,管理程序调用、页错误)或者中断,迫使控制转移到在支持的较高特权模式或者级别(例如,H、S或者M模式)之一运行的陷阱处理器。然后执行陷阱处理器的代码,且控制然后可以返回到导致陷阱的初始用户代码或者应用。这种用户代码或者应用的执行可以在触发陷阱处理器调用的U-模式中的初始陷阱指令处或者其之后恢复。RISC-V实现中支持的模式的不同组合可以仅包括:单个M模式,两个模式M和U,三个模式M、S和U,或者所有四个模式M、H、S、U。在在这里描述的至少一个实施例中,可以支持所有4个前述特权级别。至少,根据在这里的技术的实施例可以支持M和U模式。

RISC-V架构具有可以由一个或多个关联的特权级别原子地读取和修改的控制状态寄存器(CSR)。总的来说,CSR可以以四个特权级别的第一个和高于第一个的四个特权级别的任何其他访问。例如,假定在U-模式(级别3)下执行程序且发生比如规则高速缓存未命中的陷阱,由此控制转移到以较高特权或者模式(例如,0-2的任意级别)运行的陷阱处理器,比如规则高速缓存未命中处理器代码。在陷阱的发生时,信息可以位于在M模式下执行的陷阱处理器可访问的CSR中,例如,该CSR要不然就对以较低特权级别执行的任何其他代码不可访问(例如,对在H、S或者U模式下的代码不可访问)。在至少一个实施例中,规则高速缓存未命中处理器可以以PUMP保护级别以上的特权级别运行(例如,可以在H-模式、S-模式或者M-模式下运行)。在这种实施例中,如在这里其他地方描述的,标记定义和策略可以在规则高速缓存未命中处理器级别是跨操作系统(例如,每个虚拟机)全局的,由此可以跨所有执行代码应用相同标记定义和策略。在至少一个实施例中,可以支持每个应用或者处理策略,其中全局地安装这种策略且可以标记PC(标识当前指令的程序计数器)和/或代码以区分进程或者应用专用规则。在虚拟机(VM)不共享存储器的实施例中,可以以每个VN的基础定义策略。

按照在这里其他地方的讨论,PUMP可以特性化为用于SDMP的规则高速缓存。可能有在关于指令和指令输入的标记和用于操作结果的标记的集合之间的映射。标记处理是与指令的正常操作独立和并行的。在至少一个实施例中,PUMP并行于普通RISC-V操作运行,提供用于操作结果的标记。因为PUMP是高速缓存,第一次PUMP接收特定指令就发生规则高速缓存未命中,且因此特定的PUMP输入(例如,强制性)的相应集合或者当PUMP不能在高速缓存中保持规则时(例如,超过高速缓存的容量因此从规则高速缓存中逐出规则,或者可能冲突)。规则高速缓存未命中导致然后由未命中处理器系统(例如,规则高速缓存未命中处理器)的代码处理的未命中陷阱。输入可以通过PUMP CSR传递到未命中处理器,且也可以通过CSR提供规则插入回到PUMP。这在以下更详细地讨论。在这里其他地方讨论第一实施例,其中存在5个PUMP输入标记。作为变型,实施例可以包括不同数目的标记及其他PUMP输入。PUMP标记输入的特定数目可以随指令集和操作数而变。例如,基于RISC-V架构在一个实施例中可以包括以下作为PUMP输入:

1.Opgrp-指示包括当前指令的特定操作组。通常,操作组是一组指令的抽象且在这里的其他地方讨论。

2.PCtag-关于PC的标记

3.CItag-关于指令的标记

4.OP1tag-关于到指令的RS 1输入的标记

5.OP2tag-关于到指令的RS2输入的标记(或者当CSR指令时关于CSR的标记)

6.OP3tag-关于到指令的RS3输入的标记

7.Mtag-关于到指令的存储器输入或者指令的存储器目标的标记

8.functl2(funct7)-如在这里其他地方描述的在某些指令中发生的扩展的操作码位。

9.subinstr-当存在在字中封装的多个指令时,该输入标识在字中的哪个指令是由PUMP操作的当前指令。

基于RISC-V架构在一个实施例中可以包括以下作为PUMP输出:

1.Rtag-关于结果的标记:目的地寄存器、存储器或者CSR

2.newPCtag-关于在该操作之后PC的标记(例如,有时在这里称为PCnew标记)。

信息例如可以从在陷阱发生时在U-模式中执行的用户代码经由CSR传递到在M模式中执行的陷阱处理器,比如规则高速缓存未命中处理器。以类似的方式,当恢复U-模式下的程序执行时信息可以经由CSR在M模式下的陷阱处理器之间传递,其中CSR中的信息可以位于在U-模式下可访问的相应的寄存器中。以该方式,可能有在一个特权级别的CSR和在其他特权级别的寄存器之间的映射。例如,在根据在这里的技术的实施例中,可以定义CSR对M模式处理器和PUMP可访问,其中在陷阱发生时特定的指令操作数标记写入到CSR以将标记作为输入传递到PUMP和规则高速缓存未命中处理器。以类似的方式,CSR可以用于将信息从陷阱处理器和/或PUMP(在高于U-模式的特权级别操作)传递到在U-模式中执行的其他代码,比如当在规则高速缓存未命中之后恢复程序执行时(例如,其中当在用于当前指令的PUMP规则高速缓存中未找到匹配规则时发生规则高速缓存未命中)。例如,CSR可以用于输出或者传送用于PCnew和RD的PUMP输出标记。另外,可以定义CSR,其中可以响应于到特定CSR的写入发生不同动作。例如,规则高速缓存未命中处理器代码可以通过写入到特定的CSR而将新规则写入/插入到PUMP的规则高速缓存中。定义的特定的CSR可以随实施例而变。

参考图25,示出了在根据在这里的技术的一个实施例中可以定义和使用的CSR的实例。表900包括具有十六进制的CSR地址的第一列902,特权的第二列904,指示CSR名称的第三列906和具有CSR的描述的第四列908。表900的每行可以标识不同定义的CSR的信息。900中的不同的CSR也在这里其他地方关于可以包含在实施例中的附加特征更详细地描述。

行901a-c标识具有用于由PUMP标记代码和/或指令的特殊标记值的CSR。在至少一个实施例中,由项901a定义的sboottag CSR可以包括系统中使用的第一初始或者开始标记值。前述开始标记值可以被称为自举标记值。在一个方面中,自举标记值可以特性化为可以从其衍生出所有其他标记或者所有其他标记基于的“种子”。因此,自举标记可以在一个实施例用作用于生成所有其他标记的开始点。以类似于操作系统中的自举代码的起始位置的初始加载的方式,硬件可以用于将CSR 901a初始化为用作自举标记的特定的预定义标记值。一旦已经读取自举标记作为引导根据在这里的技术的系统的一部分,可以清除sboottag CSR。例如,操作系统代码的特权部分可以包括调用使用自举标记值执行初始标记传播的规则的指令。在这里其他地方进一步描述自举标记的使用和标记生成及传播。行901b标识包含用于标记来自如在这里其他地方描述的公开不可信源的数据的标记值的CSR。对于行901c,标识包含可以用作当标记数据和/或指令时的默认标记值的默认标记值的CSR。

行901d和e分别指示用于写入到操作组/关心表的地址和数据(例如,在这里其他地方也称为包括操作组和操作码的关心/不关心位的映射或者转译表)。写入到由行901e指示的CSR触发到操作组/关心表的写入。行901f标识为了清空PUMP规则高速缓存可以写入的CSR。行901g-901m标识将用于当前指令的标记输入提供到PUMP和规则高速缓存未命中处理器的CSR。行901j-m每个指示用于导致规则高速缓存未命中的正在处理的当前指令的操作数的不同操作数标记,由此指令可以包括多达4个这种操作数(4个操作数中的3个是寄存器(CSR 901j-l)且第四个操作数是具有在由行901m指示的CSR中存储的标记的存储器位置)。行901n标识当当前指令的操作码使用如在这里其他地方描述的扩展的funcl2字段时保持扩展操作码位的CSR。行901o标识指示字中的哪个子指令是正在参考的当前指令的CSR。如在这里其他地方讨论的,单个标记的字可以是64位且每个指令可以是32位,由此两个指令可以包括在单个标记的字中。由行901o指示的CSR标识两个指令中的哪个正在由PUMP处理。行901p-q分别标识新PC(例如,下一指令的新PC标记)和RD(目的地寄存器,当前指令的结果的地址)包括PUMP输出标记的CSR。写入到由901q指示的CSR导致规则(例如,匹配触发PUMP规则高速缓存未命中的当前指令)写入到PUMP规则高速缓存中。行901r标识PUMP操作的标记模式。在这里其他地方更加详细地描述标记模式。

在至少一个实施例中,可以通过写入到由901e指示的CSR sopgrpvalue来填充用于存储操作组和关心/不关心位的一个或多个表(例如操作组/关心表),其中前述CSR 901e的内容写入到由901d指示的sopgrpaddr CSR中存储的地址。规则可以响应于写入到由项901q定义的srtag CSR而写入或者安装到PUMP规则高速缓存中。规则写入是经由PUMP CSR(例如,基于PUMP CSR输入901g-o)指定与操作码(或更具体地,用于操作码的操作组)匹配的标记值和用于当前指令的标记值作为到PUMP的输入的规则。

为允许关于CSR操作的标记和标记保护,数据流允许CSR标记输入到PUMP和从PUMP输出。根据RISC-V架构,存在分别从CSR读取和写入到CSR的读和写指令。关于具有PUMP的CSR指令,到PUMP的R2tag输入是当前CSR标记。CSR读/写指令(例如,csrrc、csrrci、csrrs、csrrsi、csrrw、csrrwi)写入两个输出:(1)RD和(2)由指令参考的CSR。在该情况下,PUMP输出R标记(或者目的地的RD标记)指定由PUMP输出和将CSRtag直接复制到寄存器目的地标记的CSR标记。

RDtag←CSRtag

CSRtag←Rtag

关于由列904指示的特权,由行901r的定义CSR mtagmode通过在机器或者M-模式级别的代码执行可访问以用于读/写。由行901a-q定义的其余CSR通过至少在管理程序或者S-模式级别的代码执行可访问以用于读/写。因此,对于各种CSR在列904指示的特权表示执行代码的最小RISC-V特权级别以用于代码访问特定的CSR。实施例可以对于实施例中使用的CSR分配与实例900中图示的不同的RISC-V特权级别。

根据在这里的技术的实施例可以定义影响由PUMP执行的标记传播的多标记模式。当前标记模式由在如行901r所定义的CSR mtagmode中存储的当前时间点的值来标识。在至少一个实施例中,可以与RISC-V定义特权(例如,上面描述的M、H、S和U模式)组合地使用标记模式以定义关于PUMP使用的CSR保护模型。

为了允许规则高速缓存未命中处理器设置可配置,可以使用进一步扩展RISC-V特权的保护模型。不是完全由特权级别定义PUMP CSR访问,而是可以进一步相对于与RISC-V特权级别结合的当前标记模式来定义CSR访问。因此,在根据在这里的技术的至少一个实施例中,是否允许执行代码访问CSR可以取决于CSR的最小RISC-V特权级别,当前标记模式和执行代码的当前RISC-V特权级别。以下更详细地讨论标记模式。

参考图26,示出了可以用于根据在这里的技术的实施例的标记模式的实例。表910包括以下列-912mtagmode位编码,914操作和916标记结果。表910的每一行表示用于不同可能标记模式的信息。当标记模式如由911a表示的是000时,PUMP关闭且不使用且不生成任何标记结果。当标记模式是010时,PUMP写入关于全部结果的默认标记(例如,用于目的地或者结果寄存器或者存储器位置的Rtag)。

关于行911c-f,表示是可以对于在不同RISC-V特权级别的代码执行指定用于启用或者脱离PUMP的不同标记模式。当启用PUMP时,PUMP可以特性化为有效、使能的,且当执行代码时提供保护由此在代码执行期间推行其策略的规则。相反地,当脱离PUMP时,PUMP可以特性化为无效、禁用的且当执行代码时不提供保护由此在代码执行期间不推行其策略的规则。当脱离PUMP时,可以使用一个或多个默认标记传播规则传播标记,而不是基于具有匹配当前指令的那些标记值的标记值的规则的评估来传播标记。启用或者脱离PUMP可以随特定的假定可信级别和归因于在不同RISC-V特权级别执行的代码的期望保护级别而变。

关于标记模式911c-f,除了由901r表示的mtagmode CSR之外,实例900的全部PUMPCSR仅当脱离PUMP时可访问。也就是,除了由901r表示的mtagmode CSR之外,实例900的PUMPCSR仅对在当前RISC-V操作特权执行的代码或者比由标记模式表示的最高层级PUMP特权更特权的模式可访问(例如,由911c表示的最高层级特权是U模式,由911d表示的最高层级特权是S模式,由911e表示的最高层级特权是H模式,且由911f表示的最高层级特权是M模式)。

当如由911c表示的标记模式是100时,PUMP脱离且当RISC-V特权级别表示比U-模式更高或更提升的特权级别时不操作。因此,标记模式911c指示PUMP及其提供保护的规则仅当在U-模式执行代码时启用和推行,由此指示在高于U-模式的特权级别(例如,在S、M或者H模式)执行的代码是可信的。当如由911c表示标记模式是100且执行代码的RISC-V保护级别是S、M或者H模式时,PUMP脱离且其CSR可对仅在S、M或者H模式中执行的代码可访问(例如,CSR对以U-模式执行的代码不可访问)。

当如由911d表示的标记模式是101时,PUMP脱离且当RISC-V特权级别表示比S-模式更高或更提升的特权级别时不操作。因此,标记模式911d指示PUMP及其提供保护的规则仅当在S-模式和U-模式执行代码时启用和推行,由此指示在高于S-模式的特权级别(例如,在M或者H模式)执行的代码是可信的。当如由911d表示标记模式是101且执行代码的RISC-V保护级别是M或者H模式时,PUMP脱离且其CSR可对仅在M或者H模式中执行的代码可访问(例如,CSR对以S或者U模式执行的代码不可访问)。

当如由911e表示的标记模式是110时,PUMP脱离且当RISC-V特权级别表示比H-模式更高或更提升的特权级别时不操作。因此,标记模式911e指示PUMP及其提供保护的规则仅当在H-模式、S-模式和U-模式执行代码时启用和推行,由此指示在高于H-模式的特权级别(例如,在M模式)执行的代码是可信的。当如由911e表示标记系统模式是110且执行代码的RISC-V保护级别是M模式时,PUMP脱离且其CSR可对仅在M模式中执行的代码可访问(例如,CSR对以U、H或者S模式执行的代码不可访问)。

当如由911f表示标记模式是111时,总是启用PUMP且对于M、H、S和U的全部RISC-V特权级别操作。因此,标记911f指示当在M-模式、H-模式、S-模式和U-模式的任意执行代码时启用和推行PUMP及其提供保护的规则,由此指示没有代码是固有地可信的。通过如由911f表示的标记模式=111,从不脱离PUMP且其CSR对任何执行代码都不可访问。

关于由行911c-f表示的标记模式,当执行代码的当前RISC-V特权级别高于由标记模式表示的最高参与PUMP级别时,可以脱离PUMP,且可以使用一个或多个默认标记传播规则来传播标记。

当标记模式具有如由行911a表示的编码000时(指示PUMP关闭)或者当标记模式具有如由行911b表示的编码010时(指示写入默认模式),表900的全部CSR可以仅由以M模式执行的代码可访问。

因此,在根据在这里的技术的至少一个实施例,是否允许执行代码访问CSR可以取决于CSR的最小RISC-V特权级别(比如在表900的列904中指定的)、当前标记模式和执行代码的当前RISC-V特权级别。例如,在不考虑标记模式的RISC-V架构中,由于对于所有这种CSR的由904表示的最小特权级别,不允许在U-模式执行的代码访问900中定义的的任意CSR。但是,不考虑标记模式的情况下,允许以至少H模式的特权执行的代码访问除了901r之外的900的全部CSR,且允许以M模式执行的代码访问900的全部CSR。现在考虑根据904的最小RISC-V特权和标记模式确定900的CSR的CSR访问。例如,考虑在H-级别执行的代码部分A。当如由911c表示的标记模式是100时或者当如由911d表示的标记模式是101时,允许代码部分A访问(表900的)CSR 901a-q。但是,可以不允许在S模式执行的代码部分B访问CSR 901a-q,因为代码部分B不具有由用于这种CSR的904中的定义的CSR特权级别指定的最小特权级别。因此,例如,在使用表900中定义的CSR在H级别执行的一个实施例中,代码部分A可以是高速缓存未命中处理器。如第二实例,假定对于CSR 901a-q定义的最小RISC-V特权是SRW(S模式表示为访问这种CSR的最小特权级别)。当如在911c标记模式是100时和当如在911d标记模式是101时,允许在H模式执行的代码部分A访问CSR 901a-q,且当如在911c标记模式是100时允许在S模式执行的代码部分B访问CSR 901a-q。因此,代码部分A或者B可以是高速缓存未命中处理器的代码。

在至少一个实施例中,当PUMP关闭时,比如在引导处理的适当部分期间,911a的关闭标记模式可以是当前标记模式。当初始化存储器位置具有相同默认标记(例如,如由CSR901c表示的)时,911b的默认标记模式可以是当前标记模式。通常,虽然在RISC-V架构中指定4个特权模式,实施例可以替代地使用不同数目的特权模式,其中第一特权级别表示用户模式或者无特权模式,且第二特权级别表示执行的提升的或者特权模式(例如,类似于基于UNIX的操作系统中的核心模式)。在这种实施例中,可以启用PUMP且当在用户或者无特权模式中执行代码时推行策略规则,且当在第二提升的特权模式中执行代码时可以脱离PUMP(例如,PUMP保护关闭或不推行规则)。以该方式,当执行比如未命中处理器的可信或者提升的特权代码以在PUMP规则高速缓存中存储新规则时,实施例可以脱离PUMP。

如上所述,实施例可以使用默认传播规则以确定例如,当脱离PUMP时和/或当规则指定不关心PUMP输出新PC标记和R标记时,PUMP输出新PC标记和R标记(例如,这种不关心值可以由当前指令的特定操作码的关心矢量指示)。在一个实施例中,以下可以表示在使用的默认传播规则中具体表现的逻辑。

·newpctag是用于默认传播的PCtag

·Rtag是用于CSR读和写操作的CSR;

·RDtag是分配的RS2tag(CSRtag)

-允许各标记与各数据值一起交换

-RDtag←RS2tag←初始CSRtag

-CSRtag←Rtag←初始RS1tag

·Rtag是用于CSRR?I、CSRRS、CSRRC的RS2tag(CSRtag)

-保持CSRtag不变

-RDtag←RS2tag←初始CSRtag

-CSRtag←Rtag←初始RS2tag←初始CSRtag

·Rtag是用于JAL和JALR指令的PCtag(其用于返回地址)

·Rtag是用于AUIPC指令的PCtag。在RISC-V中,AUIPC(添加上层邻接(upperimmediate)到PC)指令用于建造PC相对地址和使用U类型格式。AUIPC形成与20位U-邻接的32位偏移,最低12位以零填充,添加该偏移到PC,然后将结果置于寄存器rd中。

·Rtag是用于LUI指令的CItag。在RISC-V中,LUI(加载上层邻接)指令用于建造32位常数和使用U类型格式。LUI将U邻接值置于目的地寄存器RD的顶部20位,最低12位以零填充。

·Rtag是用于非存储器非CSR、非JAL(R)/AUIPC/LUI操作的RSltag,

·Rtag是用于存储器写操作的RS2tag

·Rtag是用于存储器加载操作的Mtag

在基于RISC-V架构的在这里的技术的至少一个实施例中,可以对于规则高速缓存未命中发生定义新PUMP未命中陷阱。PUMP未命中陷阱可以具有比虚拟存储器故障或者非法指令更低的优先级。

在使用RISC-V架构处理根据在这里的技术的至少一个实施例中,可以维护数据和元数据之间的严格分隔和隔离,其中在标记元数据处理和普通指令处理之间存在分隔和隔离。因此,可以维持元数据规则处理和普通或者典型程序指令执行之间的分开的执行域。可以执行用于与执行代码的指令和数据相关联的标记使用PUMP执行的元数据处理。陷阱中的PUMP规则高速缓存未命中结果导致控制转移到高速缓存未命中处理器,规则高速缓存未命中处理器生成或者提取匹配当前指令的规则并在PUMP规则高速缓存中存储该规则。信息可以使用CSR在以上提到的执行域之间通信。当从执行程序的指令执行域切换到元数据规则处理域时(比如当经由规则高速缓存未命中陷阱触发规则高速缓存未命中处理器时),可以使用CSR提供标记及与指令(导致该陷阱)相关的其他信息作为到PUMP以及未命中处理器的输入。以类似的方式,当控制从元数据规则处理域转移执行程序的指令执行域时(比如当在处理规则高速缓存未命中陷阱之后从规则高速缓存未命中处理器返回时),可以使用CSR来传递PUMP输出,其中CSR的内容然后存储在指令执行域中的相应的映射寄存器中。按照在这里的讨论,不映射到规则的指令(例如,没有该指令的匹配规则位于高速缓存中,且高速缓存未命中处理器确定对于当前指令不存在这种匹配规则)指示不允许执行该规则由此触发陷阱或者其他事件。例如,处理器可以停止当前程序代码的执行。

以该方式,即使相同RISC-V处理器和存储器可以用于两个域中,可能存在前述域和关联的数据路径之间的严格分隔。使用在这里的技术,不允许执行代码的指令读取或者写入元数据标记或者规则。包括标记指令和数据的全部元数据转换可以通过PUMP进行。类似地,可以仅由元数据子系统的规则高速缓存未命中处理器执行到PUMP高速缓存中的规则插入。关于由元数据子系统或者处理系统执行的处理,执行代码的元数据标记被置于PUMPCSR中,且成为输入到且由元数据系统在上面操作的“数据”(例如,指针到元数据存储器空间中)。元数据子系统经由PUMP输入CSR读取PUMP输入以用于根据规则的处理。如果允许指令经由规则进行,则PUMP写入标记结果(例如,比如对于PC新和R标记)到定义的PUMP输出CSR。可以响应于到特定CSR(例如,比如901q中的srtag CSR)的写入触发到规则高速缓存中的规则插入。以该方式,通过PUMP中的规则进行全部标记更新且由元数据子系统控制。仅元数据子系统可以经由在发生规则高速缓存未命中时调用的高速缓存未命中处理器将规则插入到PUMP高速缓存中。另外,在使用RISC-V架构在这里描述的至少一个实施例中,可以维持元数据处理和一般指令处理之间的前述分隔而不增加超出“RISC-V用户级ISA”和“RISC-V特权ISA”中的那些指令的任何新指令。按照在这里其他地方的讨论,根据在这里的技术的实施例可以维持数据和元数据之间的严格分隔和隔离,由此在基于标记的元数据处理和一般指令处理之间存在分隔。在至少一个实施例中,可以通过使得分开的物理元数据处理子系统具有分开的处理器和分开的存储器来维持这种分隔。因此,当执行程序的处理指令时可以使用第一处理器和第一存储器,且第二处理器和第二存储器可以包括在元数据处理子系统中,用于比如当执行规则高速缓存未命中处理器的代码时,执行元数据处理来使用。

参考图27,示出了可以在根据在这里的技术的实施例中包括的组件的实例1000。实例1000包括关于用于执行程序的一般处理使用的第一子系统或者处理器1002和元数据处理子系统或者处理器1004。第一子系统1002可以特性化为关于一般程序执行使用的程序执行子系统。子系统1002是包括关于执行程序代码和使用其中这种代码和数据包括如在这里其他地方描述的由元数据处理子系统1004使用的标记的数据使用的组件。子系统1002包括存储器1008a,指令或者I-存储1008b,ALU(算术及逻辑单元)1008d和程序计数器(PC)1008e。应当注意,PUMP 1003可以关于子系统1002中代码的执行使用,但是可以被认为是元数据处理子系统1004的一部分。可以标记子系统1002中的全部代码和数据,比如一般地由与数据1002b相关联的标记1002a图示的,其中1002a和1002b可以存储在存储器1008a中。类似地,元素1001a表示关于PC 1008e的指令的标记,1001b表示指令1008b的标记,1001c表示存储器位置1008a的标记,且1001d表示寄存器1008c的标记。

元数据处理子系统1004是包括使用当前指令的标记和作为到PUMP1003的输入提供的关联数据的关于元数据规则处理使用的组件的处理器(也称为元数据处理器)。PUMP1003可以如在这里其他地方描述的且包括规则高速缓存。例如,在至少一个实施例中,PUMP1003可以包括图22中图示的组件。PUMP 1003的组件的更多具体图示和实例,用于PUMP输入和输出的关联的PUMP CSR和可以在根据在这里的技术的至少一个实施例中包括的关联逻辑以下和在这里其他地方更加详细地描述。子系统1004是用于元数据处理的单独的处理器且包括类似于子系统1002中的那些组件。子系统1004包括存储器1006a,I-存储1006b,寄存器文件1006b和ALU 1006d。存储器1006a可以包括关于元数据规则处理使用的元数据结构。例如,存储器1006a可以包括由作为指针的标记指向的结构或者数据。指针标记和由指针标记指向的结构/数据的实例在这里其他地方描述,比如关于CFI策略描述。I-存储1006b和存储器1006a可以包括指令或者代码,比如执行元数据处理的未命中处理器。元数据处理器1004不需要访问1002的其他组件,比如关于程序执行使用的数据存储器1008a,因为元数据处理器1004仅执行元数据处理(例如,基于标记和规则)。子系统1004包括它自己的组件,比如单独的存储器1006a,且不需要存储子系统1002中的元数据处理代码和数据。而是,任何信息,比如可以由PUMP 1003使用的当前指令的标记,被作为输入提供给元数据处理子系统1004(例如,PUMP输入1007)。

实例1000图示具有单独的元数据处理子系统1004的替换实施例,而不是在如在这里其他地方描述的对一般程序执行使用的相同子系统上执行元数据处理。例如,不是启用单独的元数据处理器或者子系统1004,而是实施例可以仅包括PUMP 1003和子系统1002。在具有单个处理器的这种实施例中,CSR可以如在这里描述的使用以在元数据处理和执行用户程序的普通处理模式之间传递信息以由此提供隔离和分隔。在具有单个处理器而不是单独的元数据处理器的这种实施例中,未命中处理器的代码可以用使其受保护的方式来存储在该单个存储器中。例如,没有单独的元数据处理器或者子系统,可以使用如在这里其他地方描述的标记来保护未命中处理器的代码以限制访问,未命中处理器的代码可以映射到不可由用户代码等访问的存储器的部分。

现在将描述的是关于PUMP I/O(输入/输出)的更多细节。应当注意,以下描述的PUMP I/O应用于可以使用与一般代码执行相同的处理器或者子系统的PUMP的实施例以及可以使用单独的处理器或者子系统的实施例,比如在实例1000中的。此外,以下描述的PUMPI/O可以与基于RISC-V架构的实施例一起使用,且可以通用化以用于其他处理器架构。